### SEMICONDUCTOR TECHNICAL DATA

## KIC9316F/FA/FB

CMOS DIGITAL INTEGRATED CIRCUIT

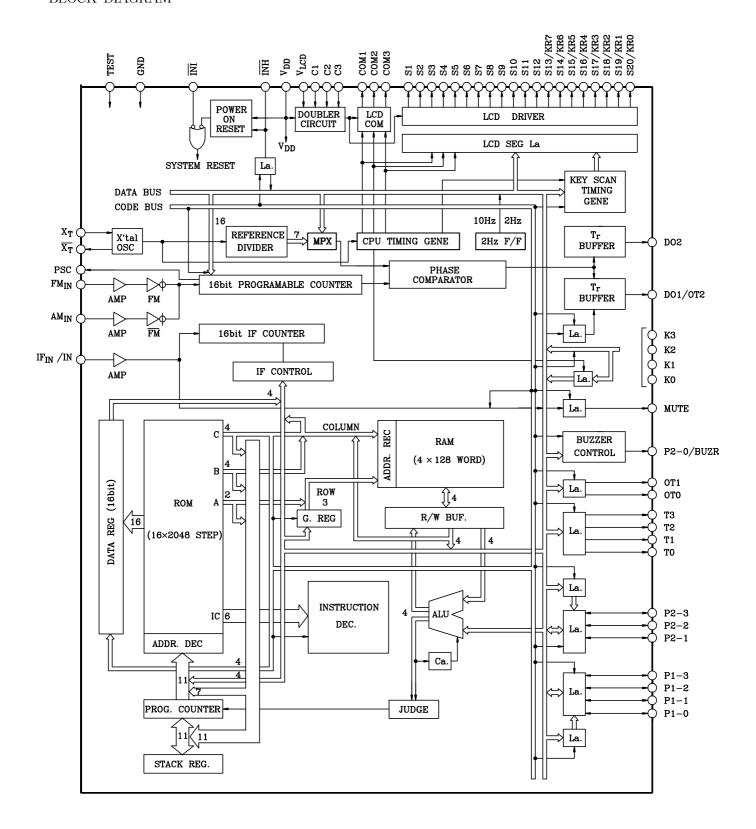

# DTS MICRO CONTROLLER CONTAINING PLL, LCD DRIVER (DTS-11)

The KIC9316F/FA/FB are a 4bit CMOS microcontroller for digital tuning system capable of making 3V low voltage operation, and containing PLL circuit, LCD driver. CPU has 4bit parallel addition and substruction (AI/SI instructions, etc.), logical operation (OR, AN instructions etc.), plural bit judge, comparison instructions (TM, SL instructions, etc.) and time base function.

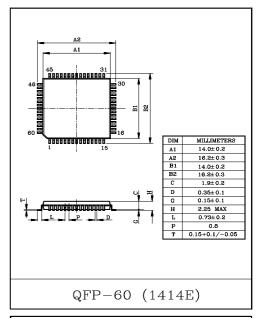

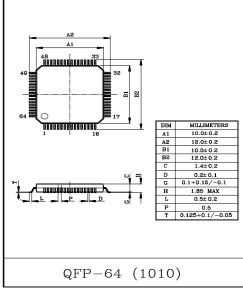

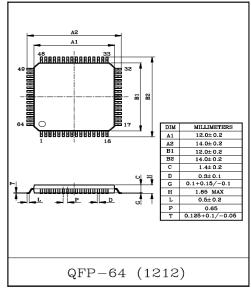

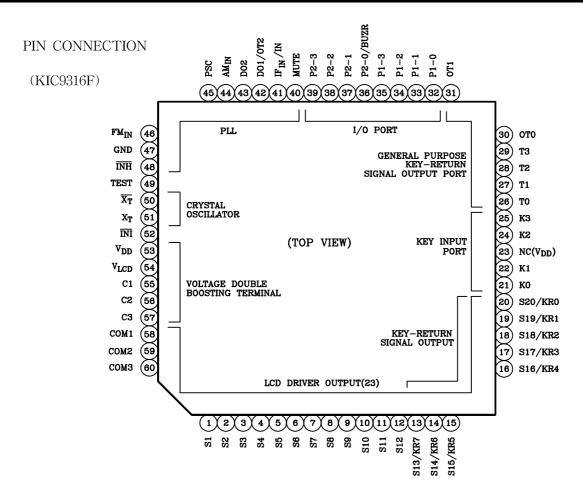

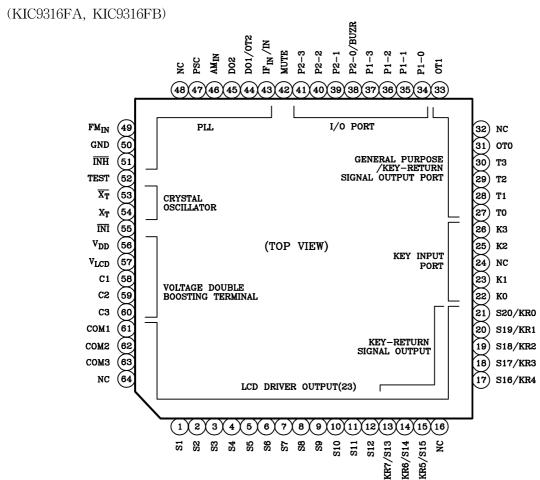

The package is 60pin mini-flat type (KIC9316F), 64 pin mini-flat type (KIC9316FA, KIC9316FB) and has abundant I/O ports and exclusive key-input ports controlled by the powerful input/output instructions (IO, KEY instructions), besides containing PLL circuit.

By combining with the prescaler KID6134AF or KID7101F or KID7103F, it permits the configuration of DTS that receives FM/AM and TV(VHF) bands.

#### **FEATURES**

- · 4bit micro controller for digital tuning system use.

- It is operated with 3V single power supply.  $(V_{DD}=1.8\sim3.6V)$

- Back up of data memory (RAM) and each ports are easily made. (By  $\overline{\text{INH}}$  terminal)

- Built-in LCD driver (1/3 duty, 1/2 bias driving, driving frequency

52Hz) and boosting circuit for display.

- · Program memory (ROM): 16bit×2048 steps.

- Data memory (RAM) : 4bit×128 words.

- · Powerful instruction set of 65 kinds. (all single word instruction).

- Instruction executing time 80µS. (75kHz crystal connection).

- Abundant addition and substruction instructions.

(Addition instructions 12 kinds, substraction instructions 12 kinds).

- Powerful compound judge instructions.

(TMTR, TMFR, TMT, TMF, TMTN, TMFN instructions).

- · Data transfer in same low address is possible.

- Indirect transfer of register is possible.

(MVRD, MVRS, MVGD, MVGS instructions).

- 16 Powerful general registers. (arranged in RAM).

- · Stack level: 1 Level.

- Program memory (ROM) has no conception of page, field, and JUMP and CAL instruction can be freely made among 2048 steps.

- At the FM or TV band, swallow counter is composed by combining with prescaler KID6134AF or KID7103F, and is able to receive TV VHF band. At the AM or FM band, swallow counter is composed by combining with prescaler KID7101F, and is able to receive SW, AM, FM band.

- It is possible to freely refer to the contents, 16bits, of optional address within 1024 steps in program memory (ROM). (DAL instruction)

- Independent frequency input terminal at FM and AM (FM<sub>IN</sub>, AM<sub>IN</sub>), and two phase-comparator outputs. (DO1, DO2)

- 7 kinds of reference frequency can be selected with program.

- · Powerful input/output instructions. (IO, KEY instructions)

- Exclusive input port (K0~K3) for key input use and abundant 23 exclusive LCD driving terminals.

- Abundant 15 I/O ports. (ports for which input and output can be assigned for each bit : 8, exclusive output port : 7)

- IF<sub>IN</sub> port and DO1 port are able to use IN port (exclusive input port) and OT2 port (exclusive output port) by changing instruction.

- 3 kinds of back-up mode (only CPU operating, crystal oscillation and clock stop) are possible by instructions.

- · 2Hz timer F/F and 10Hz interval pulse output are contained. (internal port for time base use)

- · Locked condition of PLL can be detected.

- · Universal-type IF counter is built in.

- 8 Output ports in LCD segment ports (S13~S20) are able to use as key return timing output ports. exclusive output ports are not only use key return timing output ports but use the others.

- 16 bit universal-type IF counter is built in, It is able to detect the auto stop signal at auto-tuning mode with counting intermediate frequency of each band.

- · Built-in 3V voltage regulation circuit for driving LCD.

### MAXIMUM RATINGS (Ta=25℃)

| CHARACTERISTIC              | SYMBOL             | RATING                    | UNIT          |

|-----------------------------|--------------------|---------------------------|---------------|

| Power Supply Voltage        | $ m V_{DD}$        | -0.3~4.0                  | V             |

| Input Voltage               | $ m V_{IN}$        | -0.3~V <sub>DD</sub> +0.3 | V             |

| Power Dissipation           | $P_{D}$            | 100                       | mW            |

| Operating Temperature Range | $T_{opr}$          | -10~60                    | ${\mathbb C}$ |

| Storage Temperature Range   | $T_{\mathrm{stg}}$ | -55 <b>~</b> 125          | $^{\circ}$    |

#### ELECTRICAL CHARACTERISTICS

(Unless otherwise specified,  $V_{DD}=3.0V$ , Ta=25°C)

|   | CHARACTERISTIC | SYMBOL CIRCU | I TEST CONDITION I | MIN. | TYP. | MAX. | UNIT |

|---|----------------|--------------|--------------------|------|------|------|------|

|   |                |              |                    |      |      |      |      |

| 1 | 0 11 70        |              |                    |      |      |      |      |

| Operating Power<br>Supply Voltage Range | $ m V_{DD}$        | - | -                                                         | 1.8 | 3.0 | 3.6 | V       |

|-----------------------------------------|--------------------|---|-----------------------------------------------------------|-----|-----|-----|---------|

| Memory Holding<br>Voltage Range         | $ m V_{HD}$        | - | Crystal oscillation stops * (Executing CKSTP instruction) | 1.2 | ~   | 3.6 | V       |

|                                         | $I_{\mathrm{DD1}}$ | _ | Normal Operation,<br>Output No-load                       | -   | 0.7 | 2.0 | mA      |

| Operating Power                         | ${ m I}_{ m DD2}$  | _ | At only CPU operation,<br>(Radio off, lighting display)   | ı   | 60  | 150 |         |

| Supply Current                          | $ m I_{DD3}$       | _ | At stand-by mode (Radio off, only crystal oscillation)    | -   | 50  | 100 | $\mu A$ |

| Memory Holding Power Supply Current     | $ m I_{HD}$        | _ | Crystal oscillation stop (Executing CKSTP instruction)    | ı   | 0.1 | 1.0 | μΑ      |

| Crystal Oscillation<br>Frequency        | $f_{\mathrm{XT}}$  | _ | *                                                         | -   | 75  |     | kHz     |

| Crystal Oscillation<br>Starting Time    | t <sub>ST</sub>    | _ | Crystal Oscillation=75kHz                                 | _   | _   | 1.0 | S       |

### Voltage Double Boosting Circuit

| Voltage Double<br>Reference Voltage      | $ m V_{EE}$      | _ | V <sub>DD</sub> Reference (C3) | -1.2 | -1.5 | -1.8 | 77 |

|------------------------------------------|------------------|---|--------------------------------|------|------|------|----|

| Voltage Double<br>Boosting Voltage       | $ m V_{LCD}$     | _ | $V_{DD}$ Reference $(V_{LCD})$ | -2.4 | -3.0 | -3.6 | v  |

| V <sub>LCD</sub> Pull-Down<br>Resistance | R <sub>IN3</sub> | _ | $(V_{ m LCD})$                 | 0.75 | 1.5  | 3.0  | ΜΩ |

<sup>\*</sup> Marked items are guaranteed by all conditions of  $V_{DD}$ =1.8~3.6V, Ta=-10~60°C

| CHARACT                                | TERISTIC       | SYMBOL             | TEST<br>CIRCUIT | TEST CONDITION                                                         | ON   | MIN. | TYP. | MAX.                 | UNIT         |

|----------------------------------------|----------------|--------------------|-----------------|------------------------------------------------------------------------|------|------|------|----------------------|--------------|

| rogrammable                            | counter, IF    | counter            |                 |                                                                        |      |      |      |                      |              |

| Operating Fre                          | equency        | $f_{ m IN1}$       | _               | $V_{\rm IN}$ =0.3 $V_{\rm P-P}$ (FM <sub>IN</sub> , AM <sub>IN</sub> ) | *    | 0.2  | ~    | 5.0                  | MHz          |

| Range                                  |                | $ m f_{IN2}$       | -               | $V_{IN}$ =0.3 $V_{P-P}$ (IF <sub>IN</sub> )                            | *    | 0.35 | ~    | 12.0                 | NII Z        |

| Operating Inp                          | ut             | $V_{\mathrm{IN1}}$ | _               | $f_{IN}$ =0.2~5.0MHz (FM <sub>IN</sub> , AM <sub>IN</sub> )            | *    | 0.3  | ~    | V <sub>DD</sub> -0.3 |              |

| Amplitude Ra                           |                | $ m V_{IN2}$       | -               | $f_{IN}$ =0.35 ~ 12.0MHz (IF <sub>IN</sub> )                           | *    | 0.3  | ~    | V <sub>DD</sub> -0.3 | $ m V_{P-P}$ |

| rogrammable                            | counter, IF    | counter            |                 |                                                                        |      |      |      |                      |              |

| FM <sub>IN</sub> -PSC Tr<br>Delay Time | ansfer         | $t_{\mathrm{pd}}$  | _               | V <sub>IN</sub> =0.3V <sub>P-P</sub> ,<br>C=15pF (FM <sub>IN</sub> )   | *    | _    | -    | 200                  | nS           |

| PSC Maximur<br>Load Capacity           |                | $C_{L}$            | -               | (PSC)                                                                  | *    | -    | _    | 15                   | рF           |

| CD common                              | output (CO     | M1~COM             | 3)              |                                                                        |      |      |      |                      |              |

| Output                                 | "II" I orrel   | I <sub>OH1</sub>   | -               | $V_{LCD}=0V$ , $V_{OH}=2.7V$                                           |      | -100 | -200 | _                    |              |

| Current                                | "L" Level      | I <sub>OL1</sub>   | _               | $V_{LCD}=0V$ , $V_{OL}=0.3V$                                           |      | 100  | 200  | _                    | μΑ           |

| .CD segment                            | output (S1     | ~S20)              |                 |                                                                        |      |      |      |                      |              |

| Output                                 | "II" I ozzol   | I <sub>OH2</sub>   | _               | $V_{LCD}$ =0V, $V_{OH}$ =2.7V                                          |      | -0.5 | -1.0 | _                    | mA           |

| Current                                | "L" Level      | I <sub>OL2</sub>   | _               | $V_{LCD}=0V$ , $V_{OL}=0.3V$                                           |      | 50   | 100  | _                    | μΑ           |

| Kev return ou                          | itnut nort g   | eneral nuri        | oose outr       | out port (T0~T3, O                                                     | T0~0 | T1)  |      |                      |              |

| "H" Level Ou                           |                | I <sub>OH3</sub>   | -               | $V_{OH}$ =2.7V (T0~T3)                                                 | 100  | -0.5 | -1.0 | _                    | mA           |

| N-ch FET Si<br>Resistance              | de Load        | Ron                | _               | V <sub>OL</sub> =3.0V (T0~T3)                                          |      | 75   | 150  | 300                  | kΩ           |

| Aute, psc out                          | nut            |                    | l               |                                                                        |      |      |      |                      |              |

| , 1                                    | //II// I ozzol | $I_{ m OH4}$       | _               | V <sub>OH</sub> =2.7V                                                  |      | -300 | -600 | _                    |              |

| Output<br>Current                      | "L" Level      | I <sub>OL4</sub>   | _               | $V_{OL}$ =0.3V                                                         |      | 300  | 600  | _                    | μΑ           |

| 001/OT2, DO                            | 19 output      | 1                  | I               | 1                                                                      |      | I    | I    | l                    |              |

|                                        | "H" Level      | $I_{ m OH4}$       | _               | V <sub>OH</sub> =2.7V                                                  |      | -300 | -600 | _                    |              |

| Output<br>Current                      | "L" Level      | I <sub>OL4</sub>   | _               | V <sub>OL</sub> =0.3V                                                  |      | 300  | 600  | _                    | μΑ           |

| Output off-Le<br>Current               | eakage         | $I_{\mathrm{TL}}$  | _               | V <sub>TLH</sub> =3.0V, V <sub>TLL</sub> =0V                           |      | _    | _    | ±100                 | nA           |

| Current                                |                | 1                  | l               |                                                                        |      | I    |      | 1                    |              |

<sup>\*</sup> Marked items are guaranteed by all conditions of  $V_{DD}$ =1.8~3.6V, Ta=-10~60°C

| CHARACTERISTIC | SYMBOL TEST CIRCUIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT |

|----------------|---------------------|----------------|------|------|------|------|

|----------------|---------------------|----------------|------|------|------|------|

### General purpose I/O port (P1-0~P1-3, P2-0~P2-3)

| Output                | "H" Level | $I_{ m OH4}$       | _ | $V_{OH}$ =2.7 $V$            | -300 | -600 | _    |    |

|-----------------------|-----------|--------------------|---|------------------------------|------|------|------|----|

| Current               | "L" Level | $I_{\mathrm{OL4}}$ | - | $V_{OL}$ =0.3 $V$            | 300  | 600  | _    | μΑ |

| Input Leakage Current |           | $I_{LI}$           | = | $V_{IH}$ =3.0V, $V_{IL}$ =0V | =    | -    | ±1.0 |    |

| Input                 | "H" Level | $V_{ m IH1}$       | - | _                            | 2.4  | ~    | 3.0  | V  |

| Voltage               | "L" Level | $V_{\rm IL1}$      | - | _                            | 0    | ~    | 0.6  | V  |

### $\overline{INI}$ input, $IF_{IN}/IN$ port (When using in port)

| Input Leakage | Input Leakage Current |              | П | $V_{IH}$ =3.0V, $V_{IL}$ =0V | -   | - | ±1.0 | $\mu A$ |

|---------------|-----------------------|--------------|---|------------------------------|-----|---|------|---------|

| Input         | "H" Level             | $ m V_{IH2}$ | - | ( <del>INI</del> , IN0~IN3 ) | 2.4 | ~ | 3.0  | V       |

| Voltage       | "L" Level             | $ m V_{IL2}$ | - | ( <del>INI</del> , IN0~IN3 ) | 0   | ~ | 0.6  | V       |

### Key input port (K0∼K3)

| Input Pull-Down<br>Resistance |           | $ m R_{IN1}$ | - | - | 75  | 150 | 300 | kΩ  |

|-------------------------------|-----------|--------------|---|---|-----|-----|-----|-----|

| Input                         | "H" Level | $ m V_{IH2}$ | - | _ | 1.8 | ~   | 3.0 | 7.7 |

| Voltage                       | "L" Level | $ m V_{IL2}$ | - | - | 0   | ~   | 0.3 | V   |

### $\overline{\text{INH}}$ input port

| Input Leakage Current |           | ${ m I}_{ m LI}$ | - | $V_{IH}$ =3.0V, $V_{IL}$ =0V | -   | - | ±1.0 | μΑ |

|-----------------------|-----------|------------------|---|------------------------------|-----|---|------|----|

| Input                 | "H" Level | $ m V_{IH3}$     | - | _                            | 2.6 | ~ | 3.0  | V  |

| Voltage               | "L" Level | $ m V_{IL3}$     | _ | _                            | 0   | ~ | 1.2  | V  |

### Others

| Input Pull-Down<br>Resistance   | R <sub>IN2</sub>   | _ | (TEST)                                                    | 25   | 50  | 100  | kΩ        |

|---------------------------------|--------------------|---|-----------------------------------------------------------|------|-----|------|-----------|

| XT Input Feedback<br>Resistance | $ m R_{fXT}$       | _ | $(X_T \sim \overline{X_T})$                               | 3.75 | 7.5 | 15.0 | $M\Omega$ |

| XT Output Resistance            | R <sub>OUT</sub>   | - | $\overline{(X_T)}$                                        | 50   | 100 | 200  |           |

| Input Pull-Down<br>Resistance   | $R_{\mathrm{fIN}}$ | _ | (FM <sub>IN</sub> , AM <sub>IN</sub> , IF <sub>IN</sub> ) | 375  | 750 | 1500 | kΩ        |

<sup>\*</sup> Marked items are guaranteed by all conditions of  $V_{DD}$ =1.8~3.6V, Ta=-10~60°C

#### BLOCK DIAGRAM

PIN FUNCTION

(Data in parentheses are for KIC9316FA, KIC9316FB)

| PIN NO.                                                                                     | SYMBOL              | PIN NAME                                   | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                       | REMARKS          |

|---------------------------------------------------------------------------------------------|---------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 58<br>(61)                                                                                  | COM1                |                                            | This is a common signal output terminal to LCD.                                                                                                                                                                                                                                                                              | V <sub>DD</sub>  |

| 59<br>(62)                                                                                  | COM2                | LCD Common<br>Output                       | Indication of maximum 60 segments is possible with matrix made with S1 ~ S20. To this terminal, three value                                                                                                                                                                                                                  | $v_{\rm EE}$     |

| 60<br>(63)                                                                                  | СОМЗ                |                                            | levels of $V_{\rm DD}$ , $V_{\rm EE}$ , $V_{\rm LCD}$ are output with 3.2mS interval and 52Hz cycle.                                                                                                                                                                                                                         | V <sub>LCD</sub> |

| 1~12                                                                                        | S1~S12              | LCD Segment<br>Output                      | This is a segment signal output terminal to LCD. Indication of maximum 60 segments is possible with matrix made with COM1, COM2 and COM3. The data for these terminals are output by the execution of SEG                                                                                                                    | V <sub>DD</sub>  |

| $   \begin{array}{c}     13 \sim 20 \\     (13 \sim 15) \\     (17 \sim 21)   \end{array} $ | S13/KR7<br>~S20/KR0 | LCD Segment<br>Output/Key<br>Return Output | instruction and MARK instruction. \$13/KR7~\$20/KR0 are able to output LCD segment signal and Key Return Timing signal at same time by program. Maximum 32(=8×4) Key input be able to combine with matrix made with Key input ports K0~K3 without the other output port.                                                     | V <sub>LCD</sub> |

| 21, 22<br>24, 25<br>(22, 23)<br>(25, 26)                                                    | K0∼K3               | Key Input Port                             | This is a 4bit input port for key matrix input.  It is able to input data of maximum total 56 key, maximum 24 key (=6×4) with matrix made with Key Return Timing output port, besides maximum 32 key (8×4) with matrix made with LCD Segment Output S13/KR7~S20/KR0. All these terminals are built in pull down resistances. | V <sub>DD</sub>  |

| PIN NO.          | SYMBOL               | PIN NAME                                                | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                    | REMARKS                          |

|------------------|----------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 26~29<br>(27~30) | Т0~Т3                | General Purpose<br>/Key Return<br>Timing Output<br>Port | This is a 6bit output port for General Purpose/Key Return Timing output. Besides use for general purpose output port, it is able to output the timing signal for key matrix by program. For making the key matrix, it is built in load resistance at N-ch FET side, useless the diode when used push key. | V <sub>DD</sub>                  |

| 30, 31 (31, 33)  | OT0, OT1             |                                                         |                                                                                                                                                                                                                                                                                                           | RoN                              |

| 32~35<br>(34~37) | P1-0~P1-3            | I/O Port                                                | This is a 8bit general purpose I/O Port. It is possible to assign input and output for each bit by program. P2-0 is able to use as the beep sound pulse output port by program. It is able to output 3 kinds of the beep sound pulse signal by program.                                                   | V <sub>DD</sub> V <sub>DD</sub>  |

| 36<br>(38)       | P2-0/BUZR            | I/O Port/Buzzer<br>Pulse Output<br>Port                 |                                                                                                                                                                                                                                                                                                           |                                  |

| 37~39<br>(34~41) | P2-1~P2-3            | I/O Port                                                |                                                                                                                                                                                                                                                                                                           |                                  |

| 40<br>(42)       | MUTE                 | Muting Output<br>Port                                   | This is a 1bit output port. This is usually used as muting control signal output.                                                                                                                                                                                                                         | V <sub>DD</sub>                  |

| 41 (43)          | IF <sub>IN</sub> /IN | IF Counter Input<br>Port/Input Port                     | This is an IF signal input terminal of 16bit general purpose IF counter. This terminal has built-in amplifiers, and operates with C-connection and small amplitude. It is able to use as a 1bit general purpose input port by program.                                                                    | R <sub>fIN</sub> V <sub>DD</sub> |

| 42<br>(44)       | DO1/OT2              | Phase<br>Comparator<br>Output/Output<br>Port            | This is a phase comparator output terminal of PLL. DO1 and DO2 are parallel outputs. Therefore, optimum filter constant can be set for each band of FM/AM. DO1 is able to use as a 1bit general purpose output port by program.                                                                           | V <sub>DD</sub>                  |

| 43<br>(45)       | DO2                  | Phase<br>Comparator<br>Output                           |                                                                                                                                                                                                                                                                                                           |                                  |

| PIN NO.    | SYMBOL                      | PIN NAME                            | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                | REMARKS                          |

|------------|-----------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 44 (46)    | $ m AM_{IN}$                | AM<br>Programmable<br>Counter Input | This is a programmable counter input terminal at 12bit direct frequency-divider mode.  Usually the local oscillator signal at AM band is input to this terminal.  This terminal has built-in amplifiers, and operated with C-connection and small amplitude.                                                                                                          | R <sub>fIN</sub> V <sub>DD</sub> |

| 45<br>(47) | PSC                         | Prescaler<br>Control Output         | This is an output terminal which controls 1/15 or 1/16 frequency-dividing mode of two modulus prescaler.  This output signal controls two frequency-dividing mode of external prescaler as using programmable counter for pulse-swallow counter.  "H": 1/16, "L": 1/15                                                                                                | V <sub>DD</sub>                  |

| 46<br>(49) | $\mathrm{FM}_{\mathrm{IN}}$ | FM<br>Programmable<br>Counter Input | This is an input terminal of programmable counter at 16bit swallow-counter mode.  This terminal is input the divided frequency output signal of external prescaler, and has built-in input amplifiers and operates with C-connection and small amplitude.                                                                                                             | R <sub>fIN</sub>                 |

| 48<br>(51) | ĪNH                         | Inhibit Input                       | This is a signal input terminal for selecting radio mode. "H": radio ON, "L": radio OFF                                                                                                                                                                                                                                                                               | V <sub>DD</sub>                  |

| 49<br>(52) | TEST                        | Test Input                          | This is an input terminal for controlling test mode control. At "H" level, test mode is made, and at "L" level, normal operation is carried out. In the test mode, the device operates as evaluator chip, and program evaluation is made possible on EPROM base through combination with external simulation board. This terminal is built in a pull-down resistance. | V <sub>DD</sub>                  |

| PIN NO.    | SYMBOL                      | PIN NAME                                                    | FUNCTION AND OPERATION                                                                                                                                                        | REMARKS                                         |

|------------|-----------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 50<br>(53) | $\overline{X_{\mathrm{T}}}$ | Crystal<br>Oscillation<br>Terminal                          | This is a connecting terminal of crystal resonator. Reference crystal of 75kHz is connected. During the execution of CKSTP instruction, oscillation is automatically stopped. | $R_{OUT}$ $\overline{X}_{T}$ $R_{fXT}$ $V_{DD}$ |

| 51<br>(54) | $X_{\mathrm{T}}$            |                                                             |                                                                                                                                                                               | X <sub>T</sub>                                  |

| 52<br>(55) | ĪNĪ                         | Initializing<br>Input                                       | This is a system reset signal input terminal of the device.  During INT is at "L" level, reset is applied, and when it becomes "H" level, it is normal operation mode.        | V <sub>DD</sub>                                 |

| 54<br>(57) | $V_{ m LCD}$                | Voltage Double<br>Boosting<br>Terminal                      | These are voltage double boosting terminal for driving LCD. Boosting capacitors are connected to these terminals. (Typ. $0.1\mu\text{F}\sim3.3\mu\text{F}$ )                  | -                                               |

| 55<br>(58) | C1                          |                                                             |                                                                                                                                                                               |                                                 |

| 56<br>(59) | C2                          |                                                             |                                                                                                                                                                               |                                                 |

| 57<br>(60) | СЗ                          | Reference Voltage Stabilizing Capacitor Connecting Terminal | The stabilizing capacitor of Reference Voltage is connected to this terminal for LCD driving. (Typ. $0.01\mu F \sim 0.1\mu F$ )                                               | _                                               |

| 53<br>(56) | $ m V_{DD}$                 | Power Supply<br>Terminal                                    | Power supply voltage is applied. $V_{DD}$ =1.8 $\sim$ 3.6V (Typ. 3.0V)                                                                                                        | -                                               |

| 47<br>(50) | GND                         |                                                             |                                                                                                                                                                               |                                                 |