# Description

The HDG14P180 is a 4-bit single chip microcomputer which has mounted a standard EPROM 2764/27128 for program memory.

The HD614P180 is pin-compatible with the mask ROM type HMCS412C, but has some differences with it as shown in Table 26. By modifying the program in the EPROM, it can be used for the evaluation of the HMCS412C or for small-scale production.

#### HARDWARE FEATURES

- 4-bit Architecture

- Applicable to 4k or 8k words x 10 bits of EPROM

2048 words x 10 bits HN482764, HN27C64

8192 words x 10 bits . . . . HN4827128

- Data Memory (RAM) Capacity . . . . . . 576 digits x 4 bits.

- 36 I/O Pins 24 I/O pins are high voltage up to 40V (max.).

- 1 Timer/Counter

11-bit Prescaler

8-bit Auto-reload Timer/Event Counter (Timer B)

3 Interrupts

External 2

Timer/Counter 1

- Subroutine Stack

- Up to 16 levels including interrupts

- Minimum Instruction Execution Time; 1,33 μs

- 2 Low Power Modes

- Standby Stops instruction execution while keeping clock generator and interrupt functions included Timer/Counter in operation

- Stop Stops instruction execution and clock generation while retaining RAM data

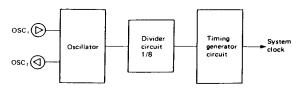

- Clock Generator

External Connection of Crystal Resonator or Ceramic Filter Resonator (externally drivable)

- Power Voltage Range; 5V ± 10%

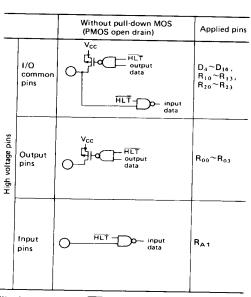

- I/O Pin Circuit Form

All standard pins are "without pull-up MOS"

All high voltage pins are "without pull-down MOS".

- 42 Pin EPROM On-package

- SOFTWARE FEATURES

- Software Compatible with HMCS412/414

- Instruction Set Similar to and More Powerful than HMCS40 Series; 98 Instructions

- High Programming Efficiency with 10-bit ROM/Word; 78 instructions are single word instructions.

- Direct Branch to All ROM Area

- Direct or Indirect Addressing to All RAM Area

- Subroutine Nesting Up to 16 Levels Including Interrupts

- Binary and BCD Arithmetic Operation

- Powerful Logic Arithmetic Operation

- Pattern Generation Table Look Up Capability -

- Bit Manipulation for Both RAM and I/O

#### **■ PROGRAM DEVELOPMENT SUPPORT TOOLS**

- Cross assembler and simulator software for use with IBM PCs and compatibles

- In circuit emulator for use with IBM PC

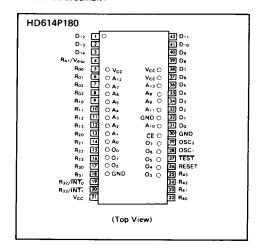

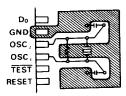

#### ■ PIN ARRANGEMENT

#### RECOMMENDED APPLICABLE EPROM

| Type No.  | Program Memory<br>Capacity | f <sub>osc</sub> (MHz) | EPROM Type No.           |

|-----------|----------------------------|------------------------|--------------------------|

|           | 2048 words<br>4096 words   | 4                      | HN27C64-30<br>HN482764-3 |

| HD614P180 |                            | 6                      | HN27C64G-25<br>HN482764  |

|           | 8192 words                 | 4                      | HN4827128-45             |

|           | 6192 Words                 | 6                      | HN4827128-25             |

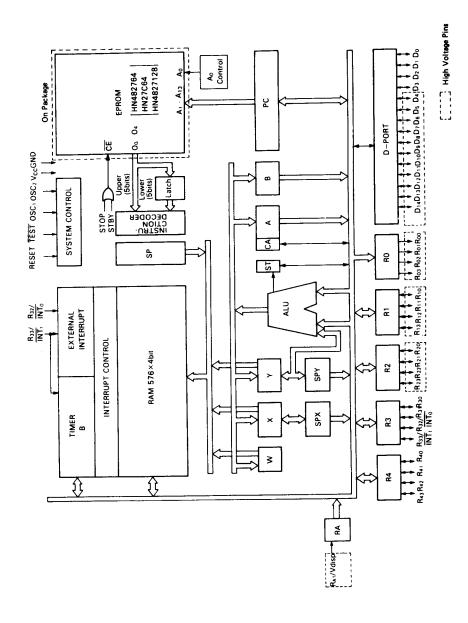

# **■ BLOCK DIAGRAM**

( HITACHI

Hitachi America Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

# ABSOLUTE MAXIMUM RATINGS

| Item                               | Symbol                                | Value                                       | Unit | Note  |

|------------------------------------|---------------------------------------|---------------------------------------------|------|-------|

| Supply Voltage                     | Vcc                                   | -0.3 to +7.0                                | V    |       |

|                                    | , , , , , , , , , , , , , , , , , , , | -0.3 to V <sub>CC</sub> +0.3                | V    | 3     |

| Terminal Voltage                   | VT                                    | V <sub>CC</sub> -45 to V <sub>CC</sub> +0.3 | V    | 4     |

| Total Allowance of Input Currents  | ΣΙο                                   | 50                                          | mA   | 5     |

| Total Allowance of Output Currents | $-\Sigma I_{O}$                       | 150                                         | mA   | 6     |

| Maximum Input Current              | lo lo                                 | 15                                          | mA   | 7, 8  |

|                                    |                                       | 4                                           | mA   | 9, 10 |

| Maximum Output Current             | -I <sub>O</sub>                       | 6                                           | mA   | 9, 11 |

|                                    |                                       | 30                                          | mA   | 9, 12 |

| Operating Temperature              | Topr                                  | -20 to +75                                  | °C   |       |

| Storage Temperature                | T <sub>stq</sub>                      | -55 to +125                                 | °C   |       |

(Note 1) Permanent damage may occur if "Absolute Maximum Ratings" of the LSI or the EPROM are exceeded, Normal operation should be under the conditions of "Electrical Characteristics". If these conditions are exceeded, it may cause the malfunction and affect the reliability of LS1.

(Note 2) All voltages are with respect to GND.

(Note 3) Applied to standard pins.

(Note 4) (Note 5) Applied to high voltage I/O pins.

Total allowance of input current is the total sum of input current which flow in from all I/O pins to GND simultaneously.

(Note 6) Total allowance of output current is the total sum of the output current which flow out from V<sub>CC</sub> to all I/O pins simultaneously.

(Note 7) againowance or output current is the torat sum of the output current which flow out from  $V_C$  (Note 8) Maximum input current is the maximum amount of input current from each I/O pin to GND. (Note 8) Applied to  $D_a \sim D_1$  and  $R_3 \sim R_4$ . (Note 10) (Note 10) Maximum output current is the maximum amount of output current from  $V_{CC}$  to each I/O pin. (Note 11) Applied to  $D_a \sim D_1$  and  $R_3 \sim R_4$ . (Note 12) Applied to  $D_4 \sim D_1$  and  $R_3 \sim R_4$ . (Note 12) Applied to  $D_4 \sim D_1$ . (Note 7) (Note 8)

# ■ ELECTRICAL CHARACTERISTICS

DC CHARACTERISTICS (V<sub>CC</sub> = 4.5V to 5.5V, GND = 0V, Ta = −20 to +75°C, if not specified.)

|                                           |                   |                                                                     |                                                                                                           | Value                                                                 |                    |     | Unit                 | Note  |     |

|-------------------------------------------|-------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|-----|----------------------|-------|-----|

| item                                      | Symbol            | Pin Name                                                            | Test C                                                                                                    | Test Conditions                                                       |                    | typ | max                  | J     |     |

| nput "High"                               |                   | RESET,                                                              |                                                                                                           |                                                                       | 0,7V <sub>CC</sub> | -   | V <sub>CC</sub> +0.3 | v     |     |

| Voltage                                   | Viн               | OSC <sub>1</sub>                                                    |                                                                                                           |                                                                       | V∞-0.5             |     | V <sub>CC</sub> +0.3 | v     |     |

| Input "Low"                               |                   | RESET,                                                              |                                                                                                           |                                                                       | -0.3               | -   | 0.22V <sub>CC</sub>  | \ \ \ |     |

| Voltage                                   | V <sub>IL</sub>   | OSC <sub>1</sub>                                                    |                                                                                                           |                                                                       | -0.3               | _   | 0.5                  | V     |     |

| input/Output<br>Leakage Current           | hirl              | RESET,<br>INT <sub>0</sub> , INT <sub>1</sub> ,<br>OSC <sub>1</sub> | Vin = 0V to V <sub>CC</sub>                                                                               |                                                                       |                    | -   | 1                    | μА    | 1   |

| Current<br>Dissipation in<br>Active Mode  | ¹cc               | vcc                                                                 | Vcc-5V                                                                                                    | Crystal or<br>Ceramic Filter<br>Oscillator<br>fosc = 4MHz             | _                  |     | 2.0                  | mA    | 2,5 |

| Current<br>Dissipation in<br>Standby Mode | SBY1              | Vcc                                                                 | Maximum<br>Logic<br>Operation<br>V <sub>CC</sub> = 5V                                                     | Crystal or<br>Ceramic Filter<br>Oscillator<br>f <sub>osc</sub> = 4MHz |                    | -   | 1.2                  | mA    | 3,5 |

|                                           | ISBY2             | vcc                                                                 | Minimum<br>Logic<br>Operation<br>Vcc ≈ 5V                                                                 | Crystal or<br>Ceramic Filter<br>Oscillator<br>f <sub>osc</sub> = 4MHz | -                  | _   | 0.9                  | mA    | 4,5 |

| Current Dissipation in Stop Mode          | l stop            | Vcc                                                                 | V <sub>in</sub> (TEST) = V <sub>CC</sub> -0.3V to V <sub>CC</sub><br>V <sub>in</sub> (RESET) = 0V to 0.3V |                                                                       | -                  | _   | 10                   | μА    |     |

| Stop Mode<br>Retain Voltage               | V <sub>stop</sub> | Vcc                                                                 |                                                                                                           |                                                                       | 2                  | -   | -                    | v     |     |

(Note 1) Output buffer current are excluded.

(Note 2) The MCU is in the reset state. The input/output current does not flow.

(Note 3) The MCU is in the reset state. The input/output current does not flow.

MCU state:

Pin state:

Pin state:

Po - Dis, R3 ~ R4 ... V<sub>CC</sub> voltage

Do - Di, R3 ~ R2, R4, R4 ... V<sub>CC</sub> ~ V<sub>CC</sub> ~ 40V

(Note 3) The timer/counter with the fastest clock and input/output current does not flow.

Test Conditions:

MCU state:

Pin state:

Test Conditions: MCU state;

Standby Mode

Input/Output; Reset state

• TIMER-B; +2 prescaler divide ratio

Pin state:

RESET ... GND voltage

(Note 4) The timer/counter with the slowest clock and input/output current does not flow.

Standby Mode Test Conditions: MCU state;

• Input/Output; Reset state

TIMER-B;÷ 2048 prescaler divide ratio

Pin state:

RESET ... GND voltage

TEST ... V<sub>CC</sub> voltage

D₀ ~ D₃, R3~R4 ... V<sub>CC</sub> voltage

D₀ ~ D₁₄, R0~R2, R<sub>A1</sub> ... V<sub>CC</sub> ~ V<sub>CC</sub>~40V

(Note 5) When fosc=x[MHz], the Current Dissipation in Operation mode and Standby mode are estimated as follows:

max. value  $(f_{osc}=x[MHz])=\frac{x}{4} \times max$ . value  $(f_{osc}=4[MHz])$

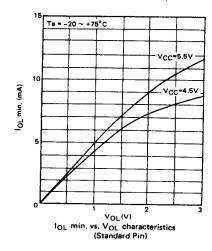

### . INPUT/OUTPUT CHARACTERISTICS FOR STANDARD PIN ( $V_{CC}$ = 4.5V to 5.5V, GND = 0V, $T_a$ = -20 to +75°C, if not specified.)

| ltem                            | Item Symbol     | Pin Name                                     | Test Conditions                         |                    | Value |                      |      | Note  |

|---------------------------------|-----------------|----------------------------------------------|-----------------------------------------|--------------------|-------|----------------------|------|-------|

| nem                             | Symbol          | rini vaine l'est conditions                  |                                         | min                | typ   | max                  | Unit | 14016 |

| Input "High"<br>Voltage         | V <sub>IH</sub> | $D_0 \sim D_3$ ,<br>R3 ~ R4                  |                                         | 0.7V <sub>CC</sub> | -     | V <sub>cc</sub> +0.3 | v    |       |

| Input "Low"<br>Voltage          | V,L             | $D_0 \sim D_3$ ,<br>R3 $\sim$ R4             |                                         | -0.3               | -     | 0.22V <sub>CC</sub>  | V    |       |

| Output "Low"<br>Voltage         | V <sub>OL</sub> | $D_0 \sim D_3$ ,<br>R3 $\sim$ R4             | l <sub>OL</sub> = 1.6 mA                | _                  | -     | 0.4                  | V    |       |

| Input/Output<br>Leakage Current | [Կե]            | D <sub>0</sub> ~ D <sub>3</sub> ,<br>R3 ~ R4 | V <sub>in</sub> = 0V to V <sub>CC</sub> | _                  | _     | 1                    | μΑ   | 1     |

(Note 1) Output buffer current are excluded.

# • INPUT/OUTPUT CHARACTERISTICS FOR HIGH VOLTAGE PIN ( $V_{CC}$ = 4.5V to 5.5V, GND = 0V, Ta = -20 to +75°C, if not specified.)

| Item                               | Symbol          | Pin Name                                                      | Test Conditions                                           |                      | Value   |                      | Unit | Note |

|------------------------------------|-----------------|---------------------------------------------------------------|-----------------------------------------------------------|----------------------|---------|----------------------|------|------|

|                                    |                 | 1                                                             |                                                           | min                  | typ max |                      | Unit | Note |

| Input "High"<br>Voltage            | V <sub>IH</sub> | D <sub>4</sub> ~ D <sub>14</sub> , R1,<br>R2, R <sub>A1</sub> |                                                           | 0.7V <sub>CC</sub>   | -       | V <sub>CC</sub> +0.3 | ٧    |      |

| Input "Low"<br>Voltage             | V <sub>IL</sub> | $D_4 \sim D_{14}$ , R1, R2, R <sub>A1</sub>                   | · · · · · · · · · · · · · · · · · · ·                     | V <sub>CC</sub> -40  | _       | 0.22V <sub>CC</sub>  | ٧    |      |

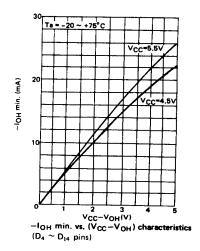

| Output "High"                      | D ~ D           | -I <sub>OH</sub> = 15mA                                       | V <sub>CC</sub> -3.0                                      | _                    | _       | V                    |      |      |

|                                    | V               | 1 ' ' 1                                                       | -I <sub>OH</sub> = 9 mA                                   | Vcc-2.0              | _       | _                    | V    |      |

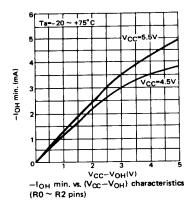

| Voltage                            | Voн             | R0 ~ R2                                                       | -I <sub>OH</sub> = 3 mA                                   | V <sub>CC</sub> -3.0 | _       | _                    | V    |      |

|                                    |                 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                         | -I <sub>OH</sub> = 1.8 mA                                 | Vcc-2.0              | -       | - 1                  | V    |      |

| Output "Low"<br>Voltage            | Vol             | $D_4 \sim D_{14}$ ,<br>R0 $\sim$ R2                           | 150kΩ to V <sub>CC</sub> -40V                             | -                    | _       | V <sub>cc</sub> -37  | ٧    |      |

| Input/Output<br>Leakage<br>Current | [ונר]           | $D_4 \sim D_{14}$ ,<br>$R0 \sim R2$ ,<br>$R_{A1}$             | V <sub>in</sub> = V <sub>CC</sub> -40V to V <sub>CC</sub> | -                    | _       | 20                   | μΑ   | 1    |

(Note 1) Output buffer current are excluded.

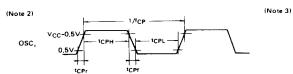

# AC CHARACTERISTICS (V<sub>CC</sub> = 4.5V to 5.5V, GND = 0V, Ta = −20 to +75°C, if not specified.)

|                              |                                      |                  |                                     | Test                           |      | Value |     | Unit             | Note |

|------------------------------|--------------------------------------|------------------|-------------------------------------|--------------------------------|------|-------|-----|------------------|------|

| Item                         |                                      | Symbol Pin Name  | Pin Name                            | Conditions                     | min  | typ   | max | J 01111          |      |

| _ ie _                       | Oscillation Frequency                | fosc             | OSC <sub>1</sub> , OSC <sub>2</sub> |                                | 0.4  | 4     | 6.2 | MHz              |      |

| ie Fil                       | Instruction Cycle Time               | t <sub>cvc</sub> |                                     |                                | 1.29 | 2     | 20  | μς               |      |

| Ceramic Filter<br>Oscillator | Oscillator Stabilization             | t <sub>RC</sub>  | OSC <sub>1</sub> , OSC <sub>2</sub> |                                | -    | -     | 20  | ms               | 1    |

|                              | External Clock Frequency             | fcp              | OSC <sub>1</sub>                    |                                | 0.4  |       | 6.2 | MHz              | 2    |

| <del>č</del>                 | External Clock "High"<br>Level Width | <sup>†</sup> CPH | osc,                                |                                | 70   |       |     | ns               | 2    |

| External Clock               | External Clock "Low"<br>Level Width  | † <sub>CPL</sub> | OSC <sub>1</sub>                    |                                | 70   | -     |     | ns               | 2    |

| teri                         | External Clock Rise Time             | t <sub>CPr</sub> | OSC <sub>1</sub>                    |                                |      |       | 20  | ns               | 2    |

| ũ                            | External Clock Fall Time             | t <sub>CPf</sub> | OSC <sub>1</sub>                    |                                |      |       | 20  | ns               | 2    |

|                              | Instruction Cycle Time               | t <sub>cvc</sub> |                                     |                                | 1.29 | -     | 20  | μs               | 2    |

| īN                           | o "High" Level Width                 | tion             | INTo                                |                                | 2    |       | I - | t <sub>cyc</sub> | 3    |

|                              | o "Low" Level Width                  | tioL             | TNT₀                                |                                | 2    | -     |     | t <sub>cyc</sub> | 3    |

|                              | "High" Level Width                   | t <sub>11H</sub> | ĪNTī                                |                                | 2    | -     | T - | t <sub>cyc</sub> | 3    |

|                              | Ti "Low" Level Width                 | till             | INT                                 |                                | 2    |       | T - | t <sub>cyc</sub> | 3    |

|                              | SET "High" Level Width               | testh            | RESET                               | 1                              | 2    | -     | _   | t <sub>cyc</sub> | 4    |

|                              | out Capacitance                      | C <sub>in</sub>  | all pins                            | f=1MHz<br>V <sub>in</sub> = 0V | _    | _     | 15  | pF               |      |

|                              | SET Fall Time                        | tRSTf            |                                     | 1                              |      |       | 20  | ms               | 4    |

(Note 1) Oscillator stabilization time is the time until the oscillator stabilizes after V<sub>CC</sub> reaches its minimum allowable voltage V<sub>CC</sub> = 4.5V after power-on, or after RESET goes high. At power-on or STOP mode release, RESET Must be kept high for at least t<sub>RC</sub>. Since t<sub>RC</sub> depends on the crystal or ceramic filter's circuit constant and stray capacitance, please get the manufacturer's advice when designing the RESET circuit.

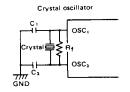

Crystal: 4.194304MHz NC-18C (Nihon Denpa Kogyo)

$R_f$ ;  $1M\Omega \pm 2\%$   $C_1$ :  $22pF \pm 20\%$  $C_2$ :  $22pF \pm 20\%$  C<sub>1</sub>

OSC<sub>1</sub>

Gramic

Rf

OSC<sub>2</sub>

OSC<sub>3</sub>

OSC<sub>3</sub>

Ceramic filter oscillator

Ceramic filter: CSA4.00MG (Murata)

R<sub>f</sub>: 1MΩ|± 2% C<sub>1</sub>: 30pF ± 20% C<sub>2</sub>: 30pF ± 20%

1NT, 1NT, 0 7Vcc - 40H, 41H - 40L, 41L

# ■ CHARACTERISTICS CURVE (REFERENCE DATA)

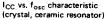

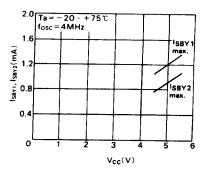

I<sub>SBY</sub> vs. f<sub>osc</sub> characteristics (crystal, ceramic resonator)

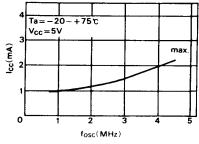

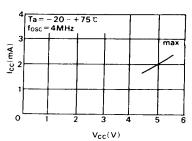

I<sub>CC</sub> vs. V<sub>CC</sub> characteristic (crystal, ceramic resonator)

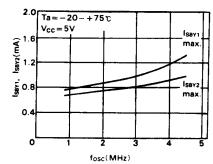

I<sub>SBY</sub> vs. V<sub>CC</sub> characteristics (crystal, ceramic resonator)

# DESCRIPTION OF PIN FUNCTIONS

Input and output signals of MCU are described below.

• GND, V<sub>CC</sub>, V<sub>disp</sub>

These are power supply pins. Connect GND pin to Earth (0V) and apply  $V_{CC}$  power supply voltage to  $V_{CC}$  pin.  $R_{A1}/V_{disp}$  pin is used for  $R_{A1}$  as all high voltage pins are "without pull-down MOS" (PMOS open drain).

# • TEST

TEST pin is not for users application. Connect it to V<sub>CC</sub>.

#### RESET

RESET pin is used to reset MCU. For details, see "RESET".

#### OSC<sub>1</sub>, OSC<sub>2</sub>

These are input pins to the internal clock generator circuit. They can be connected to crystal resonator, ceramic filter resonator, or external oscillator circuit. For details, see "INTERNAL OSCILLATOR CIRCUIT."

### • D-port (Do to D<sub>14</sub>)

D-port is a 1-bit Input/Output common port. Do to D3 are standard type, D4 to D14 are for high voltage. For details, see "INPUT/OUTPUT".

# • R-port (R0 to R4, RA)

R-port is a 4-bit Input/Output port. (only RA is 1-bit construction.) R0 is output port, RA is input port, and R1 to R4 are Input/Output common ports. R0 to R2 and RA are the high voltage ports, R3 to R4 are the standard ports. R32 and R33 are also available as INT0 and INT1, respectively. For details, see "INPUT/OUTPUT".

### • INTo, INT

These are the input pins to interrupt MCU operation externally. INTi can be used as an external event input pin for TIMER-B. INTo and INTi are also available as R32, and R33 respectively. For details, see "INTERRUPT".

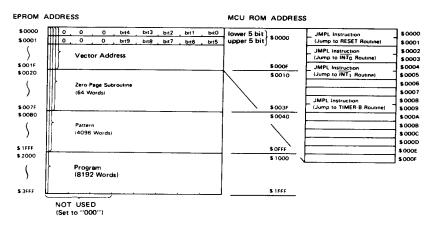

#### ROM MEMORY MAP

ROM memory map is illustrated in Fig. 1 and described in the following paragraph.

#### ◆ Vector Address Area ..... \$0000 to \$000F

When MCU reset or an interrupt is serviced, the program is executed from the vector address. Program the JMPL instructions branching to the starting addresses of reset routine or of interrupt routines.

# • Zero-Page Subroutine Area ..... \$0000 to \$003F

CAL instruction allows to branch to the subroutines in \$0000 to \$003F.

# Pattern Area ..... \$0000 to \$0FFF

P instruction allows referring to the ROM data in \$0000 to \$0FFF as a pattern.

### Program Area ..... \$0000 to \$1FFF

Fig. 1 ROM Memory Map

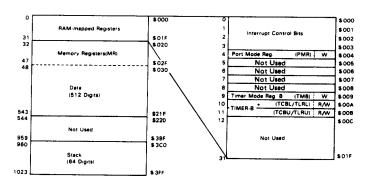

\* Two registers are mapped on same address

R : Read Only W : Write Only R/W : Read/Write

| Timer/Event Counter B Lower (TCBL) | R | Timer Load Reg. Lower (TLRL)  | w | \$ 00A |

|------------------------------------|---|-------------------------------|---|--------|

| Timer/Event Counter B Upper (TCBU) | R | Timer Load Reg. Upper. (TLRU) | w | \$ 00B |

Fig. 2 RAM Memory Map

#### RAM MEMORY MAP

The MCU includes 576 digits x 4 bits RAM as the data area and stack area. In addition to these areas, interrupt control bits

and special registers are also mapped on the RAM memory space. RAM memory map is illustrated in Fig. 2 and described in the following paragraph.

|   | bit 3                            | bit 2                            | bit 1                            | bit 0                            | _     |

|---|----------------------------------|----------------------------------|----------------------------------|----------------------------------|-------|

| 0 | IMO<br>(IM of INT <sub>0</sub> ) | IFO<br>(IF of INT <sub>o</sub> ) | RSP<br>(Reset SP Bit)            | I/E<br>(Interrupt Enable Flag)   | \$000 |

| , | Not Used                         | Not Used                         | IM1<br>(IM of INT <sub>1</sub> ) | IF1<br>(IF of INT <sub>1</sub> ) | \$001 |

| 2 | Not Used                         | Not Used                         | IMTB<br>(IM of TIMER-B)          | IFTB<br>(IF of TIMER-B)          | \$002 |

| 3 | Not Used                         | Not Used                         | Not Used                         | Not Used                         | \$003 |

Interrupt Request Flag

1M Interrupt Mask

(Note)

Interrupt Enable Flag I/E SP

Each bit in Interrupt Control Bits Area is set by SEM/SEMD instruction, is reset by REM/REMD instruction and is tested by TM/TMD instruction. It is not affected by other instructions. Furthermore, Interrupt Request Flag is not affected by SEM/SEMD instruction. The content of Status becomes invarid when "RSP" bit and "Not Used" bit is tested.

# Fig. 3 Configuration of Interrupt Control Bit Area

# Interrupt Control Bit Area ..... \$000 to \$003

This area is used for interrupt controls, and is illustrated in Fig. 3. It is accessable only by RAM bit manipulation instruction. However, the interrupt request flag cannot be set by software. The RSP bit is only used to reset the SP.

# Special Register Area ..... \$004 to \$00B

Special Register is a mode or a data register for the external interrupt, the serial interface, and the timer/counter. These registers are classified into 3 types: Write-only, Read-only, and Read/Write as shown in Fig. 2. These registers cannot be accessed by RAM bit manipulation instruction.

# Data Area ..... \$020 to \$21F

16 digits of \$020 to \$02F are called memory register (MR) and accessable by LAMR and XMRA instructions.

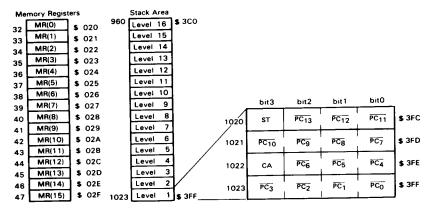

#### Stack Area .... \$3C0 to \$3FF

Stack Area is used for LIFO stacks with the contents of the program counter (PC), status (ST) and carry (CA) when processing subroutine call and interrupt. As 1 level requires 4 digits, this stack area is nested to 16 level-stack max. The data pushed in the stack and LIFO stack state are provided in Fig. 4. The program counter is restored by RTN and RTNI instructions. Status and Carry are restored only by RTNI instruction, and not affected by RTN instruction. The area, not used for stacking, is available as a data area.

PC<sub>13</sub> to PC<sub>0</sub>; Program Counter

ST; Status CA; Carry

Fig. 4 Configuration of Memory Register, Stack Area and Stack Position

#### ■ REGISTER AND FLAG

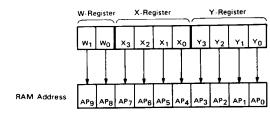

The MCU has nine registers and two flags for the CPU operations. They are illustrated in Fig. 5 and described in the following paragraphs.

#### · Accumulator (A), B Register (B)

Accumulator and B Register are 4-bit registers used to hold the results of Arithmetic Logic Unit (ALU), and to transfer data to/from memories, I/O and other registers.

#### W Register (W), X Register (X), Y Register (Y)

W Register is 2-bit, and X and Y Register are 4-bit registers used for indirect addressing of RAM. Y Register is also used for D-port addressing. W Register is write-only and cannot be read.

#### SPX Register (SPX), SPY Register (SPY)

SPX and SPY Register are 4-bit registers used to assist X and Y Register respectively.

#### • Carry (CA)

Carry (CA) stores the overflow of ALU generated by the arithmetic operation. It is also affected by SEC, REC, ROTL and ROTR instructions.

During interrupt servicing, Carry is pushed onto the stack and restored back from the stack by RTNI instruction. (It's not affected by RTN instruction.)

#### Status (ST)

Status (ST) holds the ALU overflow. ALU non-zero and the results of bit test instruction for the arithmetic or compare instruction. It is used for a branch condition of BR, BRL, CAL or CALL instructions. The value of the Status remains unchanged until the next arithmetic, compare or bit test instruction is executed. Status becomes "1" after the BR, BRL, CAL or CALL instruction has been executed (irrespective of its execution/skip). During the interrupt servicing, Status is pushed onto the

Accomplation

Accomplation

B Report

W Mag Str.

W Mag Str.

W Mag Str.

stack and restored back from the stack by RTNI instruction. (It's not affected by RTN instruction.)

#### • Program Counter (PC)

Program Counter is a 14-bit binary counter for ROM addressing.

#### Stack Pointer (SP)

Stack Pointer is used to point the address of the next stacking area up to 16 levels.

The Stack Pointer is initialized to locate \$3FF on the RAM address, and is decremented by 4 as data pushed into the stack, and incremented by 4 as data restored back from the stack.

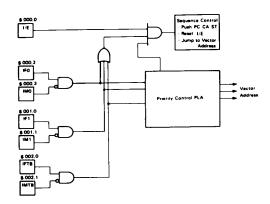

#### INTERRUPT

The MCU can be interrupted by three different sources: the external signals  $(\overline{INT_0},\overline{INT_1})$  and timer/counter (TIMER-B). In each sources, the Interrupt Request Flag, Interrupt Mask and interrupt vector address will be used to control and maintain the interrupt request. The Interrupt Enable Flag is also used to control the total interrupt operations.

#### Interrupt Control Bit and Interrupt Service

The interrupt control bit is mapped on \$000 to \$003 of the RAM address and accessable by RAM bit manipulation instruction. (The Interrupt Request Flag (IF) cannot be set by software.) The Interrupt Enable Flag (I/E) and Interrupt Request Flag (IF) are set to "0", and the Interrupt Mask (IM) is set to "1" at the initialization by MCU reset.

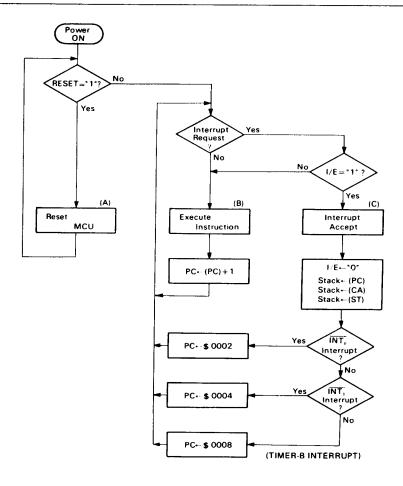

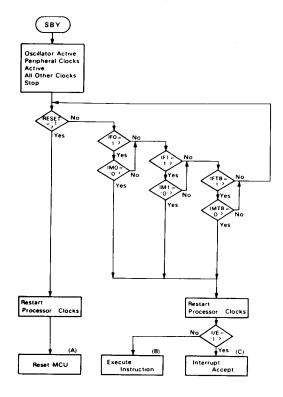

Fig. 6 shows the interrupt block diagram. Table 1 shows the interrupt priority and vector addresses, and Table 2 shows the conditions that the interrupt service is executed by any one of the three interrupt sources.

The interrupt request is generated when the Interrupt Request Flag is set to "1" and the Interrupt Mask is "0". If the Interrupt Enable Flag is "1", then the interrupt will be activated and vector addresses will be generated from the priority PLA corresponding to the three interrupt sources.

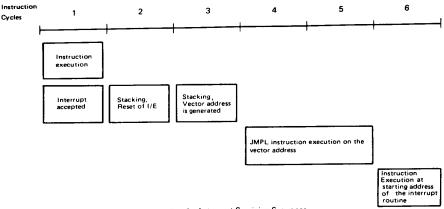

Fig. 7 shows the interrupt services flowchart, and Fig. 8 shows the interrupt sequence. If the interrupt is requested, the instruction finishes its execution in the first cycle. The Interrupt Enable Flag is reset in the second cycle. In the second and third cycles, the Carry, Status and Program Counter are pushed onto the stack. In the third cycle, the instruction is executed again after jumping to the vector address.

In each vector address, program JMPL instruction to branch to a starting address of the interrupt routine. The Interrupt Request Flag which caused the interrupt service has to be reset by software in the interrupt routine.

Fig. 6 Interrupt Circuit Block Diagram

Table 1. Vector Addresses and Interrupt Priority

| Reset - Interrupt | Priority | Vector addresses |

|-------------------|----------|------------------|

| RESET             | -        | \$0000           |

| INTo              | 1        | \$0002           |

| INT               | 2        | \$0004           |

| TIMER-B           | 3        | \$0008           |

Table 2. Conditions of Interrupt Service

| Interrupt Interrupt source control bits | ĪNT <sub>o</sub> | ĪNT <sub>1</sub> | TIMER-B |

|-----------------------------------------|------------------|------------------|---------|

| I/E                                     | 1                | 1                | 1       |

| IFO-IMO                                 | 1                | 0                | 0       |

| IF1 · IM1                               | *                | 1                | 0       |

| IFTB · IMTB                             | *                | *                | 1       |

• Don't care

Fig. 7 Interrupt Servicing Flowchart

Fig. 8 Interrupt Servicing Sequence

# • Interrupt Enable Flag (I/E: \$000,0)

The Interrupt Enable Flag controls enable/disable of all interrupt requests as shown in Table 3. The Interrupt Enable Flag is reset by the interrupt servicing and set by RTNI instruction.

Table 3. Interrupt Enable Flag

| Interrupt Enable Flag | Interrupt Enable/Disable |

|-----------------------|--------------------------|

| 0                     | Disable                  |

| 1,                    | Enable                   |

# External Interrupt (INT<sub>0</sub>, INT<sub>1</sub>)

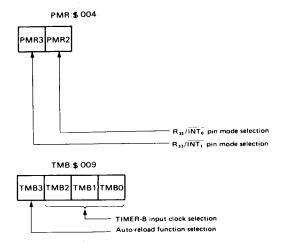

To use external interrupt, select R<sub>32</sub>/INT<sub>0</sub>, R<sub>33</sub>/INT<sub>1</sub> port for INT<sub>0</sub>, INT<sub>1</sub> mode by setting the Port Mode Register (PMR:

The External Interrupt Request Flags (IFO, IF1) are set at the falling edge of INT<sub>0</sub>, INT<sub>1</sub> inputs.

INT, input can be used as a clock signal input of TIMER-B. Then, TIMER-B counts up at each falling edge of input. When using INT, as TIMER-B external event, an External Interrupt Mask (IMI) has to be set so that the interrupt request by INT; will not be accepted.

- External Interrupt Request Flag (IFO: \$000,2, IF1: \$001,0)

The External Interrupt Request Flags (IFO, IFI) are set at the falling edges of INT<sub>0</sub>, INT<sub>1</sub> inputs respectively.

- External Interrupt Mask (IMO: \$000,3, IM1: \$001,1)

The External Interrupt Mask is used to mask the external interrupt requests.

Table 4. External Interrupt Request Flag

| External Interrupt Request Flags | Interrupt Requests |

|----------------------------------|--------------------|

| 0                                | No                 |

| 1                                | Yes                |

Table 5. External Interrupt Mask

| External Interrupt Masks | Interrupt Requests |

|--------------------------|--------------------|

| 0                        | Enable             |

| 1                        | Disable (masks)    |

# Port Mode Register (PMR: \$004)

Ther Port Mode Register is a 2-bit write-only register which controls the  $R_{32}/\overline{INT_0}$  pin and  $R_{33}/\overline{INT_1}$  pin as shown in Table 6. The Port Mode Register will be initialized to \$0 by MCU reset, so that all these pins are set to a port mode.

Table 6. Port Mode Register

| PMR               | R <sub>33</sub> /INT <sub>1</sub> pin                                                |  |  |  |

|-------------------|--------------------------------------------------------------------------------------|--|--|--|

| bit 3             | n <sub>33</sub> /(NT <sub>1</sub> pin                                                |  |  |  |

| 0                 | Used as R <sub>33</sub> port input/output pin                                        |  |  |  |

| 1                 | Used as INT <sub>1</sub> input pin                                                   |  |  |  |

|                   |                                                                                      |  |  |  |

|                   | R <sub>22</sub> /INT <sub>0</sub> pin                                                |  |  |  |

| PMH               | R <sub>22</sub> /INT <sub>0</sub> pin                                                |  |  |  |

|                   | $R_{32}/\overline{INT_0}$ pin                                                        |  |  |  |

| PMR<br>bit 2<br>0 | R <sub>32</sub> /INT <sub>0</sub> pin  Used as R <sub>32</sub> port input/output pin |  |  |  |

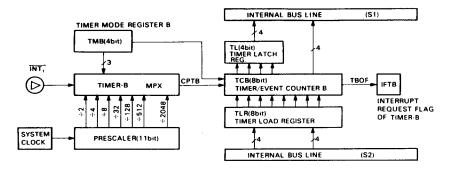

Fig. 9 Timer/Counter Block Diagram

#### - TIMER

The MCU contains a prescaler and timer/counter (TIMER-B), Fig. 9 shows the block diagram. The prescaler is an 11-bit binary counter which has same function with the HMCS412C. TIMER-B is an 8-bit auto-reload timer/counter which has same function with the HMCS412C.

#### Prescaler

The input to the prescaler is a system clock signal. The prescaler is initialized to \$000 by MCU reset, and the prescaler starts to count up the system clock signal as soon as RESET input goes to logic "0". The prescaler keeps counting up except MCU reset and stop mode. The prescaler provides clock signals to TIMER-B. The prescaler divide ratio of the clock signals are selected according to the content of the mode registers such as — Timer Mode Register B (TMB).

#### • TIMER-B Operation

Timer Mode Register B (TMB: \$009) is used to select the auto-reload function and the prescaler divide ratio of TIMER-B as the input clock source. When the external event input is used as an input clock signal to TIMER-B, select the  $R_{33}/INT_1$  as  $\overline{INT_1}$  and set the External Interrupt Mask (IMI) to "1" to

prevent the external interrupt request from occurring.

TIMER-B is initialized according to the value written into the Timer Load Register by software. TIMER-B counts up at every clock input signal. When the next clock signal is applied to TIMER-B after TIMER-B is set to \$FF, TIMER-B will be initialized again and generate overflow output. In this case if the auto-reload function is selected, TIMER-B is initialized according to the value of the Timer Load Register. Else if the auto-reload function is not selected, TIMER-B goes to \$00. TIMER-B Interrupt Request Flag (IFTB: \$002,0) will be set at this overflow output.

#### • Timer Mode Register B (TMB: \$009)

The Timer Mode Register B is a 4-bit write-only register. The Timer Mode Register B controls the selection for the autoreload function of TIMER-B and the prescaler divide ratio, and the source of the clock input signal, as shown in Table 7.

The Timer Mode Register B is initialized to \$00 by MCU reset.

The operation mode of TIMER-B is changed at the second instruction cycle after writing into the Timer Mode Register B.

Therefore, it is necessary to program the write instruction to TLRU after the content of TMB is changed.

Table 7 Timer Mode Register B

| тмв   | Auto-reload Function |

|-------|----------------------|

| Bit 3 | Auto-reload runction |

| 0     | No                   |

| 1     | Yes                  |

| тмв   |       |       | Prescaler Divide Ratio,     |  |  |  |

|-------|-------|-------|-----------------------------|--|--|--|

| Bit 2 | Bit 1 | Bit 0 | Clock Input Source          |  |  |  |

| 0     | 0     | 0     | ÷2048                       |  |  |  |

| 0     | 0     | 1     | ÷ 512                       |  |  |  |

| 0     | 1     | 0     | ÷ 128                       |  |  |  |

| 0     | 1     | 1     | ÷ 32                        |  |  |  |

| 1     | 0     | 0     | ÷ 8                         |  |  |  |

| 1     | 0     | 1     | ÷ 4                         |  |  |  |

| 1     | 1     | 0     | ÷ 2                         |  |  |  |

| 1     | 1     | 1     | INT; (External Event Input) |  |  |  |

# • TIMER-B (TCBL: \$00A, TCBU: \$00B)

TIMER-B consists of an 8-bit write-only Timer Load Register, and an 8-bit read-only Timer/Event Counter. Each of them has a low-order digit (TCBL: \$00A, TLRL: \$00A) and a high-order digit (TCBU: \$00B, TLRU: \$00B).

The Timer/Event Counter can be initialized by writing data into the Timer Load Register. In this case, write the low-order digit first, and then the high-order digit. The Timer/Event Counter is initialized at the time when the high-order digit is written. The Timer Load Register will be initialized to \$00 by the MCU reset.

The counter value of TIMER-B can be obtained by reading the Timer/Event Counter. In this case, read the high-order digit first, and then the low-order digit. The count value of low-order digit is latched at the time when the high-order digit is read.

# TIMER-B Interrupt Request Flag (IFTB: \$002, 0)

The TIMER-B Interrupt Request Flag is set by the overflow output of TIMER-B.

# • TIMER-B Interrupt Mask (IMTB: \$002, 1)

TIMER-B Interrupt Mask prevents an interrupt request generated by TIMER-B Interrupt Request Flag.

Fig. 10 Mode Register Configuration and Function

Table 8. TIMER-B Interrupt Request Flag

| TIMER-B Interrupt<br>Request Flag | Interrupt Request |

|-----------------------------------|-------------------|

| 0                                 | No                |

| 1                                 | Yes               |

Table 9. TIMER-B Interrupt Mask

| TIMER-B Interrupt<br>Mask | Interrupt Request |

|---------------------------|-------------------|

| 0                         | Enable            |

| 1                         | Disable (Mask)    |

#### INPUT/OUTPUT

The MCU provides 36 Input/Output pins, and they are consist of 12 standard pins of "Without pull-up MOS (NMOS open drain)" and 24 high voltage pins of "Without pull-down MOS (PMOS open drain)".

When any input/output common pin is used as input pin, it is necessary to set the output data as shown in Table 10.

Table 10 Data Input from Input/Output Common Pins

| Table 10 Bate input from input Gatpat Common Fins               |                                   |  |  |  |

|-----------------------------------------------------------------|-----------------------------------|--|--|--|

| I/O circuit type                                                | Available pin condition for input |  |  |  |

| For Standard pins "Without pull-up MOS (NMOS open drain)"       | "1"                               |  |  |  |

| For High voltage pins "Without pull-down MOS (PMOS open drain)" | ′′0′′                             |  |  |  |

Table 11 I/O Pin Circuit Forms

|                       | Without pull-up MOS<br>(NMOS open drain) | Applied pins                      |

|-----------------------|------------------------------------------|-----------------------------------|

| I/O<br>common<br>pins | HLT on input data                        | Do ~D3,<br>R30 ~R33,<br>R40 ~R43  |

| Input<br>oins         | input data                               | INT <sub>o</sub> INT <sub>1</sub> |

| <br>                  |                                          | (Continued                        |

(Note) In the stop mode, HLT signal is "0", HLT signal is "1" and I/O pins are in high impedance.

### D-port

D-port is 1-bit I/O port, and it has 15 Input/Output common pins. It can be set/reset by the SED/RED and SEDD/REDD

instructions, and can be tested by the TD and TDD instructions. Table 11 shows the classification of standard pins, high voltage pins and the Input/Output pins circuit types.

#### R-port

R-port is 4-bit I/O port. It provides 16 input/output common pins, 4 output-only pins, and 1 input-only pin. Data input is processed using the LAR and LBR instructions and data output is processed using the LRA and LRB instructions. The MCU will not be affected by writing into the input-only and/or non-existing ports, invalid data will be read by reading from the output-only and/or non-existing ports.

The R<sub>32</sub> and R<sub>33</sub> pins are also used as the INT<sub>0</sub> and INT<sub>1</sub> pins respectively. Table 11 shows the classification of standard

pins, high voltage pins and Input/Output pins circuit types.

#### - DECET

The MCU is reset by setting RESET pin to "1". At power ON or recovering from stop mode, apply RESET input more than t<sub>RC</sub> to obtain the necessary time for oscillator stabilization. In other cases, the MCU reset requires at least two instructions cycle time of RESET input.

Table 12 shows initialized items by MCU reset and each status after reset.

Table 12 MCU Initial Value by Reset

|                                           | Items               |                              | Initial value by<br>MCU reset                | Contents                                              |  |

|-------------------------------------------|---------------------|------------------------------|----------------------------------------------|-------------------------------------------------------|--|

| Program counter (PC) Status (ST)          |                     | \$0000                       | Execute program from the top of ROM address. |                                                       |  |

|                                           |                     |                              | "1"                                          | Enable to branch with conditional branch instructions |  |

| Stack pointer (S                          |                     |                              | \$3FF                                        | Stack level is 0.                                     |  |

|                                           |                     | Standard pin Without pull-up | "1"                                          | Enable to input.                                      |  |

| register High v                           | High voltage<br>pin | Without pull-down            | "0"                                          | Enable to input.                                      |  |

| Interrupt Enable Flag (I/E)               |                     | "0"                          | Inhibit all interrupts.                      |                                                       |  |

| Interrupt flag                            | Interrupt Rec       | Interrupt Request Flag (IF)  |                                              | No interrupt request.                                 |  |

|                                           | Interrupt Ma        | Interrupt Mask (IM)          |                                              | Mask interrupt request.                               |  |

|                                           | _ <del></del>       | egister (PMR)                | "0000"                                       | See Item "Port Mode Register".                        |  |

| Mode register Timer Mode Register B (TMB) |                     | "0000"                       | See Item "Timer Mode Register B".            |                                                       |  |

|                                           | Prescaler           |                              |                                              |                                                       |  |

| Timer/Counter                             |                     | Timer/Event Counter B (TCB)  |                                              | _                                                     |  |

|                                           |                     | Register (TLR)               | \$00                                         |                                                       |  |

(Note) The values of registers and flags which are not described on above table will become as follows.

| Item                                                                                                   |  | After releasing stop mode<br>by MCU Reset                                                                     | After MCU Reset except the left                                                                             |  |

|--------------------------------------------------------------------------------------------------------|--|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| Carry (CA) Accumulator (A) B register (B) W register (W) X/SPX register (X/SPX) Y/SPY register (Y/SPY) |  | The value immediately before MCU reset is not guaranteed. Initialization by the program should be required.   | The value immediately before MCU Reset is not guaranteed. Initialization by the program should be required. |  |

| RAM                                                                                                    |  | The value immediately before MCU reset (the value immediately before executing stop instruction) is retained. | – ditto –                                                                                                   |  |

#### ■ INTERNAL OSCILLATOR CIRCUIT

Fig. 11 gives internal oscillator circuit. The oscillator type can be selected from the followings; crystal resonator, or ceramic

filter resonator as shown in Table 13. In any cases, external clock operation is available.

Fig. 11 Internal Oscillator Circuit

Table 13 Oscillator Circuit Example

|                          | Circuit configuration                                  | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External clock operation | Oscillator OSC, Open — OSC,                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Ceramic filter resonator | C1 OSC1 Ceramic SR, OSC2 GND                           | $\label{eq:continuous} \begin{array}{ll} \text{Ceramic filter: CSA 4.00MG (Murata)} \\ \text{Rf:} & 1\text{M}\Omega \pm 2\text{\%} \\ \text{C}_1: & 30\text{pF} \pm 20\text{\%} \\ \text{C}_2: & 30\text{pF} \pm 20\text{\%} \\ \\ \text{Ceramic filter: CSA 6.00MG (Murata)} \\ \text{Rf:} & 1\text{M}\Omega \pm 2\text{\%} \\ \text{C}_1: & 30\text{pF} \pm 20\text{\%} \\ \text{C}_2: & 30\text{pF} \pm 20\text{\%} \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Crystal<br>resonator     | Crystal R, Crystal Crystal OSC2 GND                    | $ \begin{array}{lll} & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ $ |

|                          | ATcut parallel resonance crystal  C1 Rs  OSC1 OSC2  C0 | Crystal: A T cut parallel resonance crystal $C_0$ : 7 pF max. $R_s$ : $100\Omega$ max. f: $2.0 \sim 4.5 MHz$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

(Note 1) On the crystal and ceramic filter resonator, the upper circuit parameters are the one recommended by crystal or ceramic filter maker. The circuit parameters are changed by crystal, ceramic filter resonator and the floated capacitance in designing the board. In employing the resonator, please consult with the engineers of crystal or ceramic filter maker to determine the circuit parameter.

(Note 2) Wiring among OSC<sub>1</sub>, OSC<sub>2</sub> and elements should be as short as possible, and never cross the other wirings. Refer to the layout of crystal and ceramic filter.

Fig. 12 Layout of Crystal and Ceramic Filter

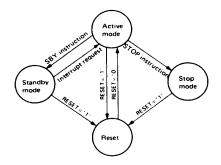

# . LOW POWER DISSIPATION MODE

The MCU provides two low power dissipation modes, that is, a Standby mode and a Stop mode. Table 14 shows the function of the low power dissipation mode, and Fig. 13 shows the diagram of the mode transition.

Table 14 Low Power Dissipation Mode Function

| Low Power<br>Dissipation Mode |             | Condition             |                       |                   |                       |          |                         |                   |                                   |

|-------------------------------|-------------|-----------------------|-----------------------|-------------------|-----------------------|----------|-------------------------|-------------------|-----------------------------------|

|                               | Instruction | Oscillator<br>circuit | Instruction execution | Register,<br>Flag | Interrupt<br>function | RAM      | Input/<br>Output<br>pin | Timer/<br>Counter | Recovering method                 |

| Standby mode                  | SBY         | Active                | Stop                  | Retained          | Active                | Retained | Retained*2)             | Active            | RESET Input,<br>Interrupt request |

| Stop mode                     | STOP        | Stop                  | Stop                  | RESET 1)          | Stop                  | Retained | High impedance          | Stop              | RESET Input                       |

1) As the MCU recovers from STOP mode by RESET input, the contents of the flags and registers are initialized according to Table 12.

\*2) As a I/O circuit is active, a I/O current possibly flows according the state of I/O pin. This is the additional current to the current dissipation in Standby Mode (ISBY1, ISBY2).

Fig. 13 MCU Operation Mode Transition

#### Standby Mode

The SBY instruction puts the MCU into the Standby mode. In the Standby mode, the oscillator circuit is active and timer/ counter continues working. On the other hand, the CPU stops since the clock related to the instruction execution stops. Registers, RAM and Input/Output pins retain the state they had just before going into the Standby mode.

The Standby mode is canceled by the MCU reset or interrupt request. When canceled by the interrupt request, the MCU becomes an active mode and executes the instruction next to the SBY instruction. At this time, if the Interrupt Enable Flag is "1", the interrupt is executed. If the Interrupt Enable Flag is "0", the interrupt request is held on and the normal instruction execution continues.

Fig. 14 shows the flowchart of the Standby Mode.

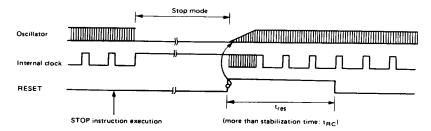

#### Stop Mode

The STOP instruction brings the MCU into the Stop mode. In this mode the oscillator circuit and every function of the

The Stop mode is canceled by the MCU reset. At this time, as shown in Fig. 15, apply the RESET input for more than tRC to get enough oscillator stabilization time. (Refer to the "AC CHARACTERISTICS".) After the Stop mode is canceled, RAM retains the state it had just before going into the Stop mode after releasing stop mode by MCU reset, the values of the B register, W register, X/SPX register, Y/SPY register, carry and serial data register are not guaranteed.

Fig. 14 MCU Operating Flowchart

Fig. 15 Stop Mode Cancel Timing Chart

# ■ RAM ADDRESSING MODE

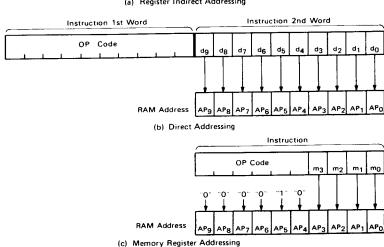

As shown in Fig. 16, the MCU provides three RAM addressing modes; Register Indirect Addressing, Direct Addressing and Memory Register Addressing.

# Register Indirect Addressing

The combined 10-bit contents of W Register, X Register and Y Register is used as the RAM address in this mode.

#### Direct Addressing

The direct addressing instruction consists of two words and the second word (10 bits) following Op-code (the first word) is used as the RAM address.

# Memory Register Addressing

The Memory Register Addressing can access 16 digits (Memory Register: MR) from \$020 to \$02F by using the LAMR and XMRA instruction.

(a) Register Indirect Addressing

Fig. 16 RAM Addressing Mode

### ■ ROM ADDRESSING MODE AND P INSTRUCTION

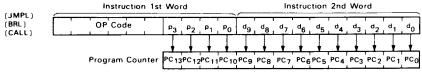

The MCU has four kinds of ROM addressing modes as shown in Fig. 17.

#### Direct Addressing Mode

The program can branch to any addresses in the ROM memory space by using JMPL. BRL or CALL instruction. These instructions replace 14-bit program counter (PC13 to PC0) with 14-bit immediate data.

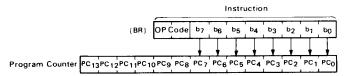

#### Current Page Addressing Mode

ROM memory space is divided into 256 words in each page starting from \$0000. The program branches to the address in the same page using BR instruction. This instruction replace the low-order eight bits of program counter (PC7 to PC0) with 8-bit immediate data. The branch destination by BR instruction on the boundary between pages is given in Fig. 19.

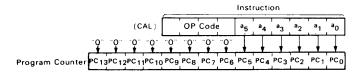

#### Zero Page Addressing Mode

The program branches to the zero page subroutine area, which is located on the address from \$0000 to \$003F, using CAL instruction. When CAL instruction is executed, 6-bit immediate data is placed in low-order six bits of program counter (PC5 to PC0) and "0's" are placed in high-order eight bits (PC13 to PC6).

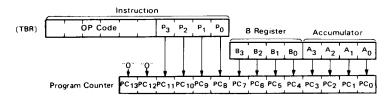

#### Table Data Addressing

The program branches to the address determined by the contents of the 4-bit immediate data, accumulator and B register, using TBR instruction.

#### (a) Direct Addressing

#### (b) Current Page Addressing

#### (c) Zero Page Addressing

(d) Table Data Addressing

Fig. 17 ROM Addressing Mode

(a) Address Designation

Fig. 18 P Instruction

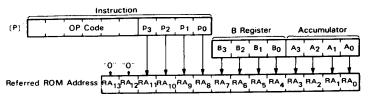

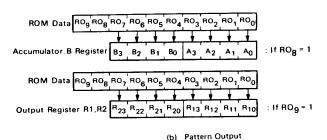

#### P Instruction

The P instruction refers ROM data addressed by Table Data Addressing. ROM data addressed also determine its destination. When bit 8 in referred ROM data is "1", 8 bits of referred ROM

Fig. 19 The Branch Destination by BR Instruction on the Boundary between Pages

data are written into the accumulator and B Register. When bit 9 is "1", 8 bits of referred ROM data are written into the R1 and R2 port output register. When both bit 8 and 9 are "1", ROM data are written into the accummulator and B Register and also to the R1 and R2 port output register at a same time.

The P instruction has no effect on the program counter.

#### Description of the Branch Destination on Page Boundary.

When BR is on page boundary (256n+255), BR instruction transfers the contents of PC to the next page with hardware architecture. Therefore, the program branches to the next page when using BR on page boundary. The HMCS400 series cross macro assembler has automatic paging facility for ROM page.

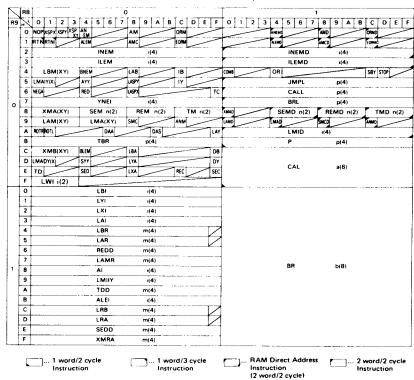

#### **\* INSTRUCTION SET**

The HD614P180 provides 98 instructions. These instructions are classified into 10 groups as follows;

- (1) Immediate Instruction

- (2) Register-to-Register Instruction

- (3) RAM Address Instruction(4) RAM Register Instruction

- (5) Arithmetic Instruction

- (6) Compare Instruction

- (7) RAM Bit Manipulation Instruction

- (8) ROM Address Instruction

- (9) Input/Output Instruction

- (10) Control Instruction

Table 15. Immediate Instruction

| OPERATION                               | MNEMONIC | OPERATION CODE                                           | FUNCTION            | STATUS | CYCLE |

|-----------------------------------------|----------|----------------------------------------------------------|---------------------|--------|-------|

| Load A from Immediate                   | LAI i    | 100011 i3 i2 i1 i0                                       | iA                  |        | 1/1   |

| Load B from Immediate                   | LBI i    | 10000013121110                                           | iB                  |        | 1/1   |

| Load Memory from Immediate              | LMID i,d | 0 1 1 0 1 0 i3 iz i1 i0<br>de de dr de ds d4 d3 d2 d1 do | ⊢⊸M                 |        | 2/2   |

| Load Memory from Immediate, Increment Y | ĹMIIY i  | 101001 i3 i2 i1 i0                                       | i-+ <b>M</b> ,Y+1→Y | NZ     | 1/1   |

Table 16. Register-to-Register Instruction

| OPERATION         | MNEMONIC |   |   | OP | ER | ATI | ON | С | OD | E  |     | FUNCTION | STATUS | CYCL |

|-------------------|----------|---|---|----|----|-----|----|---|----|----|-----|----------|--------|------|

| Load A from B     | LAB      | 0 | 0 | 0  | 1  | 0   | 0  | 1 | 0  | C  | 0   | B→A      |        | 1/1  |

| Load B from A     | LBA      | 0 | 0 | 1  | 1  | 0   | ō  | 1 | 0  | C  | 0   | A→B      |        | 1/1  |

| Load A from Y     | LAY      | 0 | 0 | 1  | 0  | 1   | 0  | 1 | 1  | 1  | 1   | Y⊸A      |        | 1/1  |

| Load A from SPX   | LASPX    | 0 | 0 | 0  | 1  | 1   | 0  | 1 | 0  | C  | 0   | SPX→A    |        | 1 1  |

| Load A from SPY   | LASPY    | 0 | 0 | 0  | 1  | 0   | 1  | 1 | 0  | С  | 0   | SPY⊸A    |        | 1 1  |

| Load A from MR    | LAMR m   | 1 | 0 | 0  | 1  | 1   | 1  | m | 3M | 2m | ımo | MR(m) →A |        | 1/1  |

| Exchange MR and A | XMRA m   | 1 | 0 | 1  | 1  | 1   | 1  | m | эm | 2m | ımo | MR(m)++A |        | 1/1  |

Table 17. RAM Address Instruction

| OPERATION                    | MNEMONIC | OPERATION CODE     | FUNCTION  | STATUS | WORD  |  |

|------------------------------|----------|--------------------|-----------|--------|-------|--|

| Load W from Immediate        | LWI i    | 00111100i,io       | ⊢→W       |        | 1/1   |  |

| Load X from Immediate        | LXI i    | 100010 i3 i2 i1 i0 | i—x       |        | 1/1   |  |

| Load Y from Immediate        | LYI i    | 100001 is iz is io | iY        |        | 1/1   |  |

| Load X from A                | LXA      | 0011101000         | AX        |        | 1/1   |  |

| Load Y from A                | LYA      | 0011011000         | A—→Y      |        | 1/1   |  |

| Increment Y                  | IY       | 0001011100         | Y+1→Y     | NZ     | 1,/1  |  |

| Decrement Y                  | DY       | 0011011111         | Y – 1 → Y | NB     | 1/1   |  |

| Add A to Y                   | AYY      | 0001010100         | Y + A-•Y  | OVF    | 1/1   |  |

| Subtract A from Y            | SYY      | 0011010100         | Y A Y     | NB     | 1/1   |  |

| Exchange X and SPX           | XSPX     | 0000000001         | X++SPX    |        | 1 1   |  |

| Exchange Y and SPY           | XSPY     | 0000000010         | Y⊷SPY     |        | 1/1   |  |

| Exchange X and SPX,Y and SPY | XSPXY    | 0000000011         | XSPX,YSPY |        | 1 / 1 |  |

Table 18. RAM Register Instruction

|          |                                                                  |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | WORD                        |