TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# T6C96A

#### Overview

The T6C96A is an advanced-function 4-bit single-chip microcontroller that integrates ROM, work RAM, I/O ports, timers and LCD driver, etc., into one chip. The T6C96A features low power consumption.

### Features

- ROM: 4096 words (1 words = 14 bit)

- Work RAM: 1024 bits (16 × 16 × 4 bit)

- Subroutine nesting level: 4 levels

- Timers: 500 ms·125 ms·31.25 ms (× 1ch each)

- IN ports: 4 bit

- IO ports: 8 bit

- IO ports for data: 1 bit (tristate I/O)

- O ports: 4 bit

- Output ports for clock: 1 bit (high-speed clock output pins)

- Output port

- External device control pin: None

- Display types: 24-segment × 4 common

1/4 duty, 1/3 pre-bias

• Minimum instruction execution time: 2.23 µs (High-speed clock 3.58 MHz)

244 µs (Low-speed clock 32.768 kHz)

• Power-saving functions: High-speed operation mode

Low-speed operation mode STOP mode OFF mode

### **Pin Functions**

| Pin name                       | I/O | Function                                             | Circuit configuration | Initial |

|--------------------------------|-----|------------------------------------------------------|-----------------------|---------|

| IN11~IN14                      | IN  | 4-bit input ports                                    |                       | Н       |

| IO11                           | Ю   | I/O ports with output latch<br>3-state output buffer | O21<br>O21            | L       |

| 1012                           | Ю   | I/O ports with output port                           | P < N                 | Н       |

| IO13~IO14<br>IO21~IO24<br>IO31 | Ю   | I/O ports with output latch                          | P < N                 | L       |

| 011~014                        | 0   | Output port with latch                               | push pull output      | L       |

| Pin name                            | I/O             | Function                                                                                                               | Circuit configuration | Initial |

|-------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------|-----------------------|---------|

| HCLK                                | 0               | Output the inverted waveform of<br>the high-speed clock or the<br>waveform of the high-speed<br>clock divided in harf. | Push-pull output      | L       |

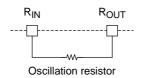

| R <sub>IN</sub><br>R <sub>OUT</sub> | IN<br>O         | Terminals for connecting<br>oscillation resistor for<br>high-speed clock oscillator                                    | _                     | _       |

| /AC                                 | IN              | System reset terminal                                                                                                  |                       | н       |

| TS1~TS3                             | IN              | Used by Toshiba for shipping<br>test. Fix the level of this terminal<br>"L".                                           |                       | L       |

| V <sub>DD</sub><br>V <sub>SS</sub>  | Power<br>supply | 4.5 V~5.5 V<br>0 V (GND)                                                                                               | _                     | _       |

| S <sub>1</sub> ~S <sub>24</sub>     | 0               | Segment signal output terminal                                                                                         |                       | (*)     |

| C <sub>1</sub> ~C <sub>4</sub>      | 0               | Common signal output terminal                                                                                          |                       | (*)     |

Total 54 pin

P: P-ch Tr output ability N: N-ch Tr output ability (\*) High level when display is OFF

## **Pad Assignment**

## **Block Diagram**

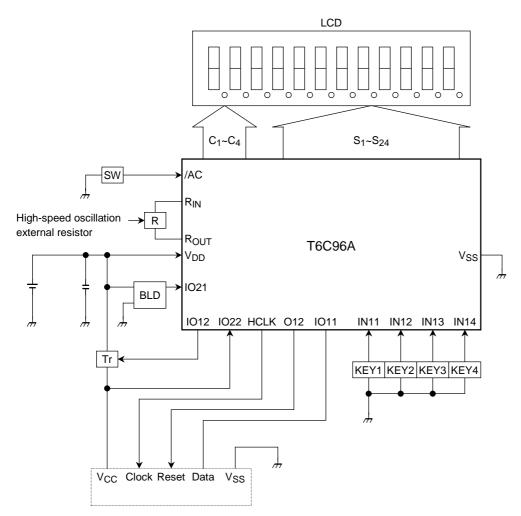

## Example of T6C96A IC Card Reader System

Use of an external BLD allows you to monitor the IC card's supply voltage of T6C96A. IO11 is 3-state type so as to use it as data line. HCLK is a supply control terminal from the driver to the IC card.

## **Internal CPU Functions**

### Program Memory (ROM)

Instruction codes are stored in the program memory. The instruction next in line to be executed is read from the address indicated by the content of the program counter. Each word in program memory consists of 14 bits, and each instruction consists of one word.

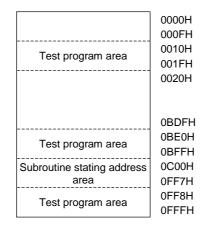

Figure 1 shows the program memory map.

### Figure 1 Program Memory Map

When creating a user program, note that a specific area is occupied by the test program used by Toshiba for its shipping tests.

## **Test Program**

The T6C96A requires the following test programs to be included with user programs. Note that the following test program areas are not available to users.

| address | object |      |      |       |

|---------|--------|------|------|-------|

|         |        |      | ORG  | 0BE0H |

| 0BE0    | 091E   |      | OIB1 | 14    |

| 0BE1    | 092F   |      | OIB2 | 15    |

| 0BE2    | 093C   |      | OIB3 | 12    |

| 0BE3    | 094D   |      | OTB1 | 13    |

| 0BE4    | 095A   |      | OTB2 | 10    |

| 0BE5    | 096B   |      | OTB3 | 11    |

| 0BE6    | 0030   | ROM1 | ROM  |       |

| 0BE7    | 0000   |      | NOP  |       |

| 0BE8    | 0001   |      | CAR  |       |

| 0BE9    | 3BF6   |      | JUMP | ROM2  |

| 0BEA    | 0914   |      | OIB1 | 4     |

| 0BEB    | 0925   |      | OIB2 | 5     |

| 0BEC    | 0932   |      | OIB3 | 2     |

| 0BED    | 0943   |      | OTB1 | 3     |

| 0BEE    | 0950   |      | OTB2 | 0     |

| 0BEF    | 0961   |      | OTB3 | 1     |

| 0BF0    | 095F   |      | OTB2 | 15    |

| 0BF1    | 093D   |      | OIB3 | 13    |

| 0BF2    | 096E   |      | OTB3 | 14    |

| 0BF3    | 091B   |      | OIB1 | 11    |

| 0BF4    | 094C   |      | OTB1 | 12    |

| 0BF5    | 0955   |      | OTB2 | 5     |

| 0BF6    | 0030   | ROM2 | ROM  |       |

| 0BF7    | 0000   |      | NOP  |       |

| 0BF8    | 0011   |      | CAS  |       |

| 0BF9    | 3BE6   |      | JUMP | ROM1  |

| 0BFA    | 092A   |      | OIB2 | 10    |

| 0BFB    | 0933   |      | OIB3 | 3     |

| 0BFC    | 0964   |      | OTB3 | 4     |

| 0BFD    | 0911   |      | OIB1 | 1     |

| 0BFE    | 0942   |      | OTB1 | 2     |

| 0BFF    | 0920   |      | OIB2 | 0     |

| address | object |     |       |

|---------|--------|-----|-------|

|         |        | ORG | 0010H |

| 0010    | 0000   | NOP |       |

| 0011    | 0000   | NOP |       |

| 0012    | 0000   | NOP |       |

| 0013    | 0000   | NOP |       |

| 0014    | 0000   | NOP |       |

| 0015    | 0000   | NOP |       |

| 0016    | 0000   | NOP |       |

| 0017    | 0000   | NOP |       |

| 0018    | 0000   | NOP |       |

| 0019    | 0000   | NOP |       |

| 001A    | 0000   | NOP |       |

| 001B    | 0000   | NOP |       |

| 001C    | 0000   | NOP |       |

| 001D    | 0000   | NOP |       |

| 001E    | 0000   | NOP |       |

| 001F    | 0000   | NOP |       |

|         |        | ORG | 0FF8H |

| 0FF8    | 0000   | NOP |       |

| 0FF9    | 0000   | NOP |       |

| 0FFA    | 0000   | NOP |       |

| 0FFB    | 0000   | NOP |       |

| 0FFC    | 0000   | NOP |       |

| 0FFD    | 0000   | NOP |       |

| 0FFE    | 0000   | NOP |       |

| 0FFF    | 0000   | NOP |       |

|         |        | ;   |       |

END

## **Program Counter**

The program counter, which is a 12-bit binary counter (Figure 2), indicates the address in program memory of the next instruction to be executed.

The program counter is normally incremented each time an instruction is executed. When the count reaches 0FFFH, it is reset to 000H.

When the CPU is reset, the program counter and page register are both initialized to "1".

Figure 2 shows the structure of the program counter.

|    |    |    |    | I  | Program | counte | r  |    |    |    |    |

|----|----|----|----|----|---------|--------|----|----|----|----|----|

| PC | PC | PC | PC | PC | PC      | PC     | PC | PC | PC | PC | PC |

| 11 | 10 | 9  | 8  | 7  | 6       | 5      | 4  | 3  | 2  | 1  | 0  |

### Figure 2 Program Counter

Table 1 is a table of change in the program counter.

|                         | ction and<br>eration | Condi-<br>tion | PC<br>11 | PC<br>10 | PC<br>9 | PC<br>8  | PC<br>7   | PC<br>6   | PC<br>5   | PC<br>4   | PC<br>3   | PC<br>2   | PC<br>1 | PC<br>0 |

|-------------------------|----------------------|----------------|----------|----------|---------|----------|-----------|-----------|-----------|-----------|-----------|-----------|---------|---------|

| _                       | JUMP adr             | JF = 0         |          |          |         | Ac       | ddress (a | adr) spe  | cified in | instructi | on        |           |         |         |

| Executed<br>instruction | CALLn adr            |                | 1        | 1        |         |          | Ac        | ddress (a | adr) spe  | cified in | instructi | on        |         |         |

|                         | RETn                 |                |          | 1        | Address | stored i | n work F  | RAM by    | correspo  | onding C  | ALLn in   | structior | า       |         |

| Address fol<br>0FFFH    | lowing               |                | 0        | 0        | 0       | 0        | 0         | 0         | 0         | 0         | 0         | 0         | 0       | 0       |

| Reset                   |                      |                | 1        | 1        | 1       | 1        | 1         | 1         | 1         | 1         | 1         | 1         | 1       | 1       |

### Table 1 Table of Change in Program Counter

The program counter can directly specify addresses throughout the whole address space of the program memory. However, care is required when using the following branching instructions.

(1) Jump Instruction [JUMP adr]

When JUMP is executed, the value (adr) specified in the instruction is set in the program counter (PC11 to PC0) if the jump flag (JF) is "0".

(2) Subroutine Instructions [CALLn adr] and [RETn]

When [CALLn adr] is executed, the value of [program counter content +1] are stored in a predetermined area of work RAM as the subroutine return address, and the value (adr) specified in the instruction is set in the lower 10 bits (PC9 to PC0) of the program counter. At this point, the upper 2 bits of the program counter (PC11 and PC10) are each set to "1". That is, the starting address of the subroutine must be between 0C00H and 0FFFH of the last page.

When [RETn] is executed, execution returns to the address stored using the [CALLn adr] instruction corresponding to n.

Subroutines can be nested up to 4 levels.

#### (3) One-Step Branch Instruction [ROM]

This instruction temporarily changes the output of the program counter. After [ROM] instruction is executed, the instruction following by one is executed. The instruction doesn't access the program memory directly by the contents of the program counter, but temporarily replaces the 5 th bit from the LSB of the program counter with the contents of the Ca register, and the 4 bits with the contents of the accumulator with the program counter output the address following [ROM] instruction. After executing one step at the branch destination, execution returns to the address of the ROM instruction + 2. However, if a second branching is executed from the first destination, execution is transferred to the address specified in that branch instruction.

| Example | Address | Instruction |                    |                                                                                                                              |

|---------|---------|-------------|--------------------|------------------------------------------------------------------------------------------------------------------------------|

| (1      | 02E0H   | MVBA 5      | Acc $\leftarrow$ 5 | Instructions are executed in the order of the circled numbers.                                                               |

| 2       | 02E1H   | CAS         | Ca ← 1             | At ①, the accumulator is set to "5" and, at ②, the Ca register is set to "1". If [ROM] is now executed, the instruction ④ in |

| 3       | 02E2H   | ROM         |                    | the step after [ROM] is executed and then the address in $(4)$                                                               |

| (4      | 02E3H   | NOP         |                    | is changed into the address in ⑤ replaced with the contents of Ca register and accumulator, and the instruction at the       |

| 6       | 02E4H   | ****        |                    | address in (5) is executed.                                                                                                  |

| (7      | 02E5H   | ****        |                    |                                                                                                                              |

| (8      | 02E6H   | ****        |                    | -                                                                                                                            |

| 9       | 02E7H   | ****        |                    | Program counter                                                                                                              |

| Ĩ       | 02E8H   | ****        |                    | PC11~PC5 PC4 PC3 PC2 PC1 PC0                                                                                                 |

|         | 02E9H   | ****        |                    | ~ Ca Acc                                                                                                                     |

|         | 02EAH   | ****        |                    |                                                                                                                              |

|         | 02EBH   | ****        |                    | ♥♥ ♥ ♥ ♥ ♥ ♥<br>Execution address                                                                                            |

|         | 02ECH   | ****        |                    |                                                                                                                              |

|         | 02EDH   | ****        |                    |                                                                                                                              |

|         | 02EEH   | ****        |                    |                                                                                                                              |

|         | 02EFH   | ****        |                    |                                                                                                                              |

|         | 02F0H   | ****        |                    |                                                                                                                              |

|         | 02F1H   | ****        |                    |                                                                                                                              |

|         | 02F2H   | ****        |                    |                                                                                                                              |

|         | 02F3H   | ****        |                    |                                                                                                                              |

|         | 02F4H   | ****        |                    |                                                                                                                              |

| (5      | ) 02F5H | ****        |                    | The instruction at (5) is executed and execution then return to the normal address (6).                                      |

|         | 02F6H   | ****        |                    |                                                                                                                              |

|         | 02F7H   | ****        |                    |                                                                                                                              |

|         | 02F8H   | ****        |                    |                                                                                                                              |

|         |         |             |                    |                                                                                                                              |

Note 1: Do not use branch instructions such as [PAGE], [JUMP], [CALL] or [RET] in position ④. When a branch instruction is executed at position ⑤, execution branches to the destination specified at position ⑤.

### X, Y, and T Registers

#### X and Y Registers

Both X and Y registers are 4-bit registers. They are mainly used as address registers for work RAM, but can also be used as general-purpose registers.

|    | X re | gister |    |  |

|----|------|--------|----|--|

| X8 | X4   | X2     | X1 |  |

- \* Specifies X address of work RAM

- \* General-purpose register

|    | Y  | regis | ster |    |

|----|----|-------|------|----|

| Y8 | Y4 |       | Y2   | Y1 |

\* Specifies Y address of work RAM

\* General-purpose register

#### T Register

The T register is a 4-bit general-purpose register. It can also be used to specify the X address in work RAM when using the [ADD b] and [SUB b] instructions. It can also be used to set the delay time in the [DLY b] instruction.

|    | T re | egister |    |

|----|------|---------|----|

| T8 | T4   | T2      | T1 |

\* General-purpose register

\* Specifies X address of work RAM

\* Sets delay time

#### Work RAM

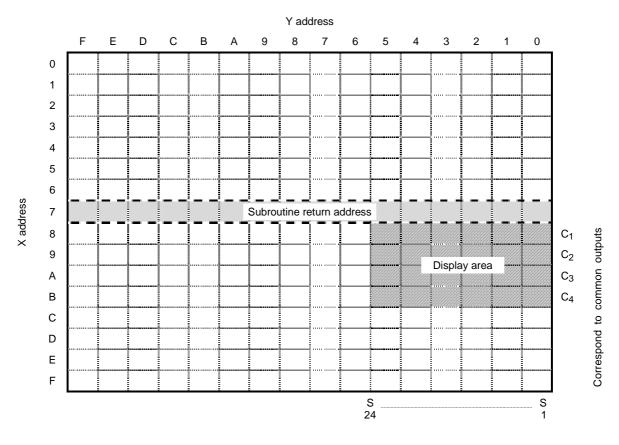

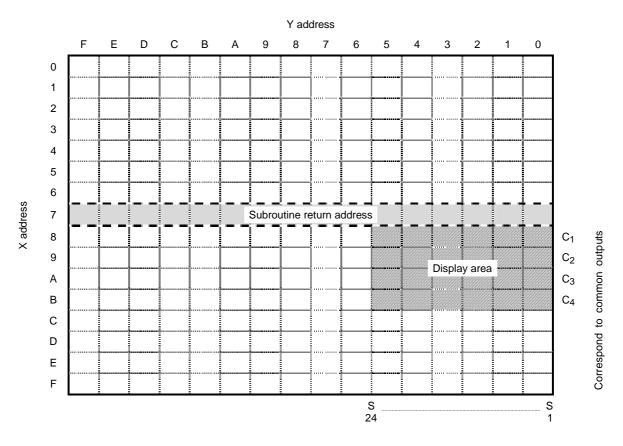

The work RAM is a  $16 \times 16$  matrix with each cell having a 4-bit capacity. The work RAM stores user data for working, LCD display data, and subroutine return addresses.

LCD display data is stored in the work RAM such that it corresponds to the LCD panel matrix. "1" lights the corresponding dot, which "0" turns it off. The position and capacity of the LCD display area is different depending on products.

When making a subroutine call, the value of the address of the [CALLn adr] instruction + 1 (program counter +1) can be stored in row X7. Up to 4 values can be stored in Y = 0 to 3 for [CALL1 adr], Y = 4 to 7 for [CALL2 adr], Y = 8 to 11 for [CALL3 adr], and Y = 12 to 15 for [CALL4 adr]. When returning from a subroutine, the value stored in the work RAM by the [CALLn adr] instruction (where n corresponds to n in [RETn]) is sent to the program counter. Other areas are available to the user, but because the user can also access the subroutine return address area, care must be taken not to corrupt the contents at that location.

The work RAM is undefined when the power is turned on, and must therefore be initialized.

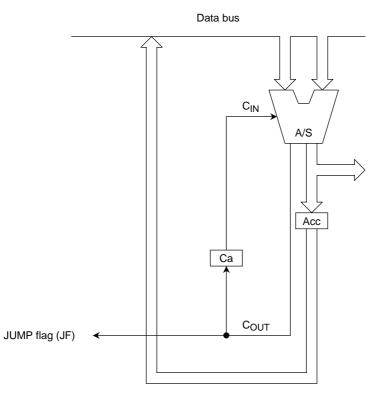

### A/S, Accumulator (Acc), Carry Register (Ca) and Jump Flag (JF)

#### A/S

The A/S (adder/subtracter unit) is a circuit for calculations on 4-bit binary data. The A/S performs calculations as specified in instructions and outputs the result (4 bits) with carry data.

Figure 4 A/S

#### Accumulator (Acc)

The accumulator is a 4-bit register that stores the results of calculations.

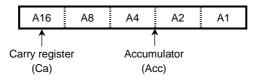

## Carry Register (Ca)

The carry register is a 1-bit register that stores the carry data output from the A/S. It can be set to "0" or "1" by instructions. Whichever value remains unchanged until the next instruction is executed that has an effect on the carry register setting.

As shown in Figure 5, the carry register can also be used in conjunction with the accumulator as a 5-bit register.

## Figure 5 Ca Register Used in Conjunction with Accumulator

#### Jump Flag (JF)

The jump flag is a 1-bit flag consisting of the carry information output from the A/S and used as the branch condition for a jump instruction [JUMP]. The jump flag is set to "1" when an instruction that sets the jump flag is executed and all conditions for the instruction are satisfied. It is kept at "1" until the next instruction has been executed, at which point it is reset to "0". An unconditional jump is performed when an instruction that does not affect the jump flag is inserted before the jump instruction.

Note that setting the jump flag (JF) and the carry register (Ca) are different processes.

#### **Oscillation and Operating Modes**

#### **Clock Generator and Timing Generator**

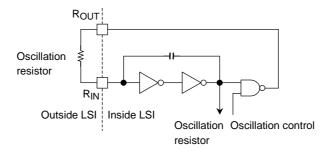

The T6C96A clock generator consists of two oscillation circuits, allowing a high-speed clock (frequency fCR) and low-speed clock (frequency fXT) to be generated. By using each of these clocks in appropriate circumstances, it is possible to save power consumption. Both the high-speed and the low-speed clock oscillation circuit are CR oscillation circuits.

The system clock supplied to the CPU is created using the timing generator. Either the high-speed or low-speed clock can be selected, using instructions, for sending to the timing generator. Executing the [FCR] instruction sends the high-speed clock to the timing generator. Conversely, executing [FXT] sends the low-speed clock to the timing generator.

On a system reset, the high-speed clock is sent to the timing generator.

Either the high-speed or low-speed clock can be selected using instructions for sending to the LCD driver. Executing the [DXT] instruction sends the low-speed clock to the LCD driver.

#### **Clock Generator**

The high-speed CR oscillation clock generator oscillates by the external mounting of a resistor (Rosc). The high-speed CR oscillation clock generator frequency is defined as "fCR". The oscillation frequency of the low-speed CR clock generator is defined as "fXT".

Note the following:

- Note 2: The value of the oscillation resistor must be selected such that fCR>fXT.

- Note 3: Due to variations in the oscillation resistor and the respective LSI characteristics, the values shown for fCR in the electrical characteristics table are only for reference. For debugging software, for example, it may be necessary to check operation with a ±50% frequency variation.

With reference to the above and the electrical characteristics tables, select the optimum oscillation resistance to ensure power savings.

Figure 6 shows the high-speed clock oscillation circuit.

### Figure 6 High-Speed Clock Oscillation Circuit

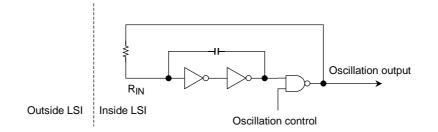

Low-speed CR oscillation clock generator is built in resistor and capacitor so that external parts are not required.

Figure 7 shows the CR oscillation circuit for low-speed CR.

#### **Timing Generator**

OSHIBA

The timing generator is a circuit that generators the system clock supplied to the CPU from the source clock generated by the clock generator.

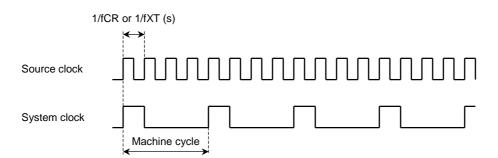

The execution of instructions and CPU operations are performed in sync with the system clock. Instruction executions are executed as combinations of basic instructions called "microinstructions". The time required to execute one microinstruction is called a machine cycle, which is one cycle of the system clock. The T6C96A instructions include 2-cycle instructions, which are executed in 2 machine cycles, 4-cycle instructions, which are executed in 6 machine cycles, and 8-cycle instructions, which are executed in 8 machine cycles.

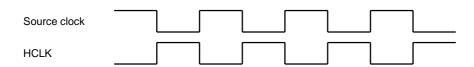

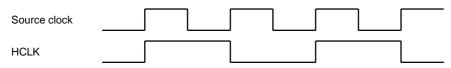

Figure 8 shows the relationship between the source clock and system clock.

Figure 8 Source Clock and System Clock

#### **Operating Modes**

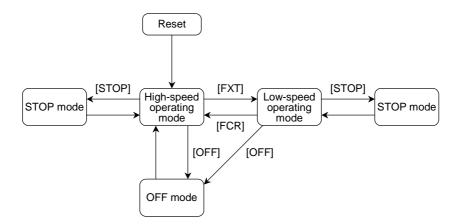

To achieve greater power savings, the T6C96A microcontrollers have four CPU operating modes: high-speed, low-speed, STOP, and OFF.

#### **Statuses in Respective Operating Modes**

• High-Speed Operating Mode

In high-speed operating mode, both high-speed and low-speed clocks oscillate, the system clock being generated from the high-speed clock so that instructions are executed at high speed. The system is initialized to high-speed operating mode after a system reset.

• Low-Speed Operating Mode

In low-speed operating mode, the high-speed clock is stopped such that only the low-speed clock oscillates, the system clock being generated from the low-speed clock so that instructions are executed at low speed.

• STOP Mode

In STOP mode, the high-speed clock is stopped such that only the low-speed clock oscillates. The system clock is stopped and the CPU is therefore also stopped. The internal status of the CPU is maintained.

• OFF Mode

In OFF mode, both high-speed and low-speed clocks are stopped such that both the CPU and display system are also stopped. The internal status of the CPU is maintained.

Table 2 shows the oscillation circuits, CPU, and LCD driver status in the respective operating modes.

### Table 2 Oscillation Circuit, CPU, and LCD Driver Statuses in Operating Modes

|                  | High-speed<br>operating mode | Low-speed operating mode | STOP mode         | OFF mode   |

|------------------|------------------------------|--------------------------|-------------------|------------|

| High-speed clock | Oscillating                  | Stopped                  | Stopped           | Stopped    |

| Low-speed clock  | Oscillating                  | Oscillating              | Oscillating       | Stopped    |

| CPU              | High-speed clock             | Low-speed clock          | Stopped           | Stopped    |

| LCD display      | Display available            | Display available        | Display available | No display |

#### **Transition between Operating Modes**

- At Power-ON and at Resetting The system defaults to high-speed operating mode when the power is turned ON or after a system reset.

- Transition from High-speed Operating Mode

The [FXT] instruction transfers from high-speed to low-speed operating mode.

STOP mode is selected by executing the [STOP] instruction. OFF mode is selected by executing the [OFF] instruction. When STOP mode or OFF mode have been selected from high-speed operating mode, high-speed operating mode resumes when those modes are exited.

After resuming operation, instructions start to be executed from the step following execution of the [STOP] or [OFF] instruction.

- Note 4: Neither [STOP] or [OFF] are executed when an "L" level signal is input to the IN terminal, or when the timer F/F corresponding to the content of the TIM register is set.

- Transition from Low-speed Operating Mode

The [FCR] instruction transfers from low-speed to high-speed operating mode.

STOP mode is selected by executing the [STOP]" instruction. OFF mode is selected by executing the [OFF] instruction. When STOP mode has been selected from low-speed operating mode, low-speed operating mode resumes when that mode is exited.

When OFF mode has been selected form low-speed operation mode, high-speed operation mode resumes when that mode is exited.

After resuming operation, instructions start to be executed from the step following execution of the [STOP] or [OFF] instruction.

- Note 5: Neither [STOP] or [OFF] are executed when an "L" level signal is input to the IN terminal, or when the timer F/F corresponding to the content of the TIM register is set.

- Resumption from STOP Mode There are two methods of resuming operation from STOP mode, as follows:

- Resumption Using IN Terminal When an "L" level signal is input to one of the normally pulled up IN terminals (IN11 to IN14)

- (2) Resumption by Timer When the timer F/F corresponding to the content of the TIM register is set

When STOP mode has been selected from high-speed operating mode, the system resumes high-speed operation when the STOP mode is exited.

When STOP mode has been selected from low-speed operating mode, the system resumes low-speed operation when the STOP mode is exited.

Note 6: [STOP] is not executed while the conditions for resuming operation from STOP mode are satisfied.

Note 7: See timer description for details.

#### • Resumption from OFF Mode

There is only one method of resuming operation from OFF mode, as follows:

Resumption from IN Terminal When an "L" level signal is input to one of the normally pulled up IN terminals (IN11 to IN14)

Note that the system is initialized to high-speed operating mode on resuming operation whether OFF mode was selected from high-speed or low-speed operating modes.

Note 8: [OFF] is not executed when the conditions for resuming operation from OFF mode are satisfied or when the timer F/F corresponding to the content of the TIM register is set.

Figure 9 shows the transition between operating modes.

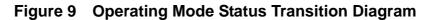

#### Timer

The timer is created by splitting the low-speed clock source oscillation (TYP. 32.8 kHz) using a 16-stage binary counter. The 10 th stage outputs a 31.25 ms signal, the 12 th stage a 125 ms signal, the 14 th stage a 500 ms signal, and the 16 th stage a 2 s signal. These four signals set specially provided timer F/Fs. The timer functions are implemented by checking the statuses of these F/Fs.

When a CR oscillation is used for the low-speed clock, the timer signals are not output with precision timing. Figure 10 shows the timer structure.

## Figure 10 Timer Structure

The timer has the following 3 functions:

- (1) Detection of 31.25 ms, 125 ms and 500 ms signals by instructions

- (2) Exiting STOP mode

- (3) Checking the oscillation status of the quartz oscillation circuit

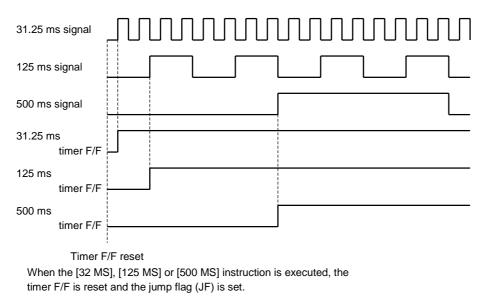

#### Detection of 31.25 ms, 125 ms and 500 ms Signals by Instructions

The statuses of F/Fs of the 31.25 ms, 125 ms and 500 ms signals can be checked using instructions [32 MS], [125 MS] and [500 MS]. If the timer F/F is set, the jump flag is set (the Ca register is not set).

At the same time, the timer F/F is reset and again set at the next timing pulse.

Figure 11 shows the timer signals output from the 16-stage timer F/F and the respective timer F/F timing.

#### Figure 11 Timing for Setting Timer F/Fs

#### **Exiting STOP Mode**

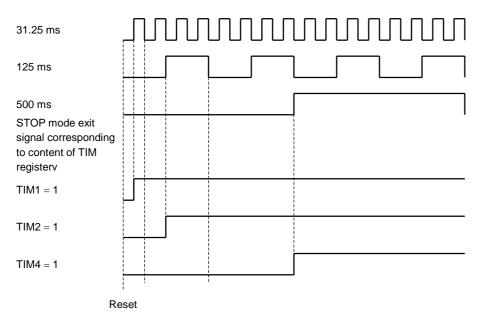

Executing [TIM] sends the lower 3 bits of Acc to the TIM register. TIM1 corresponds to the 31.25 ms timer signal, TIM2 to 125 ms, and TIM4 to 500 ms, and check the timer F/Fs. If, when checked, the timer F/F corresponding to the bit of the set TIM register is set, STOP mode is exited. If two or more bits are set to "1", the STOP mode exit signal is generated at the respective timings.

The timer F/F is not reset.

Figure 12 shows the timer signal output from the 16-stage timer F/F and the timing of the STOP mode exit signal according to the content of the TIM register.

## **External Interface**

The T6C96A has one 4-bit input port, input-output port, and output port (IN port  $\cdot$  I/O port  $\cdot$  O port). The ports are used to "exchange data with peripheral circuits" by executing instructions.

First of all, the following is an explanation on port descriptions. In the case of IOmn (n = 1 to 4) being used as the description, m represents the port number and n represents the port's internal terminal number. For example, IO2 indicates the second IO port, and IO23 indicates the third terminal of the second IO port.

## Input Ports (IN Ports)

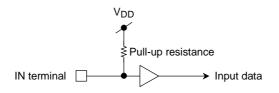

IN ports are dedicated four terminal, four bit input ports, and the data input through the IN ports is stored in the accumulator.

As the In terminals are constantly subject to pull-up within the LSI, simple input circuits can be created with a minimum of external components.

Figure 13 shows the configuration of the IN terminals.

Figure 13 IN Terminal Configuration in the Normal Mode

Figure 14 shows an example of timing using the input instruction [IIN] to fetch IN port data into the accumulator.

| Source clock |            |

|--------------|------------|

| System clock |            |

| Instruction  | X IIN X    |

| Input strobe | $\Box$     |

| Accumulator  | Input data |

Figure 14 IN Port Input Timing

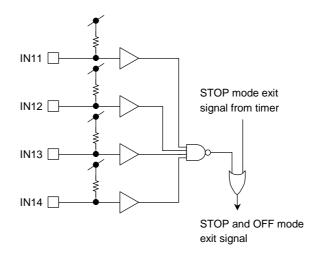

The IN ports also function for exiting the STOP and OFF modes. When the MCU is in STOP or OFF mode, inputting an "L" level signal to one of the normally pulled-up IN terminals exits the STOP or OFF mode.

Figure 15 shows the structure of a circuit for creating the signals for exiting the STOP and OFF modes. Please also refer to the timer in Figure 10.

Figure 15 STOP and OFF Mode Exit Signal from IN Port

#### **IO Ports**

Each T6C96A port consists of two four-bit IO ports (IO11 to IO14, IO21 to IO24) and one single-bit IO port (IO31).

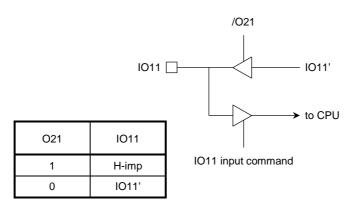

<IO11 Terminals>

Port IO11 has a 3-state structure equipped with output latching which enables HI-Z when the O21 control signal (single-bit) is set with software. The O21 control signal for [OTB2 1] is initialized with "L" when reset. Figure 16 shows the configuration of the IO11 terminal.

## Figure 16 IO11 Terminal Configuration

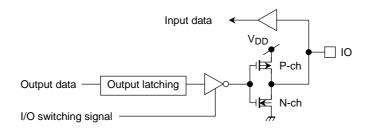

<IO12 to IO14, IO21 to IO24 and IO31>

Ports IO12 to IO14, IO21 to IO24 and IO31 employ a method that does not utilize 3-state buffers. This method creates large "H" level output resistance for the inverter's P channel transistors used for the output. Figure 17 shows the configuration of these terminals.

### Figure 17 IO12 to IO14, IO21 to IO24 and IO31 Terminal Configuration

As the performance of the N-ch transistor used for output is large when the latch data in the output latch is "L", there will be cases where the "H" level in Acc cannot be loaded despite the [INIOm] input instruction being executed.

It is therefore necessary to execute the [OIBm 15] instruction and set the inverter's P channel transistor at ON prior to executing the input instruction.

#### **IO Port Input Timing**

Figure 18 shows an example of the input instruction [IIOm] for reading data via an IO port with nothing connected to the IO port.

| Source clock      |            |

|-------------------|------------|

| System clock      |            |

| Instruction       |            |

| I/O select signal |            |

| IO port           | X          |

| Input strobe      |            |

| Acc               | Input data |

Figure 18 Input Timing of IO Port

### IO Port Output Timing

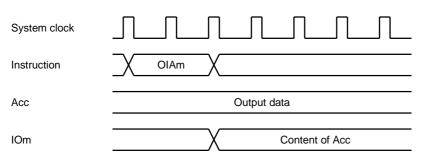

Figure 19 shows an example of using the 2-cycle IO port output instruction [OIAm]. This instruction outputs the content of the accumulator (Acc) to port IOm.

## Figure 19 IO Port Output Timing for [OIAm] Instruction

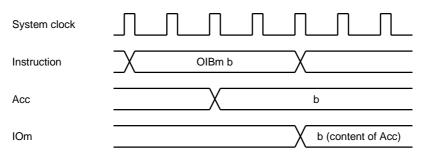

Figure 20 shows an example of using the 4-cycle IO port output instruction [OIBm b].

This instruction writes immediate data b (4 bits) to the accumulator (Acc) and outputs that data to port IOm.

## Figure 20 IO Port Output Timing for [OIBm b] Instruction

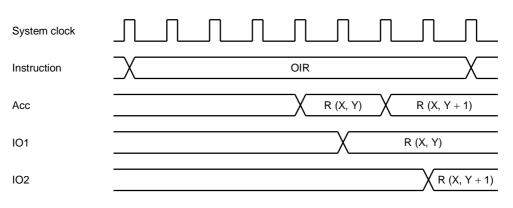

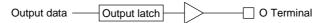

Figure 21 shows an example of using the 8-cycle IO port output instruction [OIR]. This instruction writes the content of work RAM specified by the contents of the X and Y registers to the accumulator (Acc), then outputs the data to port IO1. It then writes the contents of the work RAM specified by the contents of the X and Y registers + 1 to the Acc, then outputs that data to port IO2.

### **Output Ports (O)**

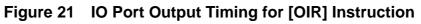

O ports are 4-bit output only ports with 4 terminals. All are push-pull structures with latches. When the output instruction is executed, the output data is latched before being output. The latch is initialized to the "L" level when the MCU is reset.

Figure 22 shows the structure of an O terminal.

Figure 22 O Terminal Structure

The following shows O port output timing.

Figure 23 shows an example of the 2-cycle O port output instruction [OTAm]. This instruction outputs the contents of the accumulator (Acc) to port Om.

| System clock |                | L |  |  |  |  |

|--------------|----------------|---|--|--|--|--|

| Instruction  | V OTAm V       | _ |  |  |  |  |

| Acc          | Output data    |   |  |  |  |  |

| Om           | Content of Acc |   |  |  |  |  |

## Figure 23 O Port Output Timing for [OTAm] Instruction

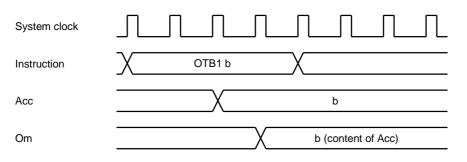

Figure 24 shows an example of the 4-cycle O port output instruction [OTBm b]. This instruction writes immediate data b (4 bits) to the accumulator (Acc) and outputs that data to port Om.

Figure 24 O Port Output Timing for [OTBm b] Instruction

### T6C96A

### HCLK

TOSHIBA

The HCLK is mainly used for outputting a high-speed CR oscillation (3.58/1.79 MHz) clock. The HCLK pin is controlled using the output instruction [IOBm b] by which output data to the IO11 to IO14 and IO31 pins are determined.

Either the high-speed CR oscillation frequency (3.58 MHz) or half of that frequency (1.79 MHz) output from the HCLK pin can be selected as shown in the mask option table below. Please request the desired mask option at sampling.

| AL CODE | HCLK output frequency                                       |  |

|---------|-------------------------------------------------------------|--|

| AL7432  | High-speed CR oscillation frequency (3.58 MHz)              |  |

| AL7434  | High-speed CR oscillation frequency $\times$ 1/2 (1.79 MHz) |  |

Table 3 Mask Option

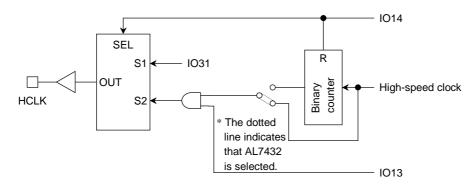

A structural diagram of the HCLK circuit is shown below.

| IO14 | IO13 | IO31 (= S1) | S2    | HCLK  |

|------|------|-------------|-------|-------|

| 1    | *    | 0           | *     | 0     |

| 1    | *    | 1           | *     | 1     |

| 0    | 1    | *           | CLK*1 | CLK*1 |

\* : Don't care

\*1: When mask option AL7434 is selected, CLK  $\times$  1/2 is output.

### Figure 25 HCLK Structural Diagram

The relation between the source clock and HCLK is as follows: When mask option AL7432 is selected (HCLK = high-speed CR oscillation frequency output is selected)

When mask option AL7434 is selected (HCLK = high-speed CR oscillation frequency  $\times$  1/2 output is selected)

- Note 9: When the high-speed CR oscillation frequency divided in half is selected (AL7434 selected), to start the signal output from the HCLK pin at Low level, initialize the binary counter using the following procedure when starting the LSI and when stopping the HCLK output.

- OIB3  $\,$  0000b; outputs Low to IO31.

- OIB1 11\*\*b; changes HCLK output to S1 (IO31 = Low) and simultaneously resets binary counter Because the asterisks (\*\*) are the output values of IO12 and IO11, make settings accordingly.

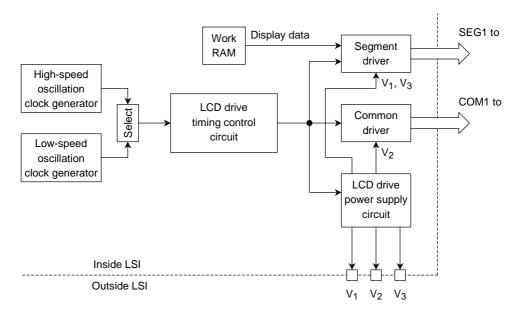

## LCD Driver

The T6C96A microcontrollers incorporate an LCD driver for driving an LCD and the necessary control circuit. It has 96 LCD pixels (segements  $\times$  common).

## LCD Driver Structure

Figure 26 shows the structure of the LCD driver.

## Figure 26 Structure of LCD Driver

The LCD drive timing is derived from either the high-speed or low-speed clock. At a system reset, the system is initialized to the high-speed clock, but the low-speed clock can be selected by executing an instruction. When in low-speed operating mode, the LCD driver should also use the low-speed clock. When the LCD driver uses the low-speed clock, the LCD display can be continued even in STOP mode.

## Method of LCD Drive

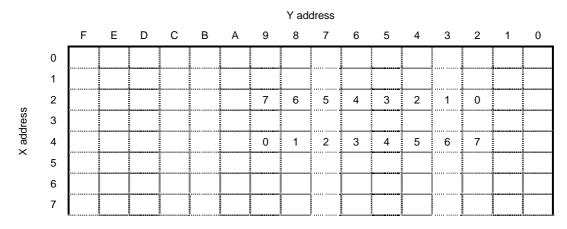

The T6C96A microcontrollers have a display area in the work RAM. By writing data to this display area, a display waveform is automatically output from the segment terminals. The display area is a bitmap that corresponds one-to-one with the LCD display pixels.

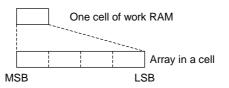

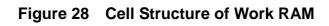

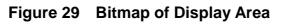

If an area as indicated in Figure 27 is included within the work RAM, a  $24 \times 4$  bit map as shown in Figure 29 exists owing to the fact that each cell consists of four bits, as indicated in Figure 28.

Figure 27 Map of Work RAM

## LCD Drive Power Supply Circuit

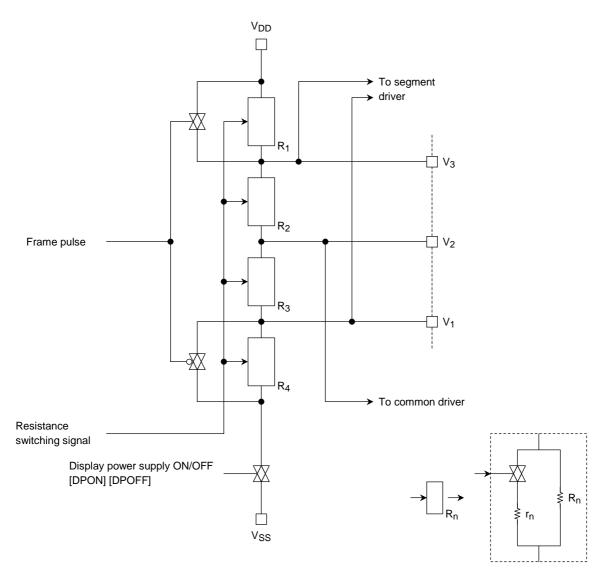

The LCD drive power supply circuit generates the  $V_1$ ,  $V_2$  and  $V_3$  voltages supplied to the common and segment drivers.

$V_{\rm 1}, V_{\rm 2}$  and  $V_{\rm 3}$  are generated by using the frame pulse to control the resistance dividing circuit between  $V_{\rm DD}$  and  $V_{\rm SS}.$

Figure 30 shows the structure of the LCD drive power supply circuit.

Note 10:  $R_1:R_2:R_3:R_4 = r_1:r_2:r_3:r_4$

If the ratio between  $R_1$ ,  $R_2$ ,  $R_3$  and  $R_4$  (the dividing resistance) is 1:1:1:1, we achieve a 1/3 prebias.

To improve the through rate when switching the LCD elements ON/OFF, a large current is caused to flow at the instant the common is switched. Concretely, the large current flows only when the LCD element turns ON (current in both  $r_n$  and  $R_n$ ), after that, the current is reduced (current only in  $R_n$ ) for power saving.

The T6C96A microcontrollers have a power saving function that operates by turning the display power supply ON/OFF. When [DPON] is executed, the display power supply turns ON. When [DPOFF] is executed, it turns OFF.

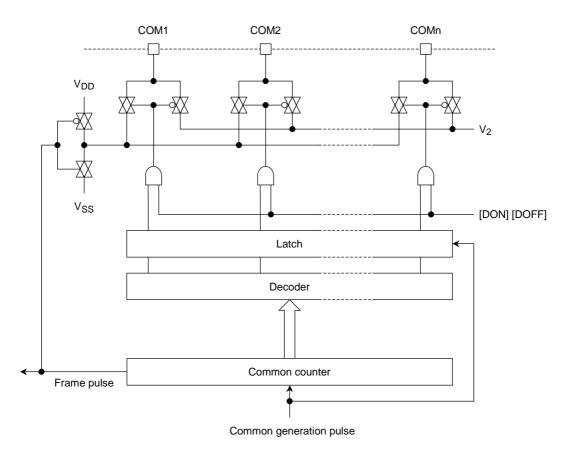

### **Common Driver**

TOSHIBA

The common driver circuit creates common signals with a predetermined timing.

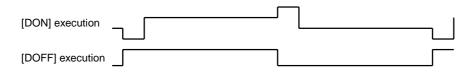

Executing [DON] changes the common level to ON. Conversely, [DOFF] turns it OFF (same as V<sub>2</sub>).

Figure 31 shows the common signal when the [DON] and [DOFF] instructions are executed. Signal COM1 is used in this example.

Figure 32 shows the structure of the common driver.

Figure 32 Structure of Common Driver

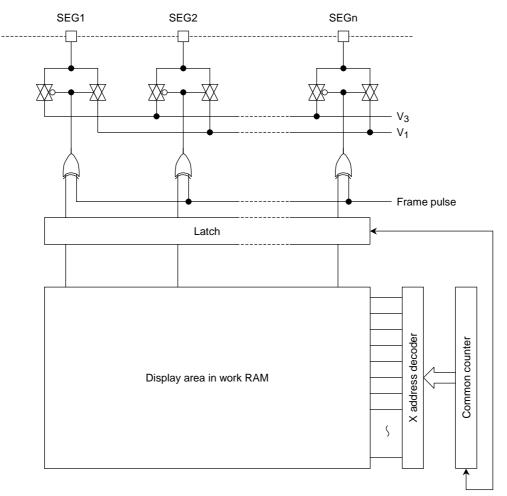

## Segment Driver

The segment driver circuit generates segment signals using the timing determined from the content of the work RAM.

Figure 33 shows the structure of the segment driver.

Common generation pulse

Figure 33 Structure of Segment Driver

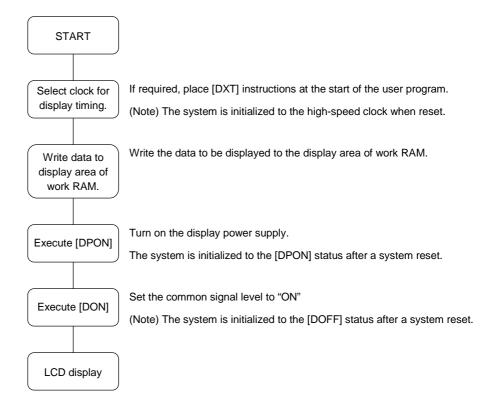

#### **Using Display Control Instructions**

This section explains how to use the display control instructions described in the previous pages.

The instructions for selecting the clock used to generate the LCD display timing are placed at the beginning of a user program. Then, after data has been written to the work RAM, [DPON] is executed to turn ON the display power supply, followed by [DON] to set the common signal level to "ON" and effect the LCD display.

### Figure 34 Flow of Operations to Displaying Data on LCD

### **Special T6C96A Instructions**

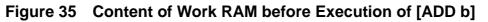

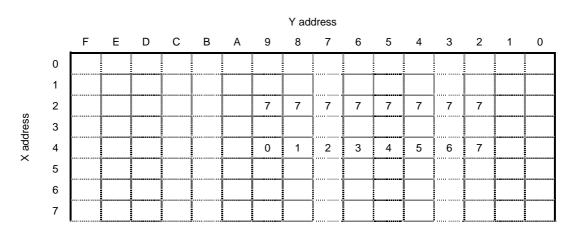

#### [ADD b]

This instruction performs addition operations on decimal numbers. The result is also stored as a decimal. Executing [ADD b] adds the content of work RAM specified by the X and Y registers and the content of work RAM specified by the T and Y registers to Ca. The result is stored in work RAM as specified by the X and Y registers.

This operation is repeated incrementing the Y register by 1 each time until an overflow occurs at Y register + b.

#### Example:

When the content of work RAM is as shown in Figure 35, executing the following instructions causes the content to change to that shown in Figure 36.

MVBW 2, 2 MVBT4 ADD 7

## T6C96A

## TOSHIBA

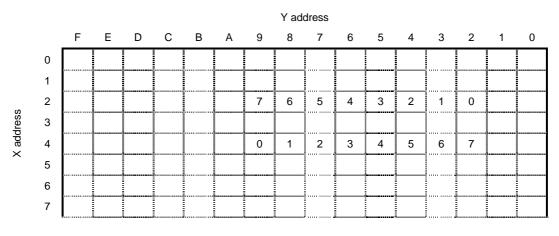

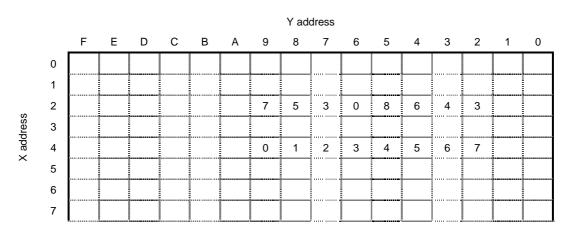

#### [SUB b]

This instruction performs subtraction operations on decimal numbers. The result is also stored as a decimal.

Executing [SUB b] subtracts the content of work RAM specified by the T and Y registers with Ca from the content of work RAM specified by the X and Y registers. The result is stored in work RAM as specified by the X and Y registers.

This operation is repeated incrementing the Y register by 1 each time until an overflow occurs at Y register + b.

#### Example:

When the content of work RAM is as shown in Figure 37, executing the following instructions causes the content to change to that shown in Figure 38.

MVBW 2, 2 MVBT4 SUB 7

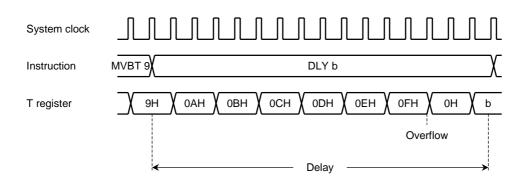

#### [DLY b]

Executing [DLY b] generates a delay of  $\{\!(16-T)\times2+2\}$  machine cycles according to the content of the T register.

The content of the T register is incremented by 1 each two machine cycles. Two machine cycles after an overflow occurs, immediate data b is sent to the T register and normal operation then resumes.

Figure 39 shows the delay that is generated and the resulting content of the T register when [DLY b] is executed when the content of the T register is 9.

Figure 39 Timing of [DLY b] Execution

## Configuration

This section contains notes on mounting T6C96A microcontrollers.

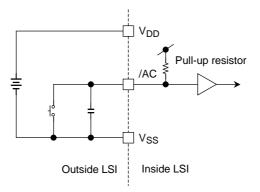

### /AC (Reset)

When the power supply voltage is within the operating voltage range, keeping the level of the /AC terminal "L" for a minimum of 100  $\mu s$  initializes the entire contents of the LSI. When the level of the /AC terminal changes to "H", the reset operation is canceled and program execution starts. The /AC terminal is internally pulled up, and it is therefore possible to create a simple reset circuit using only one switch.

Figure 40 shows a simple reset circuit.

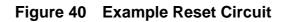

### TS (Test)

The TS terminal is used for the shipping test by TOSHIBA and has a built-in pull-down resistor. For normal use, the TS terminal level should be fixed "L" as shown in Figure 41.

Figure 41 Treatment of TS terminal

### $R_{\text{IN}}$ and $R_{\text{OUT}}$

The RIN and ROUT terminals are connected inside the LSI to the clock generators. Connect a resistor between RIN and ROUT as shown in Figure 42.

Setup the frequency form  $42.6\ \rm kHz$  upward.

Figure 42 Method of Connecting Oscillator

## Instruction Tables

In addition to the normal move, calculate, bit manipulation, and input-output instructions, the T6C96A also has special instructions for driving a LCD.

The following shows the conventions used in the instruction tables.

| Mnemonic | Machine language | Microinstruction | Acc  | Са | JF | т | х | Y | Cy-<br>cles |

|----------|------------------|------------------|------|----|----|---|---|---|-------------|

| (*1)     | (*2)             | (*3)             | (*4) |    |    |   |   |   | (*5)        |

(\*1)

The instruction mnemonic

The operation code and operand are separated by one space. The x and y operands are 4-bit data specifying the cell in work RAM.

Operands a and b are, unless specifically mentioned in the text, 4-bit data. (An exception is the move instruction MVBA (b = 5 bits).)

Operand n is 4-bit data in move instruction TRNS, or indicates a specific bit 8, 4, 2, or 1 from the MSB in bit manipulation instructions.

Operand adr is 12 bits in the branch instruction JUMP, and 10 bits in the CALL instruction.

#### (\*2)

The instruction in machine language

a, b, x, y, and n represent immediate data. The left of the string is the MSB, the right is the LSB.

#### (\*3)

Microinstruction

The functions of the instruction are written as microinstructions.

One line corresponds to one machine cycle.

RTN indicates the end of a microinstruction.

When two or more microinstructions are shown in one machine cycle, they are delimited by "f".

#### (\*4)

Contents of registers after instruction execution

- $0\quad {\rm for \ those \ that \ become \ "0"}$

- 1 for those that become "1"

- \* for those that change according to conditions

— for those that do not change

${\rm JF}$  for those storing the  ${\rm JF}$  in the Ca register

Others according to \*1 and \*2

#### (\*5)

Number of machine cycles required to execute the instruction

| Mnemonic  | Machine language  | Microinstructions                                  | Acc      | Са  | JF | т        | х   | Y   | Cy-<br>clesv |

|-----------|-------------------|----------------------------------------------------|----------|-----|----|----------|-----|-----|--------------|

| MVAT      | 00 0000 0101 0001 | T ← Acc<br>RTN                                     | _        | _   |    | Acc      | _   |     | 2            |

| MVAX      | 00 0000 0101 0010 | X ← Acc<br>RTN                                     |          | _   | _  | _        | Acc |     | 2            |

| MVAY      | 00 0000 0101 0011 | Y ← Acc<br>RTN                                     | _        | _   | _  | _        |     | Acc | 2            |

| MVAR      | 00 0001 0000 0000 | R (X, Y) ← Acc<br>RTN                              | _        |     |    |          |     |     | 2            |

| MVAI x, y | 00 0101 xxxx yyyy | R (x, y) ← Acc<br>RTN                              | _        |     |    |          |     |     | 2            |

| MVTA      | 00 0000 0101 1001 | Acc ← T<br>RTN                                     | т        | 0   | _  | _        | _   | _   | 2            |

| MVTX      | 00 0000 0101 0110 | X ← T<br>RTN                                       | _        | _   | _  | —        | т   |     | 2            |

| MVTY      | 00 0000 0101 0111 | Y ← T<br>RTN                                       |          | —   | _  |          | _   | т   | 2            |

| MVTR      | 00 0001 0000 0010 | R (X, Y) ← T<br>RTN                                |          | —   | _  |          | _   |     | 2            |

| MVXA      | 00 0000 0101 1010 | Acc ← X<br>RTN                                     | х        | 0   | _  |          | _   |     | 2            |

| MVXT      | 00 0000 0101 0100 | T ← X<br>RTN                                       | _        | _   | _  | х        | _   |     | 2            |

| MVYA      | 00 0000 0101 1011 | Acc ← Y<br>RTN                                     | Y        | 0   | _  |          | _   |     | 2            |

| MVYT      | 00 0000 0101 0101 | T ← Y<br>RTN                                       | _        | —   | _  | Y        | _   | _   | 2            |

| MVRA      | 00 0001 0000 0001 | Acc $\leftarrow$ R (X, Y) /Ca Hold<br>RTN          | R (X, Y) | —   | _  | —        | _   | _   | 2            |

| MVRT      | 00 0001 0000 0011 | $T \leftarrow R (X, Y)$<br>RTN                     | _        | —   | _  | R (X, Y) | _   | _   | 2            |

| MVIA x, y | 00 0100 xxxx yyyy | Acc ← R (x, y)<br>RTN                              | R (x, y) | 0   | _  | —        | _   | _   | 2            |

| MVBA b    | 00 0001 010b bbbb | Acc $\leftarrow$ b8~b1, Ca $\leftarrow$ b16<br>RTN | b8~b1    | b16 | _  | —        | _   |     | 2            |

| MVBAH b   | 00 0001 1000 bbbb | Acc ← b/Ca Hold<br>RTN                             | b        |     |    |          |     |     | 2            |

| MVBT b    | 00 0001 1001 bbbb | T ← b<br>RTN                                       |          |     |    | b        |     |     | 2            |

| MVBX b    | 00 0001 1100 bbbb | X ← b<br>RTN                                       | _        | _   | _  |          | b   | _   | 2            |

| Mnemonic  | Function                                                                                   |

|-----------|--------------------------------------------------------------------------------------------|

| MVAT      | Moves content of Acc to T register.                                                        |

| MVAX      | Moves content of Acc to X register.                                                        |

| MVAY      | Moves content of Acc to Y register.                                                        |

| MVAR      | Moves content of Acc to work RAM specified by contents of X and Y registers.               |

| MVAI x, y | Moves content of Acc to work RAM specified by instruction codes x and y.                   |

| MVTA      | Moves content of T register to Acc. Ca is set to "0".                                      |

| MVTX      | Moves content of T register to X register.                                                 |

| MVTY      | Moves content of T register to Y register.                                                 |

| MVTR      | Moves content of T register to work RAM specified by X and Y registers.                    |

| MVXA      | Moves content of X register to Acc. Ca is set to "0".                                      |

| MVXT      | Moves content of X register to T register.                                                 |

| MVYA      | Moves content of Y register to Acc. Ca is set to "0".                                      |

| MVYT      | Moves content of Y register to T register.                                                 |

| MVRA      | Moves content of work RAM specified by X and Y registers to Acc.                           |

| MVRT      | Moves content of work RAM specified by X and Y registers to T register.                    |

| MVIA x, y | Moves content of work RAM specified by instruction codes x and y to Acc. Ca is set to "0". |

| MVBA b    | Moves MSB of immediate data b (5 bits) to Ca and 4 bits on LSB side to Acc.                |

| MVBAH b   | Moves immediate data b to Acc.                                                             |

| MVBT b    | Moves immediate data b to T register.                                                      |

| MVBX b    | Moves immediate data b to X register.                                                      |

| Mnemonic  | Machine language  | Microinstructions                                                                                                                                                                                                                                                                                         | Acc             | Ca | JF | т  | Х     | Y         | Cy-<br>cles |

|-----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----|----|----|-------|-----------|-------------|

| MVBY b    | 00 0001 1101 bbbb | Y ← b<br>RTN                                                                                                                                                                                                                                                                                              | _               | _  |    | _  |       | b         | 2           |

| MVBW a, b | 00 0010 aaaa bbbb | X ← a Y ← b<br>RTN                                                                                                                                                                                                                                                                                        | _               |    |    | _  | а     | b         | 2           |

| MBRX b    | 00 0001 0110 bbbb | $R (X, Y) \leftarrow b$ $NOP$ $X \leftarrow X + 1$ $RTN$                                                                                                                                                                                                                                                  |                 |    | *  |    | X + 1 | _         | 4           |

| MBRY b    | 00 0001 0111 bbbb | R (X, Y) ← b<br>NOP<br>Y ← Y + 1<br>RTN                                                                                                                                                                                                                                                                   |                 |    | *  |    |       | Y + 1     | 4           |

| TRNS x, n | 00 0011 xxxx nnnn | $\begin{array}{c} Acc \leftarrow R \left( X, Y \right) \checkmark \\ Y \leftarrow Y - n \\ R \left( x, Y \right) \leftarrow Acc \\ Y \leftarrow Y + n + 1 \\ T \leftarrow T - 1 \\ JF Check \\ NOP \\ \hline RTN \\ \end{array} \begin{array}{c} JF \\ JF \\ JF \\ JF \\ JF \\ TF \\ TF \\ JF \\ TF \\ T$ | R<br>(X, Y + T) | 0  |    | 15 | _     | Y + T + 1 | 6T<br>+ 8   |

| Mnemonic  | Function                                                                                                                                                                                            |  |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MVBY b    | Moves immediate data b to Y register.                                                                                                                                                               |  |  |  |  |  |

| MVBW a, b | Moves immediate data a to X register and b to Y register.                                                                                                                                           |  |  |  |  |  |

| MBRX b    | tores immediate data b in work RAM specified by X and Y registers, then increments X register.                                                                                                      |  |  |  |  |  |

| MBRY b    | Stores immediate data b in work RAM specified by X and Y registers, then increments Y register.                                                                                                     |  |  |  |  |  |

| TRNS x, n | Moves content of work RAM specified by X and Y registers to work RAM specified by instruction code x and (Y register-n), then increments Y register.<br>This is repeated by (T register + 1) times. |  |  |  |  |  |

| Mnemonic  | Machine language  | Microinstructions                                                                            | Acc                       | Ca | JF | т               | Х     | Y                         | Cy-<br>cles |

|-----------|-------------------|----------------------------------------------------------------------------------------------|---------------------------|----|----|-----------------|-------|---------------------------|-------------|

| ADTA      | 00 0001 0001 0101 | Acc, Ca ← T + Acc + Ca<br>RTN                                                                | T + Acc<br>+ Ca           | JF | *  | _               |       |                           | 2           |

| SBTA      | 00 0001 0001 0111 | Acc, Ca $\leftarrow$ T – Acc – Ca<br>RTN                                                     | T – Acc<br>– Ca           | JF | *  |                 | _     | _                         | 2           |

| ADTR      | 00 0001 0000 0100 | $T \leftarrow T + R (X, Y)$<br>RTN                                                           |                           |    | *  | T +<br>R (X, Y) |       |                           | 2           |

| SBTR      | 00 0001 0000 0110 | T ← T − R (X, Y)<br>RTN                                                                      |                           |    | *  | T –<br>R (X, Y) |       |                           | 2           |

| ADRA      | 00 0001 0000 0101 | Acc, Ca ← R (X, Y) +<br>Acc + Ca<br>RTN                                                      | R (X, Y)<br>+ Acc<br>+ Ca | JF | *  | _               |       |                           | 2           |

| SBRA      | 00 0001 0000 0111 | Acc, Ca ← R (X, Y) –<br>Acc – Ca<br>RTN                                                      | R (X, Y)<br>– Acc<br>– Ca | JF | *  |                 |       |                           | 2           |

| ADIA x, y | 00 0110 xxxx yyyy | Acc, Ca ← R (x, y) + Acc<br>+ Ca<br>RTN                                                      | R (x, y) +<br>Acc + Ca    | JF | *  |                 | _     | _                         | 2           |

| SBIA x, y | 00 0111 xxxx yyyy | Acc, Ca ← R (x, y) – Acc<br>– Ca<br>RTN                                                      | R (x, y) –<br>Acc – Ca    | JF | *  |                 |       |                           | 2           |

| ADBA b    | 00 0000 1000 bbbb | Acc, Ca ← b + Acc + Ca<br>RTN                                                                | b + Acc<br>+ Ca           | JF | *  | _               | _     |                           | 2           |

| SBBA b    | 00 0000 1001 bbbb | Acc, Ca ← b – Acc – Ca<br>RTN                                                                | b – Acc<br>– Ca           | JF | *  | _               |       |                           | 2           |

| ADTB b    | 00 0000 1010 bbbb | T ← T + b<br>RTN                                                                             | _                         | _  | *  | T + b           | _     | _                         | 2           |

| SBTB b    | 00 0000 1011 bbbb | T ← T – b<br>RTN                                                                             |                           |    | *  | T – b           |       |                           | 2           |

| ADXB b    | 00 0000 1100 bbbb | X ← X + b<br>RTN                                                                             |                           |    | *  | _               | X + b |                           | 2           |

| SBXB b    | 00 0000 1101 bbbb | X ← X – b<br>RTN                                                                             | _                         |    | *  |                 | X - b | _                         | 2           |

| ADYB b    | 00 0000 1110 bbbb | Y ← Y + b<br>RTN                                                                             | _                         | —  | *  |                 |       | $\mathbf{Y} + \mathbf{b}$ | 2           |

| SBYB b    | 00 0000 1111 bbbb | Y ← Y – b<br>RTN                                                                             |                           | _  | *  |                 |       | Y – b                     | 2           |

| INC x, y  | 00 1110 xxxx yyyy | Acc, Ca $\leftarrow$ R (x, y) + 1<br>R (x, y) $\leftarrow$ Acc<br>R (x, y) – Acc – Ca<br>RTN | R (x, y)<br>+ 1           | JF | *  | —               | —     |                           | 4           |

| DEC x, y  | 00 1111 xxxx yyyy | Acc, Ca $\leftarrow$ R (x, y) – 1<br>R (x, y) $\leftarrow$ Acc<br>R (x, y) – Acc – Ca<br>RTN | R (x, y)<br>– 1           | JF | *  | _               |       | _                         | 4           |

| Mnemonic  | Function                                                                                                                                                              |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADTA      | Adds the content of the T register to contents of Acc and Ca and stores the result in Acc. An overflow sets Ca to "1".                                                |

| SBTA      | Subtracts the contents of Acc and Ca from the content of the T register and stores the result in Acc. A borrow sets Ca to "1".                                        |

| ADTR      | Adds the content of the T register to the content of work RAM specified by the X and Y registers, then stores the result in the T register.                           |

| SBTR      | Subtracts the content of work RAM specified by the X and Y registers from the content of the T register, then stores the result in the T register.                    |

| ADRA      | Adds the content of the work RAM specified by the X and Y registers to the contents of Acc and Ca, then stores the result in Acc. An overflow sets Ca to "1".         |

| SBRA      | Subtracts the contents of Acc and Ca from the content of the work RAM specified by the X and Y registers, then stores the result in Acc. A borrow sets Ca to "1".     |

| ADIA x, y | Adds the content of work RAM specified by instruction codes x and y to the contents of Acc and Ca, then stores the result in Acc. An overflow sets Ca to "1".         |

| SBIA x, y | Subtracts the contents of Acc and Ca from the content of the work RAM specified by instruction codes x and y, then stores the result in Acc. A borrow sets Ca to "1". |

| ADBA b    | Adds immediate data b to the contents of Acc and Ca, then stores the result in Acc. An overflow sets Ca to "1".                                                       |

| SBBA b    | Subtracts the contents of Acc and Ca from immediate data b, then stores the result in Acc. A borrow sets Ca to "1".                                                   |

| ADTB b    | Adds the content of the T register to immediate data b, then stores the result in the T register.                                                                     |

| SBTB b    | Subtracts immediate data b from the content of the T register, then stores the result in the T register.                                                              |

| ADXB b    | Adds the content of the X register to immediate data b, then stores the result in the X register.                                                                     |

| SBXB b    | Subtracts immediate data b from the content of the X register, then stores the result in the X register.                                                              |

| ADYB b    | Adds the content of the Y register to immediate data b, then stores the result in the Y register.                                                                     |

| SBYB b    | Subtracts immediate data b from the content of the Y register, then stores the result in the Y register.                                                              |

| INC x, y  | Increments the content of work RAM specified by instruction codes x and y. An overflow sets Ca to "1". The content of work RAM after incrementing is stored in Acc.   |

| DEC x, y  | Decrements the content of work RAM specified by instruction codes x and y. A borrow sets Ca to "1". The content of work RAM after decrementing is stored in Acc.      |

| Mnemonic | Machine language  | Microinstructions                                                                                                                                                                                                                             | Acc                        | Ca | JF | т     | Х | Y          | Cy-<br>cles |

|----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----|----|-------|---|------------|-------------|

| TINC     | 00 0000 0011 1000 | $\begin{array}{l} Acc \leftarrow R (X, Y) + 1 \\ R (X, Y) \leftarrow Acc \\ converted to decimal \\ Y \leftarrow Y + 1 \\ Acc \leftarrow 0/Ca \ Hold \\ Acc, Ca \leftarrow R (X, Y) + \\ Acc + Ca \\ R (X, Y) \leftarrow Acc/RTN \end{array}$ | Same as<br>R<br>(X, Y + 1) | JF | *  |       | _ | Y + 1      | 6           |

| TDEC     | 00 0000 0011 1001 | Acc $\leftarrow$ R (X, Y) – 1<br>R (X, Y) $\leftarrow$ Acc<br>converted to decimal<br>Y $\leftarrow$ Y + 1<br>Acc $\leftarrow$ 0/Ca Hold<br>Acc, Ca $\leftarrow$ R (X, Y) –<br>Acc – Ca<br>R (X, Y) $\leftarrow$ Acc/RTN                      | Same as<br>R<br>(X, Y + 1) |    | *  |       |   | Y + 1      | 6           |

| ADD b    | 00 1011 0000 bbbb | Acc $\leftarrow$ R (T, Y) /<br>Ca Hold<br>Acc, Ca $\leftarrow$ R (X, Y) +<br>Acc + Ca<br>R (X, Y) $\leftarrow$ Acc<br>converted to decimal<br>NOP<br>Y + b //JF<br>Y $\leftarrow$ Y + 1/JF Check //<br>NOP                                    | Result<br>operatio         |    |    |       |   | 16 – b + 1 | *           |

| SUB b    | 00 1011 0001 bbbb | Acc $\leftarrow$ R (T, Y) /<br>Ca Hold<br>Acc, Ca $\leftarrow$ R (X, Y) –<br>Acc – Ca<br>R (X, Y) $\leftarrow$ Acc<br>converted to decimal<br>NOP<br>Y + b //JF<br>Y $\leftarrow$ Y + 1/JF Check<br>NOP<br>RTN                                | Result of operation        |    |    |       |   | 16 – b + 1 | *           |

| CMBA b   | 00 0001 0010 bbbb | NOP<br>Acc, Ca ← b – Acc<br>0 – Acc<br>RTN                                                                                                                                                                                                    | b – Acc                    | *  | *  | _     | _ |            | 4           |

| CMBR b   | 00 0001 0011 bbbb | $Acc \leftarrow R (X, Y)$<br>$Acc, Ca \leftarrow b - Acc$<br>0 - Acc<br>RTN                                                                                                                                                                   | b –<br>R (X, Y)            | *  | *  |       |   | _          | 4           |

| CMBT b   | 00 0001 1010 bbbb | NOP<br>$T \leftarrow T - b$<br>T - 1<br>RTN                                                                                                                                                                                                   | _                          |    | *  | T – b |   |            | 4           |

| Mnemonic | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|