# E10160VHR ECL Gate Array with ROM

# PRELIMINARY

# **DESCRIPTION**

Fujitsu's E10160VHR array utilizes advanced technology to produce an array with high I/O capability, high density, high speed, and excellent power dissipation combined with an on-chip ROM of 160K bits. The internal structure allows up to 13,440 gates, including high-drive and I/O macrocells. High-drive internal macrocells allow a maximum fanout of 40. Interconnection is implemented with four layers of metallization. The E10160VHR is especially well suited for such high-performance systems as mainframe and supermini computers, high-end workstations, telecommunications, and instrumentation for control store and fast look-up table applications.

VH series ECL arrays are designed using Fujitsu's integrated design system software in conjunction with either an Amdahl 5860 or Fujitsu M-780 mainframe supercomputer. The VH series has an extensive cell library.

# **FEATURES**

- High Performance Logic

- -80 ps/gate typical at 2.95 mW<sup>1</sup>

- 135 ps/gate typical at 1.11 mW1

- 13440 Maximum Equivalent Gates

- 163840 bit = (1024w x 20b) x 8 Mask ROM

- High I/O Count

- -294 I/O available

- 3-level Series Gating

- Loaded Delay Performance

- 250 ps/gate typical at 4.6 mW<sup>2</sup>

- $-300 \text{ ps/gate typical at } 2.95 \text{ mW}^2$

- -350 ps/gate typical at 1.11 mW<sup>2</sup>

- ROM access time = 3.0 ns max

- I/O Options

- 10KH ECL

- 100K ECL

- ECL Output Options

- $-25\Omega$ ,  $50\Omega$ , and  $100\Omega$

- Series terminated

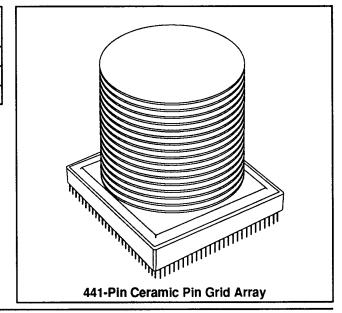

- Advanced Packaging Solutions

- 441-pin ceramic pin grid array package

- Supplied with pre-attached heat sinks

- Multiple heat sink options available

- TAB processing used

| E10160VHR Gate Array Summary |        |

|------------------------------|--------|

| Maximum Internal Gates       | 13440  |

| Bits of ROM                  | 163840 |

| Maximum I/O                  | 294    |

| Maximum Outputs              | 204    |

# Notes:

- 1. Unloaded F/I = F/O = 1, L = 0 mm.

- 2. Loaded F/I = F/O = 3. L = 3 mm.

Copyright© 1990 by FUJITSU LIMITED and Fujitsu Microelectronics, Inc

# **FUJITSU LIMITED**

Marunouchi Headquarters 6–1, Marunouchi 2-chome Chiyoda-ku, Tokyo 100, Japan Tel: (03) 216-3211

Telex: 781-22833 FAX: (03) 213-7174

For further information, please contact:

## Japan

FUJITSU LIMITED

Integrated Circuits and Semiconductor Marketing

Furukawa Sogo Bldg.

6-1, Marunouchi 2-chome

Chiyoda-ku, Tokyo 100, Japan

Tel: (03) 216-3211

Telex: 781-2224361 FAX: (03) 211-3987

# Europe

FUJITSU MIKROELEKTRONIK GmbH Lyoner Strasse 44–48 Arabella Centre 9. OG D-6000 Frankfurt 71 Federal Republic of Germany Tel: (49) (069) 66320 Telex: 441-963 FAX: (069) 663-2122

### Asia

FUJITSU MICROELECTRONICS ASIA PTE LIMITED 06-04/06-07 Plaza by the Park

No. 51 Bras Basah Road

Singapore 0719

Tel: 336-1600

Telex: 55573

FAX: 336-1609

# North and South America

FUJITSU MICROELECTRONICS, INC. Integrated Circuits Division 3545 North First Street San Jose, CA 95134-1804 USA Tel: (408) 922-9000

Telex: 910-338-0190 FAX: (408) 432-9044

©1990 FUJITSU LIMITED and Fujitsu Microelectronics, Inc.

Printed in USA OV0237-901F1