# 2K × 8 Bit Electrically Erasable PROM

#### **FEATURES**

- 2048 × 8 Bit 5V E<sup>2</sup>PROM

- Single 5-Volt Supply

- Fast Read Access Time: 250ns

- TTL Level Byte Write: 10ms Max.

- Internally Latched Address and Data in Write Cycle

- Automatic Erase Before Write

- Automatic Write Time-Out

- On-Chip False Write Protection

- TTL Compatible Inputs and Outputs

- JEDEC Approved Byte Wide Memory Pinout

- Compatible with Xicor 2816A

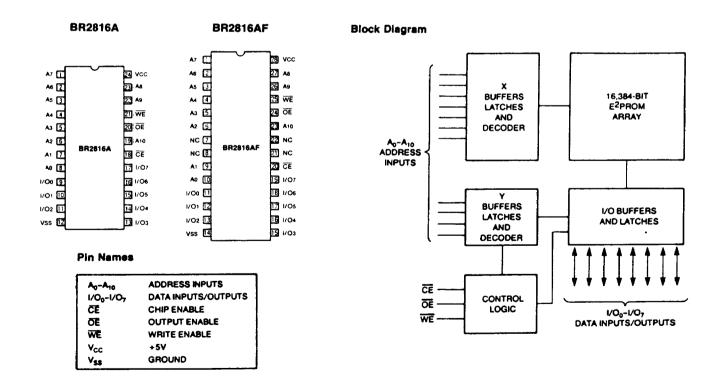

The BR2816A is a 5-Volt 2048  $\times$  8 bit electrically erasable programmable read only memory (E2PROM). It is remarkably easy to use, operating from a single 5-Volt power supply with read and write cycle timing very similar to that of a static RAM. Byte modification in the 5V programming mode is initiated with a 150ns TTL low level write signal. Address and data bus information is internally latched, freeing the system for other tasks during the write period. The BR2816A automatically erases the selected byte before writing and completes an erase/write cycle in a maximum of 10ms. Advanced power up/down protection mechanisms are incorporated in the BR2816A.

The BR2816A is the ideal device to use in applications that require a nonvolatile memory capable of insystem modification. The device's integrated features and simple microprocessor interface ensure both design ease and minimized board space requirements. Typical applications include self-calibrating equipment, tax table storage in point-of-sale terminals, key storage for data encryption, programmable character generators, and terrain mapping for military avionics.

ROHM CORPORATION, 8 Whatney, Irvine, CA 92718 (714) 855-2131 FAX: 714-855-1669

#### **DEVICE OPERATION**

#### Read

Data is read from the BR2816A by applying a high to WE, a low to CE and a low to OE. Data is available within t<sub>AA</sub> time from when the address inputs are valid, within t<sub>CE</sub> time after CE is brought low, or within t<sub>OE</sub> time after OE is brought low, whichever is later. The I/O pins remain in a high impedance state whenever OE or CE are high to eliminate bus contention in a system environment.

#### Write

In the 5-Volt programming mode, the write cycle is initiated by applying a low to both WE and CE while OE is high. The address inputs are latched into the device on the fal-ling edge of WE or CE (whichever is last) to specify the byte location that is to be written. Data on the I/O pins is then latched into the device by bringing either WE or CE high. Both addresses and data are latched in a brief 200ns interval using a 5V supply and TTL write signals. Once the data is latched, the BR2816A will automatically erase the selected byte and write the new data in less than 10ms. The system is freed for other functions during this period. The I/O pins will be in a high impedance state while the write operation is in progress. Thus, the system can determine the completion of the write operation by performing a read of the last location written and comparing the data read with the data previously written. If this mode of write verification is employed, it is recommended that resistive pull-ups to the V<sub>CC</sub> supply be incorporated on the outputs. In this case, the data read prior to completion of the write operation will be all 1's.

#### **MODE SELECTION**

| CE              | ŌĒ              | WE  | Mode                      | 1/0             | Power   |

|-----------------|-----------------|-----|---------------------------|-----------------|---------|

| VIH             | X               | X   | Standby                   | High Z          | Standby |

| VIL             | VIL             | VIH | Read                      | Dout            | Active  |

| VIL             | V <sub>IH</sub> | 7   | 5V Byte Write             | D <sub>IN</sub> | Active  |

| V <sub>IL</sub> | V <sub>IH</sub> | VIH | Read and Write<br>Inhibit | High Z          | Active  |

#### Standby

Power consumption may be reduced by approximately 55% by deselecting the device with a TTL high applied to  $\overline{\text{CE}}$ .

#### **Endurance**

The standard BR2816A is designed for applications requiring up to 10,000 write cycles per byte. The /E2 suffix versions are designed for applications requiring up to 100 write cycles per byte. (See Ordering Information.)

#### **False Write Protection**

Four mechanisms for power-up, power-down, and power-noise protection are incorporated in the BR2816A to prevent an unintentional write to the device.

#### V<sub>CC</sub> Level Detection

Whenever V<sub>CC</sub> is below 3.0 volts, write cycles to the device will automatically be inhibited.

#### Time Delay

During power-up the BR2816A automatically prevents any write operation for a period between 5 and 20ms after V<sub>CC</sub> reaches the V<sub>WI</sub> level. This will provide the system with sufficient time to bring WE or CE to a high level before a write can occur. Read cycles can be executed during the initialization period.

#### **OE** Gating

The BR2816A inhibits all write operations while the OE input is low.

## Noise Protected WE

A write pulse of less than 20ns duration on the WE input will not activate a write cycle.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Temperature Under Bias                                 | 55°C to +125°C |

|--------------------------------------------------------|----------------|

| Storage Temperature                                    | 65°C to +125°C |

| Voltage on any Pin with Respect to Ground <sup>2</sup> | 0.5V to +6V    |

| D.C. Output Current                                    | 5mA            |

# **Operating Range**

| Range    | Ambient Temperature |  |  |  |  |

|----------|---------------------|--|--|--|--|

| Standard | 0°C to 75°C         |  |  |  |  |

## DC OPERATING CHARACTERISTICS

Over Operating Range ,  $V_{CC} = 5V \pm 5\%$ , unless otherwise specified.

|                 |                                                | Lir  | nits |       | Test                                                                  |  |

|-----------------|------------------------------------------------|------|------|-------|-----------------------------------------------------------------------|--|

| Symbol          | Parameter                                      | Min. | Max. | Units | Conditions                                                            |  |

| V <sub>IL</sub> | Input Low Voltage                              |      | 0.8  | V     |                                                                       |  |

| V <sub>IH</sub> | Input High Voltage                             | 2.0  |      | V     |                                                                       |  |

| V <sub>OL</sub> | Output Low Voltage                             |      | 0.4  | ٧     | I <sub>OL</sub> = 2.1mA                                               |  |

| V <sub>OH</sub> | Output High Voltage                            | 2.4  |      | V     | $I_{OH} = -400\mu A$                                                  |  |

| V <sub>WI</sub> | V <sub>CC</sub> Trip Voltage for Write Inhibit | 3.0  | 3.5  | ٧     |                                                                       |  |

| lu              | Input Leakage Current                          |      | 10   | μА    | $V_{IN} = 0 \text{ to } 5.25V$                                        |  |

| lo              | Output Leakage Current                         |      | ±10  | μΑ    | $V_{OUT} = 0 \text{ to } 5.25V$                                       |  |

| lcc             | V <sub>CC</sub> Current (Active)               |      | 110  | mA    | CE = OE = V <sub>IL</sub><br>All I/O's = OPEN<br>Other Inputs = 5.25V |  |

| ISB             | V <sub>cc</sub> Current (Standby): Standard    |      | 40   | mA    | $\overline{CE} = V_{IH}, \overline{OE} = V_{IL}$                      |  |

#### CAPACITANCE

$T_A = 25^{\circ}C$ , f = 1.0 MHz,  $V_{CC} = 5V$

| Symbol           | Test                     | Max. | Unit | Conditions     |

|------------------|--------------------------|------|------|----------------|

| C <sub>1/O</sub> | Input/Output Capacitance | 10   | pF   | $V_{I/O} = 0V$ |

| C <sub>IN</sub>  | Input Capacitance        | 6    | pF   | $V_{IN} = 0V$  |

#### Notes

- Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and the

functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying any voltages higher than the rated maxima.

- 3. AC conditions of test: Input pulse levels 0 to 3.0V, input rise and fall times 10ns, input and output timing levels 1.5V, output load 1 TTL gate and C<sub>L</sub> = 100 pF.

- 4. WE is noise protected. A write pulse of less than 20ns duration will not activate a write cycle.

- 5. Data must be valid within 1  $\mu$ s after the initiation of a write cycle.

# **AC CHARACTERISTICS**<sup>3</sup>

Over Operating Range,  $V_{CC} = 5V \pm 5\%$ , unless otherwise specified.

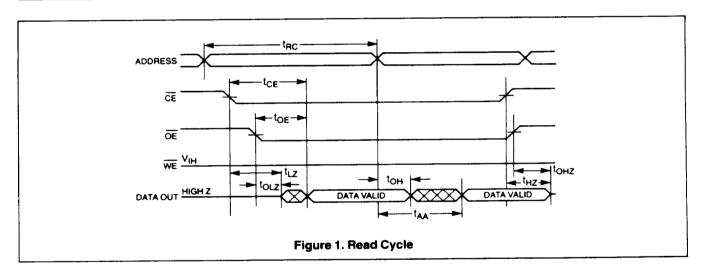

Read Cycle - See Figure 1.

|                 |                                                 |      | BR2816A<br>250<br>Limits |      | BR2816A<br>300<br>Limits |      | BR2816A<br>350<br>Limits |      | BR2816A<br>450<br>Limits |    |

|-----------------|-------------------------------------------------|------|--------------------------|------|--------------------------|------|--------------------------|------|--------------------------|----|

| Symbol          | Parameter                                       | Min. | Max.                     | Min. | Max.                     | Min. | Max.                     | Min. | Max.                     |    |

| t <sub>BC</sub> | Read Cycle Time                                 | 250  |                          | 300  |                          | 350  |                          | 450  |                          | ns |

| t <sub>CE</sub> | Chip Enable Access Time                         |      | 250                      |      | 300                      |      | 350                      |      | 450                      | ns |

| t <sub>AA</sub> | Address Access Time                             |      | 250                      |      | 300                      |      | 350                      |      | 450                      | ns |

| tOE             | Output Enable Access Time: Standard             |      | 100                      |      | 120                      |      | 135                      |      | 150                      | ns |

| t <sub>LZ</sub> | Chip Enable to Output in Low Z                  | 10   |                          | 10   |                          | 10   |                          | 10   |                          | ns |

| tHZ             | Chip Disable to Output in High Z:<br>Standard   | 10   | 100                      | 10   | 100                      | 10   | 100                      | 10   | 100                      | ns |

| toLZ            | Output Enable to Output in Low Z                | 10   |                          | 10   |                          | 10   |                          | 10   |                          | ns |

| tonz            | Output Disable to Output in High Z:<br>Standard | 10   | 70                       | 10   | 80                       | 10   | 100                      | 10   | 100                      | ns |

| toн             | Output Hold from Address Change                 | 20   |                          | 20   |                          | 20   |                          | 20   |                          | ns |

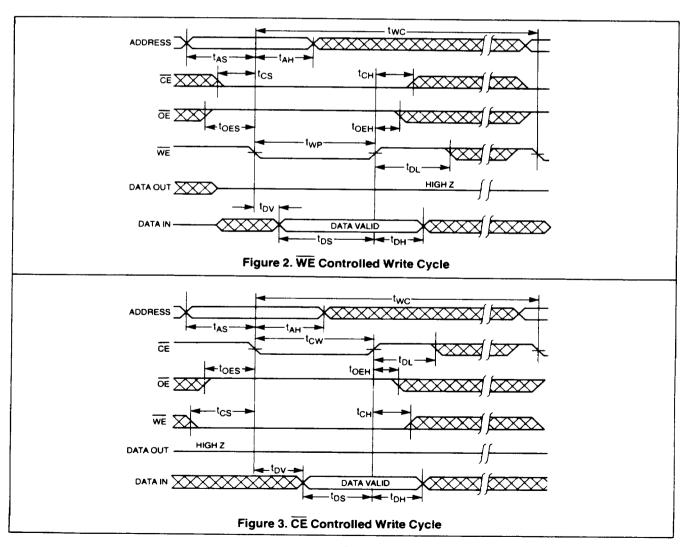

# Write Cycle – See Figures 2 and 3. 5-Volt Programming Mode

| Symbol            | Parameter                                 | Limits  |      |       |

|-------------------|-------------------------------------------|---------|------|-------|

|                   |                                           | Min.    | Max. | Units |

| twc               | Write Cycle Time                          | 10      |      | ms    |

| tas               | Address Setup Time                        | 10      |      | ns    |

| t <sub>AH</sub>   | Address Hold Time Standard                | 70      |      | ns    |

| t <sub>CS</sub>   | Write Setup Time                          | 0       |      | ns    |

| t <sub>CH</sub>   | Write Hold Time                           | 0       |      | ns    |

| tcw               | Chip Enable to End of Write Input         | 150     |      | ns    |

| toes              | Output Enable Setup Time                  | 10      |      | ns    |

| t <sub>OEH</sub>  | Output Enable Hold Time                   | Time 10 |      | ns    |

| twp-1             | Write Pulse Width                         | 150     |      | ns    |

| t <sub>DL</sub>   | Data Latch Time                           | 50      |      | ns    |

| t <sub>DV</sub> 5 | Data Valid Time                           |         | 1    | μS    |

| t <sub>DS</sub>   | Data Setup Time                           | 50      |      | ns    |

| t <sub>DH</sub>   | Data Hold Time                            | 10      |      | ns    |

| tinit             | Power-Up Initialization Period (See Text) | 5       | 20   | ms    |

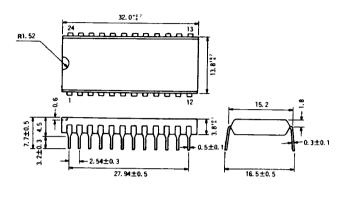

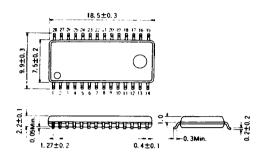

#### PACKAGE INFORMATION: UNIT IN MM.

#### **BR2816A**

DIP24pin

#### **BR2816AF**

MF28pin

#### **ORDERING INFORMATION:**

| Part Number                   | Access<br>Time (ns) | Temperature<br>Range (°C) | Endurance<br>(cycles) | Package       |

|-------------------------------|---------------------|---------------------------|-----------------------|---------------|

| BR2816A -250<br>BR2816AF -250 | 250                 | 0 - 70                    | 10,000                | DIP24<br>MF28 |

| BR2816A -300<br>BR2816AF -300 | 300                 | 0 - 70                    | 10,000                | DIP24<br>MF28 |

| BR2816A -350<br>BR2816AF -350 | 350                 | 0 - 70                    | 10,000                | DIP24<br>MF28 |

| BR2816A -450<br>BR2816AF -450 | 450                 | 0 - 70                    | 10,000                | DIP24<br>MF28 |

ROHM CORP. reserves the right to make changes to any product herein to improve reliability, function or design. ROHM CORP. does not assume any liability arising out of the application or use of any product described herein, neither does it convey any license under its patent right nor the rights of others.

ROHM CORP. 8 Whatney Irvine, CA 92718 (714) 855-2131 FAX: 714-855-1669

ROHM CORPORATION, February 1989 Printed in U.S.A.

014229 🗶 \_ 🏅