|                                                                                    |                                                      |                 |               |                                          |                                              | 7                           |                         | ·R           | REVISI  | ONS                         |              |                      |                      |                         |                                  |                  |                               |                       |               | •             |

|------------------------------------------------------------------------------------|------------------------------------------------------|-----------------|---------------|------------------------------------------|----------------------------------------------|-----------------------------|-------------------------|--------------|---------|-----------------------------|--------------|----------------------|----------------------|-------------------------|----------------------------------|------------------|-------------------------------|-----------------------|---------------|---------------|

| LTR                                                                                |                                                      |                 |               |                                          | D                                            | ESCR                        | IPTIO                   |              |         | -                           |              |                      | D/                   | ATE (Y                  | R-MO-D                           | A)               |                               | APPR                  | OVED          |               |

| Α                                                                                  | Add '                                                | "Y" pa          | ckage         | and ur                                   | odated                                       | boiler                      | plate                   |              |         | -                           |              |                      |                      |                         |                                  |                  | M. A. Frye                    |                       |               |               |

| В                                                                                  | 1                                                    | ated bo         |               |                                          |                                              |                             |                         | and t        | 5-d/E [ | DEV - 9                     | ala          |                      | 96-04-12<br>97-12-04 |                         |                                  |                  |                               | mond                  |               | in            |

|                                                                                    |                                                      |                 |               |                                          |                                              |                             |                         |              |         |                             |              |                      |                      |                         |                                  |                  |                               |                       |               |               |

|                                                                                    |                                                      |                 |               |                                          |                                              |                             |                         |              |         |                             |              |                      |                      |                         |                                  |                  |                               |                       |               |               |

| REV<br>SHEET                                                                       | B<br>35                                              | B<br>36         | B<br>37       | B<br>38                                  | B<br>39                                      | B<br>40                     | B<br>41                 |              |         |                             |              |                      |                      |                         |                                  |                  |                               |                       |               |               |

| SHEET                                                                              | 35<br>B                                              | 36<br>B         | 37<br>B       | 38<br>B                                  | 39<br>B                                      | 40<br>B                     |                         | В            | В       | В                           | В            | В                    | В                    | В                       | В                                | В                | В                             | В                     | В             | В             |

| SHEET<br>REV<br>SHEET                                                              | 35<br>B<br>15                                        | 36              | 37            | 38<br>B<br>18                            | 39<br>B<br>19                                | 40                          | 41<br>B<br>21           | 22           | 23      | 24                          | 25           | 26                   | 27                   | 28                      | 29                               | 30               | 31                            | 32                    | 33            | 34            |

| SHEET                                                                              | 35<br>B<br>15<br>S                                   | 36<br>B         | 37<br>B       | 38<br>B<br>18<br>RE\                     | 39<br>B<br>19                                | 40<br>B                     | 41<br>B<br>21<br>B      | 22<br>B      | 23<br>B | 24<br>B                     | 25<br>B      | 26<br>B              | 27<br>B              | 28<br>B                 | 29<br>B                          | 30<br>B          | 31<br>B                       | 32<br>B               | 33<br>B       | 34<br>B       |

| SHEET REV SHEET REV STATU                                                          | 35<br>B<br>15<br>S                                   | 36<br>B<br>16   | 37<br>B       | 38<br>B<br>18<br>RE\<br>SHE<br>PRE<br>Ga | 39<br>B<br>19<br>/<br>EET<br>PARED           | B 20                        | 41<br>B<br>21           | 22           | 23      | 24                          | 25<br>B<br>5 | 26<br>B<br>6         | 27<br>B<br>7         | 28<br>B<br>8            | 29<br>B<br>9                     | 30               | 31<br>B<br>11                 | 32<br>B<br>12         | 33<br>B<br>13 | 34<br>B       |

| SHEET REV SHEET REV STATU OF SHEETS PMIC N/A STAI MICRO DRA THIS DRAWNI FOR U DEPA | 35 B 15 S NDA CIR WIN NG IS A SE BY A RTMEN          | 36 B 16 RD RCUI | 37<br>B<br>17 | 38 B 18 RE\ SHE PRE Ga CHE Jef           | B 19 / EET PARED ary L. G CKED I f Bowlin    | B 20 BY ross BY Frye        | 41<br>B<br>21<br>B<br>1 | 22<br>B<br>2 | 23<br>B | 24<br>B<br>4                | 25<br>B<br>5 | 26<br>B<br>6<br>DEFE | 27 B 7 NSE S COL     | B<br>8<br>UPPL<br>UMBL  | 29<br>B<br>9<br>.Y CEN<br>JS, ON | 30<br>B<br>10    | 31<br>B<br>11<br>COLU<br>3216 | 32<br>B<br>12<br>MBUS | 33<br>B<br>13 | 34<br>B<br>14 |

| SHEET REV SHEET REV STATU OF SHEETS PMIC N/A STA MICRO DRA THIS DRAWN              | 35 B 15 S NDA OCIR AWIN NG IS A' SE BY RTMEN NCIES ( | 36 B 16 RD RCUI | 37<br>B<br>17 | 38 B 18 RE\ SHE PRE Ga CHE Jef APPI Mic  | 39 B 19 / EET PARED ATT L. G CKED I F Bowlin | BY Pross BY Frye  APPRO95-1 | 41<br>B<br>21<br>B<br>1 | 22<br>B<br>2 | 23<br>B | 24<br>B<br>4<br>MIC<br>64 > | 25<br>B<br>5 | 26 B 6 DEFE          | 27 B 7 NSE S COL     | B<br>8<br>SUPPL<br>UMBU | 29<br>B<br>9<br>.Y CEN<br>JS, ON | B 10 NTER HIO 4: | 31<br>B<br>11<br>COLU<br>3216 | 32<br>B<br>12<br>MBUS | 33<br>B<br>13 | 34<br>B<br>14 |

DSCC FORM 2233

APR 97

<u>DISTRIBUTION STATEMENT A</u>. Approved for public release; distribution is unlimited.

5962-E059-98

| 1   | S | ^ | $\cap$ | P | F |

|-----|---|---|--------|---|---|

| - 1 | • | · | v      | г | ᆮ |

- 1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V), and nontraditional performance environment (device class N). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN. For device class N, the user is cautioned to assure that the device is appropriate for the application environment.

- 1.2 PIN. The PIN shall be as shown in the following example:

| 5962        | -            | 95609 | <u>01</u>   | Q           | <u>X</u>    | X           |

|-------------|--------------|-------|-------------|-------------|-------------|-------------|

| *           | *            |       | *           | *           | *           | *           |

| *           | *            |       | *           | *           | *           | *           |

| *           | *            |       | *           | *           | *           | *           |

| Federal     | RHA          | •     | Device      | Device      | Case        | Lead        |

| stock class | designator   |       | type        | class       | outline     | finish      |

| designator  | (see 1.2.1)  |       | (see 1.2.2) | designator  | (see 1.2.4) | (see 1.2.5) |

| \           |              |       | , ,         | (see 1.2.3) | , ,         | ,           |

|             | V            |       |             |             |             |             |

| Dr          | awing number |       |             |             |             |             |

- 1.2.1 RHA designator. Device classes N, Q, and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 Device type(s). The device type(s) shall identify the circuit function as follows:

Device type

Generic number

Circuit function

01

ABT3614

64 X 36 X 2 clocked FIFO

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

M Vendor self-certification to the requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A

N Certification and qualification to MIL-PRF-38535 with a non-traditional performance environment 1/

Q or V Certification and qualification to MIL-PRF-38535

1.2.4 Case outline(s). The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style             |

|----------------|------------------------|------------------|---------------------------|

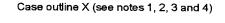

| X              | See figure 1           | 120              | Plastic quad flat package |

| Υ              | See figure 1           | 132              | Ceramic quad flat package |

- 1.2.5 <u>Lead finish</u>. The lead finish is as specified in MIL-PRF-38535 for device classes N, Q, and V or MIL-PRF-38535, appendix A for device class M.

- 1.2.5.1 <u>Lead finish D</u>. Lead finish D shall be designated by a single letter as follows:

<u>Finish letter</u> <u>Process</u>

D Palladium

1/ Any device outside the traditional performance environment, i.e., (Plastic Encapsulated Microcircuit).

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-95609 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>B | SHEET 2    |

DSCC FORM 2234 APR 97

**9004708 0033096 608**

| 1.3 Absolute maximum ratings. 2/3/4/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                   |                                                                                                                                                                                  |                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Supply voltage range (V <sub>CC</sub> )  DC input voltage range (I/O ports) (V <sub>IN</sub> )  DC output voltage range (V <sub>OUT</sub> )  DC output current (I <sub>O</sub> ) (per output)(V <sub>O</sub> = 0.0 V to V <sub>CC</sub> )  DC input clamp current (I <sub>IK</sub> ) (V <sub>IN</sub> < 0.0 V or V <sub>IN</sub> > V <sub>CC</sub> )  DC output clamp current (I <sub>OK</sub> ) (V <sub>OUT</sub> < 0.0 V or V <sub>OUT</sub> > Storage temperature range (T <sub>STG</sub> )  Lead temperature (soldering, 10 seconds)  Thermal resistance, junction-to-case (O <sub>JC</sub> )  Junction temperature (T <sub>J</sub> )  Maximum power dissipation (P <sub>D</sub> ) at T <sub>A</sub> = +55°C in still air V <sub>CC</sub> current (I <sub>VCC</sub> )  Ground current (I <sub>GND</sub> ) | V <sub>CC</sub> )                                 | -0.5 V dc to +7.0 V dc -0.5 V dc to V <sub>CC</sub> + 0.6 -0.5 V dc to V <sub>CC</sub> + 0.6 ±50 mA ±20 mA ±50 mA -65°C to +150°C +300°C 3.3°C/W +175°C 1.8 W 6/ ±400 mA ±400 mA | 5 V dc <u>5</u> /<br>5 V dc <u>5</u> / |

| 1.4 Recommended operating conditions. 3/4/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                   |                                                                                                                                                                                  |                                        |

| Supply voltage range (V <sub>CC</sub> )  Maximum low level input voltage (V <sub>IL</sub> )  Minimum high level input voltage (V <sub>IH</sub> )  Maximum high level output current (I <sub>OH</sub> )  Maximum low level output current (I <sub>OL</sub> )  Case operating temperature range (I <sub>C</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                   | +4.5 V dc to +5.5 V dc +0.8 V +2.0 V -4.0 mA +8.0 mA -55°C to +125°C                                                                                                             | c                                      |

| 1.5 <u>Digital logic testing for device classes N, Q, and V</u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |                                                                                                                                                                                  |                                        |

| Fault coverage measurement of manufacturing logic tests (MIL-STD-883, test method 5012)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   | XX percent 7/                                                                                                                                                                    |                                        |

| 2. APPLICABLE DOCUMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |                                                                                                                                                                                  |                                        |

| 2.1 <u>Government specification, standards, and handbooks</u> . The this drawing to the extent specified herein. Unless otherwise specified the Department of Defense Index of Specifications and Standar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ified, the issues of                              | these documents are those                                                                                                                                                        | listed in the issue                    |

| SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                   |                                                                                                                                                                                  |                                        |

| DEPARTMENT OF DEFENSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                   |                                                                                                                                                                                  |                                        |

| MIL-PRF-38535 - Integrated Circuits, Manufacturing, Gene                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ral Specification fo                              | or.                                                                                                                                                                              |                                        |

| STANDARDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |                                                                                                                                                                                  |                                        |

| DEPARTMENT OF DEFENSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                   |                                                                                                                                                                                  |                                        |

| MIL-STD-883 - Test Methods and Procedures for Microel<br>MIL-STD-973 - Configuration Management.<br>MIL-STD-1835 - Microcircuit Case Outlines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ectronics.                                        |                                                                                                                                                                                  |                                        |

| HANDBOOKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |                                                                                                                                                                                  |                                        |

| DEPARTMENT OF DEFENSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                   |                                                                                                                                                                                  |                                        |

| MIL-HDBK-103 - List of Standard Microcircuit Drawings (S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SMD's).                                           |                                                                                                                                                                                  |                                        |

| 2/ Stresses above the absolute maximum rating may cause permaximum levels may degrade performance and affect reliability.  3/ Unless otherwise noted, all voltages are referenced to GND.  The limits for the parameters specified herein shall apply over 55°C to +125°C.  The input negative voltage rating may be exceeded provided to the maximum package power dissipation is calculated using mils.  Z/ Values will be added when they become available.                                                                                                                                                                                                                                                                                                                                                | y.<br>the full specified V<br>that the input clam | CC range and case temper                                                                                                                                                         | rature range of -                      |

| STANDARD<br>MICROCIRCUIT DRAWING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SIZE<br><b>A</b>                                  |                                                                                                                                                                                  | 5962-95609                             |

| DEFENSE SUPPLY CENTER COLUMBUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   | DEMICIONAL EME                                                                                                                                                                   |                                        |

9004708 0033097 544

**REVISION LEVEL**

В

SHEET

**COLUMBUS, OHIO 43216-5000**

## **HANDBOOKS**

#### DEPARTMENT OF DEFENSE

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbooks are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

## 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device classes N, Q, and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes N, Q, and V or MIL-PRF-38535, appendix A and herein for device class M.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

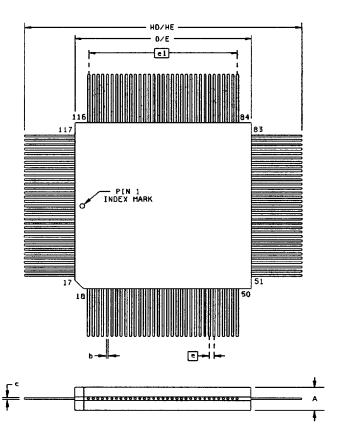

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

- 3.2.3 <u>Truth table(s)</u>. The truth table(s) shall be as specified on figure 3.

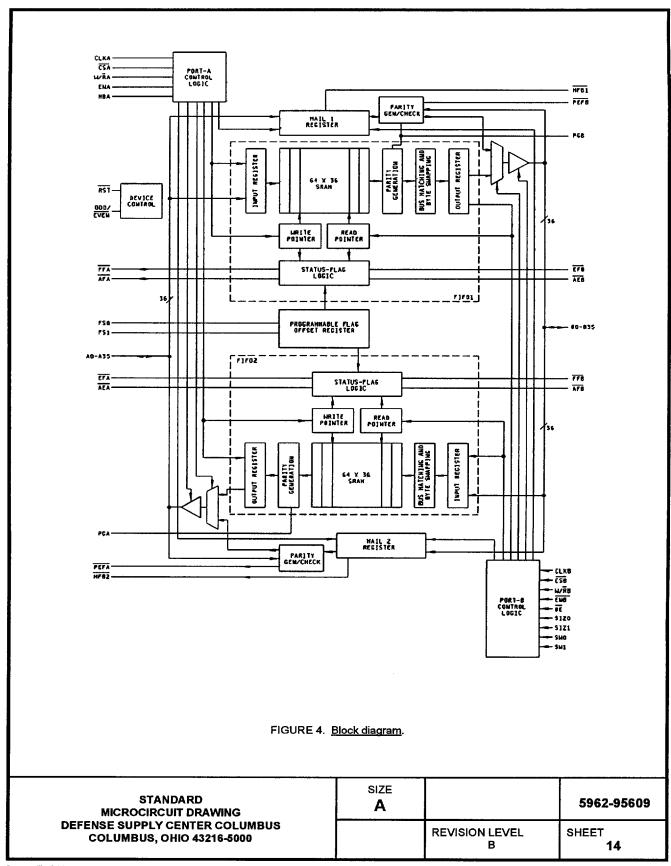

- 3.2.4 Block or logic diagram(s). The block or logic diagram(s) shall be as specified on figure 4.

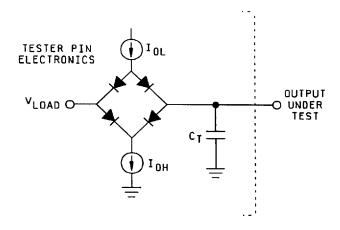

- 3.2.5 <u>Test circuit and switching waveforms</u>. The test circuit and switching waveforms shall be as specified on figure 5.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-HDBK-103. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes N, Q, and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

- 3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes N, Q, and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

- 3.6 <u>Certificate of compliance</u>. For device classes N, Q, and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes N, Q, and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43216-5000

SIZE

A

FREVISION LEVEL

B

SHEET

4

DSCC FORM 2234 APR 97

9004708 0033098 480

|                                                                               |                                         | TABLE I. Electrical per                                                                                        | formance character                                                                                                         | istics.         |                      |     |               |          |

|-------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|-----|---------------|----------|

| Test                                                                          | Symbol                                  | Test conditior<br>-55°C ≤ T <sub>C</sub> ≤ +<br>+4.5 V ≤ V <sub>CC</sub> ≤                                     | 125°C                                                                                                                      | Device<br>types | Group A subgroups 2/ |     | ts <u>3</u> / | Unit     |

|                                                                               |                                         | unless otherwise                                                                                               | specified                                                                                                                  |                 | <u> </u>             | Min | Max           |          |

| High level output voltage                                                     | V <sub>ОН</sub>                         | For all inputs affecting outputest, V <sub>IN</sub> = 2.0 V or 0.8 V,I <sub>O</sub><br>V <sub>CC</sub> = 4.5 V |                                                                                                                            | 01              | 1, 2, 3              | 2.4 |               | <b>V</b> |

| Low level output<br>voltage                                                   | V <sub>OL</sub>                         |                                                                                                                | or all inputs affecting output under est, V <sub>IN</sub> = 2.0 V or 0.8 V,I <sub>OL</sub> = 8 mA, V <sub>CC</sub> = 4.5 V |                 |                      |     | 0.5           | ٧        |

| Input current                                                                 | <u> </u><br>  <u>4</u> /                | For input under test, $V_{ } = V_{ }$<br>$V_{ } = 5.5 \text{ V}$                                               | CC or GND,                                                                                                                 | 01              | 1, 2, 3              |     | <u>+</u> 50   | μА       |

| Three-state output<br>leakage current high                                    | lozh<br><u>5</u> /                      | V <sub>OUT</sub> = V <sub>CC</sub> , V <sub>CC</sub> = 5.5 V                                                   | "                                                                                                                          |                 |                      |     | 50            | μА       |

| Three-state output leakage current low                                        | l <sub>OZL</sub><br><u>5</u> /          | V <sub>OUT</sub> = GND, V <sub>CC</sub> = 5.5 V                                                                |                                                                                                                            | 01              | 1, 2, 3              |     | -50           | μА       |

| Quiescent supply current, outputs                                             | lcc                                     | For all inputs, Output                                                                                         | Outputs high                                                                                                               | 01              | 1, 2, 3              |     | 30            | mA       |

| high                                                                          |                                         | = port B, I <sub>OUT</sub> = 0 A,<br>V <sub>CC</sub> = 5.5 V                                                   | Outputs low                                                                                                                | _               |                      |     | 130           |          |

|                                                                               | · - · · · · - · · · · · · · · · · · · · | $V_{IN} = V_{CC} - 0.2 \text{ V or GND}$                                                                       | Outputs disabled                                                                                                           |                 |                      |     | 30            |          |

| Input capacitance                                                             | CIN                                     | T <sub>C</sub> = +25°C, V <sub>BIAS</sub> = 0 V<br>V <sub>CC</sub> = 5.0 V, See 4.4.1e                         | Control inputs                                                                                                             | 01              | 4                    |     | 6             | рF       |

| I/O capacitance                                                               | c <sub>I/O</sub>                        | V <sub>CC</sub> = 5.0 V, See 4.4.1e                                                                            | A or B ports                                                                                                               | ]               | 4                    |     | 9             | ]        |

| Functional tests                                                              | <u>6</u> /                              | $V_{IH}$ = 2.0 V, $V_{IL}$ = 0.8 V, ve<br>$V_{CC}$ = 4.5 V and 5.5 V, 4.4                                      | rify output V <sub>O</sub> ,<br>.1c                                                                                        | 01              | 7, 8A, 8B            | L   | Н             |          |

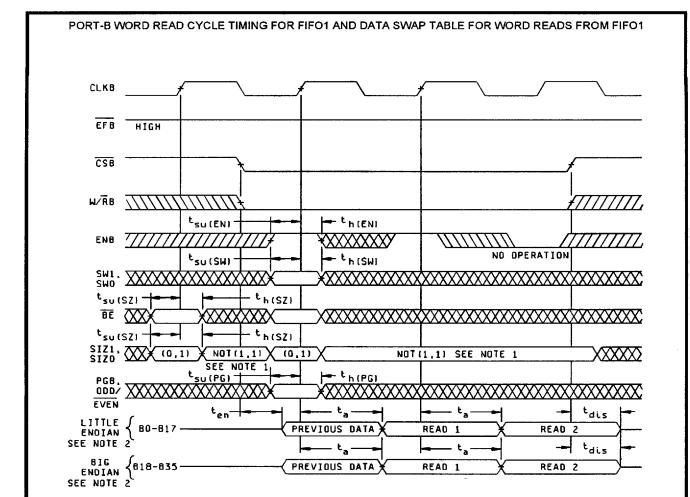

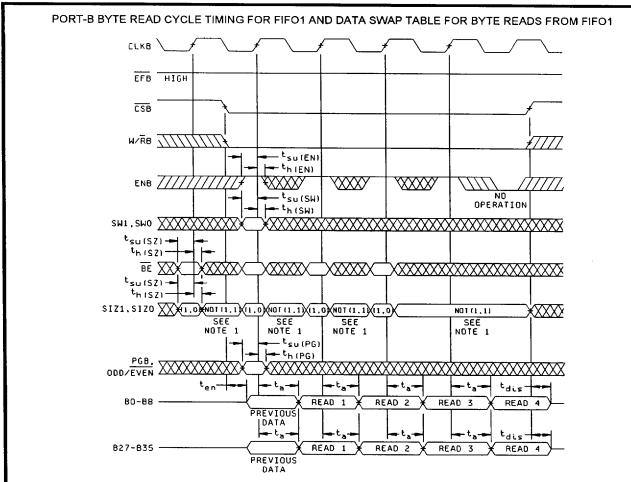

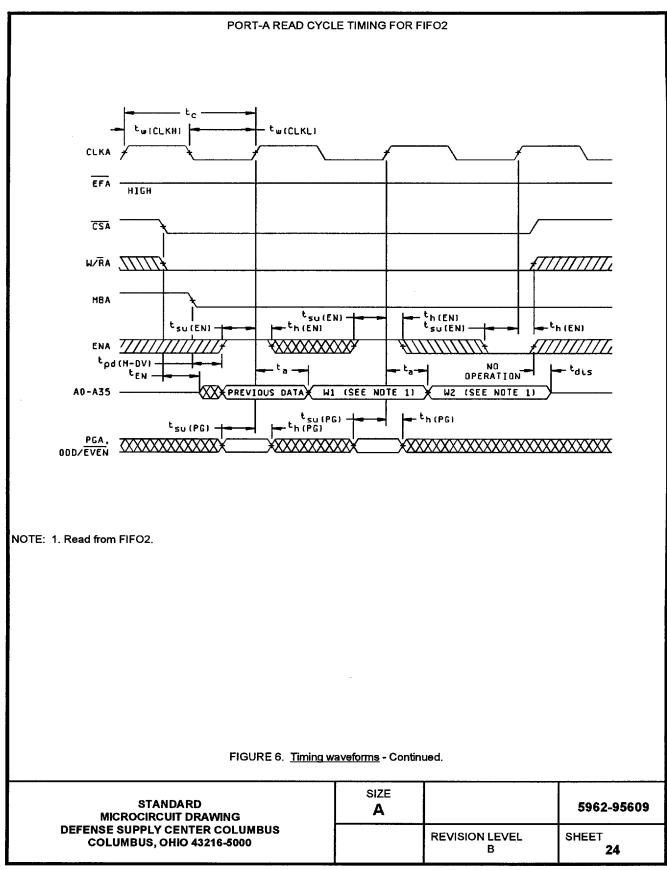

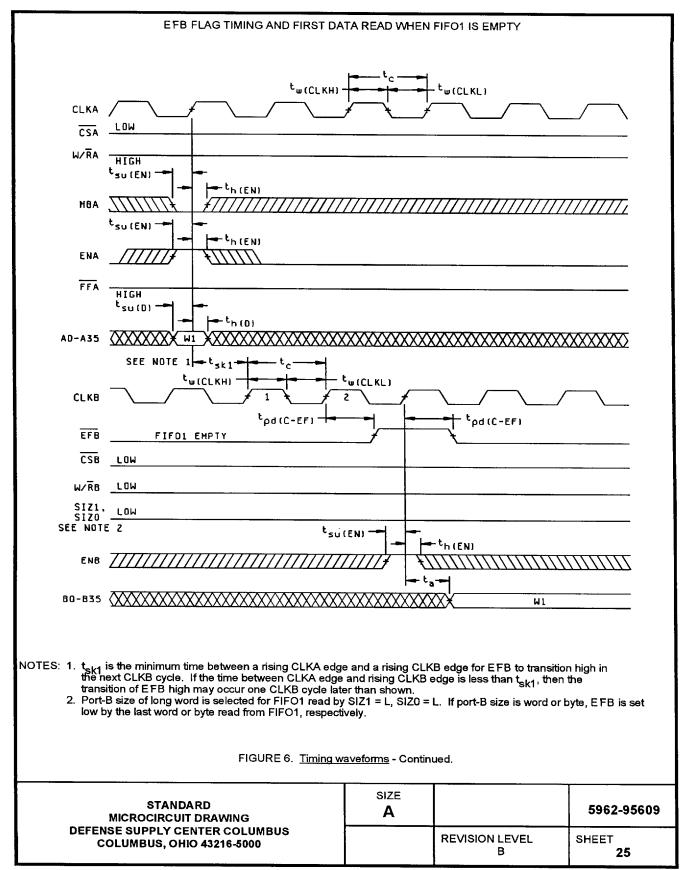

| Clock frequency<br>CLKA or CLKB                                               | <sup>f</sup> clock                      | $C_L = 20$ pF minimum, $V_{CC}$ see figures 5 and 6 as applic                                                  | = 4.5 V and 5.5 V,<br>cable                                                                                                | 01              | 9, 10, 11            |     | 50            | MHz      |

| Clock cycle time<br>CLKA or CLKB                                              | <sup>t</sup> c                          |                                                                                                                |                                                                                                                            | 01              | 9, 10, 11            | 20  |               | ns       |

| Pulse duration,<br>CLKA and CLKB<br>high or low                               | <sup>t</sup> w                          |                                                                                                                |                                                                                                                            | 01              | 9, 10, 11            | 8   |               |          |

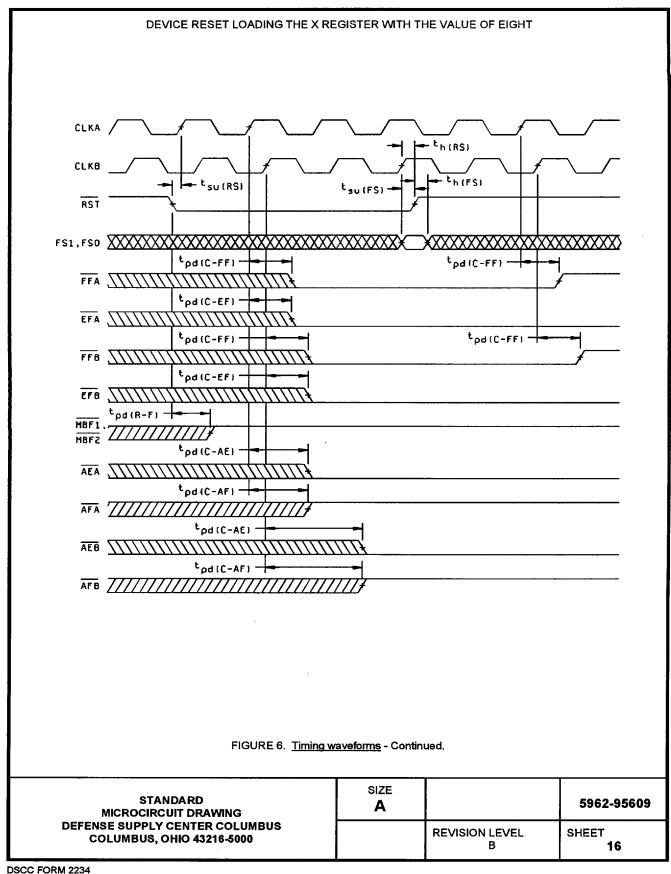

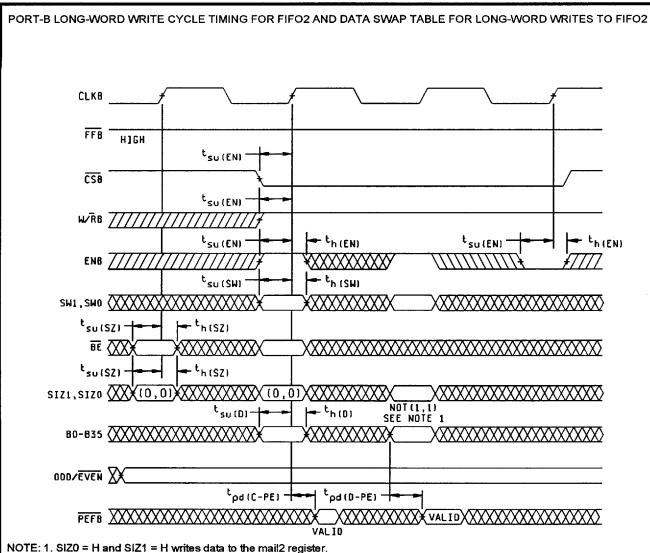

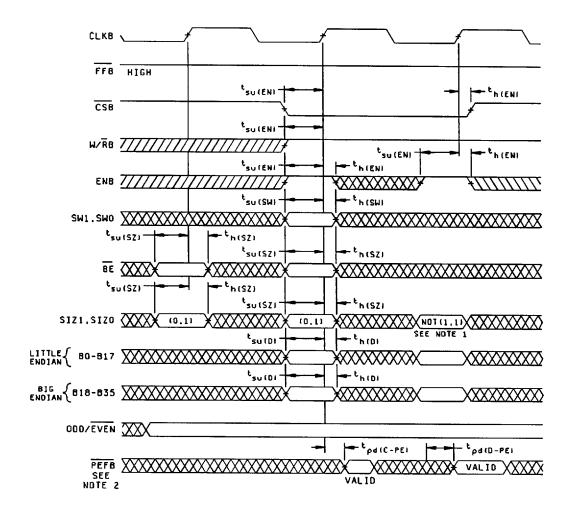

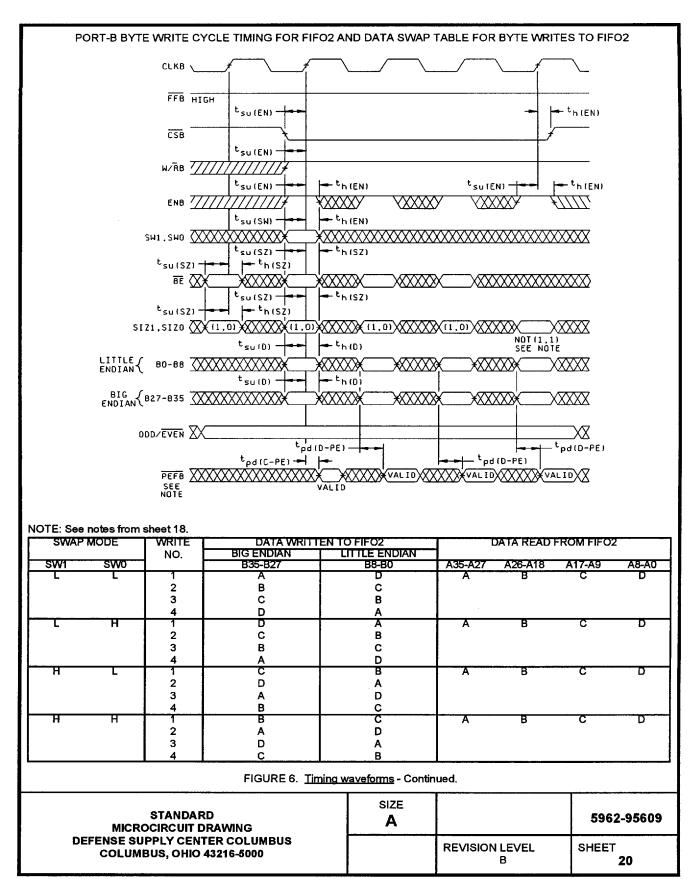

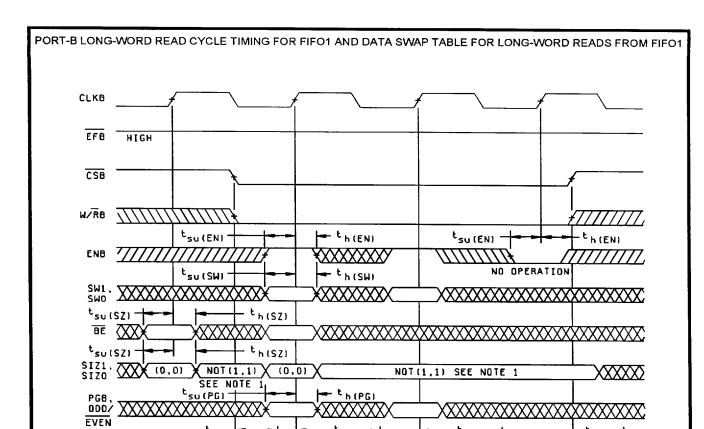

| Setup time, A0-A35<br>before CLKA1, and<br>B0-B35 before CLKB1                | <sup>t</sup> su(D)                      |                                                                                                                |                                                                                                                            | 01              | 9, 10, 11            | 5   |               |          |

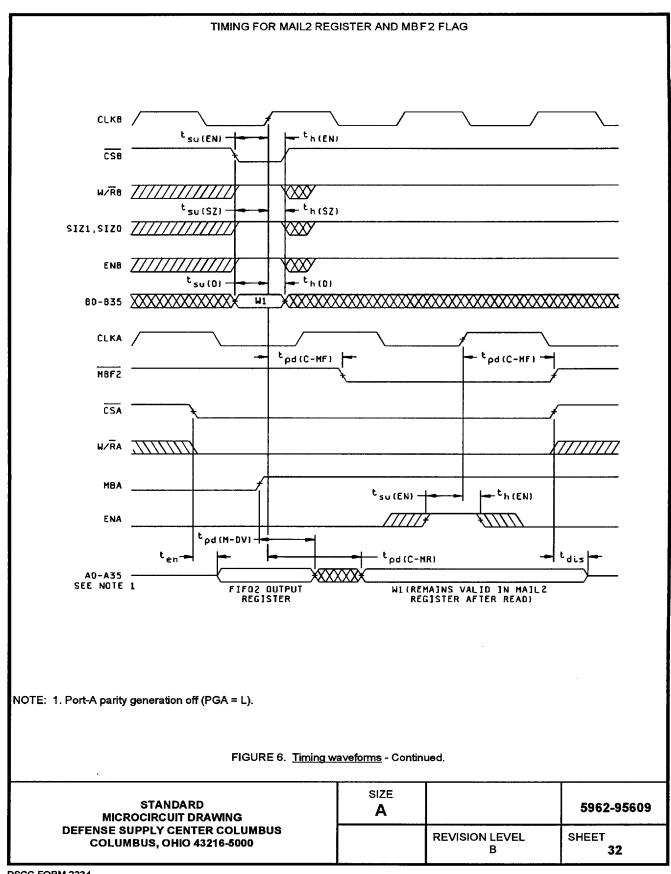

| Setup time, CSA, ENA<br>and MBA before<br>CLKA1; CSB, and<br>ENB before CLKB  | <sup>t</sup> su(EN)                     |                                                                                                                |                                                                                                                            | 01              | 9, 10, 11            | 5   |               |          |

| Setup time,<br>W/RA to CLKA1, and<br>W/RB to CLKB1                            | <sup>t</sup> su(W)                      |                                                                                                                |                                                                                                                            | 01              | 9, 10, 11            | 10  |               |          |

| See footnotes at end of t                                                     | able.                                   |                                                                                                                |                                                                                                                            |                 |                      |     |               |          |

| MICRO                                                                         | STANDARD<br>MICROCIRCUIT DRAWING        |                                                                                                                |                                                                                                                            |                 |                      |     | 5962-         | 95609    |

| MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 |                                         |                                                                                                                |                                                                                                                            | REVISIO         | N LEVEL<br>B         | SH  | IEET 5        |          |

| Test                                                                                        | Symbol              | Test conditions <u>1</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C                                              | Device<br>types | Group A<br>subgroups | Limits 3/ |     | Unit |

|---------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------|-----------------|----------------------|-----------|-----|------|

|                                                                                             |                     | -55° C ≤ T <sub>C</sub> ≤ +125° C<br>+4.5 V ≤ V <sub>CC</sub> ≤ +5.5 V<br>unless otherwise specified       | .,,,,,,         | <u>2</u> /           | Min       | Max |      |

| Setup time, SIZ0, SIZ1, and<br>BE before CLKB1                                              | <sup>t</sup> su(SZ) | C <sub>L</sub> = 20 pF minimum,<br>V <sub>CC</sub> = 4.5 V and 5.5 V,<br>See figures 5 and 6 as applicable | 01              | 9, 10, 11            | 5         |     | ns   |

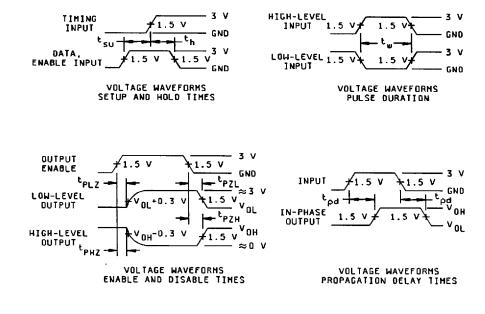

| Setup time,<br>RST low before CLKA1<br>or CLKB1                                             | tsu(RS)             | See figures 5 and 6 as applicable                                                                          | 01              | 9, 10, 11            | 6         |     |      |

| Setup time, FS0 and FS1<br>before RST high                                                  | <sup>t</sup> su(FS) |                                                                                                            | 01              | 9, 10, 11            | 6         |     |      |

| Setup time, SW0 and SW1<br>before CLKB1                                                     | <sup>t</sup> su(SW) |                                                                                                            | 01              | 9, 10, 11            | 7         |     |      |

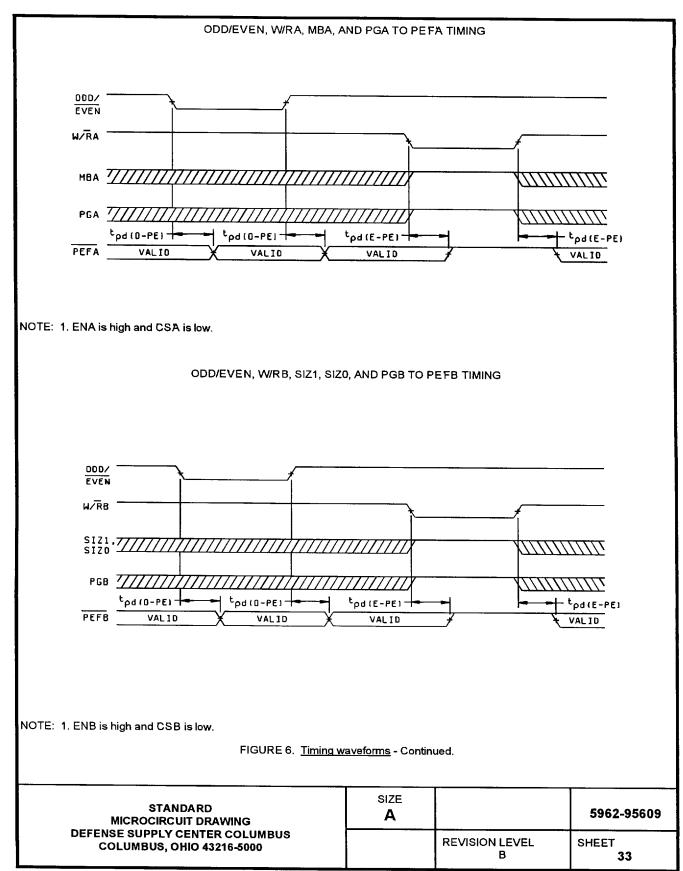

| Setup time,ODD/EVEN and<br>PGA before CLKA1;<br>ODD/EVEN and PGB<br>before CLKB1            | tsu(PG)<br>8/       |                                                                                                            | 01              | 9, 10, 11            | 6         |     |      |

| Hold time, A0-A35 after<br>CLKA↑ and B0-B35 after<br>CLKB↑                                  | th(D)               |                                                                                                            | 01              | 9, 10, 11            | 1         |     |      |

| Hold time, CSA, W/RA,<br>ENA and MBA after CLKA I<br>and CSB, W/RB, and ENB<br>after CLKB I | <sup>t</sup> h(EN)  |                                                                                                            | 01              | 9, 10, 11            | 1         |     |      |

| Hold time, SIZ0, SIZ1, and<br>BE after CLKB⊺                                                | <sup>t</sup> h(SZ)  |                                                                                                            | 01              | 9, 10, 11            | 2         |     |      |

| Hold time, SW0 and SW1<br>after CLKB1                                                       | t <sub>h</sub> (SW) |                                                                                                            | 01              | 9, 10, 11            | 7         |     |      |

| Hold time, ODD/EVEN and PGA after CLKA1; ODD/EVEN and PGB after CLKB1                       | h(PG)               |                                                                                                            | 01              | 9, 10, 11            | 0         |     |      |

| Hold time, RST low after<br>CLKA1 or CLKB1                                                  | th(RS)              |                                                                                                            | 01              | 9, 10, 11            | 6         |     |      |

| Hold time, FS0 and FS1<br>after RST high                                                    | th(FS)              |                                                                                                            | 01              | 9, 10, 11            | 4         |     |      |

| Skew time, between CLKA†<br>and CLKB† for EFA, EFB,<br>FFA, AND FFB                         | tsk(1)<br>9/        |                                                                                                            | 01              | 9, 10, 11            | 8         |     |      |

STANDARD

MICROCIRCUIT DRAWING

DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43216-5000

SIZE 5962-95609

REVISION LEVEL SHEET 6

| Test                                                                                                  | Symbol                | Test conditio                                                                              |                             | Device<br>types | Group A<br>subgroups | Limi | ts <u>3</u> / | Unit |

|-------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------|-----------------------------|-----------------|----------------------|------|---------------|------|

|                                                                                                       |                       | +4.5 V ≤ V <sub>CC</sub><br>unless otherwise                                               | ≤ +5.5 V                    | 9,500           | 2/                   | Min  | Max           |      |

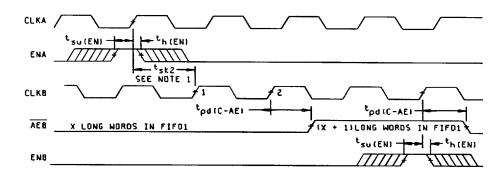

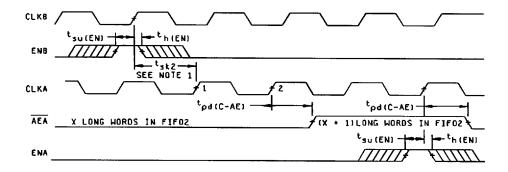

| Skew time, between CLKAT and CLKBT for AEA, AEB, AFA, and AFB                                         | tsk(2)<br>9/          | C <sub>L</sub> = 20 pF minimum<br>V <sub>CC</sub> = 4.5 V and 5.5<br>See figures 5 and 6 a | n,<br>i V,<br>as applicable | 01              | 9, 10, 11            | 16   |               | ns   |

| Access time, CLKA1 to A0-<br>A35 and CLKB1 to B0-<br>B35                                              | t <sub>a</sub>        |                                                                                            |                             | 01              | 9, 10, 11            | 2    | 12            |      |

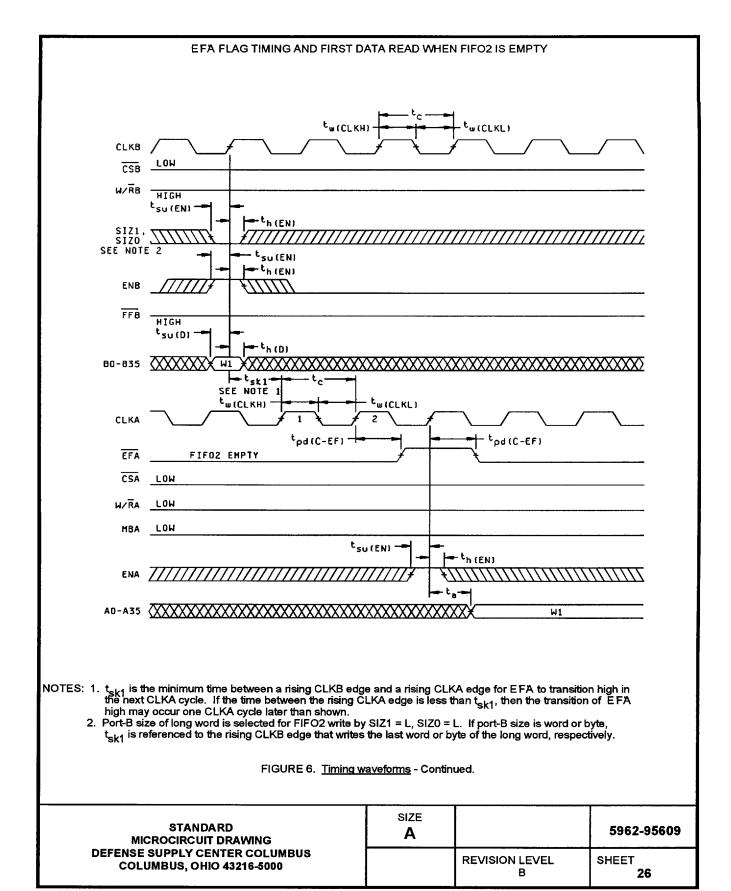

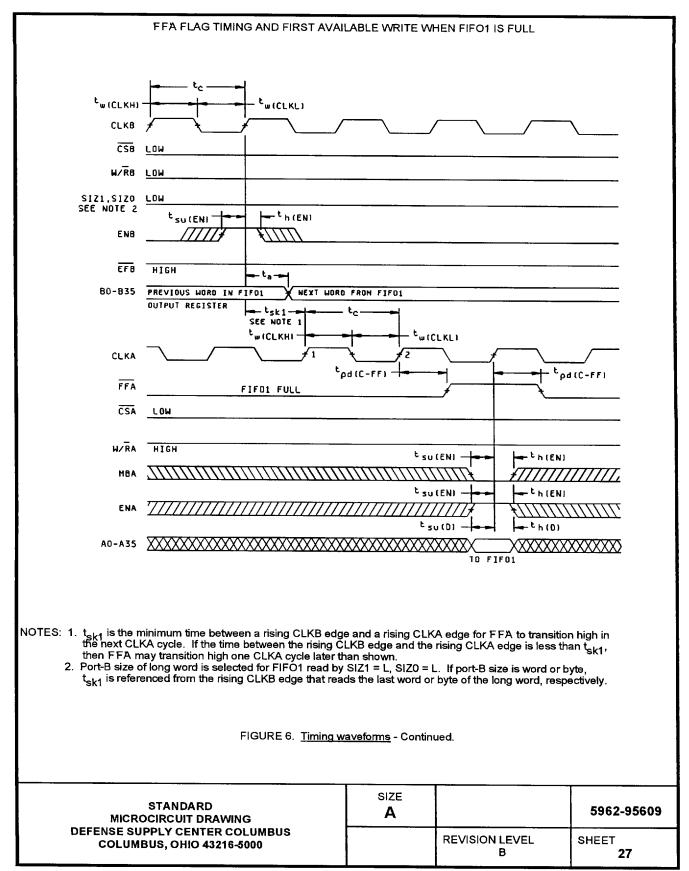

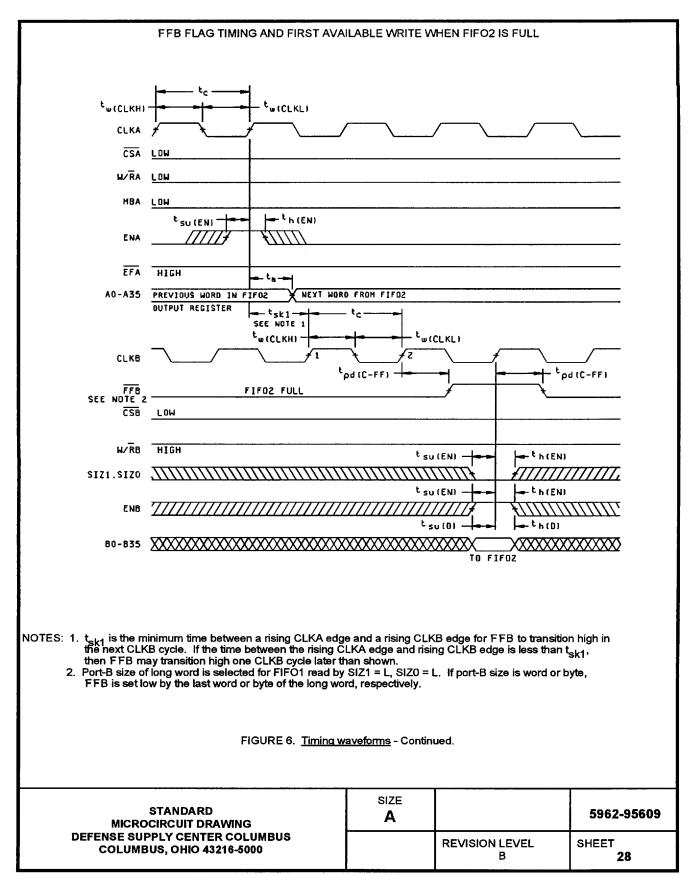

| Propagation delay time,<br>CLKA: to FFA and CLKB:<br>to FFB                                           | <sup>t</sup> pd(C-FF) |                                                                                            |                             | 01              | 9, 10, 11            |      |               |      |

| Propagation delay time,<br>CLKA: to EFA and CLKB:<br>to EFB                                           | <sup>t</sup> pd(C-EF) |                                                                                            |                             | 01              | 9, 10, 11            |      |               |      |

| Propagation delay time,<br>CLKA1 to AEA and CLKB1<br>to AEB                                           | <sup>t</sup> pd(C-AE) |                                                                                            |                             | 01              | 9, 10, 11            | 2    | 12            |      |

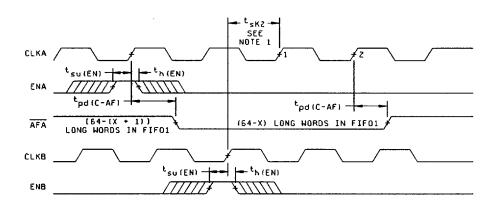

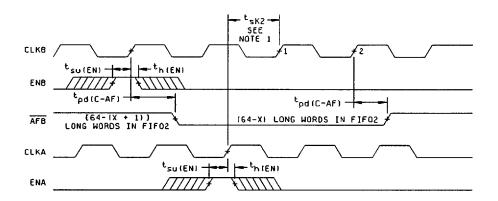

| Propagation delay time,<br>CLKA1 to AFA and CLKB1<br>to AFB                                           | <sup>t</sup> pd(C-AF) |                                                                                            |                             | 01              | 9, 10, 11            | 2    | 12            |      |

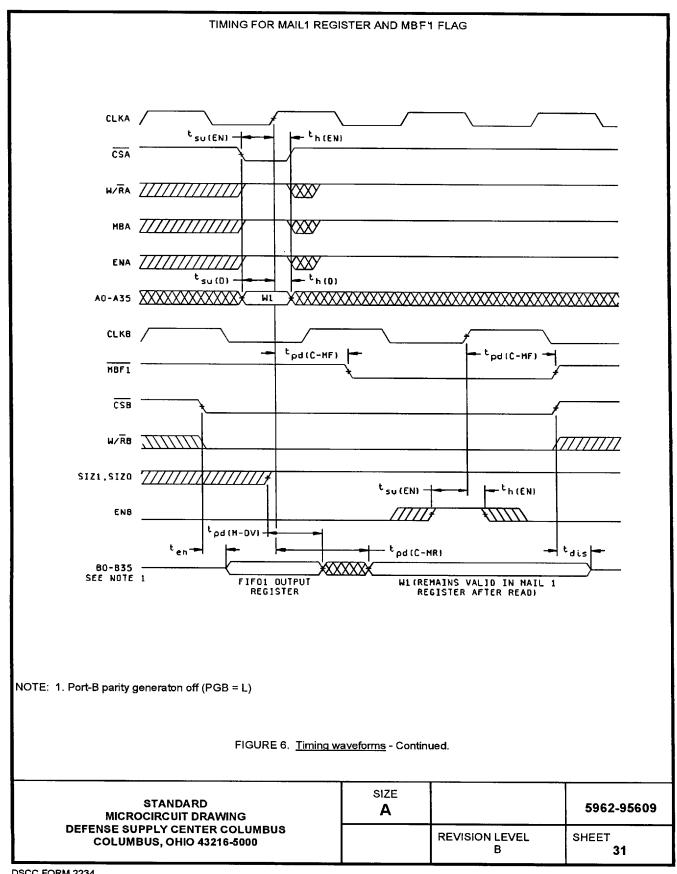

| Propagation delay time,<br>CLKA: to MBFT low or<br>MBF2 high and CLKB:<br>to MBF2 low or MBF1<br>high | <sup>t</sup> pd(C-MF) |                                                                                            |                             | 01              | 9, 10, 11            | 1    | 12            |      |

| Propagation delay time,<br>CLKA↑ to B0-B35↑ 10/<br>and CLKB↑ to A0-A35↑ 11/                           | <sup>t</sup> pd(C-MR) |                                                                                            |                             | 01              | 9, 10, 11            | 3    | 13            |      |

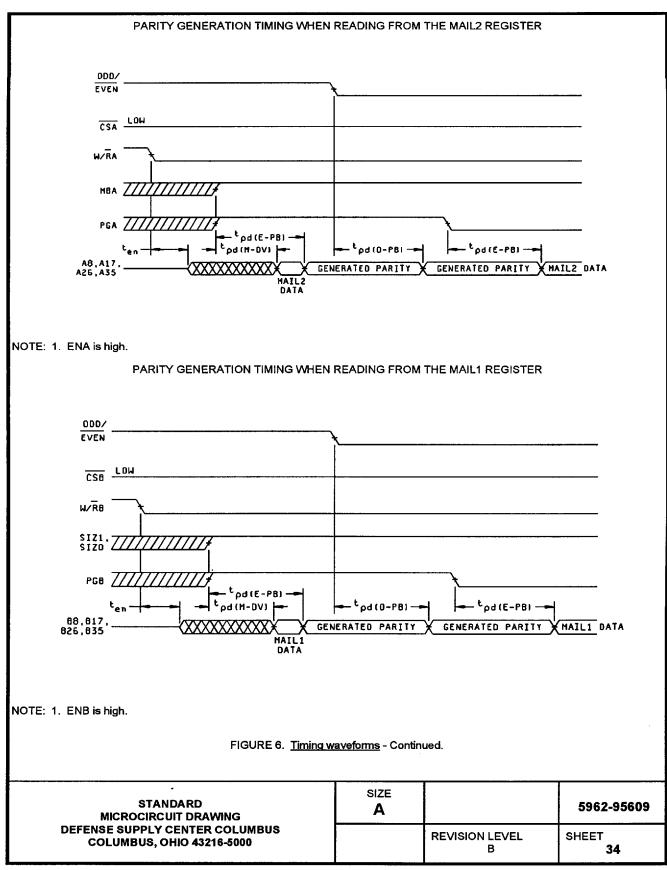

| Propagation delay time,<br>MBA to AO-A35 valid and<br>SIZ0, SIZ1 to B0-B35 valid                      | <sup>t</sup> pd(M-DV) |                                                                                            |                             | 01              | 9, 10, 11            | 1    | 11.5          |      |

| Propagation delay time,<br>CLKB1 to PEFB 12/                                                          | pd(C-PE)              |                                                                                            |                             | 01              | 9, 10, 11            | 2    | 12            |      |

| Propagation delay time,<br>A0-A35 valid to PEFA valid;<br>B0-B35 valid to PEFB valid                  | <sup>t</sup> pd(D-PE) |                                                                                            |                             | 01              | 9, 10, 11            | 3    | 12.5          |      |

| Propagation delay time,<br>ODD/EVEN to PEFA and<br>PEFB                                               | <sup>t</sup> pd(O-PE) |                                                                                            |                             | 01              | 9, 10, 11            | 3    | 12            |      |

| Propagation delay time,<br>ODD/EVEN to parity bits<br>(A8,A17,A26,A35) and<br>(B8,B17,B26,B35)        | <sup>t</sup> pd(O-PB) |                                                                                            |                             | 01              | 9, 10, 11            | 2    | 14            |      |

| ee footnotes at end of table.                                                                         |                       |                                                                                            |                             |                 |                      |      |               |      |

| STAN                                                                                                  | IDARD                 |                                                                                            | SIZE<br><b>A</b>            |                 |                      |      | 5962-         | 9560 |

|                                                                                                                                                                        | TABLE I                              | . Electrical performance characteristic                                                                    | <u>cs</u> - Contir | nued.                |       |              |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-------|--------------|------|

| Test                                                                                                                                                                   | Symbol                               | Test conditions <u>1</u> /<br>-55° C ≤ T <sub>C</sub> ≤ +125° C                                            | Device<br>types    | Group A<br>subgroups | Limit | s <u>3</u> / | Unit |

|                                                                                                                                                                        |                                      | +4.5 V ≤ V <sub>CC</sub> ≤ +5.5 V<br>unless otherwise specified                                            | ,                  | 21                   | Min   | Max          |      |

| Propagation delay time,<br>CSA, W/RA, ENA, MBA or<br>PGA to PEFA<br>CSB, W/RB, ENB, SIZ1,<br>SIZ0, or PGB to PEFB                                                      | <sup>t</sup> pd(E-PE)                | C <sub>L</sub> = 20 pF minimum,<br>V <sub>CC</sub> = 4.5 V and 5.5 V,<br>See figures 5 and 6 as applicable | 01                 | 9, 10, 11            | 1     | 23           | ns   |

| Propagation delay time,<br>CSA, W/RA, ENA, MBA or<br>PGA to parity bits (A8,A17,<br>A26,A35); CSB, W/RB, ENB,<br>SIZ1, SIZ0, or PGB to parity<br>bits (B8,B17,B26,B35) | <sup>t</sup> pd(E-PB)<br><u>13</u> / |                                                                                                            | 01                 | 9, 10, 11            | 3     | 19           |      |

| Propagation delay time, RST to (MBF1, MBF2) high                                                                                                                       | <sup>t</sup> pd(R-F)                 |                                                                                                            | 01                 | 9, 10, 11            | 1     | 20           | ]    |

| Enable time, CSA and W/RA low to A0-A35 active and CSB low and W/RB high to B0-B35 active                                                                              | <sup>t</sup> en                      |                                                                                                            | 01                 | 9, 10, 11            | 2     | 12           |      |

| Disable time, CSA or W/RA high to A0-A35 at high impedance and CSB high or W/RB low to B0-B35 at high impedance                                                        | <sup>t</sup> dis                     |                                                                                                            | 01                 | 9, 10, 11            | 1     | 9            |      |

Each input/output, as applicable, shall be tested at the specified temperature, for the specified limits, to the tests in table I herein. Output terminals not designated shall be high level logic, low level logic, or open, except for all I<sub>CC</sub> tests, where the output terminals shall be open. When performing these tests, the current meter shall be placed in the circuit such that all current flows through the meter. For input terminals not designated,  $V_{IN}$  = GND or  $V_{IN}$   $\geq$  3.0 V. For device class N, all limits for subgroups 1, 3, 7, 8B, 9 and 11 are guaranteed but not production tested. These limits are

characterized at qualification. Production testing is performed at max. operating temperature.

For negative and positive voltage and current values, the sign designates the potential difference in reference to GND and the direction of current flow, respectively, and the absolute value of the magnitude, not the sign, is relative to the minimum and maximum limits, as applicable, listed herein.

For I/O ports, the limit includes  $I_{\parallel}$  leakage current from the input circuitry.

- For I/O ports, the limit includes  $I_{OZH}^{\prime}$  or  $I_{OZL}^{\prime}$  leakage current from the output circuitry. This test is guaranteed when the control inputs affecting the output under test are at 2.0 V or 0.8 V.

- Tests shall be performed in sequence, attributes data only. Functional tests shall include the truth table and other logic patterns used for fault detection. The test vectors used to verify the truth table shall, at a minimum, test all functions of each input and output. All possible input to output logic patterns per function shall be guaranteed, if not tested, to the truth table in figure 3 herein. Functional tests shall be performed in sequence as approved by the qualifying activity on qualified devices. After incorporating allowable tolerances per MIL-STD-883,  $V_{IL}$  = 0.4 V and  $V_{IH}$  = 2.4 V. For outputs, L  $_{\leq}$  0.8 V, H  $_{\geq}$  2.0 V. Requirements to count the clock edge as one of at least four needed to reset the FIFO.

Only applies for a clock edge that does a FIFO read.

- Skew time is not a timing constraint for proper device operation and is only included to illustrate the timing relationship between CLKA cycle and CLKB cycle. This parameter is guaranteed, but not tested.

- Writing data to the mail1 register when the B0-B35 outputs are active and SIZ1, SIZ0 are high.

- Writing data to the mail2 register when the A0-A35 outputs are active and MBA is high.

- 12/ Only applies when a new port-B bus size is implemented by the rising CLKB edge.

- 13/ Only applies when reading data from a mail register.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-95609 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>B | SHEET 8    |

DSCC FORM 2234 **APR 97**

9004708 0033102 731 📟

| *Symbol | * Millimeters | *_*Symbol | *Millimeters  |    |  |  |

|---------|---------------|-----------|---------------|----|--|--|

| *       | * Min * Max   | * *       | * Min * Max   | *  |  |  |

| * A     | * * 1.60      | * *D1/E1  | *13.80 *14.20 | *  |  |  |

| * A1    | * 1.35 * 1.45 | * * D2    | * 11.60 Nom.  | *  |  |  |

| * A2    | * 0.05 *      | * *e      | * 0.40 BSC    | *  |  |  |

| * b     | * 0.13 * 0.25 | * *K      | * 0.45 * 0.75 | *  |  |  |

| * C     | * 0.13 Nom.   | * * a     | * 0° * 7°     | *  |  |  |

| * D/E   | *15.80 *16.20 | * *       | * *           | _* |  |  |

# Notes: 1. All linear dimensions are in millimeters.

- 2. Body dimensions do not include mold flash or protrusion. Allowable protrusion is 0.25 mm maximum per side. D1 and E1 are maximum plastic body size dimensions including mold mismatch.

- 3. Dimension b does not include dambar protrusion. Allowable dambar protrusion shall not cause the lead width to exceed the maximum b dimension by more than 0.08mm. Dambar cannot be located on the lower radius or the foot. Minimum space between protrusion and an adjacent lead is 0.07mm for 0.4mm pitch packages.

- 4. Thermally enhanced molded plastic package with a heat slug (HSL).

FIGURE 1. Case outline.

| STANDARD MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS | SIZE<br><b>A</b> |                | 5962-95609 |

|--------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS                               |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000                                    |                  | B              | 9          |

DSCC FORM 2234 APR 97

9004708 0033103 678

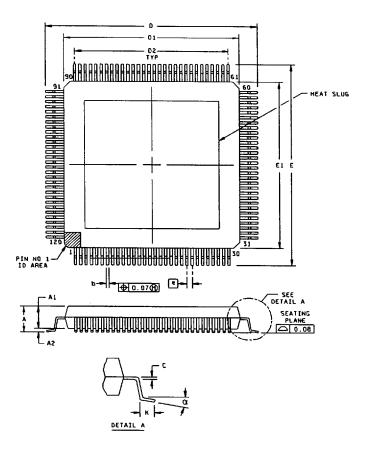

## Case outline Y (see notes 1, 2, and 3)

| Symbol | Inc   | hes   | Millimeters |       | Symbol | Incl  | nes   | Millim | eters |

|--------|-------|-------|-------------|-------|--------|-------|-------|--------|-------|

|        | Min   | Max   | Min         | Max   |        | Min   | Max   | Min    | Max   |

| Α      | 0.110 | 0.150 | 2.79        | 3.81  | HD/HE  | 1.460 | 1.540 | 37.08  | 39.12 |

| b      | 800.0 | 0.014 | 0.20        | 0.36  | е      | 0.025 |       | 0.635  |       |

| С      | 0.004 | 0.008 | 0.10        | 0.20  | e1     | 0.800 |       | 20.    | 32    |

| D/E    | 0.935 | 0.965 | 23.75       | 24.51 | N      | 132   |       |        |       |

- Notes: 1. Although dimensions are in inches, the US government preferred system of measurement is the metric SI system. However, since this item was originally designed using inch-pound units of measurement, in the event of conflict between the two, the inch-pound units shall take precedence. Metric equivalents are for general information only.

- 2. Terminal one shall be identified by a mechanical index in the lead or body, or a mark on the top surface.

- 3. Terminal identification numbers need not appear on the package.

FIGURE 1. Case outline - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-95609 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | B              | 10         |

DSCC FORM 2234 APR 97

9004708 0033104 504

| Device<br>type     | 01                 |                    |                    |                    |                    |                    |                    |  |  |  |  |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|--|--|--|

| Case<br>outline    | X                  |                    |                    |                    |                    |                    |                    |  |  |  |  |

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |  |  |  |  |

| 1                  | A23                | 31                 | AFA                | 61                 | AFB                | 91                 | B23                |  |  |  |  |

| 2                  | A22                | 32                 | FFA                | 62                 | AEB                | 92                 | B24                |  |  |  |  |

| 3                  | A21                | 33                 | CSA                | 63                 | EFB                | 93                 | B25                |  |  |  |  |

| 4                  | GND                | 34                 | ENA                | 64                 | В0                 | 94                 | B26                |  |  |  |  |

| 5                  | A20                | 35                 | CLKA               | 65                 | B1                 | 95                 | V <sub>CC</sub>    |  |  |  |  |

| 6                  | A19                | 36                 | W/RA               | 66                 | B2                 | 96                 | B27                |  |  |  |  |

| 7                  | A18                | 37                 | v <sub>cc</sub>    | 67                 | GND                | 97                 | B28                |  |  |  |  |

| 8                  | A17                | 38                 | PGA                | 68                 | В3                 | 98                 | B29                |  |  |  |  |

| 9                  | A16                | 39                 | PEFA               | 69                 | B4                 | 99                 | GND                |  |  |  |  |

| 10                 | A15                | 40                 | MBF2               | 70                 | В5                 | 100                | B30                |  |  |  |  |

| 11                 | A14                | 41                 | мва                | 71                 | В6                 | 101                | B31                |  |  |  |  |

| 12                 | A13                | 42                 | FS1                | 72                 | V <sub>CC</sub>    | 102                | B32                |  |  |  |  |

| 13                 | A12                | 43                 | FS0                | 73                 | B7                 | 103                | B33                |  |  |  |  |

| 14                 | A11                | 44                 | ODD/EVEN           | 74                 | B8                 | 104                | B34                |  |  |  |  |

| 15                 | A10                | 45                 | RST                | 75                 | B9                 | 105                | B35                |  |  |  |  |

| 16                 | GND                | 46                 | GND                | 76                 | GND                | 106                | GND                |  |  |  |  |

| 17                 | A9                 | 47                 | BE                 | 77                 | B10                | 107                | A35                |  |  |  |  |

| 18                 | A8                 | 48                 | SW1                | 78                 | B11                | 108                | A34                |  |  |  |  |

| 19                 | A7                 | 49                 | swo                | 79                 | B12                | 109                | A33                |  |  |  |  |

| 20                 | v <sub>cc</sub>    | 50                 | SIZ1               | 80                 | B13                | 110                | A32                |  |  |  |  |

| 21                 | A6                 | 51                 | SIZ0               | 81                 | B14                | 111                | A31                |  |  |  |  |

| 22                 | A5                 | 52                 | MBF1               | 82                 | B15                | 112                | A30                |  |  |  |  |

| 23                 | A4                 | 53                 | PEFB               | 83                 | B16                | 113                | GND                |  |  |  |  |

| 24                 | A3                 | 54                 | PGB                | 84                 | B17                | 114                | A29                |  |  |  |  |

| 25                 | GND                | 55                 | V <sub>CC</sub>    | 85                 | B18                | 115                | A28                |  |  |  |  |

| 26                 | A2                 | _                  |                    | 86                 | B19                | 116                | A27                |  |  |  |  |

| 27                 | A1                 | <sup>*</sup> 56    | W/RB               | 87                 | B20                | 117                | V <sub>CC</sub>    |  |  |  |  |

| 28                 | A0                 | 57                 | CLKB               | 88                 | GND                | 118                | A26                |  |  |  |  |

| 29                 | EFA                | 58                 | ENB                | 89                 | B21                | 119                | A25                |  |  |  |  |

| 30                 | AEA                | 59                 | CSB                | 90                 | B22                | 120                | A24                |  |  |  |  |

|                    | <u></u>            | 60                 | FFB                |                    |                    | l                  |                    |  |  |  |  |

FIGURE 2. <u>Terminal connections</u>.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-95609 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | B              | 11         |

**■** 9004708 0033105 440 **■**

| Device<br>type  | 01              |          |                 |          |                 |          |          |  |  |  |  |

|-----------------|-----------------|----------|-----------------|----------|-----------------|----------|----------|--|--|--|--|

| Case<br>outline | Y               |          |                 |          |                 |          |          |  |  |  |  |

| Terminal        | Terminal        | Terminal | Terminal        | Terminal | Terminal        | Terminal | Terminal |  |  |  |  |

| number          | symbol          | number   | symbol          | number   | symbol          | number   | symbol   |  |  |  |  |

| 1               | GND             | 34       | A10             | 67       | GND             | 100      | B10      |  |  |  |  |

| 2               | RST             | 35       | A11             | 68       | B35             | 101      | GND      |  |  |  |  |

| 3               | ODD/EVEN        | 36       | v <sub>cc</sub> | 69       | B34             | 102      | В9       |  |  |  |  |

| 4               | FS0             | 37       | A12             | 70       | B33             | 103      | B8       |  |  |  |  |

| 5               | FS1             | 38       | A13             | 71       | GND             | 104      | B7       |  |  |  |  |