#### **Features**

- Complete 2.4GHz High performance Radio Transceiver

- No external trimming is required in production

- Bluetooth wireless technology, 2.4 GHz licensefree band

- Compliant to the Bluetooth<sup>TM</sup> specification v1.1

- Bluetooth Class 2, 3 Level Output Power

- High Receive sensitivity -85 dBm typ.

- Communications of up to 10m range in free space

- Frequency Hopping Spread Spectrum (FHSS) with Gaussian Frequency Shift Keying (GFSK)

- Transmission scheme TDD time division duplex.

- Frequency 2402 to 2480 MHz

- Channel intervals 1 MHz

- Number of channels 79 CH

- Symbol rate 1M symbol/s

- Compliant to FCC, CE, ETSI and other countries' EMI standards

- Very good data quality--tolerates blocking by other services

- Internal 16MHz crystal and clock oscillator

- Integrated RF bandpass filter

- SPI interface for installing and configuring the module

- Low Power standby modes to enable very efficient power management

- Available for either external antenna or internal patch\_antenna

- Power supply voltage 2.7 V and 3.3V

- Operation Temperature: 0 ~ 40°C

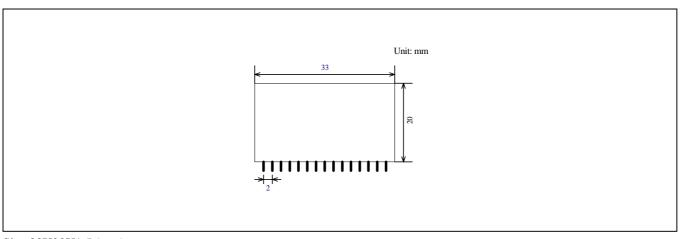

- Small size, lightweight, size 33mm X 20mm X 1.5mm

- Available in small quantities

## **Application**

- Laptop and Desktop PCs

- Computer Accessories (Compact Flash, PCMCIA and SD cards)

- Cordless game controllers

- Printers, FAX, WebPAD

- Personal Digital Assistants (PDAs)

- Cordless Headsets

- Digital camera

- USB Dongle /RS232 adaptor

- And many other computer peripherals or embedded devices applications, including wireless keyboard, mouse, joystick etc.

### **General Descriptions**

The PT8R2401 is well suited to applications that fall within the 2.4 GHz radio spectrum designated as Industrial, Scientific and Medical (ISM).

Transmission scheme TDD – time division duplex. Spreading type FHSS – frequency hopping spread spectrum. Number of channels 79. Channel intervals 1 MHz [(f = 2.402 + k) GHz, k = 0.1,2,...78]. Hop rate 1.6k hops/second. Modulation Method GFSK 0.5BT Gaussian. Support point-to-multipoint functionality.

The PT8R2401 control interface consists of a data interface and a control interface for transmitting and receiving data, and a serial interface for programming the internal registers of the PT8R2401.

There are two subsections of the interface:

- RF data and control path

- Register control interface (serial).

Six signals are used in the RF data and control path (TXDATA, RXDATA, TXACTIVE, RXACTIVE, TXDATA\_EN, SYNCDETECT). Four in the serial register control interface (TDI, TDO, TMS, TCK), one system clock (DATACLK) and one reset signal (RET). All of the signals are unidirectional.

Standard PT8R2401 has built-in antenna. Option PT8R2401N has no built-in antenna. Customer can use external antenna.

These modules can be integrated into almost any radio electrical device for wireless data communications, including PDAs, mobile phones, laptop computers, and game pad devices.

## **Ordering Information**

| Device    | Descr                 | Order Number   |            |

|-----------|-----------------------|----------------|------------|

| Device    | Туре                  |                |            |

| PT8R2401  | Have built-in antenna | 33X20X1.5 (mm) | PT8R2401MD |

| PT8R2401N | No built-in antenna   | 33X20X1.5 (mm) | PT8R2401MD |

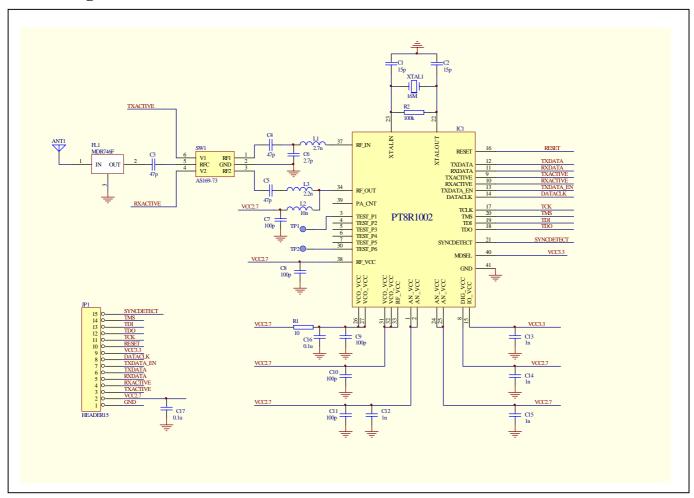

# **Block Diagram**

### **Pin Information**

Package Diagram

Size 33X20X1.5 (mm)

# **Pin Descriptions**

| Pin | PIN Name   | TYPE  | Description                             |

|-----|------------|-------|-----------------------------------------|

| 1   | GND        | Power | GND                                     |

| 2   | VCC2.7     | Power | 2.7V Power Supply                       |

| 3   | TXACTIVE   | I     | Transmitter enable                      |

| 4   | RXACTIVE   | I     | Receiver enable                         |

| 5   | RXDATA     | О     | Receive data                            |

| 6   | TXDATA     | I     | Transmit data                           |

| 7   | TXDATA_EN  | I     | Timing reference of valid data          |

| 8   | DATACLK    | О     | Reference data clock                    |

| 9   | VCC3.3     | Power | 3.3V Power Supply                       |

| 10  | RESET      | I     | Reset                                   |

| 11  | TCK        | I     | A serial register interface clock       |

| 12  | TDO        | О     | Phy control register serial data output |

| 13  | TDI        | I     | Phy control register serial data input  |

| 14  | TMS        | I     | Control signal of Phy's TAP controller  |

| 15  | SYNCDETECT | I     | Indication of SYNC word detection       |

### I/O Description

#### **RF** interface

The radio interface establishes the connection of antenna-to-LNA in receiving mode and antenna-to-power amplifier in transmitting mode. An antenna filter is located between the antenna and SPDT (Single Pole Double Throw) switch. The antenna filter blocks unwanted signals in receive mode and suppresses harmonics in the transmit mode. The filter can be either a discrete component or fully integrated in ceramic substrate. The SPDT switch isolates the transmit path and the receive path and thus impedance can be matched for entire signal path. A matching circuit is placed between LNA\_IN pin and SPDT switch to match the 50 ohm source to the complex input impedance of the LNA. Another external matching circuit is required at PA\_OUT to transfer maximum power to the antenna.

#### Unidirectional interface

The interface connections for unidirectional mode are shown as follows: the unidirectional interface can be split into two subsections: RF data and control path, register control interface. In RF interface, ten signals are used in the RF data and control path, and four in the register control interface.

All of the signals are unidirectional.

The unidirectional interface requires that the PT8R2401 control registers interface to the Baseband via an IEEE 1149.1 JTAG interface. The unidirectional interface requires that the Baseband portion of the interface is referenced to a Baseband generated clock.

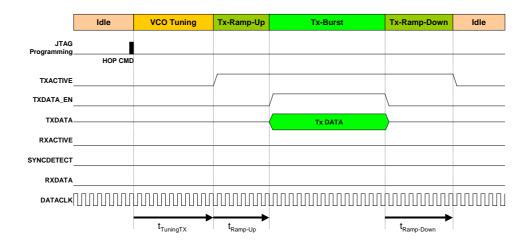

#### **Transmit Operation In Unidirectional Interface**

The primary signal for data transmit is TXACTIVE signal. The actual data transmission starts after TXDATA\_EN provided by baseband. During transmit mode,

DATACLK is sent from PT8R2401 to baseband as a timing reference. The baseband circuit transmits data to the PT8R2401 at the falling edge of DATACLK, whereas the PT8R2401 latches the data at the rising edge of DATACLK.

The state of PT8R2401 transits from the **idle state** when the baseband drives TXACTIVE HIGH. TXACTIVE enables all the transmit circuitry except for the final output stage. TXACTIVE is driven high at a time  $T_{TuningTX}$  before the hop frequency synthesizer has settled to allow any frequency offsets caused by the TX circuitry to be eliminated. Either when, or just before, the TX circuitry has correctly settled on frequency, the baseband drives TXDATA\_EN HIGH, which enables the PA stage, and causes the unidirectional interface to enter the **transmit data state**. The baseband drives data to the PT8R2401 on the falling edge of DATACLK, and the PT8R2401 reads the transmit data on the rising edge. When all the data has been transmitted, the baseband drives TXDATA\_EN and TXACTIVE LOW to disable the PA stage and return to the **idle state**.

Figure 2. Transmit procedure timing diagram in unidirectional interface

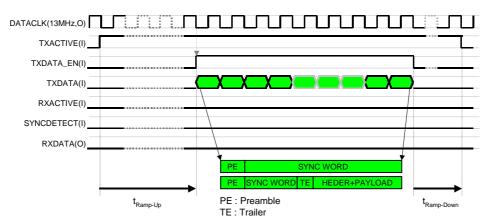

Figure 3. Transmit signal timing diagram in unidirectional interface

### **Receive Operation In Unidirectional Interface**

The primary signal for data reception is RXACTIVE signal. When RXACTIVE goes to high, the RF circuitry starts to operate and send data after fixed time from RXACTIVE. The baseband receives data and searches for the access code. During receive mode, DATACLK is sent from PT8R2401 to baseband as a timing reference. The PT8R2401 circuit sends the data to baseband at the rising edge of DATACLK, where the baseband latches the data at the falling edge of DATACLK. Prior to receiving information over air, the baseband transfers control information including the hop frequency over the JTAG interfaces, and enters PT8R2401 into **search access code state** after fixed time to turn on receiver circuitry by driving RXACTIVE HIGH. In the **search access code state**, the baseband performs all of the tasks required to correlate with the access code from the receive data. When the baseband has correlated the access code, then it drives SYNCDETECT HIGH and makes PT8R2401 enter into **receive payload state**. During the payload, PT8R2401 eliminates any frequency offset between local and remote Bluetooth devices based on its measurement during syncword acquisition. PT8R2401 transmits demodulated data to the baseband at half frequency of DATACLK, which can be read by the baseband using appropriate timing recovery algorithm. The unidirectional interface is returns to the **idle state** with the baseband driving RXACTIVE LOW after a fixed interval of T<sub>RxOff</sub>.

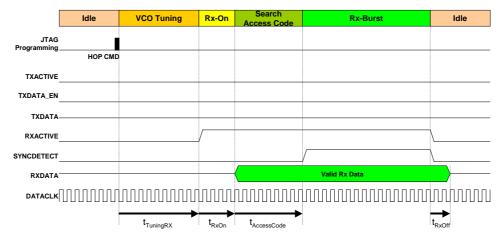

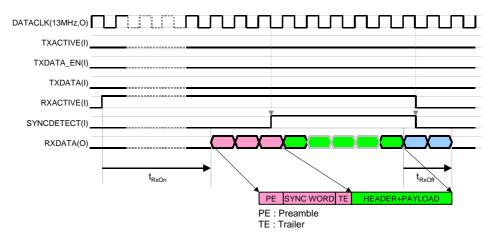

Figure 4. Receiver procedure timing-diagram in unidirectional interface

Figure 5. Receiver signal timing diagram in unidirectional interface

#### **Power-Up Sequence**

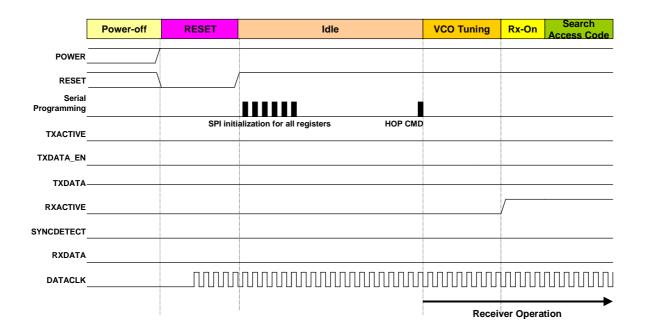

The power-up sequence of PT8R2401 is very simple mechanism. After power is applied to the PT8R2401, the activating RESET signal into LOW for  $t_{RESET}$  is the only required operation. After this procedure, PT8R2401 will come into idle mode for waiting transmit or receive operation indicated by Bluetooth baseband. Before this normal operation, all SPI register value should be initialized even though its value is set by the default value. The initialized value will be provided by PTI. After activating RESET signal, 13 or 16MHz baseband reference signal, DATACLK will be activated until execution of external power down command through SPI interface.

Figure 6. Power-up sequence procedure timing-diagram

#### **Power-Down Sequence**

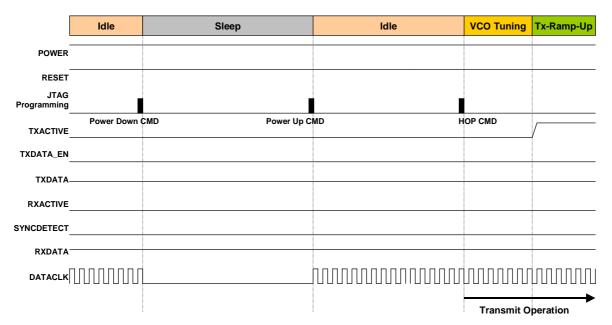

The lowest operation power state of PT8R2401 is **Sleep state**, where all clocks including RF and baseband and circuits in the PT8R2401 is placed in their minimum power mode. In this mode, the control register can be accessed through serial interface logic and retain their programmed value. To enter into **Sleep state**, power-down command which sets power-down of clock generator including crystal buffer should be programmed through the serial interface. After power-down command, the DATACLK from the PT8R2401 will stop until it comes back to **Idle state**. To escape from **Sleep state**, power-up command which sets power-up of clock generator should be programmed through the serial interface. After power-up command, the DATACLK will start again from the PT8R2401 into external baseband.

Figure 7. Power-down sequence procedure timing-diagram

#### **Power Control**

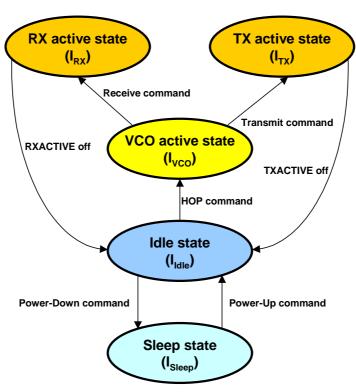

In the PT8R2401, there are five different states with different current consumption; Sleep, Idle, VCO active, TX active, and RX active. Upon reset, the PT8R2401 stays in the Idle state to wait for the command through serial programming interface from the baseband controller. In the Idle state, there is DATACLK from the radio to the baseband controller. In the Idle mode, all RF circuits are shut down to reduce the static current consumption. Only the reference clock oscillator and DATACLK pump to the baseband is active. After HOP set command through the serial programming, the VCO will operate to lock the programmed channel frequency. Owing to the signal such as RXACTIVE or TXACTIVE, the PT8R2401 will enter into the active state such as TX active state and RX active state. In those state, all RF circuits and GFSK modem will operate and result in the maximum current consumption. In the unidirectional mode, the falling signal of RXACTIVE or TXACTIVE will make the PT8R2401 into Idle state automatically. In the bidirectional mode, the explicit command to stop receive or transmission through serial programming will make the PT8R2401 into Idle state. The PT8R2401 enters into Sleep state by power down command through serial programming. Sleep state is the least power consumption among other states and all clocks include reference oscillator will stop the operation as well as the power down of all RF circuits. In Sleep state, only the serial programming interface logic can operate which uses clock from external device. However, the value of all registers will sustain until the wake up from Sleep state. Following figure shows the state transition in terms of power control.

Figure 8. State transition diagram for power control

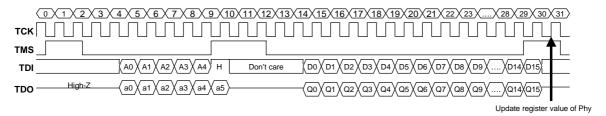

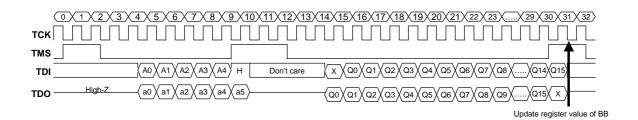

#### **Serial Programming Interface (JTAG interface)**

The serial programming interface is a JTAG boundary-scan architecture compliant with IEEE 1149.1. Interconnection between the serial interface and external baseband consists of four 1-bit digital signals: control data input(TDI), control mode select (TMS), control clock (TCK) and control data output (TDO). You must refer to the full IEE std 1149.1-1990 Standard Test Access Port and Boundary-Scan Architecture document for a complete, definitive description of the operation of the fundamentals of the JTAG interface. PT1002 support TCK up to 16MHz.

**Table 1. TAP instructions**

| Instruction             | Opcode   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST                  | 0x000000 | EXTEST initiates testing of external circuitry, typically board-level interconnects and off chip circuitry. EXTEST connects the Boundary-Scan register between TDI and TDO in the SHIFT_DR state only. When EXTEXT is selected, all output signal pin values are driven by values shifted into the Boundary-Scan register and may change only on the falling-edge of TCK in the Update_DR state. Also, when EXTEST is selected, all system input pin states must be loaded into the Boundary-Scan register on the rising-edge of TCK in the Capture_DR state. Values shifted into input latches in the Boundary-Scan register are never used by the processor's internal logic.                                                                |

| SAMPLE /<br>PRELOAD     | 0x000001 | SAMPLE / PRELOAD performs two functions:  • When the TAP controller is in the Capture-DR state, the SAMPLE instruction occurs on the rising edge of TCK and provides a snapshot of the component's normal operation without interfering with that normal operation. The instruction causes Boundary-Scan register cells associated with outputs to SAMPLE the value being driven by or to the processor.  • When the TAP controller is in the Update-DR state, the PRELOAD instruction occurs on the falling edge of TCK. This instruction causes the transfer of data held in the Boundary-Scan cells to the slave register cells. Typically the slave-latched data is then applied to the system outputs by means of the EXTEST instruction. |

| IDCODE                  | 0x011111 | IDCODE is used in conjunction with the device identification register. It connects the identification register between TDI and TDO in the Shift_DR state. When selected, IDCODE parallel-loads the hard-wired identification code (32 bits) on TDO into the identification register on the rising edge of TCK in the Capture_DR state.  NOTE: The device identification register is not altered by data being shifted in on TDI.                                                                                                                                                                                                                                                                                                               |

| REGISTER<br>PROGRAMMING | 0x1SSSSS | REGISTER PROGRAMMING instruction select the REGISTER with address indicator SSSSS.  • When the TAP controller is in the Capture-DR state, the REGISTER PROGRAMMING instruction occurs on the rising edge of TCK and executes a snapshot of register addressed SSSSS into serial register.  • When the TAP controller is in the Update-DR state, the REGISTER PROGRAMMING instruction occurs on the falling edge of TCK. This instruction causes the transfer of data held in serial register to register addressed SSSSS.                                                                                                                                                                                                                      |

| BYPASS                  | 0x111111 | BYPASS instruction selects the Bypass register between TDI and TDO pins while in SHIFT_DR state, effectively bypassing the processor's test logic. 0 is captured in the CAPTURE_DR state. While this instruction is in effect, all other test data registers have no effect on the operation of the system. Test data registers with both test and system functionality perform their system functions when this instruction is selected.                                                                                                                                                                                                                                                                                                      |

#### **SPI Register Map**

The values of all registers except read-only are set by default values after rest. The default values can be overrided by accessing each register. Typical register values are subject to change and should be obtained from PTI. During normal operation, SPI access should occur to address the following functions only.

- Programming PLL hop frequency of BT\_RF\_PLL\_CTRL0

- Setting Tx power control value of BT\_RF\_TX\_CTRL in the transmit mode

- Reading receive signal strength indication of BT\_RSSI\_STA in the receive mode

- Programming TXA or RXA of BT\_RF\_PLL\_CTRL1 to indicate transmit or receive mode in bidirectional interface

Table 2. SPI register address map

| Address   | Name             | Attribute  | Description                                  |

|-----------|------------------|------------|----------------------------------------------|

| 0x00      | BT_SOFT_RESET    | write      | RESET by serial interface*                   |

| 0x01      | BT_MODEM_CTRL    | read/write | Modem control register                       |

| 0x02      | BT_RF_RX_CTRL    | read/write | RF receiver control register                 |

| 0x03      | BT_RF_TX_CTRL    | read/write | RF transmitter control register              |

| 0x04      | BT_RF_BB_CTRL0   | read/write | RF baseband control0 register                |

| 0x05      | BT_RF_BB_CTRL1   | read/write | RF baseband control1 register                |

| 0x06      | BT_RF_PLL_CTRL0  | read/write | RF PLL control0 register                     |

| 0x07      | BT_RF_PLL_CTRL1  | read/write | RF PLL control1 register                     |

| 0x08      | BT_RF_PLL_CTRL2  | read/write | RF PLL control2 register                     |

| 0x09      | BT_RF_PLL_CTRL3  | read/write | RF PLL control3 register                     |

| 0x0A      | BT_RF_TIM_CTRL0  | read/write | RF timing adjustment configuration0 register |

| 0x0B      | BT_RF_TIM_CTRL1  | read/write | RF timing adjustment configuration1 register |

| 0x0C      | BT_RF_TIM_CTRL2  | read/write | RF timing adjustment configuration2 register |

| 0x0D      | BT_RF_TIM_CTRL3  | read/write | RF timing adjustment configuration3 register |

| 0x0E      | BT_RF_TIM_CTRL4  | read/write | RF timing adjustment configuration4 register |

| 0x0F      | BT_RF_TIM_CTRL5  | read/write | RF timing adjustment configuration5 register |

| 0x10      | BT_RF_AUX_CTRL0  | read/write | RF auxiliary control0 register               |

| 0x11      | BT_RF_AUX_CTRL1  | read/write | RF auxiliary control1 register               |

| 0x12      | BT_RSSI_STA      | read       | Modem RSSI register                          |

| 0x13      | BT_RF_STA        | read       | RF status register                           |

| 0x14      | BT_DAC_TEST_CTRL | read/write | DAC test register                            |

| 0x15      | BT_PWD_CTRL0     | read/write | MODEM power detector register0               |

| 0x16      | BT_PWD_CTRL1     | read/write | MODEM power detector register1               |

| 0x17~0x1D | -                | -          | Reserved                                     |

| 0x1E      | BT_PWDN          | write      | Power down register                          |

| 0x1F      | IDCODE           | read       | IDCODE                                       |

<sup>\*</sup> Equivalent to hardware reset by asserting RESET pin.

\* The values in all registers are the recommended initial value to be set by the serial programming interface, since some of them may be different value with the default configuration by hardware after reset. Also, these value can be changed in order to be optimized for special purpose. Please contact PTI semiconductor to get up-to-date configuration.

|      | iiiizeu i | •     |        | se. Piease          | Comaci                                                                                                            | l F I I Sel              | inconduc   | otor to g | get up-to | -date co   | iiiigurai | 1011.    |            |             |           |

|------|-----------|-------|--------|---------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------|------------|-----------|-----------|------------|-----------|----------|------------|-------------|-----------|

| 0x01 |           |       | ODEM_  | CTRL                |                                                                                                                   |                          |            |           |           |            |           |          |            |             |           |

| 15   | 14        | 13    | 12     | 11                  | 10                                                                                                                | 9                        | 8          | 7         | 6         | 5          | 4         | 3        | 2          | 1           | 0         |

| CKS  |           |       |        |                     |                                                                                                                   |                          |            |           |           |            |           |          |            | TE          | EPM       |

| 0    |           |       | 01011b |                     |                                                                                                                   |                          | 011        | 1b        |           | 0          | 1         | 1        | 1          | 0           | 0b        |

| TEPM |           |       |        | 00 : off<br>01 : on |                                                                                                                   | amp drive                |            |           |           |            |           |          |            |             |           |

| CKS  |           |       |        |                     |                                                                                                                   | select fla               |            |           |           |            |           |          |            |             |           |

|      |           |       |        | 0 : 13M<br>1 : 16M  | Hz                                                                                                                | ·                        |            |           |           |            |           |          |            |             |           |

| 0x02 |           |       | F_RX_C |                     |                                                                                                                   |                          |            |           |           | ,          |           |          |            |             |           |

| 15   | 14        | 13    | 12     | 11                  | 10                                                                                                                | 9                        | 8          | 7         | 6         | 5          | 4         | 3        | 2          | 1           | 0         |

|      | 1b        | 0     |        | 1b                  |                                                                                                                   | 10                       | 00b        |           | 0b        |            |           | 000      | 0000b      |             |           |

| 0x03 |           |       | TX_C   |                     |                                                                                                                   |                          |            |           |           |            |           |          |            |             |           |

| 15   | 14        | 13    | 12     | 11                  | 10                                                                                                                | 9                        | 8          | 7         | 6         | 5          | 4         | 3        | 2          | 1           | 0         |

|      |           |       | OS     |                     |                                                                                                                   |                          |            |           |           | TPG        |           |          |            | TAG         |           |

|      |           | 1     | 0      |                     | 011                                                                                                               |                          |            |           |           | 11111b     |           |          |            | 001b        |           |

| OS   |           |       |        | 0 : The             | put DATACLK PAD strength<br>The driving capability of DATACLK is low<br>The driving capability of DATACLK is high |                          |            |           |           |            |           |          |            |             |           |

| TPG  |           |       |        |                     |                                                                                                                   | mp gain<br>11111b(       |            | h 3211A   | sten      |            |           |          |            |             |           |

| TAG  |           |       |        |                     |                                                                                                                   | GC gain c                |            | 02011     | p         |            |           |          |            |             |           |

|      |           |       |        | 000b(-3             | dB), 001                                                                                                          | b(-1.5dB)<br>b(4.5dB),   | ), 010b(0  |           |           | ,          |           |          |            |             |           |

| 0x04 |           | BT_RF | _BB_CT |                     |                                                                                                                   |                          |            |           |           |            |           |          |            |             |           |

| 15   | 14        | 13    | 12     | 11                  | 10                                                                                                                | 9                        | 8          | 7         | 6         | 5          | 4         | 3        | 2          | 1           | 0         |

|      | 0         | 0     | 0      | 1                   | 1                                                                                                                 | 0                        | 1          | 1         | 1b        | 0          |           | 00       | )11b       | •           | 0         |

| 0x05 |           | BT_RF | BB_CT  | RL1                 |                                                                                                                   |                          |            |           |           |            |           |          |            |             |           |

| 15   | 14        | 13    | 12     | 11                  | 10                                                                                                                | 9                        | 8          | 7         | 6         | 5          | 4         | 3        | 2          | 1           | 0         |

| 0    |           | 101   | l0b    |                     | 0                                                                                                                 |                          | 111b       |           |           | 011b       |           |          | 00         | )00b        |           |

| 0x06 |           | BT_RF | PLL_C  | CTRL0               |                                                                                                                   |                          |            |           |           |            |           |          |            |             |           |

| 15   | 14        | 13    | 12     | 11                  | 10                                                                                                                | 9                        | 8          | 7         | 6         | 5          | 4         | 3        | 2          | 1           | 0         |

| TXA  | RXA       |       |        |                     | TG                                                                                                                |                          |            |           |           |            |           | СН       |            |             |           |

| 0    | 0         |       |        |                     | )111111b                                                                                                          |                          |            |           |           |            |           | 0000000  |            |             |           |

|      | TΣ        | ΚA    |        | Internal            | TXACT                                                                                                             | IVE signa                | al generat | ion in bi | direction | al interfa | ce. Writi | ng HIGH  | I          |             |           |

|      |           |       |        |                     |                                                                                                                   |                          | , refer to | I/O des   | scription | of transr  | nit opera | tion. Th | is field o | does not a  | affect in |

|      |           |       |        |                     | tional int                                                                                                        |                          |            |           |           |            |           |          |            |             |           |

|      |           | ΧA    |        | descript            | ion of rec                                                                                                        | ceiver ope               | eration. T | his field | does not  | affect in  |           |          |            | ation, refe | er to I/O |

|      | TG        | i[6]  |        |                     |                                                                                                                   | er amp ga                |            | I with bi | as chang  | e          |           |          |            |             |           |

| -    | mar       | 5.01  |        |                     |                                                                                                                   | 0 : gain o               |            | 124 - 2   |           | 1:4        |           |          |            |             |           |

|      | TG        | [5:0] |        |                     |                                                                                                                   | er amp ga                |            |           |           |            |           |          |            |             |           |

| -    |           | H     |        |                     |                                                                                                                   | ım gain) -<br>el selecti |            | v(max1m   | ium gain  | )          |           |          |            |             |           |

| 0x07 |           |       | _PLL_C | 0000000             |                                                                                                                   | ei seiecti<br>innel(240  |            | 00000011  | o: 1 char | mel(2403   | MHz), .   |          |            |             |           |

| 15   | 14        | 13    | 12     | 11                  | 10                                                                                                                | 9                        | 8          | 7         | 6         | 5          | 4         | 3        | 2          | 1           | 0         |

| 1.0  | 0         | 0     | 14     | 11                  | 10                                                                                                                | 00000                    |            |           | U         | J          | +         | J        | 00000      | 1 1         | 1 0       |

| 0x08 | U         |       | PLL C  | TDL2                |                                                                                                                   | 00000                    |            |           |           |            |           |          | 00000      |             |           |

| 15   | 14        | 13    | 12     | 11                  | 10                                                                                                                | 9                        | 8          | 7         | 6         | 5          | 4         | 3        | 2          | 1           | 0         |

| 0    |           | )b    |        | lb                  | 10                                                                                                                | 001b                     | O          |           |           |            | )b        | 1        |            | 010b        | 1 0       |

| 0x09 |           |       | PLL    |                     |                                                                                                                   | 0010                     |            |           | <i></i>   | 10         | <i></i> _ | 1        |            | 0100        |           |

| 15   | 14        | 13    | 12     | 11                  | 10                                                                                                                | 9                        | 8          | 7         | 6         | 5          | 4         | 3        | 2          | 1           | 0         |

| 13   | 14        | 13    | 14     | 100000              |                                                                                                                   | 7                        | o          | /         | U         | 3 00       |           |          | 0b         | 0           | 0         |

| 0x0A |           | PT DE | TIM (  |                     |                                                                                                                   |                          |            |           |           |            | <i></i> _ |          | υυ<br>     | U           | U         |

| 15   | 14        | 13    | 12     | 1 KLU<br>11         | 10                                                                                                                | 9                        | 8          | 7         | 6         | 5          | 4         | 3        | 2          | 1           | 0         |

| 13   |           | BD    | 14     | 11                  | TB                                                                                                                |                          | O          | /         |           | 3D         | 4         | 3        |            | BD 1        | 1 0       |

|      | 11        | ענ    |        |                     | 1 1                                                                                                               | עי                       |            |           | 11        | ענ         |           | l        | 1          | עע          |           |

| 0x0B                                             |              | RT RE | TIM_O     | TRL1                 |           |          |            |                  |           |          |       |          |       |       |     |

|--------------------------------------------------|--------------|-------|-----------|----------------------|-----------|----------|------------|------------------|-----------|----------|-------|----------|-------|-------|-----|

| 15                                               | 14           | 13    | 12        | 11                   | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

|                                                  | TI           | 3D    |           |                      | TH        | 3D       |            |                  | TI        | BD       |       |          | T     | BD    |     |

| 0x0C                                             |              | BT_RF | TIM_C     | CTRL2                |           |          |            |                  |           |          |       |          |       |       |     |

| 15                                               | 14           | 13    | 12        | 11                   | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

|                                                  | TI           |       |           |                      | TE        | BD       |            |                  | TI        | BD .     |       |          | T     | BD    |     |

| 0x0D                                             | 1.4          |       | TIM_C     |                      | 10        | 0        | 0          | 7                |           | -        | 4     | 2        | 2     | 1     | 0   |

| 15                                               | 14<br>TI     | 13    | 12        | 11                   | 10<br>TE  | 9        | 8          | 7                | 6<br>TI   | 5        | 4     | 3        | 2     | BD    | 0   |

| 0x0E                                             | 11           |       | TIM_C     | TDI 1                | 11        | עמ       |            |                  | 11        | עמ       |       |          | 1.    | עמ    |     |

| 15                                               | 14           | 13    | 12        | 11<br>11             | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

| 13                                               | Ti           |       | 12        | 11                   | TE        |          |            | ,                | TI        |          |       | 3        |       | BD    |     |

| 0x0F                                             |              |       | TIM       | TRL5                 |           |          |            |                  |           |          |       |          | -     |       |     |

| 15                                               | 14           | 13    | 12        | 11                   | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

|                                                  | BD           |       | 3D        |                      | BD        |          | TBD        |                  | TH        | BD       | TI    | 3D       |       | TBD   |     |

| 0x10                                             |              | BT_R  | F_AUX_    | CTRL0                |           |          |            |                  | ,         |          |       |          |       |       |     |

| 15                                               | 14           | 13    | 12        | 11                   | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

| 0                                                | 0            | 1b    | 0         | 2000                 | 10        | 00b      |            | 1                | 1         |          |       | 000      | 000b  |       |     |

| 0x11                                             | 1.4          |       | AUX_(     |                      | 10        | 0        | O          | 7                | (         | F        | 4     | 2        | 2     | 1     | 0   |

| 15                                               | 14           | 13    | 12        | 11                   | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3<br>PVN | 2     | PVL   | 0   |

| 1                                                | <del> </del> | 000b  |           | n                    | 1b        | n        | 1b         | 1                | 0         | 0        | 0     | 0        | -     | 100b  |     |

| PVN                                              | 1            | 0000  |           |                      | ver amp o |          |            | _                |           |          |       |          | 1     | 1000  |     |

|                                                  |              |       |           | 0 : disa             |           |          |            |                  |           |          |       |          |       |       |     |

|                                                  |              |       |           | 1 : enal             |           |          |            |                  |           |          |       |          |       |       |     |

| PVL                                              |              |       |           |                      | wer amp p |          |            |                  |           |          |       |          |       |       |     |

|                                                  |              |       |           |                      | 7dBm), 00 |          |            |                  |           |          |       |          |       |       |     |

| 012                                              |              | DT DC | OT OTA    | 100b(0               | dBm), 10  | 1b(1dBn  | n), 110b(2 | 2dBm), 1         | 11b(3dBi  | n)       |       |          |       |       |     |

| <b>0x12</b> 15                                   | 14           | 13    | 12        | 11                   | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

| 13                                               | PVO          |       | _PO3      | 11                   | 10        | 7        | 0          | ,                | RSS       |          | 4     | 3        |       | _AGC  | U   |

| PVO                                              | 1 10         | Robi  | _1 03     | 1 : The              | current p | ower of  | pre powe   | r amp is 1       |           |          |       | 1        | Robi  |       |     |

|                                                  |              |       |           |                      | current p |          |            |                  |           |          |       |          |       |       |     |

| RSSI_A                                           | AGC          |       |           |                      | ain value | with 3dl | 3 step fro | m –3dB(0         | 0000b) to | 42dB(11  | 111b) |          |       |       |     |

| 0x13                                             | ,            |       | OW_STA    |                      | ,         |          |            | ,                |           |          | ,     | ,        |       | ,     |     |

| 15                                               | 14           | 13    | 12        | 11                   | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

| 0.11                                             |              |       | G mag     | r corp.              |           |          |            |                  |           | C        | SS    |          |       |       |     |

| <b>0x14</b> 15                                   | 14           | 13    | 12        | 1_ <b>CTRI</b><br>11 | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

| 13                                               | 14           | 13    | DE        | 11                   | 10        |          | ACI        | /                | 0         | 3        | 4     |          | CQ CQ | 1     | U   |

|                                                  |              |       | 0         |                      |           |          | 000b       |                  |           |          |       |          | 000b  |       |     |

| 0x15                                             |              | BT PV | VD_CTR    | LO                   |           | 000      | 0000       |                  |           |          |       | 000      | 0000  |       |     |

| 15                                               | 14           | 13    | 12        | 11                   | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

|                                                  |              |       |           |                      |           |          |            |                  | PWD_S     | START    |       |          |       | AFS   | DSS |

|                                                  |              |       |           |                      |           |          |            |                  | 10000     | 0010b    |       |          |       | 1     | 1   |

| 0x16                                             |              |       | VD_CTR    |                      |           |          |            |                  |           |          |       |          |       |       |     |

| 15                                               | 14           | 13    | 12        | 11                   | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

| <u> </u>                                         |              |       | PBD       |                      | PWR       |          |            |                  |           | _TH2     |       | <u> </u> |       | 2_TH1 |     |

| 0x1E                                             |              | BT_P  | 0         |                      | 10.       | 10b      |            |                  | 010       | 00b      |       |          | 01    | 10b   |     |

| 15                                               | 14           | 13    | WDN<br>12 | 11                   | 10        | 9        | 8          | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

| 13                                               | 14           | 13    | 12        | 11                   | 10        | 9        | 0          |                  | U         | J        | 4     | 3        |       | 1     | PD  |

| <del>                                     </del> |              |       |           |                      |           |          |            |                  |           |          |       | <u> </u> |       | 1     | 0   |

| PD                                               | I.           | 1     | 1         | 1 : Pow              | er down   | mode en  | able       | I.               | 1         | <u> </u> | I.    | 1        | 1     | 1     | . ~ |

|                                                  |              |       |           |                      | er down   |          |            |                  |           |          |       |          |       |       |     |

| 0x1F                                             |              | IDCOI |           |                      |           |          |            |                  |           |          |       |          |       |       |     |

| 31                                               | 30           | 29    | 28        | 27                   | 26        | 25       | 24         | 23               | 22        | 21       | 20    | 19       | 18    | 17    | 16  |

|                                                  |              |       |           |                      |           |          |            | E[31:16]         |           |          |       |          |       |       |     |

|                                                  |              |       |           |                      |           | I -      |            | 0000             | I -       |          |       | T -      |       | T -   |     |

| 15                                               | 14           | 13    | 12        | 11                   | 10        | 9        | BCOE       | 7                | 6         | 5        | 4     | 3        | 2     | 1     | 0   |

| -                                                |              |       |           |                      |           |          |            | DE[15:0]<br>0001 |           |          |       |          |       |       |     |

|                                                  |              |       |           |                      |           |          | UXU        | 1001             |           |          |       |          |       |       |     |

#### JTAG Registers Programming Timing Diagram In Unidirectional Interface

Figure 9. Serial register write programming timing diagram in JTAG

Figure 10. Serial register read programming timing diagram in JTAG

## **Electrical Specifications**

### Absolute Maximum Rating

| Parameter                                  | Symbol | Test condition | Min   | typ | max    | Unit |

|--------------------------------------------|--------|----------------|-------|-----|--------|------|

| Storage Temperature                        |        |                | -40   |     | 85     | °C   |

| Ambient Temperature with Power             |        |                | -20   |     | 65     | °C   |

| Applied                                    |        |                |       |     |        |      |

| Supply Voltage (no damage)                 |        |                | 0.8   |     | 3.9    | V    |

| DC Input Voltage                           |        |                | -0.3  |     | Vcc    | V    |

|                                            |        |                |       |     | +0.3   |      |

| DC Voltage applied to Outputs              |        |                | -0.3  |     | Vcc    | V    |

| in High-Z State                            |        |                |       |     | +0.3   |      |

| Digital Inputs                             |        |                | Vcc – |     | Vcc+0. | V    |

|                                            |        |                | 0.4V  |     | 4V     |      |

| Static Discharge Voltage (Digital)         |        |                |       |     | 2000   | V    |

| Static Discharge Voltage (RF) <sup>1</sup> |        |                |       |     | 500    | V    |

| Latch-up Current                           |        |                | -200  |     | 200    | mA   |

Note: Rating measured using the Human Body Model (HBM).

### **Recommended Operating Conditions**

| Parameter      | Symbol | Test condition | min | typ | max | Unit |

|----------------|--------|----------------|-----|-----|-----|------|

| Supply Voltage |        | VCC2.7         |     | 2.7 |     | V    |

|                |        | VCC3.3         |     | 3.3 |     | V    |

| Temperature    |        |                | 0   |     | 40  | °C   |

| Humidity       |        |                |     |     | 95  | %    |

#### DC/AC Specification

**Power Consumption**

| Parameter                   | Symbol | Test condition                 | min | typ | max | Unit |

|-----------------------------|--------|--------------------------------|-----|-----|-----|------|

| Radio Transmit Current      |        | DH1 pakaet with PRBS9 payload, |     |     | 60  | mA   |

|                             |        | no hops                        |     |     |     |      |

| Radio Receive Current       |        | DH1 pakaet with PRBS9 payload, |     |     | 60  | mA   |

|                             |        | no hops                        |     |     |     |      |

| Radio Transmit Peak current |        | DH1 pakaet with PRBS9 payload, |     |     | 70  | mA   |

|                             |        | 1.6k hops                      |     |     |     |      |

| Radio Receive Peak current  |        | DH1 pakaet with PRBS9 payload, |     |     | 70  | mA   |

|                             |        | 1.6k hops                      |     |     |     |      |

| Idle Current                |        | Tx and Rx no active            |     |     | 20  | mA   |

| Deep Sleep Current          |        | Deep Sleep Mode                |     |     | 20  | uA   |

**Common Radio Specifications**

| Parameter                | symbol | Test condition                 | min  | typ    | max  | Unit   |

|--------------------------|--------|--------------------------------|------|--------|------|--------|

| Operating Frequency      |        | f = (2.402 + k) GHz, k =       | 2402 |        | 2480 | MHz    |

|                          |        | 0,1,2,78                       |      |        |      |        |

| Channel intervals        |        |                                |      | 1      |      | MHz    |

| Channel                  |        | Number of channels             |      | 79     |      |        |

| Duplexing slot time      |        | Transmission scheme TDD – time |      | 625    |      | us     |

|                          |        | division duplex                |      |        |      |        |

| Symbol Rate              |        |                                |      | 1M     |      | symbol |

|                          |        |                                |      |        |      | /s     |

| Modulation Data Polarity |        | "H"                            |      | Fc +dF |      |        |

|                          |        | "L"                            |      | Fc -dF |      |        |

| Hop Rate                 |        |                                |      | 1600   |      | hops/s |

|                          |        |                                |      |        |      | ec     |

| Antenna interface output |        |                                |      | 50     |      | ohm    |

| impedance                |        |                                |      |        |      |        |

### **Radio Receiver Specifications**

| Parameter                        | symbol | Test condition                  | min | typ  | max | Unit |

|----------------------------------|--------|---------------------------------|-----|------|-----|------|

| Sensitivity                      |        | 0.1% BER                        |     | -85  | -80 | dBm  |

|                                  |        | DH1 pakaet with PRBS9           |     |      |     |      |

|                                  |        | payload,no hops, at             |     |      |     |      |

|                                  |        | 2402,2441,2480 MHz              |     |      |     |      |

| Maximum received signal          |        | 0.1% BER                        | -20 | -5.0 |     | dBm  |

|                                  |        | DH1 pakaet with PRBS9           |     |      |     |      |

|                                  |        | payload,no hops, at             |     |      |     |      |

|                                  |        | 2402,2441,2480 MHz              |     |      |     |      |

| Self channel selectivity         |        | C/I Co-channel (1)              |     | 9    | 11  | dBc  |

| Adjacent channel selectivity     |        | C/I 1MHz (1)                    |     | -2.0 | 0   | dBc  |

| 2nd adjacent channel selectivity |        | C/I 2MHz (1)                    |     | -34  | -30 |      |

| 3rd adjacent channel selectivity |        | C/I • 3MHz (1) (2)              |     | -43  | -40 |      |

| Image rejection                  |        | C/I (1) (3)                     |     | -12  | -9  |      |

| Maximum level of                 |        | (1) (4)                         | -39 | -30  |     | dBm  |

| intermodulation interferes       |        |                                 |     |      |     |      |

| Maximum level of GSM             |        | 0.1% BER with wanted input at – |     | -7.0 |     | dBm  |

| signal at 1.8GHz                 |        | 67dBM, and with the RF filter   |     |      |     |      |

|                                  |        | removed from the circuit, DH1   |     |      |     |      |

|                                  |        | pakaet with PRBS9 payload, 1.6k |     |      |     |      |

|                                  |        | hops                            |     |      |     |      |

| Maximum level of W-CDMA          |        |                                 |     | -9.5 |     |      |

| signal at 1.8GHz                 |        |                                 |     |      |     |      |

| Maximum level of W-CDMA          |        |                                 |     | -11  |     | dBm  |

| signal at 2.2GHz                 |        |                                 |     |      |     |      |

**Radio Transmitter Specifications**

| Parameter Parameter               | symbol | Test condition                                                 | min  | typ    | max    | Unit |

|-----------------------------------|--------|----------------------------------------------------------------|------|--------|--------|------|

|                                   |        |                                                                |      |        |        |      |

| RF transmit power level           |        | DH1 pakaet with PRBS9                                          |      |        |        | dBm  |

|                                   |        | payload,no hops, single slot                                   |      |        |        |      |

|                                   |        | packets,                                                       |      |        |        |      |

| 77                                |        | at 2402,2441,2480 MHz                                          | 4.6  | 20     |        | 170  |

| RF power control range            |        | DH1 pakaet with PRBS9                                          | 16   | 30     |        | dB   |

|                                   |        | payload,no hops, single slot packe,<br>at 2441 MHz             |      |        |        |      |

| RF power range control            |        |                                                                |      | 2.0    |        |      |

| resolution                        |        |                                                                |      |        |        |      |

| 20 dB bandwidth for               |        | DH1 pakaet with PRBS9                                          |      | 900    | 1000   | kHz  |

| modulated carrier                 |        | payload,no hops, single slot                                   |      |        |        |      |

|                                   |        | packets,                                                       |      |        |        |      |

|                                   |        | at 2402,2480 MHz                                               |      |        |        |      |

| Initial Carrier Freq Tolerance    |        | DH1 pakaet with PRBS9 payload,                                 |      | +/- 25 | +/- 75 | KHz  |

|                                   |        | no hops, single slot packe, at 2441                            |      |        |        |      |

|                                   |        | MHz                                                            |      |        |        |      |

| Frequency Deviation               |        | single slot, Continue 101010                                   | 90   |        | 175    | kHz  |

|                                   |        | pattern, 11110000 pattern, at 2441                             |      |        |        |      |

|                                   |        | MHz                                                            |      |        |        |      |

| Zero Crossing Error               |        | single slot, Continue 101010                                   | -125 |        | 125    | ns   |

|                                   |        | pattern, 11110000 pattern, at 2441                             |      |        |        |      |

|                                   |        | MHz                                                            |      |        | • •    | 45   |

| 2nd adjacent channel transmit     |        | Second Channel Power (±2 MHz),                                 |      | -52    | -20    | dBm  |

| power                             |        | DH1 pakaet with PRBS9                                          |      |        |        |      |

|                                   |        | payload,no hops, single slot                                   |      |        |        |      |

|                                   |        | packets                                                        |      |        |        |      |

| 2 4: 1 1 +                        |        | at 2441 MHz                                                    |      | -57    | -40    | 4D   |

| >3rd adjacent channel transmit    |        | Third Channel Power (>3 MHz), DH1 pakaet with PRBS9 payload,no |      | -57    | -40    | dBm  |

| power                             |        | hops, single slot packets, at 2441                             |      |        |        |      |

|                                   |        | MHz                                                            |      |        |        |      |

| Non-harmonically Related          |        | 30 MHz – 12.75 GHz                                             |      | -57    |        | dBm  |

| Spurious                          |        | at 2441 MHz                                                    |      |        |        |      |

| 2 <sup>nd</sup> Harmonic Spurious |        | at 2441 MHz                                                    |      |        | -26    | dBm  |

| 3 <sup>rd</sup> Harmonic Spurious |        | at 2441 MHz                                                    |      |        | -30    | dBm  |

| 4 <sup>th</sup> Harmonic Spurious |        | at 2441 MHz                                                    |      |        | -37    | dBm  |

#### **Notes:**

- (1) Measured according to the Bluetooth specification.

- (2) Up to five spurious responses within Bluetooth limits are allowed

- (3) At carrier –3MHz.

- (4) Measured at f1 f2 = 5MHz.

- (5) For 0.1% BER with wanted input at -67dBM, and with the RF filter removed from the circuit.

Notes

### Pericom Technology Inc.

Email: support@pti.com.cn Web Site: www.pti.com.cn, www.pti-ic.com

China: No. 20 Building, 3/F, 481 Guiping Road, Shanghai, 200233, China

Tel: (86)-21-6485 0576 Fax: (86)-21-6485 2181

Asia Pacific: Unit 1517, 15/F, Chevalier Commercial Centre, 8 Wang Hoi Rd, Kowloon Bay, Hongkong

Tel: (852)-2243 3660 Fax: (852)- 2243 3667

**U.S.A.**: 2380 Bering Drive, San Jose, California 95131, USA

Tel: (1)-408-435 0800 Fax: (1)-408-435 1100

Pericom Technology Incorporation reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. Pericom Technology does not assume any responsibility for use of any circuitry described other than the circuitry embodied in Pericom Technology product. The company makes no representations that circuitry described herein is free from patent infringement or other rights, of Pericom Technology Incorporation.