## DC – 16 GHz Packaged Divide-by-4 Prescaler

## **Technical Data**

### **HMMC-3104**

#### **Features**

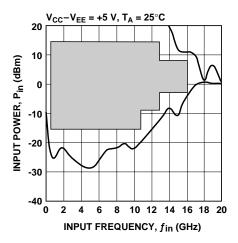

- Wide Frequency Range: 0.2 16 GHz

- High Input Power Sensitivity:

On-chip pre- and post-amps

-20 to +10 dBm (1 10 GHz)

-15 to +10 dBm (10 12 GHz)

-10 to +5 dBm (12 15 GHz)

- P<sub>out</sub>: +6 dBm (0.99 V<sub>p-p</sub>) will drive ECL

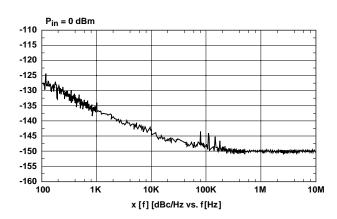

- Low Phase Noise: -153 dBc/Hz @ 100 kHz Offset

- (+) or (-) Single Supply Bias with Wide Range: 4.5 to 6.5 V

- Differential I/0 with on-chip 50  $\Omega$  matching

### **Description**

The HMMC-3104 is a packaged GaAs HBT MMIC prescaler which offers DC to 16 GHz frequency translation for use in communications and EW systems incorporating high-frequency PLL oscillator circuits and signal-path down conversion applications. The prescaler provides a large input power sensitivity window and low phase noise.

Package Type:

Package Dimensions:

Package Thickness:

Lead Pitch:

Lead Width:

8-lead SSOP Plastic

4.9 x 3.9 mm Typ.

1.55 mm Typ.

1.25 mm Nom.

0.42 mm Nom.

## **Absolute Maximum Ratings**<sup>[1]</sup>

(@  $T_A = 25$ °C, unless otherwise indicated)

| Symbol                            | Parameters/Conditions                                                                | Units | Min.                 | Max.                 |

|-----------------------------------|--------------------------------------------------------------------------------------|-------|----------------------|----------------------|

| $V_{CC}$                          | Bias Supply Voltage                                                                  | volts |                      | +7                   |

| $V_{\rm EE}$                      | Bias Supply Voltage                                                                  | volts | -7                   |                      |

| V <sub>CC</sub> - V <sub>EE</sub> | Bias Supply Delta                                                                    | volts | +7                   |                      |

| $V_{Logic}$                       | Logic Threshold Voltage                                                              | volts | V <sub>CC</sub> -1.5 | V <sub>CC</sub> -1.2 |

| P <sub>in(CW)</sub>               | CW RF Input Power                                                                    | dBm   |                      | +10                  |

| V <sub>RFin</sub>                 | DC Input Voltage<br>(@ RF <sub>in</sub> or $\overline{\text{RF}}_{\text{in}}$ Ports) | volts |                      | $V_{\rm CC} \pm 0.5$ |

| $T_{BS}^{[2]}$                    | Backside Operating Temp.                                                             | °C    | -40                  | +85                  |

| T <sub>STG</sub>                  | Storage Temperature                                                                  | °C    | -65                  | +165                 |

| T <sub>max</sub>                  | Maximum Assembly Temp. (60 seconds max.)                                             | °C    |                      | 310                  |

#### Notes

- 1. Operation in excess of any parameter limit (except  $T_{\text{BS}}$ ) may cause permanent damage to the device.

- 2. MTTF > 5 x  $10^5$  hours @  $T_{BS}$  <  $85^{\circ}$ C. Operation in excess of maximum operating temperature ( $T_{BS}$ ) will degrade MTTF.

# HMMC-3104 DC Specifications/Physical Properties, (T\_A = 25 °C, V\_{CC} - V\_{EE} = 5.0 V unless otherwise listed)

| Symbol                                                    | <b>Parameters and Test Conditions</b>                                                      | Units | Min.                   | Тур.                   | Max.                   |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------|-------|------------------------|------------------------|------------------------|

| V <sub>CC</sub> - V <sub>EE</sub>                         | Operating Bias Supply Difference <sup>[1]</sup>                                            | volts | 4.5                    | 5.0                    | 6.5                    |

| $ I_{CC} $ or $ I_{EE} $                                  | Bias Supply Current                                                                        | mA    | 68                     | 80                     | 92                     |

| $\begin{matrix} V_{RFin(q)} \\ V_{RFout(q)} \end{matrix}$ | Quiescent DC Voltage appearing at all RF Ports                                             | volts |                        | $V_{CC}$               |                        |

| $V_{Logic}$                                               | Nominal ECL Logic Level ( $V_{\text{Logic}}$ contact self-bias voltage, generated on-chip) | volts | V <sub>CC</sub> - 1.45 | V <sub>CC</sub> - 1.35 | V <sub>CC</sub> - 1.25 |

#### Note:

## **RF Specifications,** $(T_A = 25^{\circ}C, Z_O = 50\Omega, V_{CC} - V_{EE} = 5.0 \text{ V})$

| Symbol                           | <b>Parameters and Test Conditions</b>                                                                                                                                                        | Units  | Min. | Тур. | Max. |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|------|

| $f_{\rm in(max)}$                | Maximum input frequency of operation                                                                                                                                                         | GHz    | 16   | 18   |      |

| $f_{ m in(min)}$                 | Minimum input frequency of operation <sup>[1]</sup> (P <sub>in</sub> = -10 dBm)                                                                                                              | GHz    |      | 0.2  | 0.5  |

| $f_{ m Self	ext{-}Osc.}$         | Output Self-Oscillation Frequency <sup>[2]</sup>                                                                                                                                             | GHz    |      | 3.4  |      |

| P <sub>in</sub>                  | @ DC, (Square-wave input)                                                                                                                                                                    | dBm    | -15  | >-25 | +10  |

|                                  | @ $f_{in}$ = 500 MHz, (Sine-wave input)                                                                                                                                                      | dBm    | -15  | >-20 | +10  |

|                                  | $f_{\rm in}$ = 1 to 10 GHz                                                                                                                                                                   | dBm    | -15  | >-25 | +10  |

|                                  | $f_{\rm in}$ = 10 to 12 GHz                                                                                                                                                                  | dBm    | -10  | >-15 | +10  |

|                                  | $f_{\rm in}$ = 12 to 15 GHz                                                                                                                                                                  | dBm    | -4   | >-10 | +4   |

| RL                               | Small-Signal Input/Output Return Loss (@ $f_{\rm in}$ < 12 GHz)                                                                                                                              | dB     |      | 15   |      |

| S <sub>12</sub>                  | Small-Signal Reverse Isolation (@ $f_{in}$ < 12 GHz)                                                                                                                                         | dB     |      | 30   |      |

| $\phi_{ m N}$                    | SSB Phase Noise (@ $P_{in} = 0$ dBm, 100 kHz offset from a $f_{out} = 1.2$ GHz Carrier                                                                                                       | dBc/Hz |      | -153 |      |

| Jitter                           | Input Signal Time Variation @ Zero-Crossing $(f_{in} = 10 \text{ GHz}, P_{in} = -10 \text{ dBm})$                                                                                            | ps     |      | 1    |      |

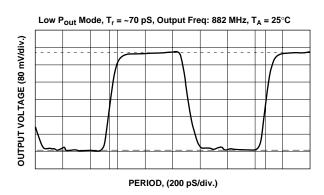

| T <sub>r</sub> or T <sub>f</sub> | Output Transition Time (10% to 90% rise/fall time)                                                                                                                                           | ps     |      | 70   |      |

|                                  | $@f_{\text{out}} < 1 \text{ GHz}$                                                                                                                                                            | dBm    | 4    | 6    |      |

| P <sub>out</sub> <sup>[3]</sup>  | $f_{\text{out}} = 2.5 \text{ GHz}$                                                                                                                                                           | dBm    | 3.5  | 5.5  |      |

|                                  | $f_{\text{out}} = 3.5 \text{ GHz}$                                                                                                                                                           | dBm    | 0    | 2.0  |      |

|                                  | $@f_{\text{out}} < 1 \text{ GHz}$                                                                                                                                                            | volts  |      | 0.99 |      |

| $ V_{\text{out}(p-p)} ^{[4]}$    | $f_{\text{out}} = 2.5 \text{ GHz}$                                                                                                                                                           | volts  |      | 0.94 |      |

|                                  | $f_{\text{out}} = 3.5 \text{ GHz}$                                                                                                                                                           | volts  |      | 0.63 |      |

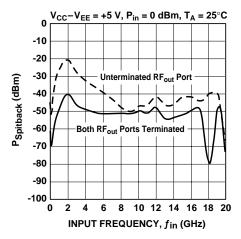

| P <sub>Spitback</sub>            | $f_{ m out}$ power level appearing at RF <sub>in</sub> or $\overline{ m RF}_{ m in}$ (@ $f_{ m in}$ = 12 GHz, Unused RF <sub>out</sub> or $\overline{ m RF}_{ m out}$ unterminated)          | dBm    |      | -40  |      |

|                                  | $f_{\rm out}$ power level appearing at RF <sub>in</sub> or $\overline{\rm RF}_{\rm in}$ (@ $f_{\rm in}$ = 12 GHz, Both RF <sub>out</sub> & $\overline{\rm RF}_{\rm out}$ <b>terminated</b> ) | dBm    |      | -47  |      |

| P <sub>feedthru</sub>            | Power level of $f_{in}$ appearing at RF <sub>out</sub> or $\overline{RF}_{out}$ (@ $f_{in}$ = 12 GHz, $P_{in}$ = 0 dBm, Referred to $P_{in}(f_{in})$ )                                       | dBc    |      | -23  |      |

| H <sub>2</sub>                   | Second harmonic distortion output level (@ $f_{out} = 3.0$ GHz, Referred to $P_{out}(f_{out})$ )                                                                                             | dBc    |      | -25  |      |

#### **Notes:**

- 1. For sine-wave input signal. Prescaler will operate down to D.C. for square-wave input signal. Minimum divide frequency limited by

- 2. Prescaler can exhibit this output signal under bias in the absence of an RF input signal. This condition may be eliminated by use of the input DC offset technique described on page 3.

- 3. Fundamental of output square wave's Fourier Series.

- 4. Square wave amplitude calculated from Pout.

<sup>1.</sup> Prescaler will operate over full specified supply voltage range.  $V_{CC}$  or  $V_{EE}$  not to exceed limits specified in Absolute Maximum Ratings section.

## **Applications**

The HMMC-3104 is designed for use in high frequency communications, microwave instrumentation, and EW radar systems where low phase-noise PLL control circuitry or broad-band frequency translation is required.

## **Operation**

The device is designed to operate when driven with either a single-ended or differential sinusoidal input signal over a 200 MHz to 16 GHz bandwidth. Below 200 MHz the prescaler input is "slew-rate" limited, requiring fast rising and falling edge speeds to

properly divide. The device will operate at frequencies down to DC when driven with a squarewave. AC coupling at  $P_{in}$  5 (RF $_{in}$ ) is recommended for most applications.

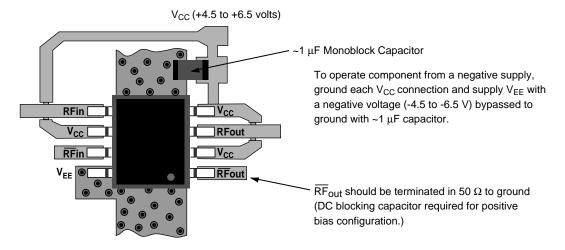

The device can be operated from either a single positive or single negative supply. For positive supply operation  $V_{CC}$  pins are nominally biased at any voltage in the +4.5 to +6.5 volt range with  $P_{in}$  8 ( $V_{EE}$ ) grounded. For negative bias operation  $V_{CC}$  pins are typically grounded and a negative voltage between -4.5 to -6.5 volts is applied to  $P_{in}$  8 ( $V_{EE}$ ).

## **Input DC Offset**

To prevent false triggers or self-oscillation conditions, apply a 20 to 100 mV DC offset voltage between the RF $_{\rm in}$  and  $\overline{\rm RF}_{\rm in}$  ports. This prevents noise or spurious low level signals from triggering the divider.

GaAs MMICs are ESD sensitive. Proper precautions should be used when handling these devices.

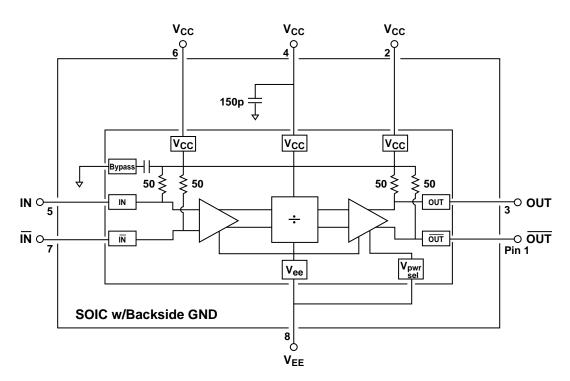

Figure 1. HMMC-3104 Simplified Schematic.

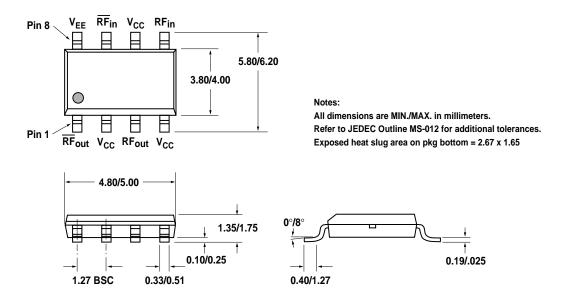

Figure 2. Package and Dimensions.

Figure~3.~Assembly~Diagram.~(single-supply,~positive-bias~configuration~shown)

## **HMMC-3104 Supplemental Data**

Figure 4. Typical Input Sensitivity Window.

Figure 6. Typical Output Voltage Waveform.

Figure 8. Typical Phase Noise Performance.

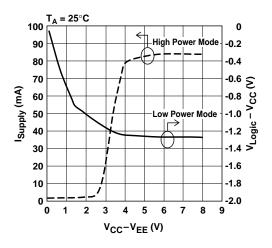

Figure 5. Typical Supply Current &  $\ensuremath{V_{Logic}}\xspace$  vs. Supply Voltage.

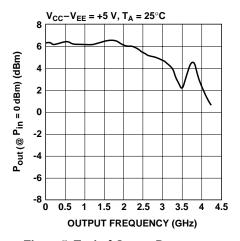

Figure 7. Typical Output Power vs. Output Frequency,  $f_{out}$  (GHz).

Figure 9. Typical "Spitback" Power.  $P(f_{out})$  appearing at RF input port.

## **Supplemental Information Input DC Offset**

As long as an RF signal is always present and within the input power specifications, there will not be any problems with false triggering or self-oscillations. If this is not the case, you can put ≈10KΩ to ground from the unused input and this, when combined with the on-chip  $50\Omega$  resistor to  $V_{CC} = 5$ , will put an offset of ≈25 mV between the RF inputs (i.e., if  $\overline{\mbox{RF}}_{in}$  has 10KQ to ground, it will be at  $\approx 4.975\,V$  and  $RF_{in}$  will be at  $\approx 5$  V). If you want a 20 to 100 mV offset per the note on page 3, the resistor value to ground will be  $12.45 \text{K}\Omega$  to  $2.45 \text{K}\Omega$ when  $V_{CC} = 5$ .

## **Biasing and DC-Blocking**

The backside of the divider chip is gold plated and attached to the heat slug in the package. Also in the package is a capacitor connected between the chip's topside  $V_{CC}$  rail and the heat slug making the heat slug an RF ground. In the majority of cases, you would tie the exposed heat slug on the bottom of the package to ground. In a typical positive bias setup with  $V_{CC} = 5$ ,  $V_{EE}$  is DC ground

along with the package's heat slug. The RF input and RF output nodes are each tied to V<sub>CC</sub> through  $50\Omega$  and will be floating nominally at that bias level (depending, of course, on the input drive level and the appropriate output state) so blocking capacitors will usually be required. For a typical negative bias setup with  $V_{\rm EE}$  = -5,  $V_{\rm CC}$  is DC ground along with the package's heat slug. In some cases, such as level shifting to subsequent stages, you might want to "float" the package and apply bias as the difference between V<sub>CC</sub> and V<sub>EE</sub>. For such applications, the package's heat slug must be attached to a point that is both a good heat sink and a good RF ground.

### **Heat Slug/Bonding Pad**

The exposed area of the package's backside heat slug (or pad) measures 2.67 x 1.65 mm (0.105" x 0.065"). Anything larger than this on a PCB would be at the customer's preference or convenience. On our test PCBs, we use a 0.200" x 0.082" pad with eight 0.020" diameter solder-filler thermal vias.