# R65C10 One-Chip Microcomputer

# SECTION I

#### SUMMARY

The Rockwell R65C10 microcomputer is a complete 8-bit computer fabricated on a single chip using an N-well silicon gate CMOS process. The R65C10 complements an industry standard line of R6500 and R65C00 microprocessors, R6500/\* and R65C00/\* microcomputers and compatible peripheral devices. The R65C10 has a wide range of microcomputer applications where high 8-bit performance, minimal chip count and low power consumption is required.

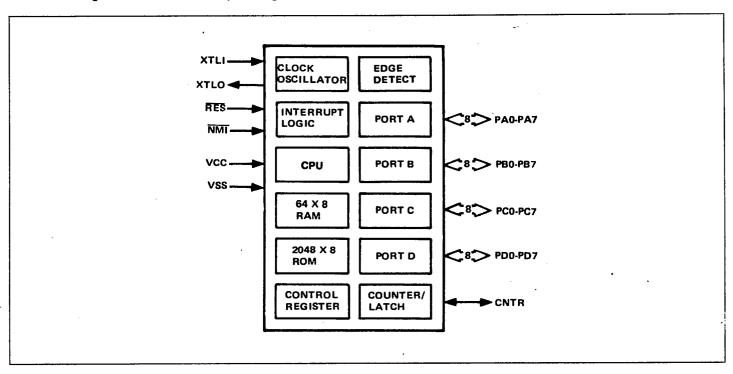

The R65C10 consists of a 6502 Central Processing Unit (CPU), 2048 bytes of mask programmable Read Only Memory (ROM), 64 bytes of Random Access Memory (RAM) and interface circuitry for peripheral devices. The parallel interface consists of four 8-bit ports including two edge detect lines. A 16-bit counter/timer with four selectable modes is also included.

The innovative architecture and the demonstrated nigh performance of the R65C02 CPU, as well as instruction simplicity, result in system cost-effectiveness and a wide range of computational power. These features make the R65C10 a leading candidate for low-power single-chip microcomputer applications.

Hardware enhancements of the R65C10 include a software-controlled system and/or counter/timer clock prescaler, and an ultra-low-power Stop mode.

This description assumes that the reader is familiar with the R6502 CPU programming capabilities as described in the R6500 Programming Manual (Order No. 202).

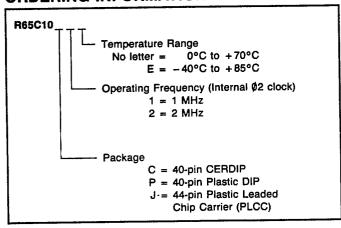

#### ORDERING INFORMATION

#### **FEATURES**

- · Single-chip microcomputer

- R6502 CPU instruction compatible

- 8-bit parallel processing

- · Decimal or binary arithmetic

- Variable length stack

- True indexing capability

- 13 addressing modes

- Internal 1 MHz to 2 MHz clock with crystal or clock input

- Internal divide-by-2 network

- 2 MHz to 4 MHz crystal input

- 20 kHz to 4 MHz clock input

- Software-controllable prescaler

- Selectable system clock and timer clock prescaler or timer clock only prescaler

- Divide by 8, 32, 64, or 128 options

- Low-power oscillator Stop mode (cleared by RES)

- 15 mW to 30 mW operating power (1 MHz to 2 MHz)

- 2K x 8 ROM on-chip

- 64 x 8 RAM on-chip

- 32 bidirectional TTL compatible I/O lines

- 1 positive edge-sensitive I/O line

- 1 negative edge-sensitive I/O line

- 1 bidirectional TTL compatible counter I/O line

- 16-bit buffered timer/counter with four modes

- Interval timer

- Pulse generator

- Event counter

- Pulse width measurement

- Three maskable interrupt requests (IRQ)

- 1 counter overflow

- -2 I/O edge detect

- . NMI and RES inputs

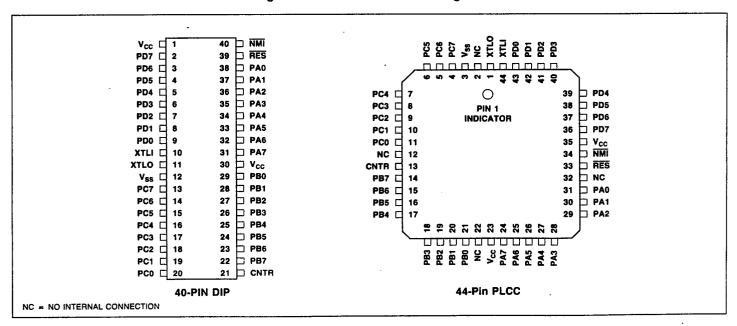

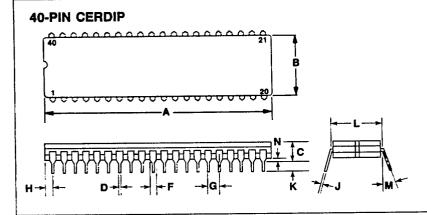

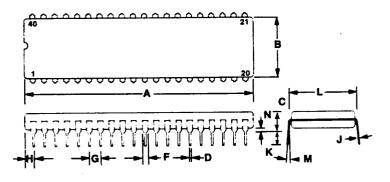

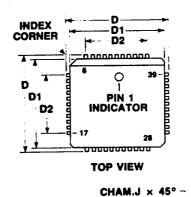

- Available in 40-pin DIP and 44-pin PLCC packages

- +5V ± 10% power

Document No. 29651N93 Product Description

Order No. 2193 Rev. 2, November 1991

# SECTION 2 INTERFACE DESCRIPTION

This section describes the interface requirements for the R65C10 single-chip microcomputer. An interface diagram for the R65C10 is shown in Figure 2-1. The R65C10 pin assignments are

identified in Figure 2-2. The function of each pin of the R65C10 is explained in Table 2-1.

Figure 2-1. R65C10 Interface Diagram

Figure 2-2. R65C10 Pin Assignments

## Table 2-1. R65C10 Pin Description

| Signal Name     | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>cc</sub> |     | POWER. +5 Vdc; must be connected to both pins.                                                                                                                                                                                                                                                                                                                          |

| V <sub>SS</sub> |     | GROUND. Signal return and power ground (0V).                                                                                                                                                                                                                                                                                                                            |

| XTLI            | 1   | CRYSTAL INPUT. The crystal or external clock input to the internal clock oscillator. The oscillator generates the internal master clock at the frequency of the input crystal/clock divided either by 1 or by 2 depending upon mask option. The system and counter/timer clocks are derived from the master clock under control of the Prescaler Control Register.      |

| XTLO            | 0   | CRYSTAL OUTPUT. The crystal output from the internal clock oscillator. XTLO should be left open when a clock is input at XTLI.                                                                                                                                                                                                                                          |

| RES             | 1   | <b>RESET.</b> The active low $\overline{\text{RES}}$ input initializes the R65C10. This signal must not transition from low to high for at least eight cycles after $V_{CC}$ reaches operating range and the internal oscillator has stabilized.                                                                                                                        |

| ЙMI             | 1   | NON-MASKABLE INTERRUPT. A negative-going edge on the NMI input interrupts the CPU.                                                                                                                                                                                                                                                                                      |

| PA0-PA7         | 1/0 | PORT A. General purpose I/O Port A.                                                                                                                                                                                                                                                                                                                                     |

| PB0-PB7         | 1/0 | PORT B. General purpose I/O Port B.                                                                                                                                                                                                                                                                                                                                     |

| PC0-PC7         | 1/0 | PORT C. General purpose I/O Port C.                                                                                                                                                                                                                                                                                                                                     |

| PD0-PD7         | 1/0 | PORT D. General purpose I/O Port D.                                                                                                                                                                                                                                                                                                                                     |

|                 |     | Four 8-bit ports used for either input or output. Each line consists of an active transistor to V <sub>SS</sub> and an optional active pull-up to V <sub>CC</sub> (see Section 4.3). The two lower bits of the Port A (PA0 and PA1) also serve as edge-detect inputs with maskable interrupts. PA0 detects a positive-going edge and PA1 detects a negative-going edge. |

| CNTR            | 1/0 | <b>COUNTER</b> . This line is either an input to, or an output from, the counter. CNTR is an input in the event counter and pulse width measurement modes, and is an output in the pulse generator modes. It consists of an active transistor to $V_{SS}$ and an optional active pull-up to $V_{CC}$ .                                                                  |

# SECTION 3 SYSTEM ARCHITECTURE

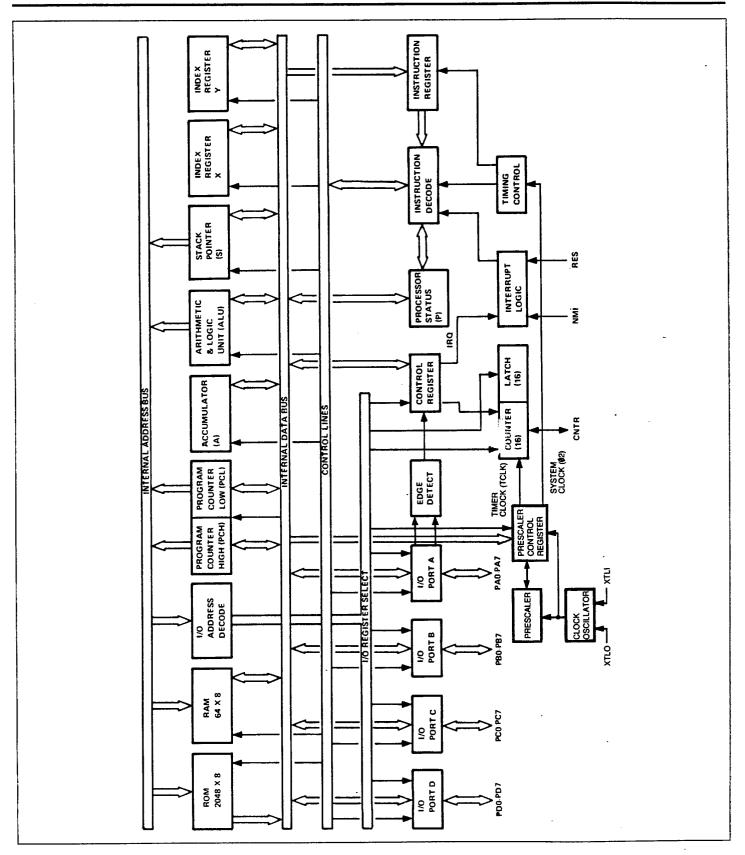

This section provides a functional description of the R65C10. A block diagram of the R65C10 is presented in Figure 3-1.

#### 3.1 INDEX REGISTERS

There are two 8-bit index registers: X and Y. Either index register can be used as a base to modify the program counter contents and thus obtain a new address—the sum of the program counter contents and the index register contents.

When executing an instruction which specifies indexed addressing, the CPU fetches the op code and the address, and modifies the address from memory by adding the index register to it prior to loading or storing the value of memory.

#### 3.2 STACK POINTER

The Stack Pointer is an 8-bit register. It is automatically incremented and decremented under control of the CPU to perform stack manipulation in response to program instructions, the NMI interrupt input or the internally generated IRQ interrupt. The Stack Pointer must be initialized by the user program. The JSR, BRK, RTI, and RTS instructions use the stack and the Stack Pointer. The stack is located in RAM from address 0 to address \$3F (0 to 63 decimal).

#### 3.3 ARITHMETIC AND LOGIC UNIT (ALU)

All arithmetic and logic operations take place in the ALU, including incrementing and decrementing internal registers (except the Program Counter). The ALU cannot store data for more than one cycle. If data is placed on the inputs to the ALU at the beginning of a cycle, the result is always gated into one of the storage registers or to memory during the next cycle.

Each bit of the ALU has two inputs. These inputs can be tied to various internal buses or to a logic 0; the ALU then generates the function (AND, OR, SUM, and so on) using the data on the two inputs.

#### 3.4 ACCUMULATOR

The Accumulator is a general purpose 8-bit register that stores the results of most arithmetic and logic operations. In addition, the Accumulator usually contains one of the two data words used in these operations.

#### 3.5 PROGRAM COUNTER

The 12-bit Program Counter provides the addresses that step the processor through sequential instructions in a program. Each time the processor fetches an instruction from the program memory, the lower (least significant) byte of the Program Counter (PCL) is placed on the eight low-order lines of the internal address bus and the higher (most significant) byte of the Program Counter (PCH) is placed on the four high-order lines of the internal address bus. The Program Counter is incremented each time an instruction or data is fetched from program memory.

# 3.6 INSTRUCTION REGISTER AND INSTRUCTION DECODE

Instructions are fetched from ROM or RAM and gated onto the internal data bus. These instructions are latched into the Instruction Register, then decoded along with timing and interrupt signals to generate control signals for the various registers.

#### 3.7 PROCESSOR STATUS REGISTER (PSR)

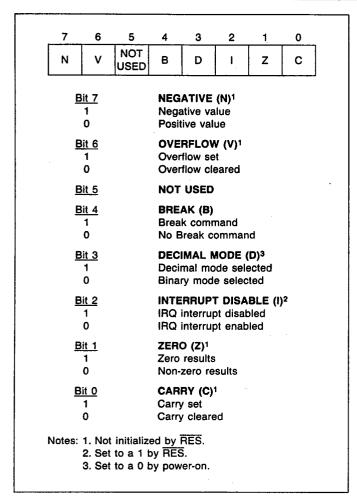

The 8-bit Processor Status Register, shown in Figure 3-2, contains seven status flags. Some of these flags are controlled by the user program; others may be controlled both by the user program and the CPU. The R65C10 instruction set contains a number of conditional branch instructions which allow testing of these flags. Each of the seven processor status flags is described in the following paragraphs.

#### CARRY (C) BIT

The Carry (C) bit can be considered as the ninth bit of an arithmetic operation. It is set to logic 1 if a carry from the eighth bit has occurred, or cleared to logic 0 of no carry occurred, as the result of arithmetic operations.

The Carry bit may be set or cleared under program control by use of the Set Carry (SEC) or Clear Carry (CLC) instruction, respectively. Other operations which affect the Carry bit are ADC, ASL, CMP, CPX, CPY, LSR, PLP, ROL, ROR, RTI, and SBC.

#### ZERO (Z) BIT

The Zero (Z) bit is set to logic 1 by the CPU during any data movement or by any calculation which sets all eight bits of the result to zero. This bit is cleared to logic 0 when the resultant eight bits of a data movement or calculation operation are not all zero. The R65C10 instruction set contains no instruction to specifically set or clear the Zero bit. The Zero bit is, however, affected by the following instructions: ADC, AND, ASL, BIT, CMP, CPX, CPY, DEC, DEX, DEY, EOR, INC, INX, INY, LDX, LDX, LDY, LSR, ORA, PLA, PLP, ROL, ROR, RTI, SBC, TAX, TAY, TXA, TSX, and TYA.

Figure 3-1. R65C10 Block Diagram

Figure 3-2. Processor Status Register

#### INTERRUPT DISABLE (I) BIT

The Interrupt Disable (I) bit controls the servicing of the internal interrupt request (IRQ). If the I bit is reset to logic 0, the IRQ will be serviced. If the bit is set to logic 1, the IRQ will be ignored. The CPU will set the Interrupt Disable bit to logic 1 if NMI, an enabled IRQ interrupt or the RES signal is detected.

The I bit is restored by the Pull Processor Status from Stack (PLP) instruction, or as the result of executing a Return from Interrupt (RTI) instruction (provided the Interrupt Disable bit was cleared prior to the interrupt). The Interrupt Disable bit may be set or cleared under program control using a Set Interrupt Disable (SEI) or a Clear Interrupt Disable (CLI) instruction, respectively.

#### **DECIMAL MODE (D) BIT**

The Decimal Mode (D) bit controls the arithmetic mode of the CPU. When this bit is set to a logic 1, the adder operates as

a decimal adder. When this bit is cleared to logic 0, the adder operates as a straight binary adder. The adder mode is controlled only by two instructions. The Set Decimal Mode (SED) instruction sets the D bit; the Clear Decimal Mode (CLD) instruction clears it. The PLP and RTI instructions also affect the Decimal Mode Bit. The Decimal Mode Bit is cleared upon power application and by RES thus establishing binary mode.

#### **BREAK (B) BIT**

The Break (B) bit indicates the condition which caused the IRQ service routine to be entered. If the IRQ service routine was entered because the CPU executed a BRK command, the B bit will be set to logic 1. If the IRQ routine was entered as the result of an IRQ occurring, the B bit will be cleared to logic 0. There are no instructions which can set or clear this bit.

#### **OVERFLOW (V) BIT**

The Overflow (V) bit indicates that the result of a signed, binary addition or subtraction operation is a value that cannot be contained in seven bits ( $-128 \le n \le +127$ ). The indicator only has meaning when signed arithmetic (sign and seven magnitude bits) is performed. When the ADC or SBC instruction is performed, the V bit is set to logic 1 if the polarity of the sign bit (bit 7) is changed because the result exceeds +127 or -128; otherwise the V bit is cleared to logic 0. The V bit may also be cleared under program control by the Clear Overflow (CLV) instruction.

The Overflow bit may also be used with the BIT instruction. The BIT instruction, which may be used to sample interface devices, allows the Overflow bit to reflect the condition of Bit 6 in the sampled field. During a BIT instruction, the Overflow bit is set equal to the content of Bit 6 of the data tested with the BIT instruction. When used in this mode, the Overflow bit has nothing to do with signed arithmetic, but is just another sense bit for the CPU. Instructions which affect the V flag are ADC, BIT, CLV, PLP, RTI, and SBC.

#### **NEGATIVE (N) BIT**

The Negative (N) bit copies the arithmetic sign bit value resulting from a data movement or an arithmetic operation. If the sign bit is set, the resulting value of the data movement or arithmetic operation is negative and the N bit is a logic 1; if the sign bit is cleared, the result of the data movement or arithmetic operation is positive and the N bit is a logic 0. There are no instructions that set or clear the N bit since the N bit represents only the status of a result. The instructions that affect the state of the bit are: ADC, AND, ASL, BIT, CMP, CPX, CPY, DEC, DEX, DEY, EOR, INC, INX, INY, LDA, LDX, LDY, LSR, ORA, PLA, PLP, ROL, ROR, RTI, SBC, TAX, TAY, TSX, TXA, and TYA.

#### R65C10

#### 3.8 I/O ADDRESS DECODE

The internal memory, control registers, I/O ports, and Counter/ Latch are memory mapped into the 4096-byte address space. The I/O Address Decode logic decodes the address from the internal address bus and routes enable signals to the appropriate functions. The memory map of the R65C10 is shown in Figure 3-3.

|                                                                                                | Add        | ress       |

|------------------------------------------------------------------------------------------------|------------|------------|

| Parameter                                                                                      | Hex        | Dec        |

| IRQ Vector High                                                                                | FFF        | 4095       |

| IRQ Vector Low                                                                                 | FFE        | 4094       |

| RES Vector High                                                                                | FFD        | 4093       |

| RES Vector Low                                                                                 | FFC        | 4092       |

| NMI Vector High                                                                                | FFB        | 4091       |

| NMI Vector Low                                                                                 | FFA        | 4090       |

|                                                                                                | FF9        | 4089       |

| R65C10 User Program                                                                            |            | :          |

|                                                                                                | 800        | 2048       |

|                                                                                                | 7FF        | 2047       |

| Unassigned                                                                                     | :          | :          |

|                                                                                                | 094        | 148        |

| Port D Direction Register (Write Only)3                                                        | 093        | 147        |

| Port C Direction Register (Write Only)3                                                        | 092        | 146        |

| Port B Direction Register (Write Only)3                                                        | 091        | 145        |

| Port A Direction Register (Write Only)3                                                        | 090        | 144        |

| Control Register (CR)                                                                          | 08F        | 143        |

| Prescaler Control Register (PCR)                                                               | 08E        | 142        |

| Stop Mode (Write Only)3                                                                        | 08D        | 141        |

| Unassigned                                                                                     | 08C<br>08B | 140<br>139 |

| Clear PA1 Neg Edge Detected (Write Only)1                                                      | 08A        | 138        |

| Clear PA0 Pos Edge Detected (Write Only)1                                                      | 089        | 137        |

| Upper Latch and Transfer Latch to Counter,<br>Clear Counter Overflow (Write Only) <sup>2</sup> | 088        | 136        |

| Lower Count, Clear Counter Overflow (Read Only) <sup>2</sup>                                   | 087        | 135        |

| Upper Count (Read Only)                                                                        | 086        | 134        |

| Lower Latch (Write Only)                                                                       | 085        | 133        |

| Upper Latch (Write Only)                                                                       | 084        | 132        |

| Port D (PD)                                                                                    | 083        | 131        |

| Port C (PC)                                                                                    | 082        | 130        |

| Port B (PB)                                                                                    | 081        | 129        |

| Port A (PA)                                                                                    | 080        | 128        |

|                                                                                                | 07F        | 127        |

| Unassigned                                                                                     |            | 1 :        |

| •                                                                                              | 040        | 64         |

|                                                                                                | 03F        | 63         |

| User RAM                                                                                       | 1 :        | 1 :        |

|                                                                                                | 000        | 0          |

2. Clears Counter Overflow — Bit 7 in Control Register.

3. Mask option.

Figure 3-3. R65C10 Memory Map

#### 3.9 2K×8 ROM

The internal 2,048 x 8-bit Read Only Memory (ROM) usually contains the user's program instructions and other fixed constants. These program instructions and constants are maskprogrammed during fabrication.

The ROM is mapped from \$800 to \$FFF.

#### 3.10 64×8 RAM

The internal 64 x 8-bit Random Access Memory (RAM) contains the user program stack and is used for scratchpad memory during system operation. This RAM is completely static in operation and requires no clock or dynamic refresh. The data contained in RAM is read out nondestructively with the same polarity as the input data. In the event that execution stops, RAM data is retained until execution resumes.

The R65C10 RAM is assigned page zero memory address 0 to \$03F.

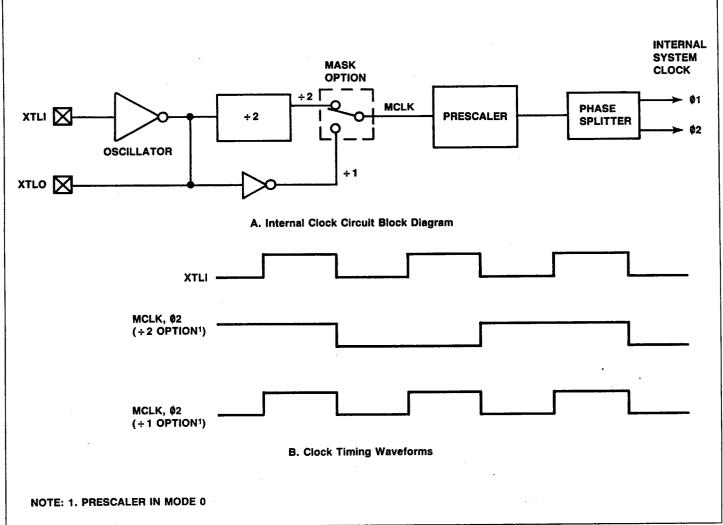

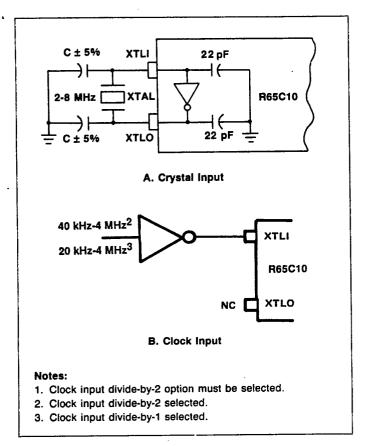

#### 3.11 CLOCK OSCILLATOR

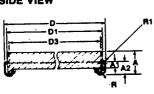

The Clock Oscillator provides the basic timing signals used by the R65C10. The reference frequency is provided by an external source and can be from a crystal or clock input. The external frequency may vary from 2 MHz to 4 MHz for a parallel resonant crystal input or from 20 kHz to 4 MHz for a clock input. The external clock rate is divided by 2 or 1 to generate an internal master clock (MCLK) as shown in Figure 3-4. Selection of the input crystal/clock divide-by-2 or divide-by-1 is a mask option. The divide-by-2 option can be used with either a crystal or clock input. The divide-by-1 option can be used only with a clock input. The divide-by-2 option causes the R65C10 to operate at the same internal frequency as the R6500/1 or R6500/1E when connected to the same input clock frequency. MCLK may be prescaled by four different values under program control (discussed below).

The on-chip oscillator is designed for a parallel resonant crystal connected between XTLI and XTLO pins. The equivalent oscillator circuit is shown in Figure 3-5A.

A parallel resonant crystal is specified by its load capacitance and series resonant resistance. For proper oscillator operation, the load capacitance (CL), series resistance (Rs) and the crystal resonant frequency (F) must meet the following two relations:

$$(C + 22) = 2C_L$$

or  $C = 2C_L - 22$

$$R_s \le R_{smax} = \frac{2 \times 10^6}{(FC_L)^2}$$

where: F is in MHz; C and CL are in pF; R is in ohms.

To select a parallel resonant crystal for the oscillator, first select the load capacitance from a crystal manufacturer's catalog. Next, calculate  $R_{\text{smax}}$  based on F and  $C_{\text{L}}$ . The selected crystal must have a Rs less than the Rsmax.

# One-Chip Microcomputer INTERNAL

Figure 3-4. Internal System Clock Timing

For example, if C<sub>L</sub> = 30 pF for a 4 MHz parallel resonant crystal, then

$C = (2 \times 30) - 22 = 38 pF$  (Use standard value of 39 pF.)

(Note: C = Total shunt capacitance including that due to board layout.)

The series resistance of the crystal must be less than

$$R_{\text{smax}} = \frac{2 \times 10^6}{(4 \times 30)^2} = 139 \text{ ohms}$$

The R65C10 internal oscillator and clock can be stopped under program control (Stop mode) and restarted by a RES input. The Stop mode is described in Section 4.

#### 3.12 PRESCALER CONTROL

Clock prescaler mode and value selection is controlled by the Prescaler Control Register (PCR) at the address \$08E (see Figure 3-6). The prescaler mode (PM) is determined by the value written to bits 0 and 1. The prescaler value (PV) is determined by the value written to bits 2 and 3. The system clock (\$\psi2\$) and timer clock (TCLK) rates are determined by the combination of selected prescaler mode and value. When prescaler mode 0 is selected, Ø2 and TCLK both run at the internal master clock (MCLK) rate regardless of the selected prescaler value. Ø2 runs at MCLK in prescaler modes 0 and 1 and at MCLK ÷ PV in prescaler mode 3. TCLK runs at MCLK in prescaler mode 0 and at MCLK ÷ PV in prescaler modes 1 and 3. Prescaler mode 2 is illegal and will cause indeterminate operation if selected.

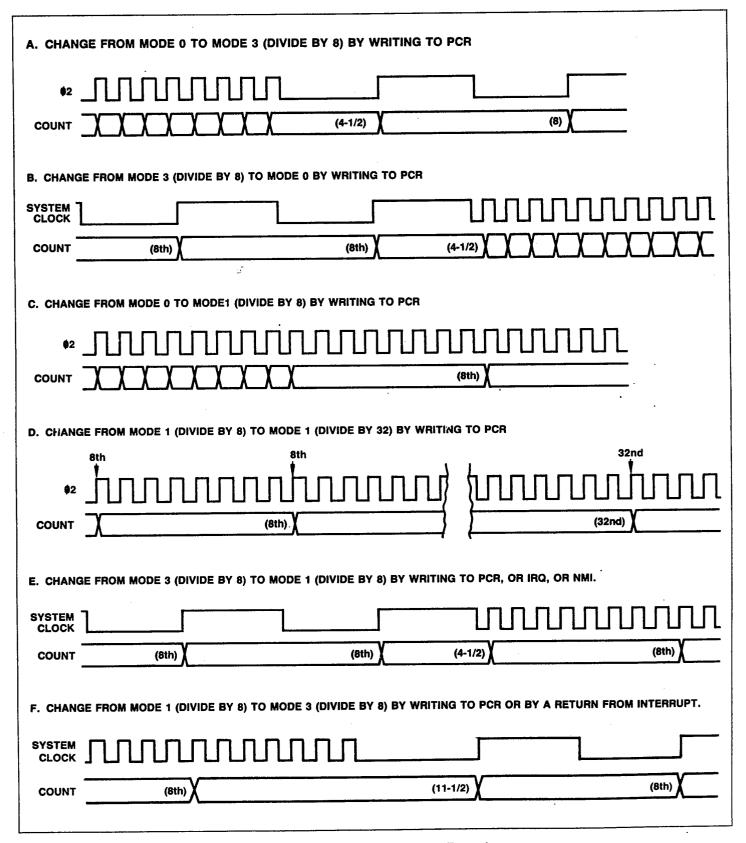

The selected prescaler value is invoked in the cycle following the write or interrupt occurrence. Waveforms for five of these operations are illustrated in Figure 3-7.

Figure 3-5. Clock Oscillator Input Options

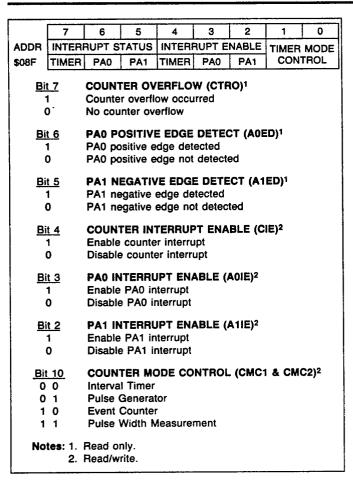

#### 3.13 CONTROL REGISTER (CR)

The Control Register (CR), shown in Figure 3-8, is located at address \$8F. The CR contains five control bits and three status bits. The control bits must be written to the Control Register. The status bits can be read, along with the previously written control bits, by reading the register. All control and status bits in the Control Register are cleared to 0 by the assertion of  $\overline{\text{RES}}$ . The signals controlled by and reported in the CR are described in the following paragraphs.

Bits 0 to 4 in the Control Register are control bits (Figure 3-8). The control signals are set by writing a 1 into the respective bit position, and cleared either by writing a 0 into the respective bit position or by assertion of  $\overline{\text{RES}}$ .

Bits 5 to 7 in the Control Register are status bits (Figure 3-8). The status bits are read-only information. Each status bit is set to a 1 by monitoring circuitry, and is cleared to a 0 either by writing to specific address or by assertion of  $\overline{\text{RES}}$ .

#### **COUNTER MODE CONTROL 0 AND 1**

Counter Mode Control signals CMC0 and CMC1 (bits 0 and 1) control the Counter operating modes. The modes of operation and the corresponding configuration of CMC0 and CMC1 are shown in Figure 3-8. These modes are selected by writing the appropriate bit values into the Counter Mode Control bits.

|               | 7            | 6          | 5 (      | 4 3      | 2      | 1          | 0       |

|---------------|--------------|------------|----------|----------|--------|------------|---------|

| ADDR<br>\$08E |              | NOT US     | SED      | V        | ı Vo   | <b>M</b> 1 | MO      |

| Bits 3-2      | Pres         | scaler Va  | lue (PV) | Select1  | I      |            |         |

| <u>V1</u>     | <u>V0</u>    |            | Presc    | ale Valu | e      |            |         |

| 0             | 0            |            | Divide   | by 8     |        |            |         |

| 0             | 1            |            | Divide   | by 32    |        |            |         |

| 1             | 0            |            | Divide   | by 64    |        |            |         |

| 1             | 1            |            | Divide   | by 128   |        |            |         |

| Bits 1-0      | <u>)</u> Pre | scaler Mo  | ode (PM) | ) Select | 1      |            |         |

|               |              |            | Syste    | em Cloc  | k      | Timer (    | Clock   |

| M1            | MO           | Mode       | (Ø2      | 2) Rate  |        | (TCLK)     | Rate    |

| 0             | 0            | 0          | MCLK     | (        | _<br>M | CLK        |         |

| Ö             | 1            | 1          | MCLK     | (        | M      | CLK + I    | PV      |

| 1             | 0            | 2          | N/A      |          | N/     | 'A (Illega | l Mode) |

| 1             | 1            | 3          | MCL      | · PV     | М      | CLK ÷      | PV      |

| Note: 1       | i. All b     | its are re | set to 0 | by RES   |        |            |         |

Figure 3-6. Prescaler Control Register

The Counter is reset to the Interval Timer mode (Mode 0) by assertion of RES (which causes 0s to be loaded into all bits of the Control Register).

#### PA1 INTERRUPT ENABLE BIT (A1IE)

If the PA1 Interrupt Enable bit (bit 2) is set to a 1, IRQ will occur when the PA1 Negative Edge Detected bit (bit 5) is set to a 1.

#### PAO INTERRUPT ENABLE BIT (A0IE)

If the PA0 Interrupt Enable bit (bit 3) is set to a 1, IRQ will occur when the PA0 Positive Edge Detected bit (bit 6) is set to a 1.

#### **COUNTER INTERRUPT ENABLE BIT (CIE)**

If the Counter Interrupt Enable Bit (bit 4) is set to a 1, IRQ will occur when Counter Overflow (bit 7) is set to a 1.

#### PA1 NEGATIVE EDGE DETECTED BIT (A1ED)

The PA1 Negative Edge Detected bit (bit 5) is set to a 1 whenever a negative (falling) edge is detected on PA1. This bit is cleared to a 0 by writing to address \$08A or by assertion of RES.

The edge detecting circuitry is active regardless of whether PA1 is an input or is an output. When PA1 is used as an output, A1ED will be set when the negative edge is detected during a high-to-low transition. When PA1 is used as an input and the negative

Figure 3-7. Prescaler Waveform Examples

Figure 3-8. Control Register

edge detecting circuitry is used, A1ED should be cleared by the user program upon initialization and upon completion of the PA1 Negative Edge Detected IRQ processing.

#### PAO POSITIVE EDGE DETECTED BIT (A0ED)

The PA0 Positive Edge Detected bit (bit 6) is set to a 1 whenever a positive (rising) edge is detected on PA0. This bit is cleared to a 0 by writing to address \$089 or by assertion of RES.

The edge detecting circuitry is active regardless of whether PA0 is an input or is an output. When PA0 is used as an output, A0ED will be set when the positive edge is detected during a low-to-high transition. When PA0 is used as an input and the positive edge detecting circuitry is used, A0ED should be cleared by the user program upon initialization and upon completion of PA0 Positive Edge Detected IRQ processing.

#### **COUNTER OVERFLOW BIT (CTRO)**

The Counter Overflow bit (bit 7) is set to a 1 whenever the Counter overflow occurs in any of the four counter operating modes. Overflow occurs when the Counter is decremented one count from 0. This bit is cleared to a 0 by reading from address \$087, writing to address \$088, or by assertion of  $\overline{\text{RES}}$ .

The CTRO bit should be cleared by the user program upon initialization and upon completion of Counter Overflow IRQ interrupt processing.

When a Counter Overflow occurs, the Upper Count (UC) in address \$086, and the Lower Count (LC) in address \$087, are loaded with to the values contained in the Upper Latch (UL) in address \$084, and in the Lower Latch (LL) in address \$085, respectively.

#### 3.14 PARALLEL INPUT/OUTPUT PORTS

The R65C10 provides four memory-mapped 8-bit Input/Output (I/O) ports: PA, PB, PC and PD. All 32 I/O lines of the four ports are completely bidirectional. All lines may be used either for input or output in any combination, i.e., there are no line grouping or port association restrictions. A mask option is available to select I/O port operation with or without direction registers. Table 3-1 lists the I/O port and edge detected bit reset addresses.

Table 3-1. I/O Port Addresses

| Port/Function                                     | Address |

|---------------------------------------------------|---------|

| Port A Direction Register (Write Only)            | \$090   |

| Port B Direction Register (Write Only)            | \$091   |

| Port C Direction Register (Write Only)            | \$092   |

| Port D Direction Register (Write Only)            | \$093   |

| Port A Data Register (Read/Write)                 | \$080   |

| Port B Data Register (Read/Write)                 | \$081   |

| Port C Data Register (Read/Write)                 | \$082   |

| Port D Data Register (Read/Write)                 | \$083   |

| Clear PA0 Positive Edge Detected Bit (Write Only) | \$089   |

| Clear PA1 Negative Edge Detected Bit (Write Only) | \$08A   |

# I/O PORT OPERATION WITHOUT DIRECTION REGISTERS

If direction registers are *not* selected, the direction of the 32 I/O lines is controlled by writing to the four 8-bit port data registers located in page zero at addresses \$80–\$83 (see Figure 3-3). This arrangement provides quick programming access using simple 2-byte zero page address instructions. I/O handling is simplified since programming of direction registers is not required.

#### Inputs

Inputs are enabled by writing a 1 into all I/O port register bit positions that correspond to input lines. A low ( $\leq$ 0.8 Vdc) input level causes a 0 to be read when a read instruction is issued to the port register. A high ( $\geq$ 2.0 Vdc) input level causes a 1 to be read. Assertion of RES forces all bits in the I/O port registers to 1s, thus initially treating all I/O lines as inputs.

The status of the input lines can be interrogated at any time by reading the I/O port addresses. Note that this will return the actual status of the input lines, not the data written into the I/O port register.

#### **Outputs**

Outputs are controlled by writing the desired I/O line output states into the corresponding I/O port register bit positions.

A 1 will force a high ( $\geq$ 2.4 Vdc) output while a 0 will force a low ( $\leq$ 0.4 Vdc) output.

#### I/O PORT OPERATION WITH DIRECTION REGISTERS

If direction registers are selected, the direction of all 32 I/O lines is controlled by individual bits in four write-only I/O port direction registers. The direction registers for ports A, B, C and D are located at addresses \$90, \$91, \$92 and \$93, respectively. Setting a bit in a direction register to a 1 causes the corresponding I/O line to operate as an output; resetting the bit to a 0 causes the I/O line to be an input. Assertion of  $\overline{\rm RES}$  clears all direction register bits to 0s causing all I/O lines to initially be inputs.

#### Inputs

If an I/O line is an input, the state of the corresponding bit in the I/O port data register shows the input logic level: 1 = high; 0 = low.

#### **Outputs**

If an I/O line is an output, the state of the corresponding bit written to the port data register determines the output logic level: 1 = high; 0 = low.

#### **EDGE DETECTION CAPABILITY**

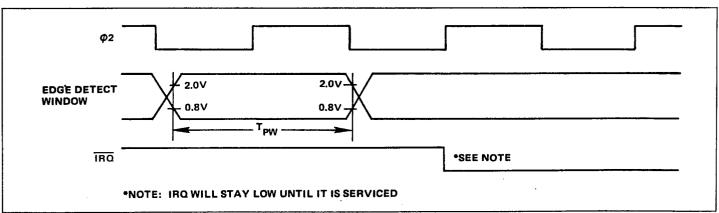

The Port A PA0 and PA1 circuitry has edge detection capability. Edges detected on these lines are reported in the Control Register and will cause an IRQ if enabled in the Control Register (see Section 3.14). The edge detect timing waveforms are illustrated in Figure 3-9.

#### PA0 Positive Edge Detection

In addition to its normal I/O function, an asynchronous positive (rising) edge signal can be detected on PA0. This occurrence will be reported in the PA0 Positive Edge Detected bit in the Control Register (CR6). CR6 is cleared by writing to address \$089 or by assertion of RES.

#### **PA1 Negative Edge Detection**

In addition to its normal I/O function, an asynchronous negative (falling) edge signal can be detected on PA1. This occurrence wil be reported in the PA1 Negative Edge Detected bit in the Control Register (CR5). CR5 is cleared by writing to address \$08A or by assertion of RES.

#### 3.15 COUNTER/LATCH

#### **GENERAL**

The Counter/Latch consists of a 16-bit Counter, and a 16-bit Latch. The Counter resides in two 8-bit registers: address \$086 contains the Upper Count value (bits 8-15 of the Counter) and address \$087 contains the Lower Count value (bits 0-7 of the Counter). The Counter contains the count of either unscaled or prescaled \$0.2 clock periods, or external events, depending on Counter mode selected in the Control Register and, for clock driven Counter modes, the Prescaler mode and value selected in the Prescaler Control Register. Table 3-2 lists the addresses associated with Counter/Latch operation.

Table 3-2. Counter/Latch Addresses

| Function                                           | Address |

|----------------------------------------------------|---------|

| Write Upper Latch (Write Only)                     | \$084   |

| Write Lower Latch (Write Only)                     | \$085   |

| Read Upper Count (Read Only)                       | \$086   |

| Read Lower Count, Clear Timer Overflow (Read Only) | \$087   |

| Write Upper Latch and Transfer Latch to Counter,   | \$088   |

| Clear Counter Overflow (Write Only)                |         |

The Latch contains the Counter initialization value. The Latch resides in two 8-bit registers: address \$084 contains the Upper Latch value (bits 8–15 of the Latch) and address \$085 contains the Lower Latch value (bits 0–7 of the Latch). The 16-bit Latch can hold values from 0 to 65,535.

The latch registers can be loaded at any time by writing to the Upper Latch address (\$084) and the Lower Latch address (\$085). In each case, the contents of the Accumulator are copied into the applicable Latch register. The Upper Latch and Lower Latch

Figure 3-9. PA0 and PA1 Edge Detection Timing Waveforms

can be loaded independently; it is not required to load both registers at the same time, or sequentially. The Upper Latch can also be loaded by writing to address \$088.

The Counter will also be initialized to the Latch value whenever the Counter overflows. When the Counter decrements from 0, the next Counter value will be the Latch value, not \$FFFF.

Whenever the Counter overflows, the Counter Overflow status bit in the Control Register (CR7) is set to a 1. This bit is cleared whenever the lower eight bits of the Counter are read from address \$087 or by writing to address \$088.

#### **COUNTER/TIMER MODES**

The Counter operates in any of four modes. These modes are selected by the Counter Mode Control bits in the Control Register (see Table 3-3).

The Interval Timer, Pulse Generator, and Pulse Width Measurement modes are internally clocked modes. The Event Counter Mode counts the occurrences of an external event on the CNTR line

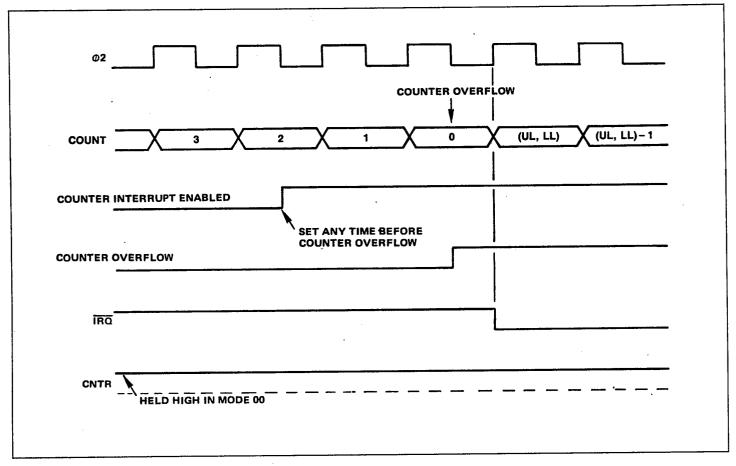

#### Interval Timer (Mode 0)

In the Interval Timer mode, the Counter is initialized to the Latch value by either of two conditions:

- 1. When the Counter is decremented from 0, the next Counter value is the Latch value, not \$FFFF.

- When a write operation is performed to the Upper Latch and the Transfer Latch to Counter address (\$088), the Counter is loaded with the Latch value. Note that the contents of the Accumulator are loaded into the Upper Latch before the Latch value is transferred to the Counter.

The Counter value is decremented at the timer clock (TCLK) rate. The 16-bit Counter can hold from 1 to 65,535 counts. For a 4 MHz internal  $\emptyset$ 2 clock and no prescaler selected, the timer range is 0.25  $\mu$ s to 16.384 ms. For a 4 MHz internal  $\emptyset$ 2 clock and divide-by-128 prescaler selected, the timer range is 32  $\mu$ s to 2.097 seconds.

When the Counter decrements from 0, the Counter Overflow bit in the Control Register (CR7) is set to a 1 at the next counter clock pulse. If the Counter Interrupt Enable bit (CR4) is also set, IRQ will occur. The Counter Overflow bit in the Control Register can be examined in the IRQ interrupt routine to determine that the IRQ was caused by the Counter overflow.

While the timer is operating in the Interval Timer mode, the Counter-Out/Event-In (CNTR) line is held in the high impedance state (output disabled).

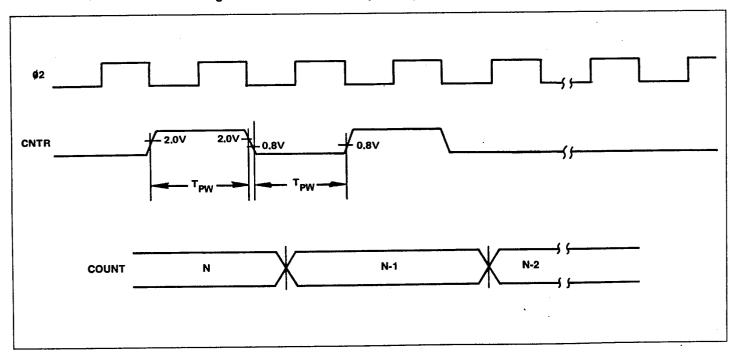

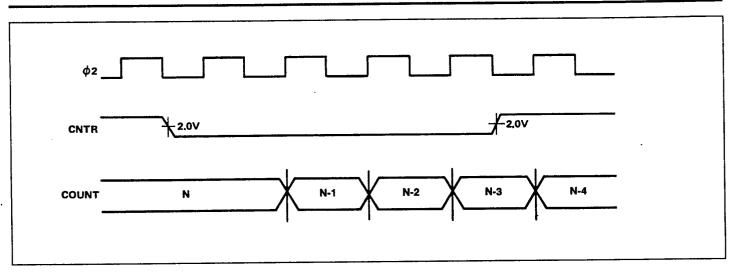

A timing diagram of the Interval Timer mode is shown in Figure 3-10.

#### Pulse Generator Mode (Mode 1)

In the Pulse Generator mode, the CNTR line operates as a Counter-Out. When a write is performed to address \$088 the CNTR output is initialized high. The Counter is decremented at the TCLK rate. The CNTR line toggles from low to high or from high to low whenever a Counter overflow occurs.

Either a symmetric or an asymmetric output waveform can be output on the CNTR line in this mode. The CNTR output is initialized to the high impedance state (output disabled) by assertion of  $\overline{\text{RES}}$  since the Interval Timer mode is established by  $\overline{\text{RES}}$ .

#### **Event Counter Mode (Mode 2)**

In this mode, the CNTR line is used as an Event-In input, and the Counter will decrement with each rising edge detected on this line. The maximum rate at which this edge can be detected is one-half the system (\$\psi 2\$) clock rate.

The Counter can count up to 65,535 occurrences before overflowing. As in the other modes, the Counter Overflow bit (CR7) is set to a 1 if the overflow occurs.

Figure 3-11 is a timing diagram of the Event Counter mode.

#### Pulse Width Measurement Mode (Mode 3)

This mode allows the accurate measurement of a low pulse duration on the CNTR line. In this mode, CNTR is used in the Event-In capacity. The Counter decrements at the TCLK rate as long as the CNTR line is held in the low state. The Counter is stopped when CNTR is in the high state.

If the CNTR pin is left disconnected, this mode may be selected to stop the Counter since the internal pull-up device (if present) will cause the CNTR input to be in the high (≥2.0 volt) state.

A timing diagram for the Pulse Width Measurement mode is shown in Figure 3-12.

#### 3.16 INTERRUPT LOGIC

Interrupt logic controls the sequencing of RES and the two interrupts: NMI, and IRQ.

#### **RES** Sequencing

RES going from low-to-high causes the R65C/1 to set the Interrupt Disable bit in the Processor Status Register (bit 2) and to initiate RES vector fetch at address \$FFC and \$FFD to begin user program execution. All of the I/O ports (PA, PB, PC, and PD) and CNTR are forced to the high (logic 1) state. All bits of the Control Register are cleared to logic 0, causing the Interval Timer Counter Mode (Mode 0) to be selected and causing all interrupt enable bits to be reset. All Prescaler Control Register bits are also reset to 0 causing Prescaler Mode 0 to be selected.

Figure 3-10. Interval Timer (Mode 0) Timing Waveforms

Figure 3-11. Event Counter (Mode 2) Timing Waveforms

Figure 3-12. Pulse Width Measurement (Mode 3) Timing Waveforms

#### NMI Sequencing

At the first operation code fetch following the high-to-low transition of the NMI input, the interrupt logic forces execution of the Break (BRK) instruction and subsequent execution from the address vector stored at \$FFA and \$FFB. Simultaneous with the execution of the BRK instruction, the Interrupt Disable bit in the Processor Status Register is set to disable an IRQ and bit 1 in the Prescaler Control Register is cleared to select unscaled system clock. Bit 0 of the Prescaler Control Register is unaffected.

#### **IRQ** Sequencing

The internal IRQ can be generated by any or all of three possible conditions: Counter Overflow, a positive edge detected on PA0, or a negative edge detected on PA1. The IRQ in response to these conditions can be enabled or disabled by setting or resetting the appropriate interrupt enable bits in the Control Register.

The first IRQ condition is Counter Overflow. IRQ will occur whenever both the Counter Interrupt Enable (CR4) and the Counter Overflow (CR7) are logic 1.

The second IRQ condition is detection of a positive edge on PA0. IRQ will occur whenever both the PA0 Interrupt Enable (CR3) and the PA0 Positive Edge Detected (CR6) are logic 1.

The third IRQ condition is detection of a negative edge on PA1. IRQ will occur whenever both the PA1 Interrupt Enable (CR2) and the PA1 Negative Edge Detected (CR5) are logic 1.

Multiple simultaneous interrupts will cause the IRQ to remain active until all interrupting conditions have been serviced and cleared.

The IRQ interrupt occurs when bit 2 of the Process Status Register is clear (enabling an IRQ), an IRQ enable bit (bit 2, 3 or 4) in the Control Register is set, and the corresponding interrupt bit (bit 5, 6 or 7) in the Control Register is set. Upon IRQ interruption, the BRK instruction is forced and subsequent program execution begins from the address vector stored at \$FFE and \$FFF. Bit 2 of the Processor Status Register is set. Bit 1 in the Prescaler Control Register is cleared to select unscaled system  $\emptyset 2$  clock. Bit 0 of the Prescaler Control Register is unaffected.

# SECTION 4 POWER ON/OFF INITIALIZATION AND OTHER CONSIDERATIONS

This section describes power turn-on, stop mode and mask option considerations for the R65C10.

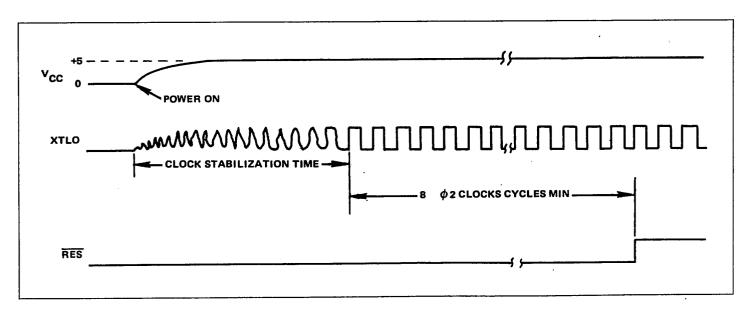

#### 4.1 POWER-ON TIMING

After application of  $V_{CC}$  power to the R65C10,  $\overline{RES}$  must be held low for at least eight  $\emptyset 2$  clock cycles after  $V_{CC}$  reaches operating range and the internal clock oscillator has stabilized. This stabilization time is dependent upon the input  $V_{CC}$  voltage and performance of the crystal or clock input circuit. The clock oscillator output can be monitored on XTLO (Pin 11).

The power turn-on waveforms are illustrated in Figure 4-1.

#### 4.2 STOP MODE

The Stop mode is an ultra-low-power mode in which the internal oscillator and clock is stopped. This mode is entered by writing to address \$08D and is exited only when  $\overline{RES}$  is asserted.

While in this mode, the R65C10 is dormant; however, the contents of RAM are preserved. Maximum power dissipation while in the Stop mode is under 4 mW. The oscillator stops with XTLO low.

A mask option is provided to inhibit Stop mode entry. This option is recommended if Stop mode is not used during operation.

#### 4.3 MASK OPTIONS

Mask options are user selectable options permanently implemented when the R65C10 device is manufactured in response

to a customer order. The options are to be specified on the R65C10 sheet in the R6500/\* ROM Code Order Forms (Literature Order No. 2134). The options deal with three basic circuits:

- Input crystal/clock frequency divisor

- I/O port direction registers and internal pull-up resistors

- Stop mode enable/disable

#### Input Crystal/Clock Frequency Divisor

The input clock/crystal frequency divisor can be selected to be either 1 or 2 (see Section 3.11).

#### **Direction Registers/Pull-up Resistors**

Direction registers can be selected for controlling port input/ output operation (see Section 3.14).

If direction registers are not used, then internal pull-up resistors can be optionally selected. In this case, pull-up resistors can be optionally included for 8-bit port groups only, i.e., not for individual I/O lines within an 8-bit port group. In addition, an internal pull-up for the CNTR line is selectable.

If direction registers are included, then internal pull-ups are not allowed.

#### **Stop Mode Entry Enable**

An option also exists to enable Stop mode use by writting to address 08D. (see Section 4.2).

Figure 4-1. Power Turn-On Timing Detail

# SECTION 5 SYSTEM SPECIFICATIONS

#### **ABSOLUTE MAXIMUM RATINGS\***

| Parameter           | Symbol           | Value        | Unit |

|---------------------|------------------|--------------|------|

| Supply Voltage      | V <sub>cc</sub>  | -0.3 to +7.0 | Vdc  |

| Input Voltage       | V <sub>IN</sub>  | -0.3 to +7.0 | Vdc  |

| Storage Temperature | T <sub>STG</sub> | -55 to +150  | °C   |

\*NOTE: Stresses exceeding those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or an ener conditions above those indicated in the other section. This document is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **OPERATING CONDITIONS**

| Parameter                                             | Symbol          | Value                                                              |

|-------------------------------------------------------|-----------------|--------------------------------------------------------------------|

| Supply Voltage                                        | V <sub>CC</sub> | 5.0 Vdc ±10%                                                       |

| Operating Temperature (Ambient) Commercial Industrial | T <sub>A</sub>  | T <sub>L</sub> to T <sub>H</sub><br>0°C to +70°C<br>-40°C to +85°C |

#### **ELECTRICAL CHARACTERISTICS**

(Over operating conditions unless otherwise noted)

| Parameter                                                                      | Symbol           | Min                 | Typ <sup>1</sup> | Max               | Units             | Test Conditions                                                                                    |

|--------------------------------------------------------------------------------|------------------|---------------------|------------------|-------------------|-------------------|----------------------------------------------------------------------------------------------------|

| Input High Voltage All except NMI and RES NMI, RES                             | V <sub>IH</sub>  | + 2.0<br>+ 2.4      | <u>-</u>         | V <sub>CC</sub>   | V                 | $V_{CC} = 5.5V$                                                                                    |

| Input Low Voltage                                                              | V <sub>iL</sub>  | _                   | _                | +0.8              | ٧                 | $V_{CC} = 4.5V$                                                                                    |

| Input Leakage Current<br>RES, NMI                                              | I <sub>IN</sub>  | _                   |                  | ± 2.5             | μΑ                | $V_{IN} = 0 \text{ to } 5.0V$                                                                      |

| Output High Voltage                                                            | V <sub>OH</sub>  | + 2.4               | _                | _                 | V                 | $V_{CC} = 4.5V$ $I_{LOAD} = -100 \mu\text{A}$                                                      |

| Output Low Voltage                                                             | V <sub>OL</sub>  | _                   | _                | +0.4              | ٧                 | V <sub>CC</sub> = 5.5V<br>I <sub>LOAD</sub> = 1.6 mA                                               |

| Output High Current (Sourcing)                                                 | I <sub>OH</sub>  | - 100               | _                |                   | μΑ                | V <sub>OUT</sub> = 2.4V                                                                            |

| Output Low Current (Sinking)                                                   | l <sub>OL</sub>  | 1.6                 | -                |                   | mA                | $V_{OUT} = 0.4V$                                                                                   |

| I/O Port Pull-Up Resistance PA0-PA7, PB0-PB7, PC0-PC7, PD0-PD7, CNTR           | R <sub>L</sub>   | 2.0                 | 3.2              | 6.0               | Kohm              |                                                                                                    |

| Input Capacitance<br>XTLI, XTLO<br>PA0-PA7, PB0-PB7, PC0-PC7,<br>PD0-PD7, CNTR | C <sub>IN</sub>  | <br>                | _                | 25<br>7           | pF                | $T_A = 25^{\circ}C$ $V_{IN} = 0V$ $f = 2 MHz-4 MHz$                                                |

| Output Capacitance                                                             | C <sub>OUT</sub> | _                   |                  | 50                | рF                | 1 TTL load                                                                                         |

| Input Frequency (f) Crystal Clock Clock                                        | f                | 2.0<br>0.04<br>0.02 | _                | 8.0<br>8.0<br>4.0 | MHz<br>MHz<br>MHz | ÷2 selected<br>÷2 selected<br>÷1 selected                                                          |

| Power Dissipation  Operating Stop Mode                                         | P <sub>D</sub>   | _                   | 20<br>4.0        | 40<br>8.0         | mW/MHz<br>mW      | V <sub>CC</sub> = 5.0V<br>Outputs High<br>Frequency = unscaled Ø2 clock<br>No external clock input |

#### Notes:

<sup>1.</sup>  $T_A = 25$ °C and  $V_{CC} = 5.0$ V.

<sup>2.</sup> Negative sign indicates outward current flow, positive indicates inward flow.

#### **SWITCHING CHARACTERISTICS**

(Over operating conditions unless otherwise noted)

| Parameter                                                                                     | Mode                  | Symbol                         | 1 M                 | Hz         | 2M                  | Hz         | Unit                 |

|-----------------------------------------------------------------------------------------------|-----------------------|--------------------------------|---------------------|------------|---------------------|------------|----------------------|

| -                                                                                             |                       |                                | Min                 | Max        | Min                 | Max        |                      |

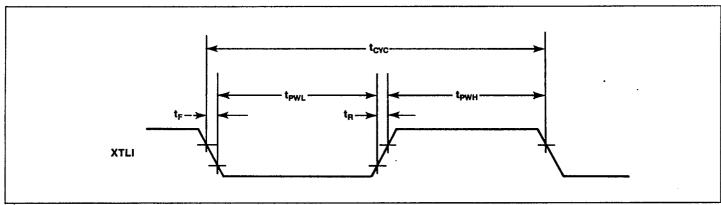

| XTLI Input Clock<br>Cycle Time<br>Pulse Width, Low<br>Pulse Width, High<br>Rise and Fall Time | + 2<br>+2<br>+2<br>+2 | tCYC<br>tpWL<br>tpWH<br>tR, tF | 0.500<br>100<br>100 | 25.0<br>60 | 0.250<br>55<br>55   | 25.0<br>25 | μs<br>ns<br>ns<br>ns |

| XTLI Input Clock<br>Cycle Time<br>Pulse Width, Low<br>Pulse Width, High<br>Rise and Fall Time | +1<br>+1<br>+1<br>+1  | tCYC<br>tpWL<br>tpWH<br>tB, tF | 1.000<br>450<br>450 | 50.0<br>20 | 0.500<br>225<br>225 | 50.0<br>15 | μs<br>ns<br>ns       |

| Count and Edge Detect<br>Pulse Width                                                          |                       |                                | 1                   |            | 1                   |            | £2<br>Period*        |

## **SWITCHING WAVEFORMS**

# APPENDIX A R65C10 INSTRUCTION SET

This appendix summarizes the R65C10 instruction set. The basic instructions are listed alphabetically by standard mnemonic in Table A-1. The instruction operation codes (OP Codes) for all valid addressing modes are listed in Table A-2. Also listed in Table A-2 are the number of bytes and number of CPU cycles required in each addressing mode. The effect of instruction execution on the Processor Status Register is also shown.

A matrix of instructions and addressing modes arranged by operation code is shown in Table A-3. For detailed information about CPU instruction execution, consult the R6500 Programming Manual (Order No. 202).

Table A-4 summarizes the differences in operation between the R65C10 CPU and the R6502 CPU.

Table A-1. R65C10 Instruction Set Alphabetic Sequence

| Mnemonic | Instruction                                | Mnemonic | Instruction                                  |

|----------|--------------------------------------------|----------|----------------------------------------------|

| ADC      | Add Memory to Accumulator with Carry       | JMP      | Jump to New Location                         |

| AND      | "AND" Memory with Accumulator              | JSR      | Jump to New Location Saving Return Address   |

| ASL      | Shift Left One Bit (Memory or Accumulator) | 1        |                                              |

|          | , , ,                                      | LDA      | Load Accumulator with Memory                 |

|          |                                            | LDX      | LOAD Index X with Memory                     |

| BCC      | Branch on Carry Clear                      | LDY      | Load Index Y with Memory                     |

| BCS      | Branch on Carry Set                        | LSR      | Shift One Bit Right (Memory or Accumulator)  |

| BEQ      | Branch on Result Zero                      |          |                                              |

| BIT      | Test Bits in Memory with Accumulator       | NOP      | No Operation                                 |

| BMI      | Branch on Result Minus                     | ORA      | "OR" Memory with Accumulator                 |

| BNE      | Branch on Result not Zero                  |          |                                              |

| BPL      | Branch on Result Plus                      | PHA      | Push Accumulator on Stack                    |

| BRK      | Force Break                                | PHP      | Push Processor Status on Stack               |

| BVC      | Branch on Overflow Clear                   | PLA      | Pull Accumulator from Stack                  |

| BVS      | Branch on Overflow Set                     | PLP      | Pull Processor Status from Stack             |

| CLC      | Clear Carry Flag                           | ROL      | Rotate One Bit Left (Memory or Accumulator)  |

| CLD      | Clear Decimal Mode                         | ROR      | Rotate One Bit Right (Memory or Accumulator) |

| CLI      | Clear Interrupt Disable Bit                | RTI      | Return from Interrupt                        |

| CLV      | Clear Overflow Flag                        | RTS      | Return from Subroutine                       |

| CMP      | Compare Memory and Accumulator             |          |                                              |

| CPX      | Compare Memory and Index X                 | SBC      | Subtract Memory from Accumulator with borrow |

| CPY      |                                            | SEC      | Set Carry Flag                               |

| CPY      | Compare Memory and Index Y                 | SED      | Set Decimal Mode                             |

|          |                                            | SEI      | Set Interrupt Disable Status                 |

| DEC      | Decrement Memory by One                    | STA      | Store Accumulator in Memory                  |

| DEX      | Decrement Index X by One                   | STX      | Store Index X in Memory                      |

| DEY      | Decrement Index Y by One                   | STY      | Store Index Y in Memory                      |

| 505      | ((Final value Coll) Mannage with Appendix  | TAX      | Transfer Accumulator to Index X              |

| EOR      | "Exclusive-Or" Memory with Accumulator     | TAY      | Transfer Accumulator to Index Y              |

|          |                                            | TSX      | Transfer Stack Pointer to Index X            |

| INC      | Increment Memory by One                    | TXA      | Transfer Index X to Accumulator              |

| INX      | Increment Index X by One                   | TXS      | Transfer Index X to Stack Register           |

| INY      | Increment Index Y by One                   | TYA      | Transfer Index Y to Accumulator              |

Table A.2. R65C10 Instruction Set by Address Modes

|          |                                            |     |       |       |       |          |     | _   |               | _   | ABORESSING MODES |      |       |         |             |      |     |      |          |     |          | <del></del> |         |           |              |                |      |            | Τ       | $\neg$   |     |     |          |                                        |          |          |                                                  |                                        |          |              |                    |          |               |          |

|----------|--------------------------------------------|-----|-------|-------|-------|----------|-----|-----|---------------|-----|------------------|------|-------|---------|-------------|------|-----|------|----------|-----|----------|-------------|---------|-----------|--------------|----------------|------|------------|---------|----------|-----|-----|----------|----------------------------------------|----------|----------|--------------------------------------------------|----------------------------------------|----------|--------------|--------------------|----------|---------------|----------|

|          |                                            | h   | MEC   | ) AT  | ī     | ABSC     | LUI |     | ZERC          | PAC | į.               | ACC  | UM    | Т       | IMP         | LIED | Т   | (194 | D. X     | , T | {EN      | D), Y       | Ţz      | PAG       | E. X         | Τ              | ABS  | X          | 1       | WS.      | ٧   | RE  | LATI     | VE                                     | HIS      | HREC     | ,                                                | 2 (                                    | AGE      | . 7          | PROCESSOR<br>CODES | STATUS   |               |          |

| MHEMONIC | OPERATION                                  | 6   | - ^   | Τ.    | 10    | P        | ٦   |     | P             | ~ [ |                  | OP 1 |       | .       | P           | T    |     | P    | _        |     | ъP       | n           | . 0     | P         | ٦.           | 01             | ,    | T,         | OF      | <b>1</b> |     | OP  | n        | •                                      | OР       | ^        | •                                                | OP                                     | ,        | •            | 7 6 5 4<br>N V • B | 3 2 1 (  |               | оніс     |

| ADC      | A + M + C - A (4) (1)                      | ┺   | +-    | +-    | +     | -        | _   | 3 6 | щ.            | 3   | -                | +    | +     | Ŧ       | +           | +    | _   | 51   | _        | _   | -        | -           | 2 7     | ┿┈        | -            | 4-             |      | 3          | _       | 4        | _   | Н   | $\dashv$ |                                        | H        | ᅥ        | ᅥ                                                | H                                      | ᅥ        | $\neg$       |                    | • • Z (  |               | 0        |

| AND      |                                            | •   | 2     |       |       | - 1      | - 1 |     |               | 3   | - 1              | 1    | 1     |         |             | ı    |     | •    |          |     | 31       | 5           | 2 3     | 5 4       | 2            | 30             | 4    | 3          | 39      | 4        | 3   |     |          |                                        |          |          |                                                  | П                                      |          |              | N                  | z        | . A N         | וסו      |

| ASL      | C0-0                                       | l   |       |       | 0     | Ε        | 6   | 3   | 26            | 5   | 2 0              | A    | 2   . | ,       | -           |      | -   | 1    | 1        | ١   |          |             | 1       | 6 6       | 3 2          | 16             | 7    | 3          | 1       |          |     |     |          |                                        |          |          |                                                  |                                        |          |              | N                  | • • Z    | C AS          |          |

| всс      | BRANCH ON C = 0 (2)                        | ١   |       |       |       | 1        |     | ١   |               | ļ   | 1                |      |       | 1       |             |      | -   | -    |          | -   | ı        |             |         |           |              |                |      |            |         |          |     | 90  | 2        |                                        |          |          |                                                  |                                        | .        |              |                    |          | L             | - 1      |

| BCS      | BRANCH ON C = 1 (2)                        | L   | L     | l     | 1     | ┵        |     | _   | 1             | _   | _                | _    | 1     | 1       | $\bot$      | 4    | 4   | 1    | 4        | ↲   | 4        | _           | 4       | 1         | $\downarrow$ | L              | ↓.   | 1          | ↓_      | L_       | ╙   | 80  | _        | _                                      | Щ        | Ц        | Ц                                                | Ц                                      | _        |              |                    | • • •    | o             |          |

| BEO      | BRANCH ON Z = 1 (2)                        | l   | 1     |       |       |          |     |     | 1             | ł   |                  | -    | -     | 1       |             |      | 1   | ı    | ļ        | ١   |          | -           | 1       |           |              |                |      |            |         |          |     | F0  | 2        | 2                                      |          |          |                                                  |                                        | 1        |              | ľ                  |          | BE            | - 1      |

| BIT      | AAM                                        | l   |       |       | 2     | c        | 4   | 3   | 24            | 3   | 2                |      | }     | ١       | -           |      | ı   | -    |          | 1   | -        |             | 1       |           | Ì            | 1              |      | 1          | 1       | 1        |     |     |          |                                        |          |          |                                                  |                                        |          |              | . •                | · · z    | . B 1         |          |

| BMI      | BRANCH ON N = 1 (2)                        | ı   |       | ł     |       | 1        | 1   | -   |               |     |                  | 1    |       | ı       | ı           | -    |     | -    | 1        |     |          | - 1         |         |           | 1            |                |      |            |         |          |     |     | 2        | 1                                      |          |          |                                                  |                                        |          |              |                    |          |               |          |

| BNE      | BRANCH ON Z = 0 (2)<br>BRANCH ON N = 0 (2) |     |       | İ     | 1     |          |     | -   |               | -   | ļ                | i    |       |         |             | 1    | -   | 1    |          | -   |          | - 1         |         |           |              | 1              |      |            |         | İ        | 1   | 10  | 2 2      |                                        |          | . 1      |                                                  |                                        |          |              |                    |          | . 8 6         | - 1      |

| BRK      | BREAK                                      | ╀   | ┿     | +     | +     | +        | +   | ╅   | +             | +   | +                | +    | ╁     | ۲,      | 00          | ,+   | 7   | ┿    | +        | ┪   | $\dashv$ | $\dashv$    | +       | ┿         | +            | ┿              | ┿    | +-         | ╁       | ╁        | H   | ۳   | ۲        | -                                      | H        | Н        | Η                                                | -                                      | _        | H            | 1                  | . 1 .    | BF            | _        |

| BVC      | BRANCHONV = 0 (2)                          | ı   | ļ     |       | 1     | ı        | - 1 | -   |               | - 1 | - 1              | ļ    |       | 1       |             |      | -   | ŀ    |          | 1   | - [      | ı           |         | 1         |              | 1              |      |            |         | l        |     | 50  | 2        | 2                                      |          |          |                                                  |                                        |          |              |                    |          | • B v         | / C      |

| BVS      | BRANCHONV = 1 (2)                          | ı   |       | ļ     |       | ١        |     | -   | -             | - 1 | ١                | 1    | ł     | ŀ       | ĺ           |      | ŀ   |      | ł        |     |          | ļ           | ı       |           |              |                |      | 1          | 1       | 1        | 1   | 70  | 2        | 2                                      |          |          |                                                  |                                        |          |              |                    |          | • B v         | / S      |

| Crc      | 0 - C                                      |     | ŀ     | ĺ     |       | ı        | -   | - [ | 1             | 1   | 1                |      | ŀ     | - 1     | 18          | 2    | 1   |      | - [      |     |          | - 1         |         |           |              | 1              |      |            |         |          |     |     |          |                                        |          |          |                                                  |                                        |          |              |                    | • • •    | 0 C L         | . c      |

| CLD      | 0 <b>-</b> D                               |     |       |       | 1.    |          |     |     |               |     |                  | _ _  |       | ŀ       | >8 <u>į</u> | 2    | 1   |      |          |     |          | $\perp$     | $\perp$ |           |              | $\perp$        |      | 1.         |         |          |     |     |          |                                        |          |          |                                                  |                                        |          |              |                    | 0        | · CL          | _        |

| CLI      | 0 +1                                       | Γ   | Ī     | Τ     | T     | 1        | T   | T   | ٦.            | T   | T                | Ţ    | T     | Ţ       | 58          | 2    | 1   | Т    | Т        | T   | T        | Т           | Т       | Τ         | Τ            | Τ              | T    | Τ          | Γ       | Γ        | Г   |     | П        |                                        |          |          |                                                  | 1                                      |          | _            | i                  | . 0 .    | - 1           | •        |

| CLV      | 0 - V                                      | 1   | ļ     |       | ļ     |          |     | ļ   |               |     | - 1              |      |       | ŀ       | B8          | 2    | - 1 |      | - 1      | ļ   | -        |             |         |           |              | 1              | 1    | 1          |         |          |     |     |          |                                        |          |          |                                                  |                                        |          |              | 1                  |          | .   01        |          |

| CMP      |                                            |     |       |       |       |          | 4   | - 1 |               | - 1 |                  |      | -     | 1       |             |      | ŀ   | C1   | 6        | 2   | D1       | 5           | 5 0     | 5 4       | ۱ :          | 2 0            | P 4  | 3          | 109     | 4        | 3   |     |          |                                        |          |          |                                                  |                                        |          |              |                    | z        | - 1           |          |

| CPX      | X - M                                      |     |       |       | - 1   |          | 4   |     | - 1           | - 1 | - 1              |      |       |         |             | Ì    | I   |      | - 1      | 1   | -        |             | 1       | 1         |              |                |      |            |         |          |     | 1   |          | 1                                      |          |          |                                                  | 1                                      |          |              |                    | z        |               | 1        |

| CPY      | Y - M                                      | 10  | 0 2   | 4     | _     |          | 4   |     |               |     | 2                | +    | +     | +       | ÷           | +    | 4   | +    | $\dashv$ | -   | -        | $\dashv$    | +       | +         | +            | +              | +-   | +-         | +       | ╀        | ╀   | ⊢   |          | $\vdash$                               | $\vdash$ | H        | -                                                | ╀                                      | Ь        | $\vdash$     |                    | Z        |               |          |

| DEC      | M - 1 → M<br>X - 1 → X                     |     |       |       | lc    | 3        | 6   | 3   | J6            | 2   | 2                | ļ    | Ì     |         |             | ١,   |     | 1    | -        | - [ |          |             | ۱       | ^  '      | ۱ ا          | الا            | ۱'   | '   3      | 1       |          | 1   | l   | 1        |                                        |          |          |                                                  | 1                                      |          |              | 1                  | z        | - 1           | - 1      |

| DEX      | X - 1 → X<br>Y - 1 → Y                     | 1   |       |       |       |          |     | -   |               |     | I                |      |       |         | B8          |      | ;   |      | - 1      | 1   | i        |             |         |           |              |                |      |            | 1       |          | 1   |     |          |                                        |          |          |                                                  |                                        | ŀ        | l            | i                  | z        |               | ı        |

| EOR      |                                            | 1,  | , أو  | ۱,    | ړ ا ړ | إوا      | 4   | 3   | 45            | 3   | ,                | !    | j     | ľ       | 00          | ۱ ٔ  |     | ا,,  | 6        | ۱,  | 51       | 5           | 2       | 5         | . ل          | 2 5            | ء اه | ١,         | 5 59    | 4        | 3   |     |          |                                        |          |          | }                                                | 1                                      |          |              | 1                  | z        |               |          |

| INC      | M + 1 → M                                  | 1   | ۱,    | 1     |       |          | 6   |     |               |     |                  | İ    | 1     |         | }           |      | -   |      | -        | 1   |          |             |         |           |              | 2 F            | - 1  |            |         |          |     |     | 1        |                                        |          |          |                                                  |                                        | 1        |              | •                  | z        |               |          |

| INX      | X + 1 → X                                  | T   | +     | 1     | Ť     | $\dashv$ | 7   | +   | +             | 7   | 7                | +    | +     | 7       | E8          | 2    | ,   | 7    | 7        | 7   | ┪        | $\dashv$    | ᆌ:      | $\dagger$ | +            | 十              | T    | T          | 1       | T        | T   | T   |          | Г                                      | Π        | Г        | Г                                                | Т                                      | Г        | Π            | N · ·              | · · · z  |               | ı x      |