NEC

**Application Note**

# $\mu$ PD784915, 784928, 784928Y Subseries

**16-bit Single-chip Microcontrollers**

**VCR Servo Basics**

| μ <b>PD784915</b>  | μ <b>ΡD784927</b>  | $\mu$ PD784927Y     |

|--------------------|--------------------|---------------------|

| μ <b>ΡD784915A</b> | μ <b>PD78F4928</b> | μ <b>PD78F4928Y</b> |

| μ <b>ΡD784916A</b> |                    |                     |

| μ <b>PD784915B</b> |                    |                     |

| μ <b>PD784916B</b> |                    |                     |

| μ <b>PD78P4916</b> |                    |                     |

Document No. U11361EJ3V0AN00 (3rd edition) Date Published March 1998 N CP(K)

© NEC Corporation 1996 Printed in Japan [MEMO]

# **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

# 2 HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# **③ STATUS BEFORE INITIALIZATION OF MOS DEVICES**

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

# The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

| NEC Electronics Inc. (U.S.)<br>Santa Clara, California<br>Tel: 408-588-6000<br>800-366-9782<br>Fax: 408-588-6130<br>800-729-9288 | <b>NEC Electronics (Germany) GmbH</b><br>Benelux Office<br>Eindhoven, The Netherlands<br>Tel: 040-2445845<br>Fax: 040-2444580 | NEC Electronics<br>Hong Kong<br>Tel: 2886-9318<br>Fax: 2886-9022/9<br>NEC Electronics |

|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|                                                                                                                                  | NEC Electronics (France) S.A.                                                                                                 | Seoul Branch                                                                          |

| NEC Electronics (Germany) GmbH<br>Duesseldorf, Germany<br>Tel: 0211-65 03 02<br>Fax: 0211-65 03 490                              | Velizy-Villacoublay, France<br>Tel: 01-30-67 58 00<br>Fax: 01-30-67 58 99                                                     | Seoul, Korea<br>Tel: 02-528-0303<br>Fax: 02-528-4411                                  |

|                                                                                                                                  | NEC Electronics (France) S.A.                                                                                                 | NEC Electronics S                                                                     |

| NEC Electronics (UK) Ltd.                                                                                                        | Spain Office                                                                                                                  | United Square, Si                                                                     |

| Milton Keynes, UK                                                                                                                | Madrid, Spain                                                                                                                 | Tel: 65-253-8311                                                                      |

| Tel: 01908-691-133                                                                                                               | Tel: 01-504-2787                                                                                                              | Fax: 65-250-3583                                                                      |

| Fax: 01908-670-290                                                                                                               | Fax: 01-504-2860                                                                                                              |                                                                                       |

| NEO Electronico Italiano e n.4                                                                                                   |                                                                                                                               | NEC Electronic                                                                        |

| NEC Electronics Italiana s.r.1.                                                                                                  | NEC Electronics (Germany) GmbH                                                                                                | Taipei, Taiwan                                                                        |

| Milano, Italy                                                                                                                    | Scandinavia Office                                                                                                            | Tel: 02-719-2377                                                                      |

| Tel: 02-66 75 41                                                                                                                 | Taeby, Sweden                                                                                                                 | Fax: 02-719-5951                                                                      |

| Fax: 02-66 75 42 99                                                                                                              | Tel: 08-63 80 820                                                                                                             |                                                                                       |

|                                                                                                                                  | Fax: 08-63 80 388                                                                                                             | NEC do Brasil                                                                         |

s Hong Kong Ltd. 9044

s Hong Kong Ltd. 3 1 Singapore Pte. Ltd.

Singapore 1130 3

cs Taiwan Ltd. -1

S.A. Cumbica-Guarulhos-SP, Brasil Tel: 011-6465-6810 Fax: 011-6465-6829

# Major Revisions in This Edition

| Page         | Description                                                                       |  |

|--------------|-----------------------------------------------------------------------------------|--|

| Throughout   | The $\mu$ PD784928, 784928Y Subseries and the $\mu$ PD784915B, 784916B are added. |  |

| Introduction | Document numbers of related documents are added or corrected.                     |  |

| p. 15        | CHAPTER 1 OUTLINE OF NEC VCR SERVO MICROCONTROLLER PRODUCTS is added.             |  |

| p. 19        | Table 2-1 Differences among $\mu$ PD784915 Subseries Products is added.           |  |

| p. 25        | CHAPTER 3 OUTLINE OF µPD784928, 784928Y SUBSERIES is added.                       |  |

The mark  $\star$  shows major revised points.

# INTRODUCTION

| Readers                 | This application note is intended for user engineers who understand the functions of the $\mu$ PD784915, 784928, 784928Y Subseries and wish to design and develop its application systems and programs.                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Purpose                 | The purpose of this applicati<br>bilities of the target device u                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ion note is to help users understand the hardware capa-<br>using application examples.                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Organization            | <ul> <li>The main topics of this application note are listed below.</li> <li>Outline of μPD784915 Subseries</li> <li>Outline of μPD784928, 784928Y Subseries</li> <li>Outline of VCR servo</li> <li>Servo control examples of stationary VCR</li> <li>Analog circuit</li> <li>VISS</li> </ul>                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| How to Read This Manual | It is assumed that the readers of this manual have a general knowledge of electronics, logical circuits, and microcontrollers. Moreover, readers should also have a general knowledge of VCRs and servo control.<br>When there are no functional differences in the products, the application note mentions the $\mu$ PD784915 Subseries as the representative subseries and the $\mu$ PD784915 as the representative version, although its descriptions also apply to the versions other than the $\mu$ PD784915. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Quality Grade           | Standard (for general electro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | onic appliances)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Legends                 | Data significance<br>Active low<br>Note<br>Caution<br>Remark<br>Numerical representation<br>Easily confused characters                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>Left: higher digit, right: lower digit</li> <li>xxx (top bar over pin or signal name)</li> <li>Footnote explaining items marked with "Note"<br/>in the text</li> <li>Description of point that requires particular<br/>attention</li> <li>Supplementary information</li> <li>Binary xxxx B or xxxx<br/>Decimal xxxx<br/>Hexadecimal xxxxH</li> <li>0 (zero), O (uppercase letter "o")<br/>1 (one), I (lowercase of letter "L"),<br/>I (uppercase of letter "i")</li> </ul> |  |

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

# ★ Device related documents

| Document Name                                                                 | Document Number |                |

|-------------------------------------------------------------------------------|-----------------|----------------|

|                                                                               | Japanese        | English        |

| μPD784915 Data Sheet                                                          | U11044J         | U11044E        |

| μPD784915A, 784916A Data Sheet                                                | U11022J         | U11022E        |

| μPD784915B, 784916B Data Sheet                                                | U11930J         | To be prepared |

| μPD78P4916 Data Sheet                                                         | U11045J         | U11045E        |

| $\mu$ PD784915 Subseries Special Function Register Table                      | U10976J         | _              |

| μPD784915 Subseries User's Manual                                             | U10444J         | U10444E        |

| μPD784927 Data Sheet                                                          | U12255J         | To be prepared |

| µPD78F4928 Preliminary Product Information                                    | U12188J         | U12188E        |

| $\mu$ PD784928 Subseries Special Function Register Table                      | U12798J         | _              |

| μPD784927Y Data Sheet                                                         | U12373J         | U12373E        |

| µPD78F4928Y Preliminary Product Information                                   | U12271J         | U12271E        |

| $\mu$ PD784928Y Subseries Special Function Register Table                     | U12719J         | _              |

| $\mu$ PD784928, 784928Y Subseries User's Manual                               | U12648J         | U12648E        |

| $\mu$ PD784915, 784928, 784928Y Subseries Application Note — VCR Servo Basics | U11361J         | This manual    |

| 78K/IV Series User's Manual — Instruction                                     | U10905J         | U10905E        |

| 78K/IV Series Instruction Table                                               | U10594J         |                |

| 78K/IV Series Instruction Set                                                 | U10595J         |                |

| 78K/IV Series Application Note — Software Basics                              | U10095J         | U10095E        |

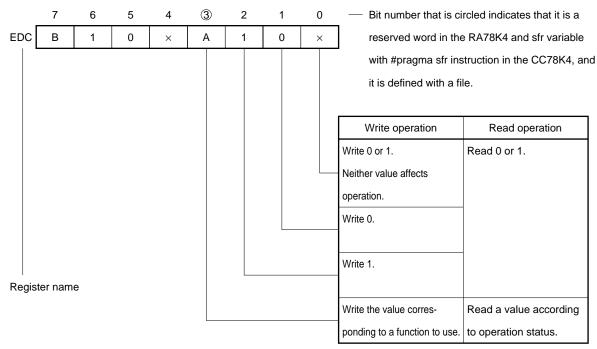

# **Register Format**

Never write a combination of codes marked "setting prohibited" in the register formats in the text.

# CONTENTS

| * | CHAPTER | 1 OUTLINE OF NEC VCR SERVO MICROCONTROLLER PRODUCTS                              | 15  |

|---|---------|----------------------------------------------------------------------------------|-----|

|   | 1.1     | Outline                                                                          | 15  |

|   | 1.2     | Features                                                                         | 17  |

|   | CHAPTER | 2 OUTLINE OF $\mu$ PD784915 SUBSERIES                                            | 19  |

|   | 2.1     | Features and Application Fields                                                  | 20  |

|   | 2.2     | Pin Configuration (Top View)                                                     |     |

|   | 2.3     | Block Diagram                                                                    | 23  |

|   | 2.4     | Outline of Functions                                                             | 24  |

| * | CHAPTER | 3 OUTLINE OF $\mu$ PD784928, 784928Y SUBSERIES                                   | 25  |

|   | 3.1     | Features and Application Fields                                                  | 26  |

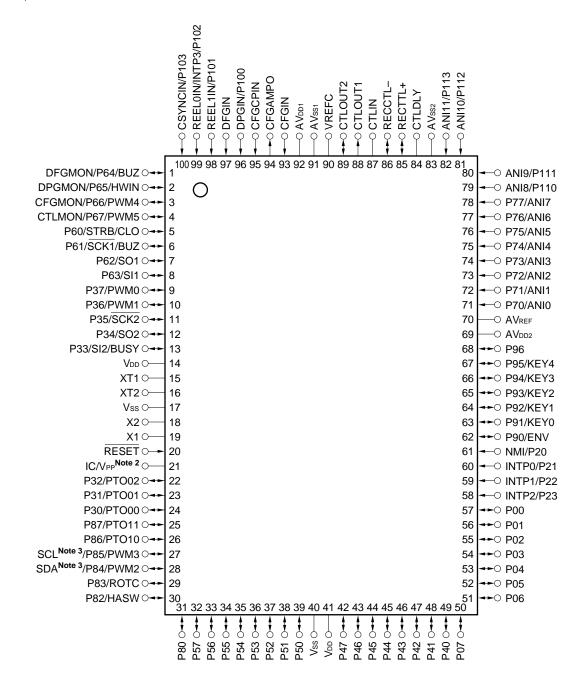

|   | 3.2     | Pin Configuration (Top View)                                                     | 27  |

|   | 3.3     | Internal Block Diagram                                                           | 29  |

|   | 3.4     | Outline of Functions                                                             | 30  |

|   | 3.5     | Differences among $\mu$ PD784928, 784928Y Subseries and $\mu$ PD784915 Subseries | 32  |

|   | CHAPTER | 4 OUTLINE OF VCR SERVO SYSTEM                                                    | 33  |

|   | 4.1     | Outline of Software Servo                                                        | 33  |

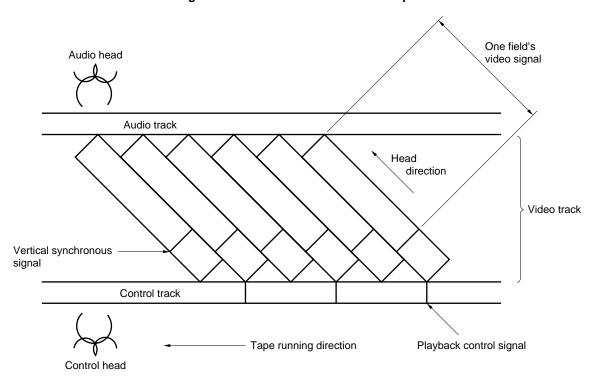

|   | 4.2     | Servo Control of VCR                                                             | 34  |

|   | 4.3     | Servo for Recording                                                              | 36  |

|   | 4.4     | Servo for Playback                                                               | 36  |

|   | 4.5     | Motor to be Used                                                                 | 37  |

|   | 4.6     | VCR Control Systems                                                              |     |

|   | 4.7     | VCR Servo System Control                                                         | 38  |

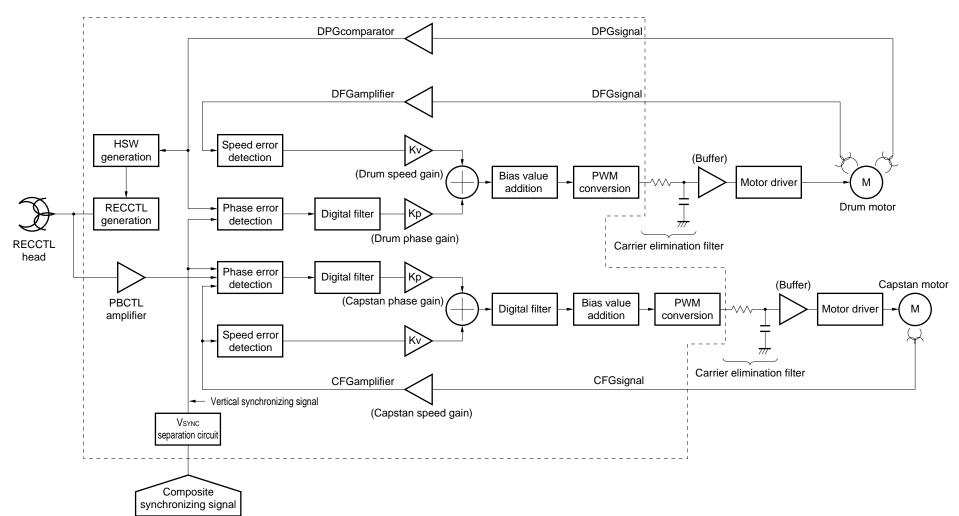

|   | CHAPTER | 5 EXAMPLES OF STATIONARY TYPE VCR SERVO CONTROL                                  |     |

|   | 5.1     | Examples of System Configuration                                                 |     |

|   | 5.2     | Outline of System                                                                |     |

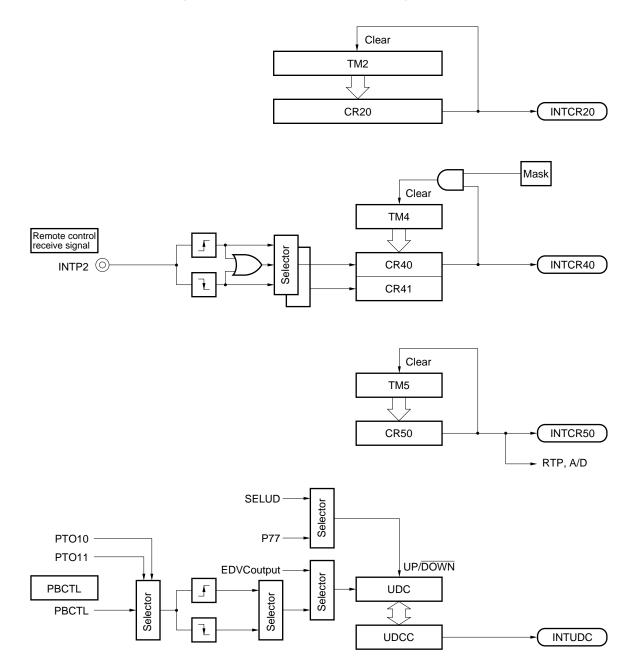

|   | 5.3     | Using Example of Super Timer Unit                                                |     |

|   | 5.4     | Head Switching Signal Generation                                                 |     |

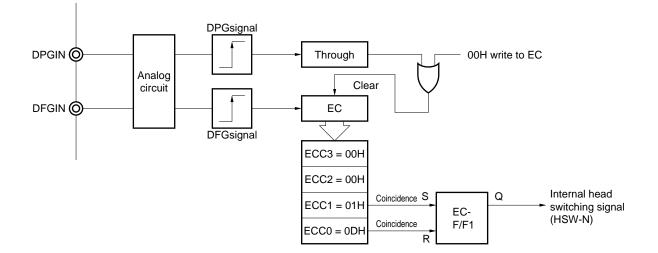

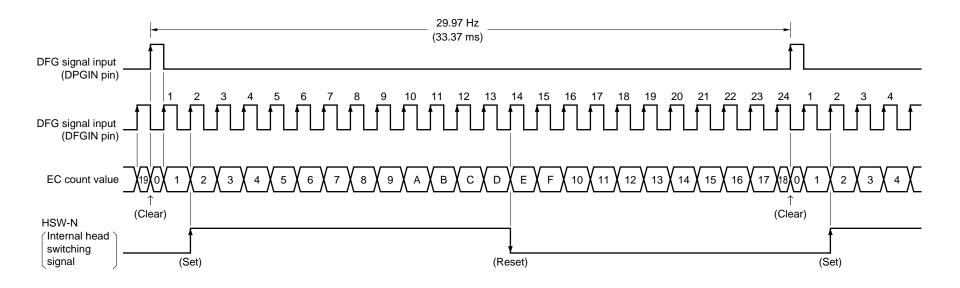

|   |         | 5.4.1 Internal head switching signal (HSW-N) generation                          | 46  |

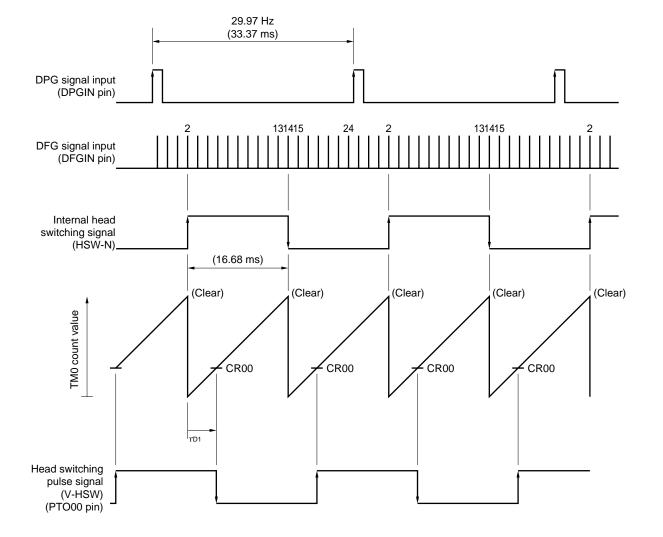

|   |         | 5.4.2 Head switching signal (V-HSW) generation                                   | 48  |

|   |         | 5.4.3 Audio head switching signal (A-HSW) generation                             |     |

|   | 5.5     | Drum Speed Control                                                               | 58  |

|   | 5.6     | Drum Phase Control                                                               | 60  |

|   |         | 5.6.1 Phase reference                                                            | 60  |

|   |         | 5.6.2 Drum phase control for playback                                            | 69  |

|   |         | 5.6.3 Drum phase control for recording                                           | 74  |

|   | 5.7     | Capstan Speed Control                                                            | 79  |

|   | 5.8     | Capstan Phase Control                                                            | 83  |

|   |         | 5.8.1 Capstan phase control for playback                                         | 83  |

|   |         | 5.8.2 Capstan phase control for recording                                        |     |

|   | 5.9     | Recording Control Signal Generation                                              |     |

|   | 5.10    | ) Quasi Vertical Synchronizing Signal (Quasi-Vsync) Generation                   | 100 |

| 5.11      | Treat  | ment of Servo Error Amount                        | 103 |

|-----------|--------|---------------------------------------------------|-----|

|           | 5.11.1 | Drum control system processing                    | 103 |

|           | 5.11.2 | Capstan control system processing                 | 107 |

| 5.12      | Comp   | ensation Filter                                   | 112 |

|           | 5.12.1 | Filter types                                      | 112 |

|           | 5.12.2 | Biprimary conversion method                       | 113 |

|           | 5.12.3 | Digital filter designing method                   | 119 |

|           | 5.12.4 | Primary IIR type digital filter transfer function | 120 |

|           | 5.12.5 | Lag-lead filter configuration method              | 121 |

|           | 5.12.6 | Filter processing method                          | 124 |

| CHAPTER 6 | CTL    | AMPLIFIER                                         | 127 |

| 6.1       | CTL A  | Amplifier Auto Gain Control Processing            | 127 |

|           | 6.1.1  | CTL amplifier auto gain control method            |     |

|           | 6.1.2  | CTL amplifier auto gain control processing        | 134 |

|           |        |                                                   | 407 |

|           |        |                                                   |     |

| 7.1       |        | is VISS                                           |     |

| 7.2       |        | Detection                                         |     |

|           | 7.2.1  | VISS detection method                             |     |

|           |        | VISS detection processing                         |     |

| 7.3       | VISS   | Rewrite                                           | 147 |

|           | 7.3.1  | VISS rewrite method                               | 147 |

|           | 7.3.2  | VISS rewrite processing                           | 149 |

| CHAPTER 8 | PRO    | GRAM LIST                                         | 151 |

| APPENDIX  | REVIS  | ION HISTORY                                       | 221 |

# LIST OF FIGURES (1/2)

| Figure No. | Title                                                                     | Page |

|------------|---------------------------------------------------------------------------|------|

| 4-1        | Track Pattern on Video Tape                                               | 35   |

| 5-1        | Application to Stationary Type VCR                                        | 40   |

| 5-2        | Software Digital Servo System Block Diagram                               |      |

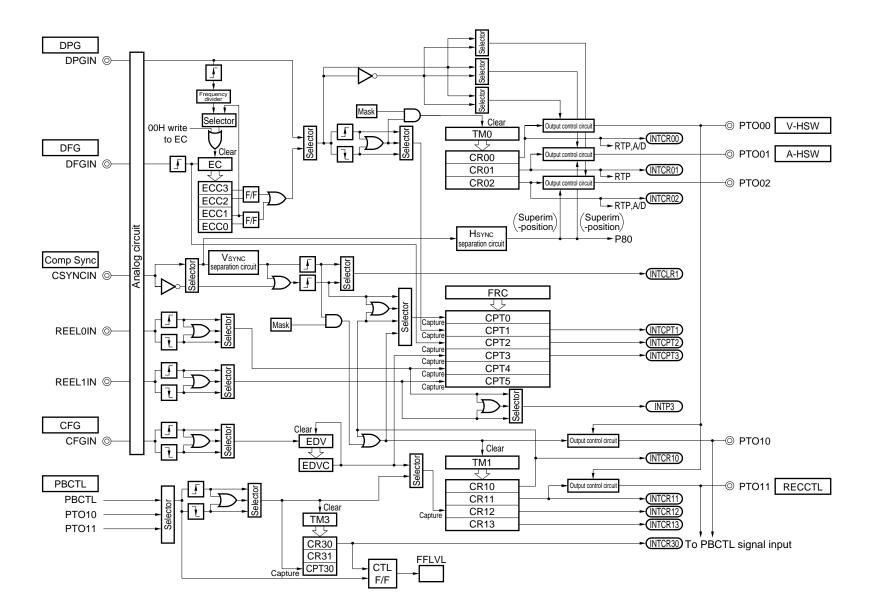

| 5-3        | Super Timer Unit Block Diagram                                            |      |

| 5-4        | Use of Event Counter (EC)                                                 |      |

| 5-5        | Event Counter (EC) Operation Timing                                       | 47   |

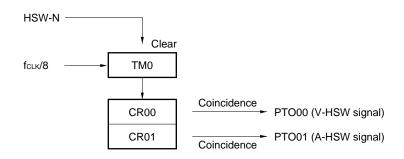

| 5-6        | Use of Timer 0                                                            | 49   |

| 5-7        | Head Switching Signal (V-HSW) Timing (PTO00)                              | 50   |

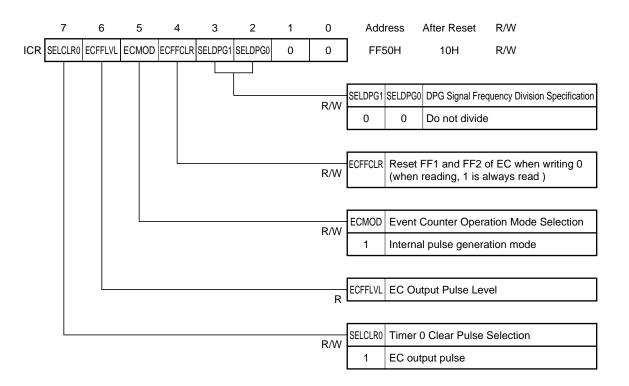

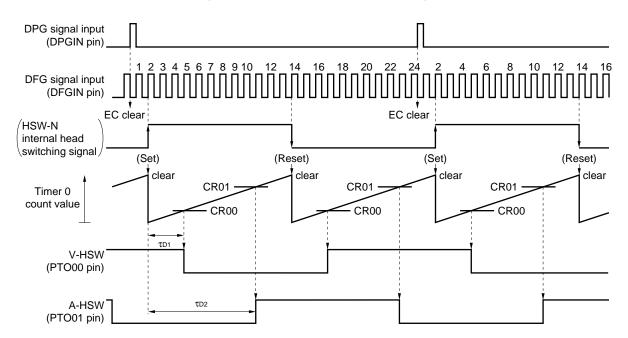

| 5-8        | Input Control Register (ICR) Format (when generating V-HSW)               | 51   |

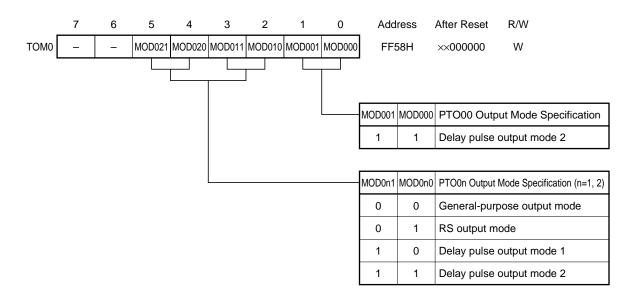

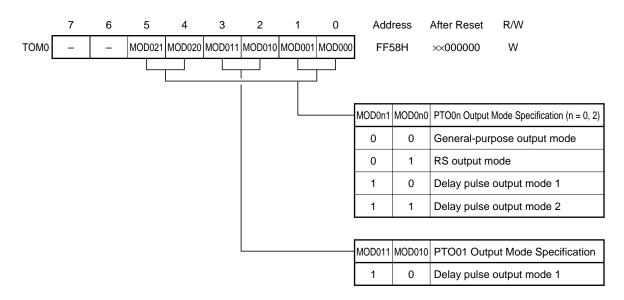

| 5-9        | Timer 0 Output Mode Register (TOM0) Format (when generating V-HSW)        | 52   |

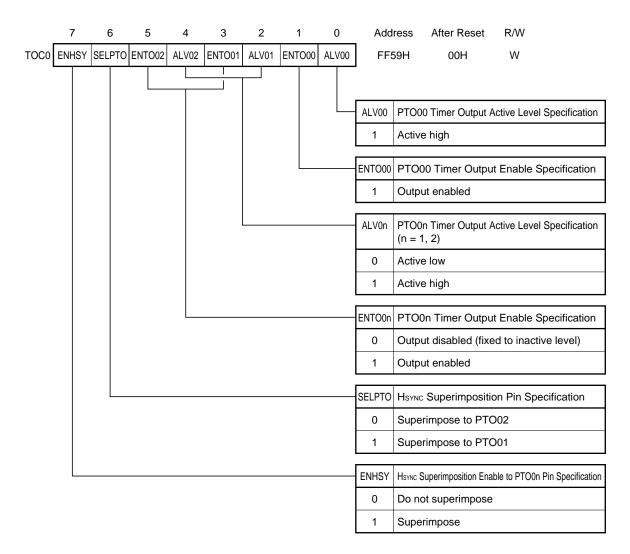

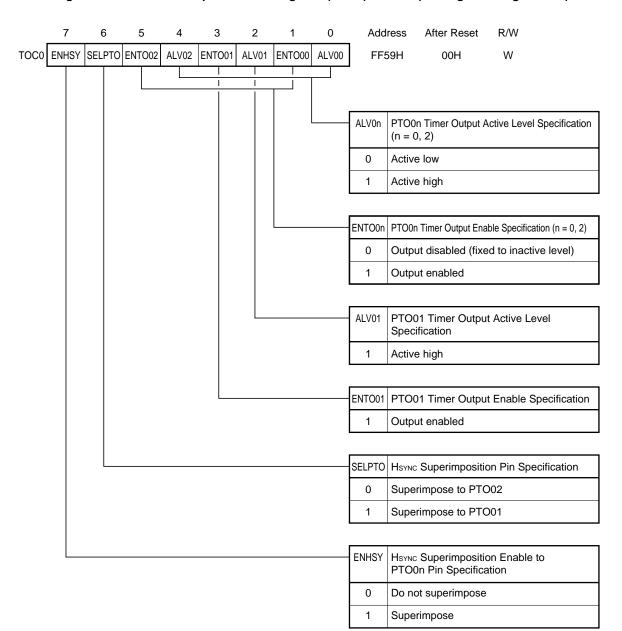

| 5-10       | Timer 0 Output Control Register (TOC0) Format (when generating V-HSW)     | 52   |

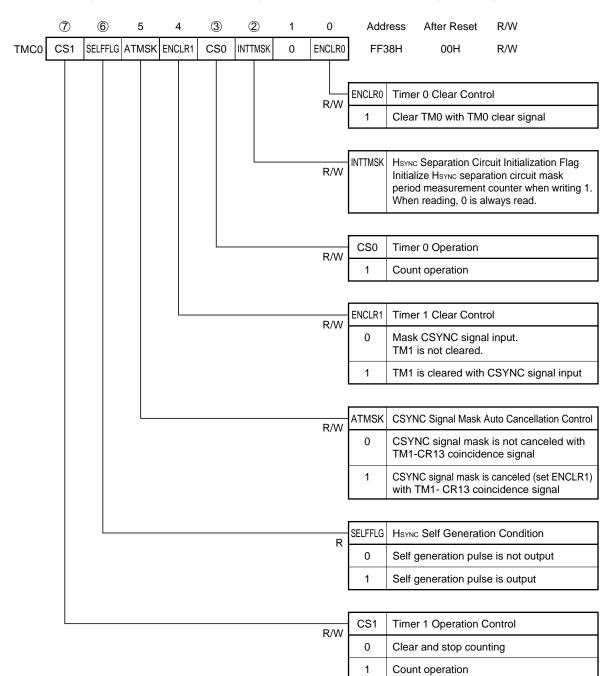

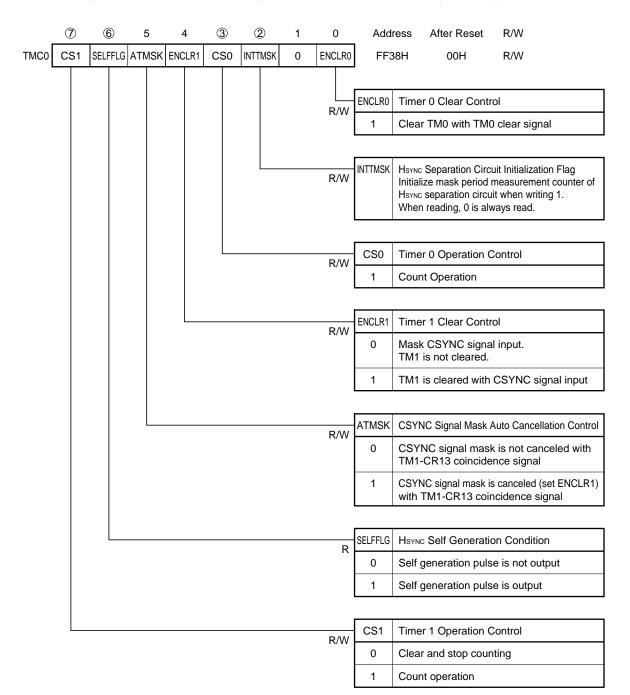

| 5-11       | Timer Control Register 0 (TMC0) Format (when generating V-HSW)            | 53   |

| 5-12       | Assigning A-HSW to Timer 0                                                | 54   |

| 5-13       | V-HSW and A-HSW Timings                                                   | 55   |

| 5-14       | Timer 0 Output Mode Register (TOM0) Format (when generating A-HSW)        | 55   |

| 5-15       | Timer 0 Output Control Register (TOC0) Format (when generating A-HSW)     | 56   |

| 5-16       | Timer Control Register 0 (TMC0) Format (when generating A-HSW)            | 57   |

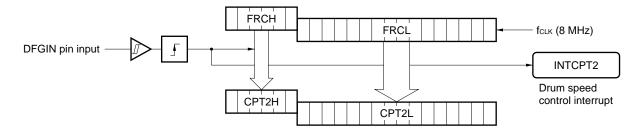

| 5-17       | Drum Speed Error Amount Detection Method                                  | 58   |

| 5-18       | Drum Speed Control Timings                                                | 59   |

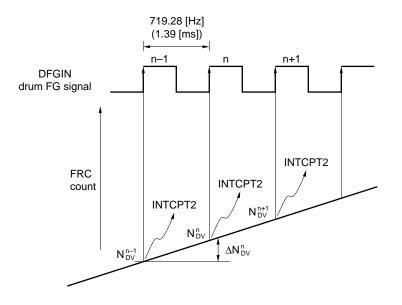

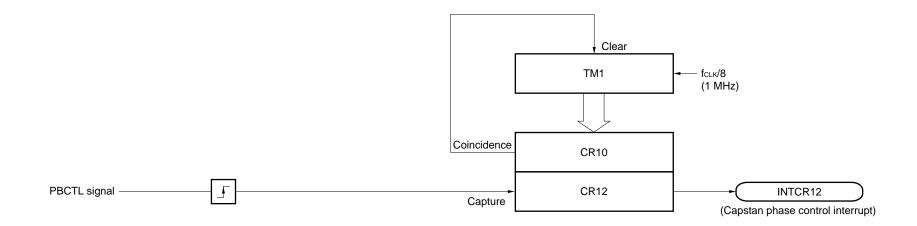

| 5-19       | Timer 1 Peripheral Circuit                                                | 61   |

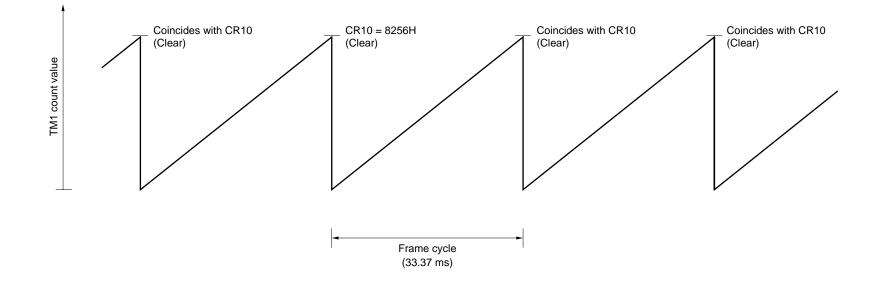

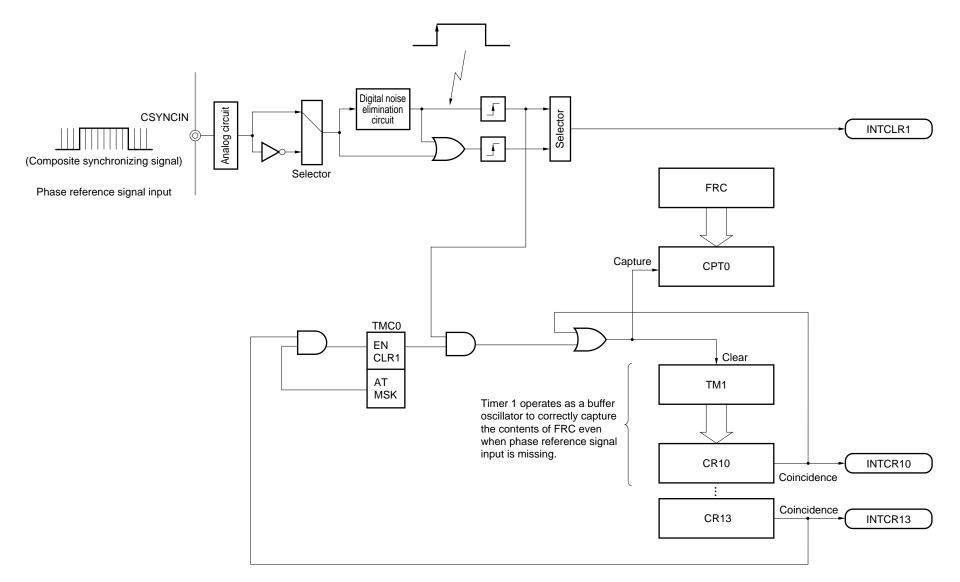

| 5-20       | Example of Timer 1 Operation Timings (for playback)                       | 63   |

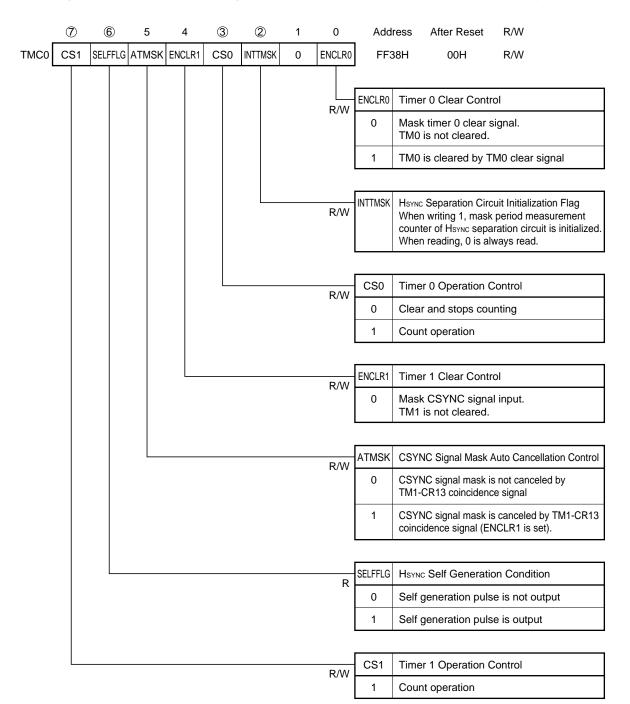

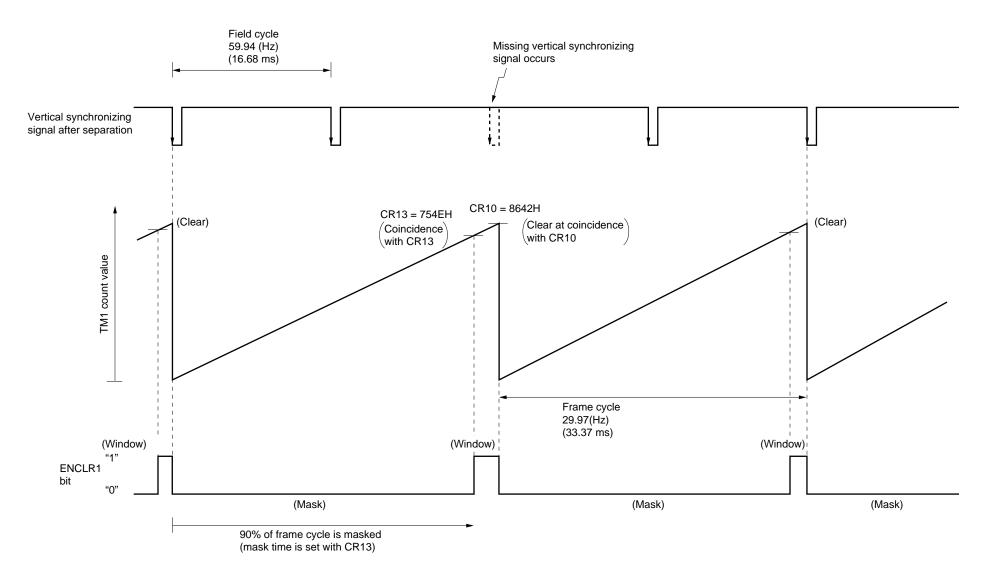

| 5-21       | Timer Control Register 0 (TMC0) Format (drum phase control for playback)  | 64   |

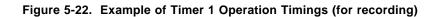

| 5-22       | Example of Timer 1 Operation Timings (for recording)                      | 67   |

| 5-23       | Timer Control Register 0 (TMC0) Format (drum phase control for recording) | 68   |

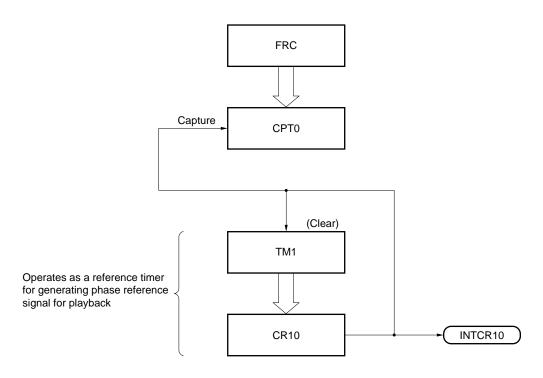

| 5-24       | Use of Timer for Drum Phase Control (for playback)                        | 69   |

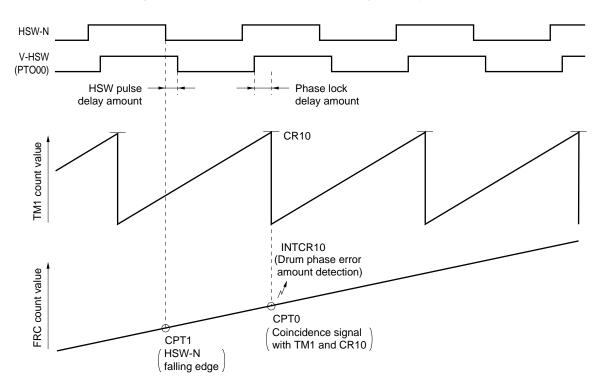

| 5-25       | Drum Phase Control Timing (for playback)                                  | 70   |

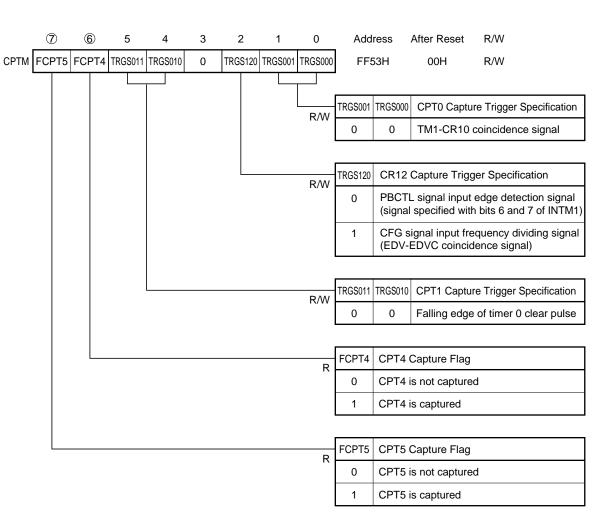

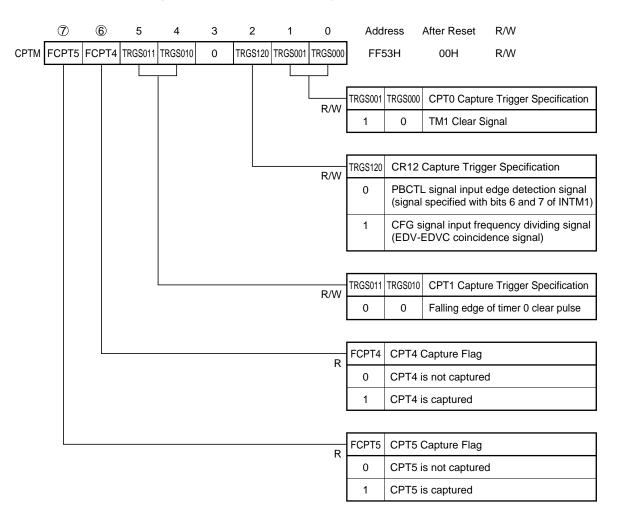

| 5-26       | Capture Mode Register (CPTM) Format                                       | 73   |

| 5-27       | Use of Timer for Drum Phase Control (for recording)                       | 75   |

| 5-28       | Drum Phase Control Timing (for recording)                                 | 76   |

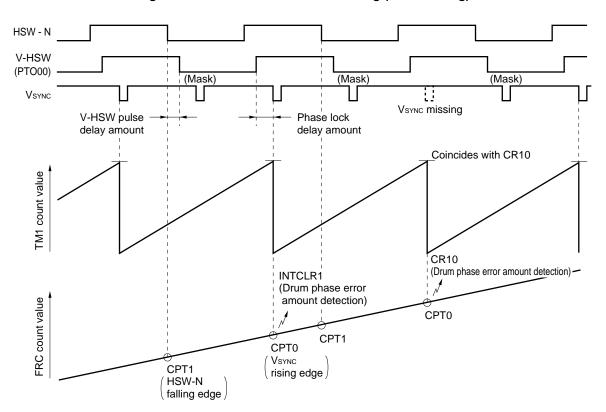

| 5-29       | Capture Mode Register (CPTM) Format                                       | 77   |

| 5-30       | Capstan Speed Detection Method                                            | 81   |

| 5-31       | Capstan Speed Control Timing                                              | 82   |

| 5-32       | Model of Capstan Phase Control                                            | 83   |

| 5-33       | Capstan Phase Error Detection Method (for playback)                       | 85   |

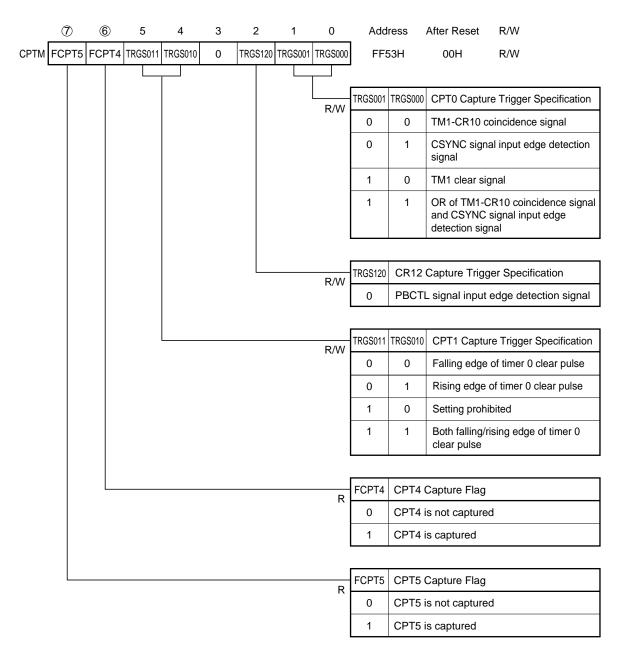

| 5-34       | Capture Mode Register (CPTM) Format                                       | 86   |

| 5-35       | Capstan Phase Control Timing (playback mode, phase locked)                | 87   |

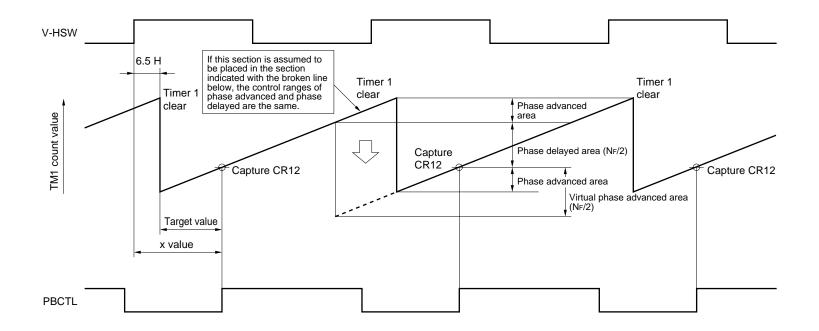

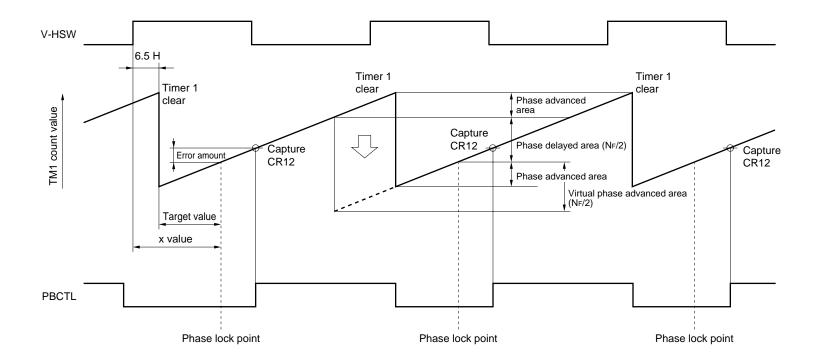

| 5-36       | Capstan Phase Control Timing (playback mode, phase delayed)               | 88   |

| 5-37       | Capstan Phase Control Timing (playback mode, phase advanced)              | 89   |

| 5-38       | Capstan Phase Error Detection Method (for recording)                      | 91   |

| 5-39       | Capture Mode Register (CPTM) Format                                       | 92   |

| 5-40       | Capstan Phase Control Timing (for recording)                              | 93   |

| 5-41       | Connection of $\mu$ PD784915 and Control Head                             | 95   |

|            |                                                                           |      |

# LIST OF FIGURES (2/2)

| Figure No. | Title                                                                   | Page |

|------------|-------------------------------------------------------------------------|------|

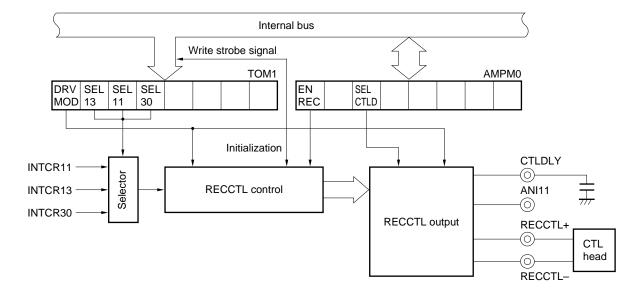

| 5-42       | RECCTL Driver Block Diagram                                             |      |

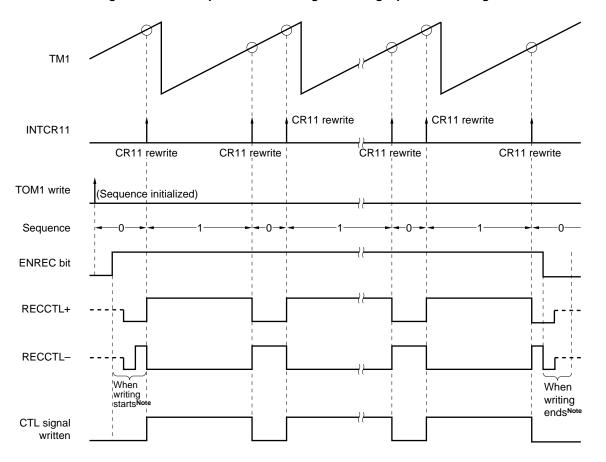

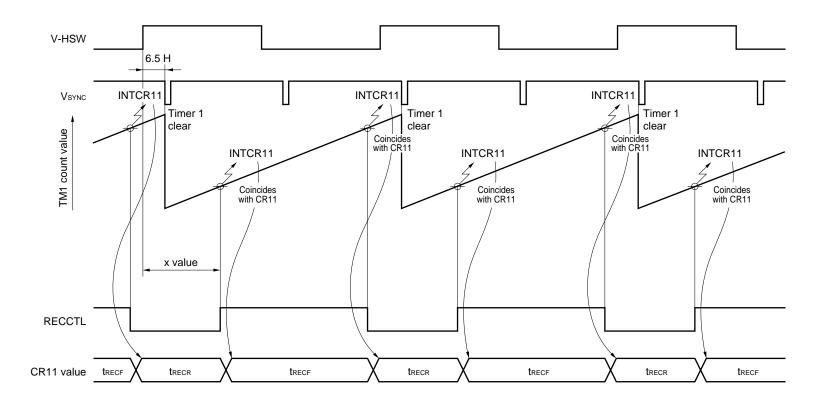

| 5-43       | Example of RECCTL Signal Writing Operation Timings                      |      |

| 5-44       | Timer 1 Output Mode Register (TOM1) Format                              |      |

| 5-45       | RECCTL Write Timing Using CR11                                          |      |

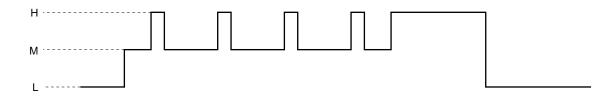

| 5-46       | Quasi-Vsync Waveform                                                    | 101  |

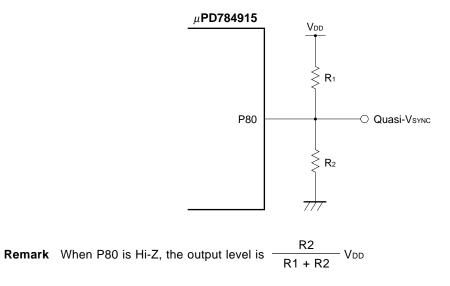

| 5-47       | Middle Level Generation                                                 | 101  |

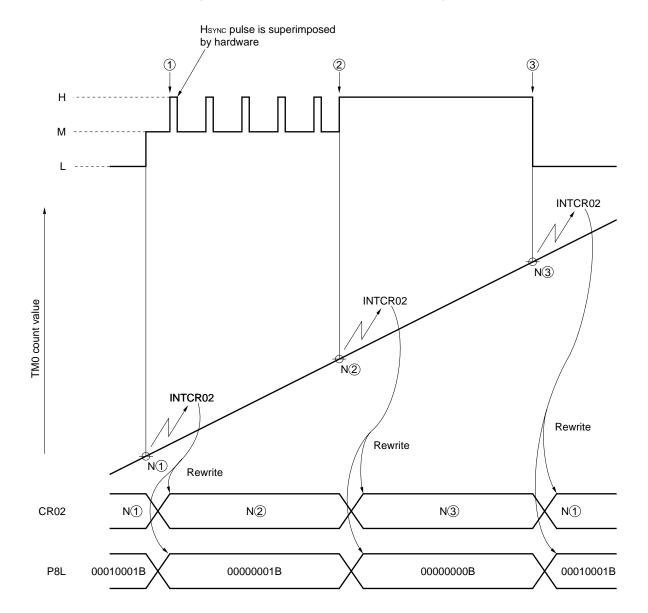

| 5-48       | Quasi-Vsync Generation Timing                                           | 102  |

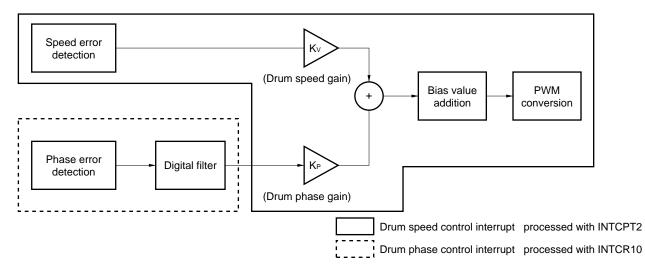

| 5-49       | Drum Control System Configuration                                       | 103  |

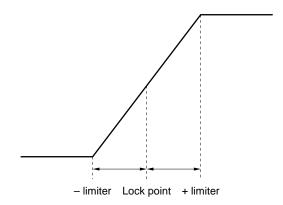

| 5-50       | Trapezoidal Pattern for Error Value Detection (drum control system)     | 104  |

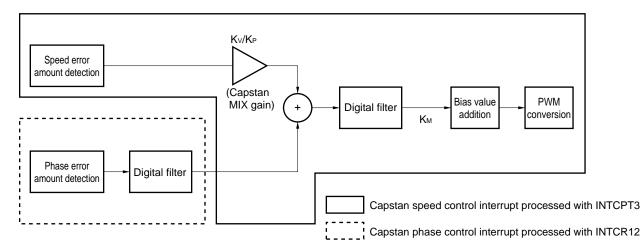

| 5-51       | Capstan Control System Configuration                                    | 107  |

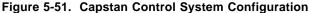

| 5-52       | Trapezoidal Pattern for Error Value Detection (capstan control system)  | 108  |

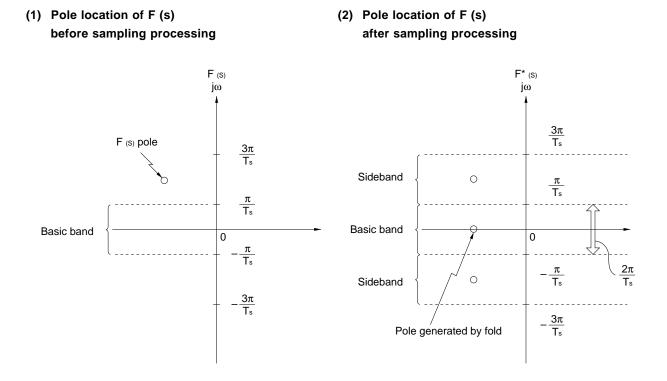

| 5-53       | Fold Error                                                              | 114  |

| 5-54       | Pole Location when Sampling Theorem is Satisfied                        | 115  |

| 5-55       | Pole Location when Sampling Theorem is Not Satisfied                    | 115  |

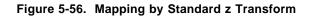

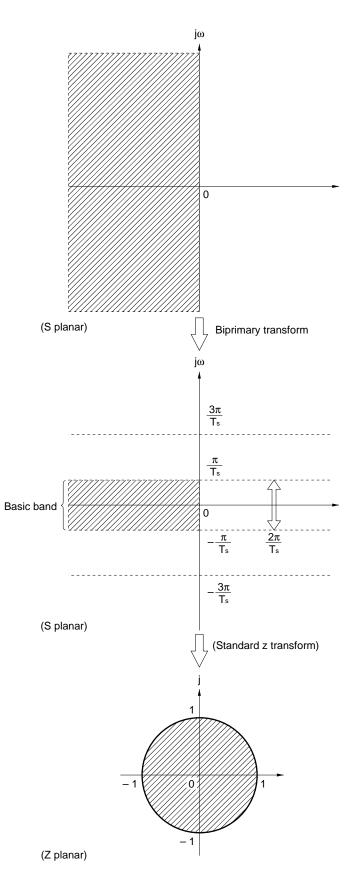

| 5-56       | Mapping by Standard z Transform                                         | 116  |

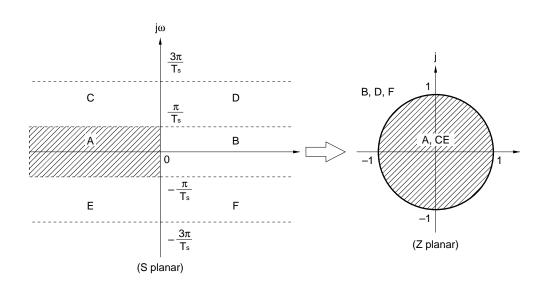

| 5-57       | Mapping by Biprimary Transform                                          | 118  |

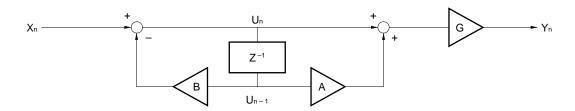

| 5-58       | Primary IIR Type Digital Filter Block Diagram                           | 120  |

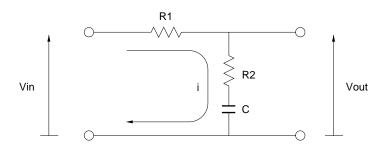

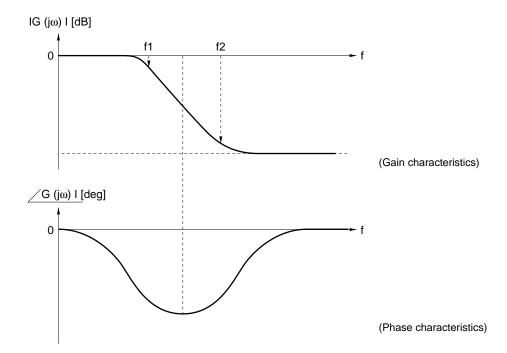

| 5-59       | Lag-lead Filter Configuration and Characteristics                       | 121  |

| 6-1        | CTL Amplifier Configuration                                             | 127  |

| 6-2        | Relationship between CTL Amplifier Output and Each Detection Level/Flag | 128  |

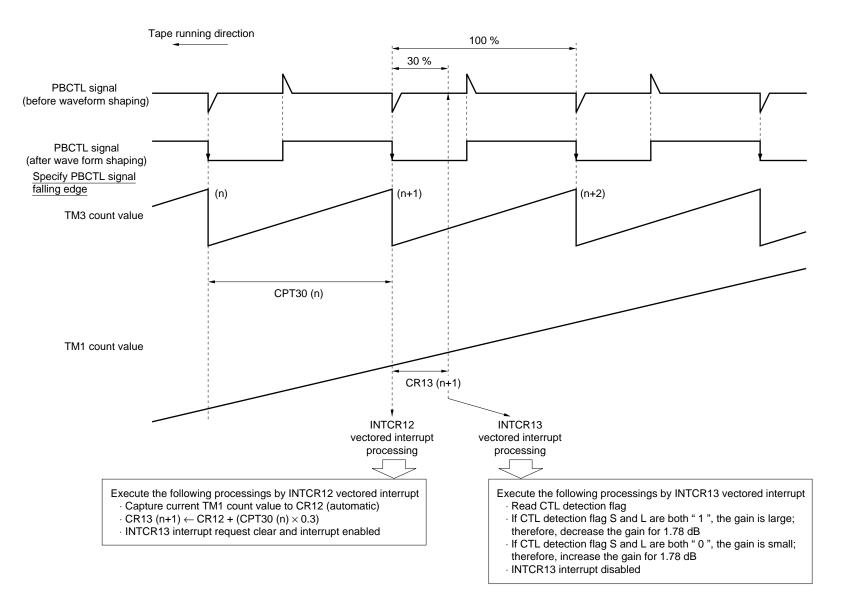

| 6-3        | Gain Change Timing for PLAY or CUE/REV in Forward Direction             | 130  |

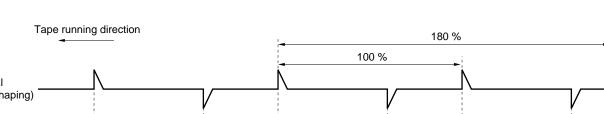

| 6-4        | Gain Change Timing for PLAY or CUE/REV in Reverse Direction             | 131  |

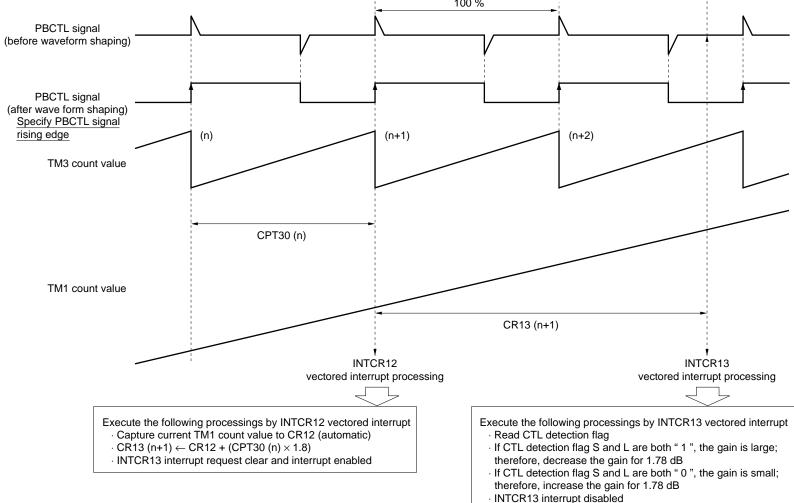

| 6-5        | Gain Change Timing for FF/REW in Forward Direction                      | 132  |

| 6-6        | Gain Change Timing for FF/REW in Reverse Direction                      | 133  |

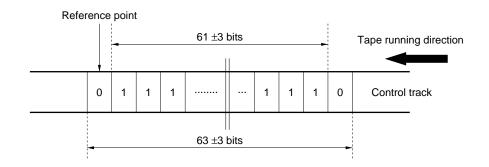

| 7-1        | VISS Cue Code                                                           | 137  |

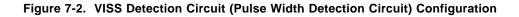

| 7-2        | VISS Detection Circuit (Pulse Width Detection Circuit) Configuration    | 138  |

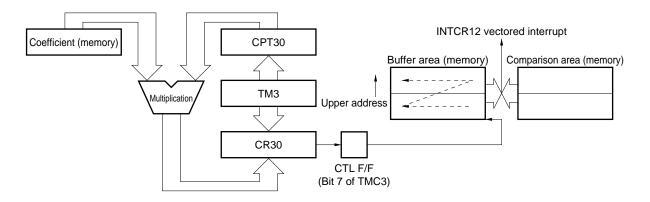

| 7-3        | Data Pattern Discrimination Mode Block Configuration                    | 140  |

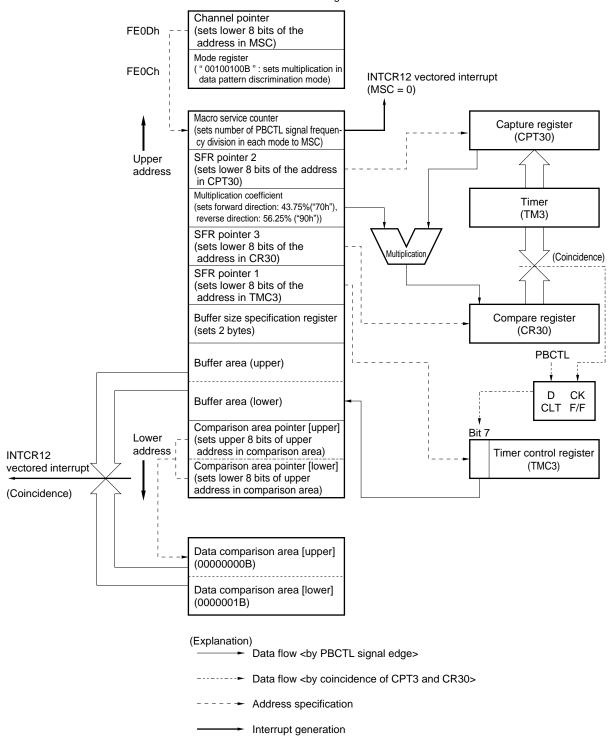

| 7-4        | Addressing and Data Setting in Data Pattern Discrimination Mode         | 141  |

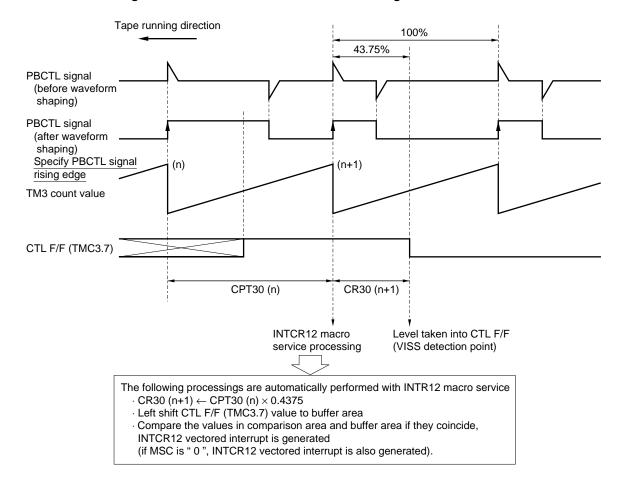

| 7-5        | INTCR12 Macro Service Processing in Forward Direction                   | 145  |

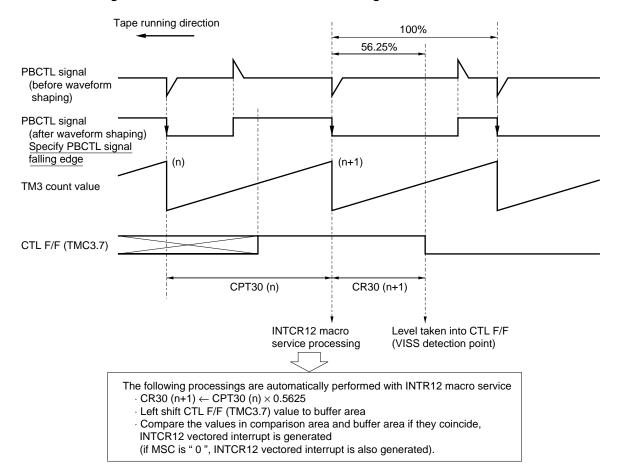

| 7-6        | INTCR12 Macro Service Processing in Reverse Direction                   | 146  |

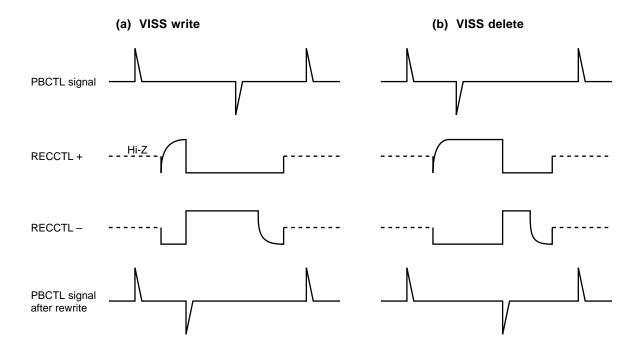

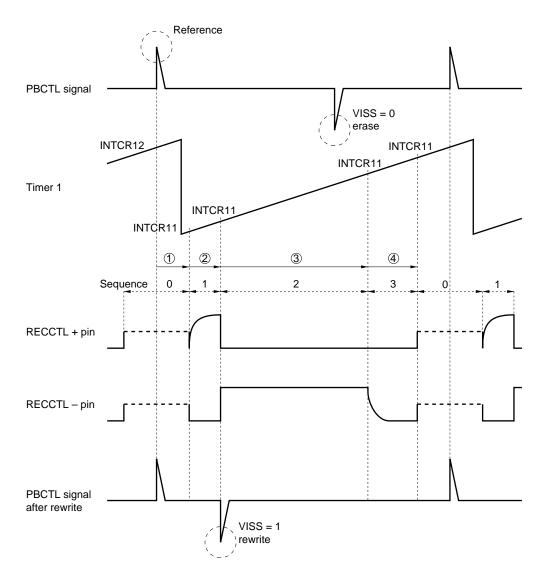

| 7-7        | VISS Rewrite                                                            | 147  |

| 7-8        | VISS = 1 Signal Rewrite Operation Timing Chart                          | 149  |

# LIST OF TABLES

| Table No. | Title                                                                            | Page  |

|-----------|----------------------------------------------------------------------------------|-------|

| 2-1       | Differences among $\mu$ PD784915 Subseries Products                              | . 19  |

| 3-1       | Differences among $\mu$ PD784928, 784928Y Subseries Products                     | . 25  |

| 3-2       | Differences among $\mu$ PD784928, 784928Y Subseries and $\mu$ PD784915 Subseries | . 32  |

| 5-1       | Using Examples of Super Timer Unit                                               | . 43  |

| 5-2       | RECCTL Driver REC Mode Sequence                                                  | . 95  |

| 5-3       | Capstan Loop Gain in Each Operation Mode                                         | . 110 |

| 5-4       | Capstan Bias Value in Each Operation Mode                                        | . 111 |

| 6-1       | CTL Detection Flag Read Value and CTL Amplifier Gain Adjustment                  | . 128 |

| 7-1       | VISS Data                                                                        | . 137 |

| 7-2       | RECCTL Driver Rewrite Mode Sequence                                              | . 148 |

| 7-3       | VISS Write Operation Timings                                                     | . 150 |

[MEMO]

# 1.1 Outline

$\star$

NEC's microcontrollers for VCR servos are 78K/IV Series products featuring a high-speed, high-performance 16bit CPU that are improved versions of the 78K/I Series of 8-bit single-chip microcontrollers for VCR software servo control.

Microcontrollers for VCR servo control comprise the following three subseries.

- μPD784915 Subseries

- μPD784928 Subseries

- μPD784928Y Subseries

NEC's lineup of microcontrollers for VCR servo control is shown below. The Y subseries support  $I^2C$  bus specifications.

Under mass production Under development

78K/IV Series

| μPD784928                 | μPD784928Y Exp<br>Enh | -pin QFP. Internal flash memory<br>anded on-chip memory capacity<br>anced analog amplifiers. Improved VCR functions. Increased number of I/Os.<br>ge-current port added. I <sup>2</sup> C function added (Y products only). |

|---------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| µPD784915<br>78K/I Series | Exp<br>On-            | -pin QFP<br>anded on-chip memory capacity<br>chip analog amplifiers. Enhanced super timer.<br>-power-dissipation mode added.                                                                                                |

| μPD78148                  |                       | -pin QFP<br>anded on-chip RAM capacity. On-chip operational amplifier, clock function, multiplier.                                                                                                                          |

| μPD78138                  | <b>7</b> 80-p         | bin QFP                                                                                                                                                                                                                     |

15

# • Microcontrollers for VCR Servo Control

# • µPD784915 Subseries

| Part Number           | μPD784915, 784915A, | μPD784916A,     | μPD78P4916    |

|-----------------------|---------------------|-----------------|---------------|

| Parameter             | $\mu$ PD784915B     | $\mu$ PD784916B |               |

| Internal ROM capacity | Mask ROM            |                 | One-time PROM |

|                       | 48 Kbytes 62 Kbytes |                 |               |

| Internal RAM capacity | 1280 bytes          |                 | 2048 bytes    |

# • µPD784928, 784928Y Subseries

| Part Number<br>Parameter | μΡD784927,<br>μΡD784927Υ | μPD78F4928 <sup>Note</sup> ,<br>μPD78F4928Y <sup>Note</sup> |

|--------------------------|--------------------------|-------------------------------------------------------------|

| Internal ROM capacity    | Mask ROM                 | Flash memory                                                |

|                          | 96 Kbytes                | 128 Kbytes                                                  |

| Internal RAM capacity    | 2048 bytes               | 3584 bytes                                                  |

Note Under development

# 1.2 Features

In this section, the  $\mu$ PD784915 Subseries is explained as the representative subseries, which is enhanced, compared with the 78K/I Series, in the points mentioned below.

### (1) Equipped with the 78K/IV core, a 16-bit high-performance CPU

The instruction set of the  $\mu$ PD784915 Subseries is perfectly upward-compatible with that of the existing 78K/I series. Therefore, the software assets of the 78K/I Series are effectively utilized.

The 78K/IV Series supports 1-Mbyte linear address space, resulting in improved program handlability. Moreover, the instruction set of the 78K/IV Series has been greatly enhanced, and realizes high-speed servo arithmetic processing by using powerful multiplication and 16-bit transmit instructions.

#### (2) Enhanced power management function

The  $\mu$ PD784915 Subseries realizes internal 8 MHz (minimum instruction execution time = 250 ns) high-speed operation in 4.5 to 5.5 V voltage range in normal operation. Its CPU guarantees 4.0-V operation. Moreover, the  $\mu$ PD784915 Subseries is equipped with a low power consumption mode which enables CPU operation using 32.768-kHz subsystem clock. Selection of CPU clock dividing ratio is made possible by onchip clock frequency dividing circuit. Since operation up to 2.7 V is guaranteed, reduction of the power consumption of the whole system is possible using these functions. The use of these functions in combination with the standby function realizes ultra low power consumption according to the operation conditions, that is, back-up supply voltage operation or battery operation.

# (3) Realizes low-frequency/high-speed operation for reducing radiation noise

The  $\mu$ PD784915 Subseries provides a low-frequency oscillation mode which enables internal operation with the clock frequency equal to the external oscillation frequency. It realizes reduction of radiation noise by enabling high-speed operation with a frequency lower than that of conventional products.

#### (4) On chip VCR servo control timer "Super Timer Unit"

The super timer unit consists of six 16-bit timers, two 8-bit timers, and a 5-bit up/down counter for linear tape in addition to 22-bit free running counter (FRC) to carry out cycle measurement of various VCR motors. Therefore, VCR servo control by software can be performed easily.

The  $\mu$ PD784915 is incorporated with special circuits such as V<sub>SYNC</sub> and H<sub>SYNC</sub> separation circuits required for VCR servo control in addition to three 16-bit resolution PWM outputs and three 8-bit resolution PWM outputs required for motor control.

#### (5) On-chip analog circuits for VCR

The analog circuits for VCR consist of a CTL amplifier to amplify record signals of the tape with any gain, a RECCTL driver required for writing CTL and VISS signals, and other constituents required for VCR servo control such as a drum FG amplifier, drum PG comparator, DPFG separation circuit (three-value separation circuit), CFG amplifier, reel FG comparator (2 channels), and CSYNC comparator.

The CTL amplifier can switch gain in 32 steps by software. In actuality, the CTL amplifier output gain is controlled by setting the CTL detection plug with software. Compared with conventional CTL amplifiers, the circuit configuration is more optimized, which results in a reduction of the number of pins from eleven to six. The analog circuits for VCR have made it possible to largely reduce the number of parts, enabling system cost reduction.

[MEMO]

# **CHAPTER 2 OUTLINE OF** µ**PD784915 SUBSERIES**

The  $\mu$ PD784915 Subseries under the 78K/IV Series consists of products provided with an on-chip high-speed, highperformance 16-bit CPU that are improved versions of the 78K/I Series of 8-bit single-chip microcontrollers for VCR software servo control.

The  $\mu$ PD784915 Subseries provides on chip optimum peripheral hardware for VCR control, including a multifunction timer unit (super timer unit) ideal for software servo control, and analog circuits, thus enabling the realization of VCR system/servo/timer control with a single chip.

Moreover, a product with on-chip one-time PROM, the  $\mu$ PD78P4916, is also available. This chapter describes the  $\mu$ PD784915 as the representative product.

\*

| Part Number<br>Parameter                          | μPD784915, 784915A,<br>μPD784915B                | μPD784916A,<br>μPD784916B | μPD78P4916    |

|---------------------------------------------------|--------------------------------------------------|---------------------------|---------------|

| Internal ROM capacity                             | Mask ROM                                         |                           | One-time PROM |

|                                                   | 48 Kbytes                                        | 62 Kbytes                 |               |

| Internal RAM capacity                             | 1280 bytes                                       |                           | 2048 bytes    |

| Internal memory capacity selection register (IMS) | Not provided                                     |                           | Provided      |

| IC pin                                            | Provided                                         |                           | Not provided  |

| VPP pin                                           | Not provided                                     |                           | Provided      |

| Electrical characteristics                        | tics Refer to data sheet of individual products. |                           |               |

# Table 2-1. Differences among *µ*PD784915 Subseries Products

# 2.1 Features and Application Fields

# (1) Features

- Minimum instruction execution time: 250 ns (operation when internal clock = 8 MHz)

- On-chip timer unit for VCR servo control (Super timer unit)

- I/O ports: 54

- On-chip VHS-compliant VCR analog circuits

• RECCTL driver (rewrite-capable)

• CTL amplifier

- DPG comparator

- DPFG separation circuit (3-value separation circuit)

CFG amplifierDFG amplifier

- Reel FG comparator (2 channels)CSYNC comparator

- Serial interface: 2 channels (3-wire serial I/O)

- A/D comparator: 8-bit resolution  $\times$  12 channels (conversion time: 10  $\mu$ s)

- PWM output: 16-bit resolution × 3 channels, 8-bit resolution × 3 channels

- Interrupt functions

- Vectored interrupt function

- Macro service function

- Context switching function

- Low-frequency oscillation mode supported: main system clock frequency = internal clock frequency

- Low-power-dissipation mode supported: CPU operation using subsystem clock possible

- Power supply voltage: VDD = 2.7 to 5.5 V

- On-chip hardware clock function: Low voltage (VDD = 2.7 V (MIN.)), low-current-dissipation clock operation possible

# (2) Application fields

System/servo/timer control for VCR (stationary type, camcorder)

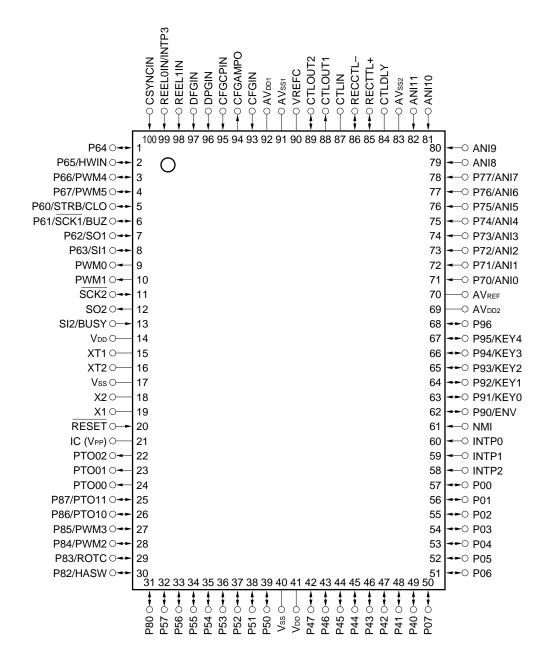

# 2.2 Pin Configuration (Top View)

100-pin plastic QFP (14 × 20 mm) μPD784915GF-xxx-3BA, 784915AGF-xxx-3BA, 784916AGF-xxx-3BA, μPD784915BGF-xxx-3BA, 784916BGF-xxx-3BA, 78P4916GF-3BA

Caution Connect IC (Internally Connected) pin directly to Vss.

**Remark** (): µPD78P4916

| ANI0 to ANI11    | : Analog Input                  | P00 to P07       | : Port0                         |

|------------------|---------------------------------|------------------|---------------------------------|

| AVdd1, AVdd2     | : Analog Power Supply           | P40 to P47       | : Port4                         |

| AVss1, AVss2     | : Analog Ground                 | P50 to P57       | : Port5                         |

| AVREF            | : Analog Reference Voltage      | P60 to P67       | : Port6                         |

| BUSY             | : Serial Busy                   | P70 to P77       | : Port7                         |

| BUZ              | : Buzzer Output                 | P80, P82 to P87  | : Port8                         |

| CFGAMPO          | : Capstan FG Amplifier Output   | P90 to P96       | : Port9                         |

| CFGCPIN          | : Capstan FG Capacitor Input    | PTO00 to PTO02,  | : Programmable Timer Output     |

| CFGIN            | : Analog Unit Input             | PTO10, PTO11     |                                 |

| CLO              | : Clock Output                  | PWM0 to PWM5     | : Pulse Width Modulation Output |

| CSYNCIN          | : Analog Unit Input             | RECCTL+, RECCTL- | : RECCTL Output/PBCLT Input     |

| CTLDLY           | : Control Delay Input           | REEL0IN, REEL1IN | : Analog Unit Input             |

| CTLIN            | : CTL Amplifier Input Capacitor | RESET            | : Reset                         |

| CTLOUT1, CTLOUT2 | : CTL Amplifier Output          | ROTC             | : Chrominance Rotate Output     |

| DFGIN            | : Analog Unit Input             | SCK1, SCK2       | : Serial Clock                  |

| DPGIN            | : Analog Unit Input             | SI1, SI2         | : Serial Input                  |

| ENV              | : Envelope Input                | SO1, SO2         | : Serial Output                 |

| HASW             | : Head Amplifier Switch Output  | STRB             | : Serial Strobe                 |

| HWIN             | : Hardware Timer External Input | Vdd              | : Power Supply                  |

| IC               | : Internally Connected          | VREFC            | : Reference Amplifier Capacitor |

| INTP0 to INTP3   | : Interrupt From Peripherals    | Vss              | : Ground                        |

| KEY0 to KEY4     | : Key Return                    | X1, X2           | : Crystal (Main System Clock)   |

| NMI              | : Non-maskable Interrupt        | XT1, XT2         | : Crystal (Subsystem Clock)     |

|                  |                                 |                  |                                 |

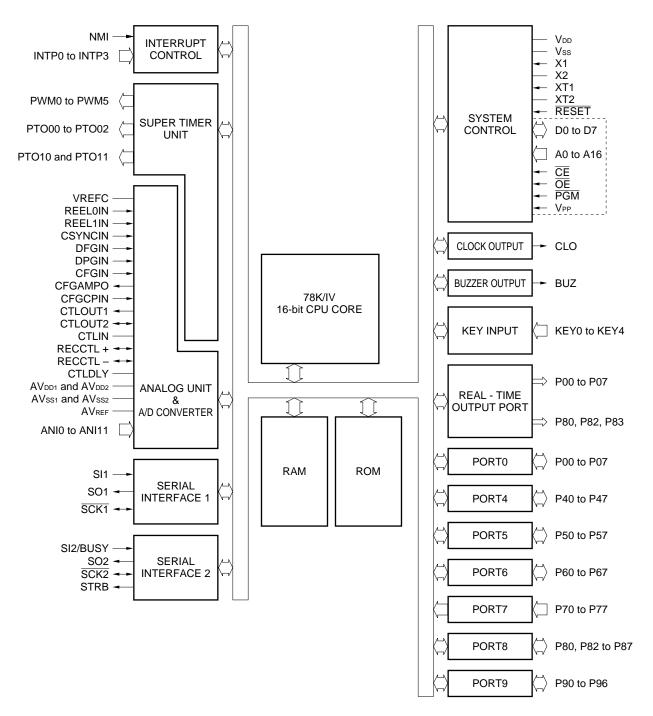

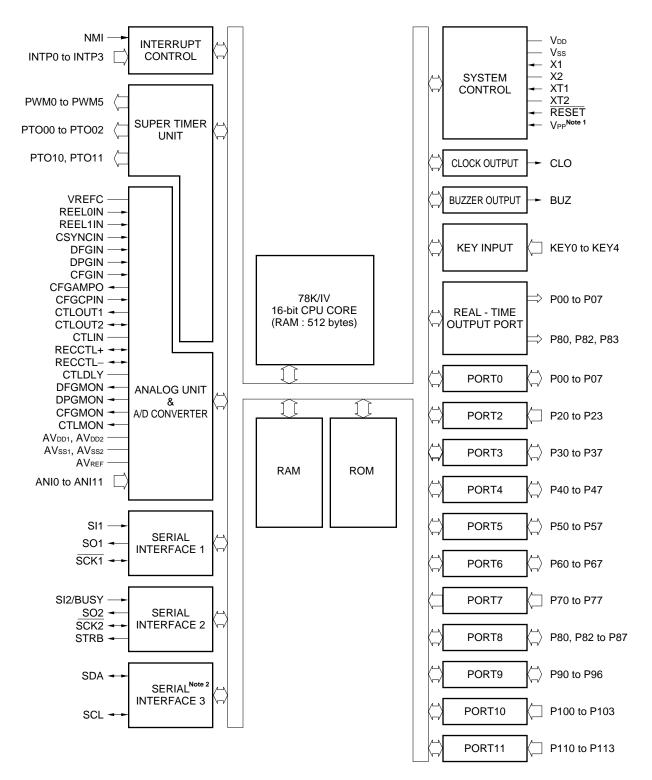

# 2.3 Block Diagram

Remarks 1. Internal ROM capacity and RAM capacity differ depending on the product.

2. The broken line indicates the connection in PROM programming mode.

# 2.4 Outline of Functions

|                                                             |                                                                                                                     | Part Number         | μPD784915, 784915A,                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  | 784916A,                                                                                                                                                 |                                                         | μPD78P4      | 916                                   |  |  |  |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------|---------------------------------------|--|--|--|

| Parameter                                                   |                                                                                                                     |                     | μPD784915B                                                                                                                                                                                                                                                                                                                                                       | μΡΟ                                                                                                                              | 784916B                                                                                                                                                  |                                                         |              |                                       |  |  |  |

| -                                                           | structions                                                                                                          |                     | 113                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |                                                                                                                                                          |                                                         |              |                                       |  |  |  |

| Minimum instruction execution time<br>Internal ROM capacity |                                                                                                                     |                     | 250 ns (internal clock: 8 MHz)                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |                                                                                                                                                          |                                                         |              |                                       |  |  |  |

|                                                             |                                                                                                                     | acity               | Mask ROM                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                |                                                                                                                                                          | One-time PROM                                           |              |                                       |  |  |  |

|                                                             |                                                                                                                     |                     | 48 Kbytes                                                                                                                                                                                                                                                                                                                                                        | 62 Kbytes                                                                                                                        |                                                                                                                                                          |                                                         |              |                                       |  |  |  |

| Inte                                                        | ernal RAM cap                                                                                                       | acity               | 1280 bytes                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |                                                                                                                                                          | 2048 I                                                  | bytes        |                                       |  |  |  |

| Interrupt                                                   |                                                                                                                     |                     | 4-level (programmable), v                                                                                                                                                                                                                                                                                                                                        | ectored interro                                                                                                                  | upts, macro servi                                                                                                                                        | ice, con                                                | ntext switcl | ning                                  |  |  |  |

|                                                             | External source                                                                                                     | e                   | 9 (including NMI)                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |                                                                                                                                                          |                                                         |              |                                       |  |  |  |

|                                                             | Internal source                                                                                                     | Э                   | 19                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                  |                                                                                                                                                          |                                                         |              |                                       |  |  |  |

|                                                             | Macro service                                                                                                       | available interrupt | 25                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                  |                                                                                                                                                          |                                                         |              |                                       |  |  |  |

| F                                                           | Number of ma                                                                                                        | cro service         | 10 (4 types)                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |                                                                                                                                                          |                                                         |              |                                       |  |  |  |

| 1/0                                                         | ) ports                                                                                                             | Input               | 8                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |                                                                                                                                                          |                                                         |              |                                       |  |  |  |

|                                                             |                                                                                                                     | I/O                 | 46                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                  |                                                                                                                                                          |                                                         |              |                                       |  |  |  |

| Tin                                                         | me-based coun                                                                                                       | 1                   | • 22-bit FRC                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |                                                                                                                                                          |                                                         |              |                                       |  |  |  |

|                                                             |                                                                                                                     |                     | Resolution: 125 ns, max                                                                                                                                                                                                                                                                                                                                          | timum count ti                                                                                                                   | me: 524 ms                                                                                                                                               |                                                         |              |                                       |  |  |  |

| Са                                                          | pture register                                                                                                      |                     | Input Signal Nu                                                                                                                                                                                                                                                                                                                                                  | mber of Bits                                                                                                                     | Measurement                                                                                                                                              | Cycle                                                   | Operatio     | n Edge                                |  |  |  |

|                                                             |                                                                                                                     |                     | CFG                                                                                                                                                                                                                                                                                                                                                              | 22                                                                                                                               | 125 ns to 52                                                                                                                                             | 4 ms                                                    | ↑            | ↓                                     |  |  |  |

|                                                             |                                                                                                                     |                     | DFG                                                                                                                                                                                                                                                                                                                                                              | 22                                                                                                                               | 125 ns to 52                                                                                                                                             | 4 ms                                                    | $\uparrow$   |                                       |  |  |  |

|                                                             |                                                                                                                     |                     | HSW                                                                                                                                                                                                                                                                                                                                                              | 16                                                                                                                               | 1 <i>µ</i> s to 65.5                                                                                                                                     | i ms                                                    | $\uparrow$   | $\downarrow$                          |  |  |  |

|                                                             |                                                                                                                     |                     | VSYNC                                                                                                                                                                                                                                                                                                                                                            | 22                                                                                                                               | 125 ns to 52                                                                                                                                             | 4 ms                                                    | $\uparrow$   |                                       |  |  |  |

|                                                             |                                                                                                                     |                     | CTL                                                                                                                                                                                                                                                                                                                                                              | 16                                                                                                                               | 1 μs to 65.5                                                                                                                                             | i ms                                                    | $\uparrow$   | $\downarrow$                          |  |  |  |

|                                                             |                                                                                                                     |                     | TREEL                                                                                                                                                                                                                                                                                                                                                            | 22                                                                                                                               | 125 ns to 52                                                                                                                                             | 4 ms                                                    | $\uparrow$   | $\downarrow$                          |  |  |  |

|                                                             |                                                                                                                     |                     | Sreel                                                                                                                                                                                                                                                                                                                                                            | 22                                                                                                                               | 125 ns to 52                                                                                                                                             | 4 ms                                                    | $\uparrow$   | $\downarrow$                          |  |  |  |

| Ge                                                          | eneral-purpose                                                                                                      | timer               | 16-bit timer × 3                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                  |                                                                                                                                                          |                                                         |              |                                       |  |  |  |

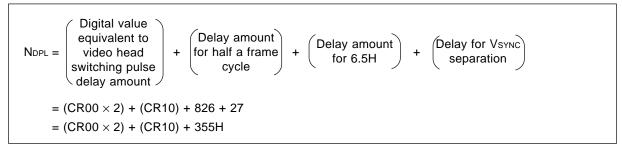

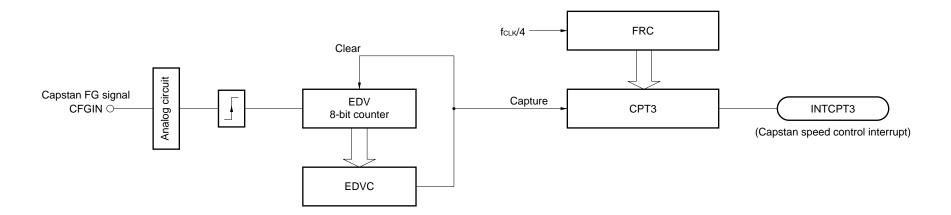

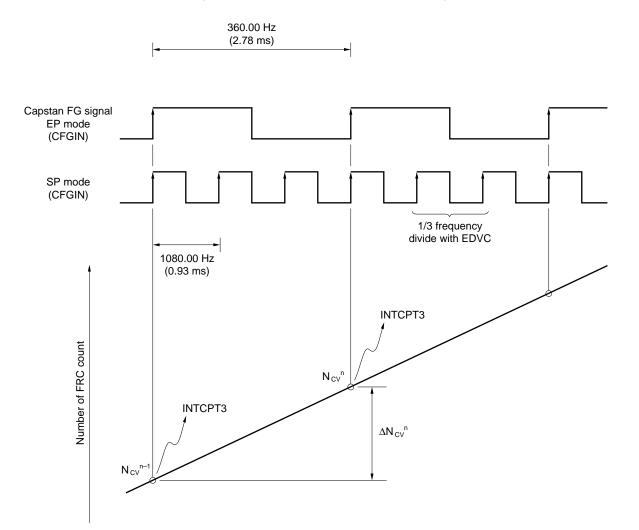

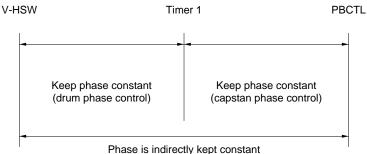

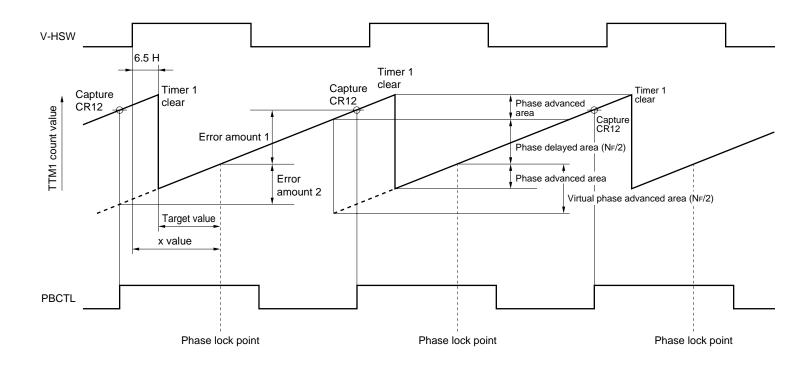

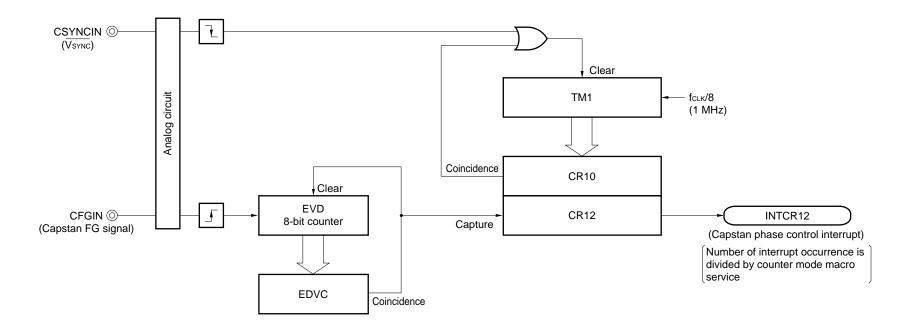

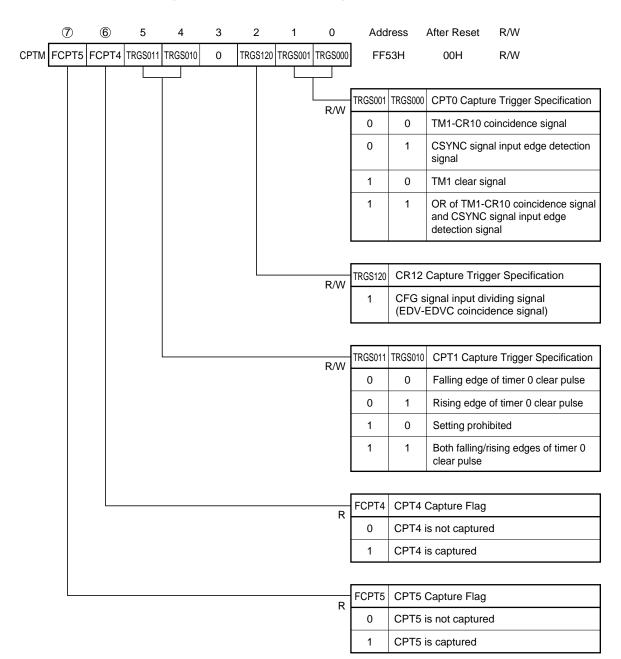

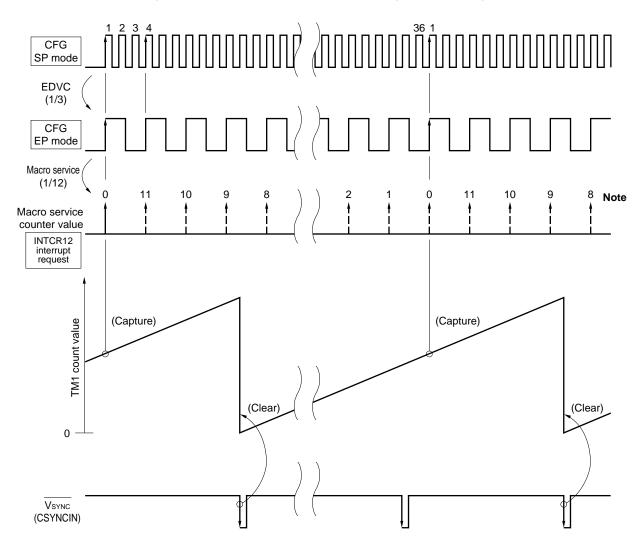

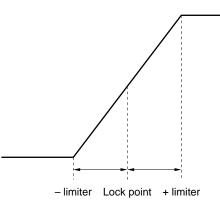

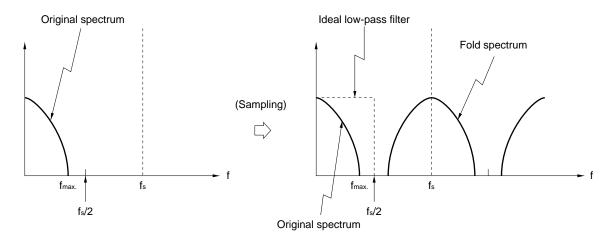

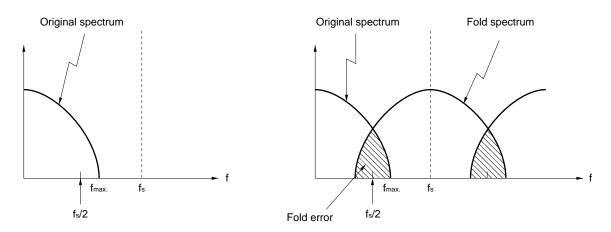

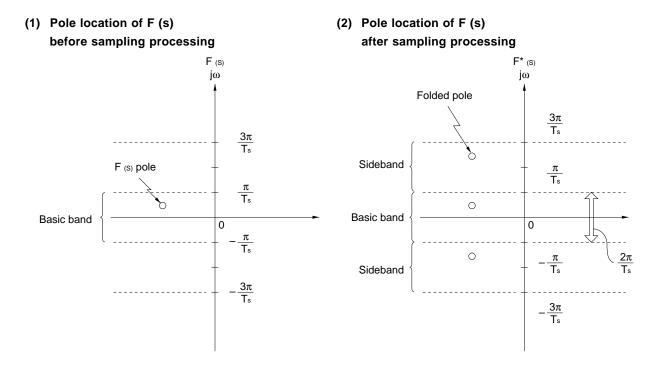

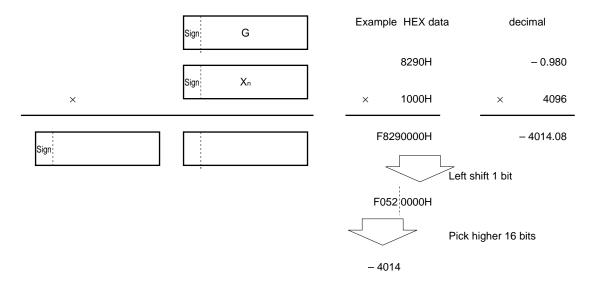

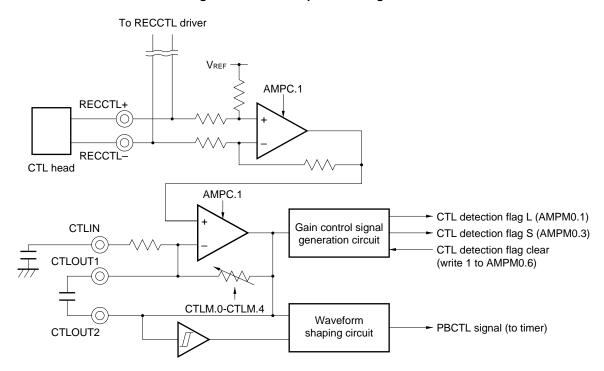

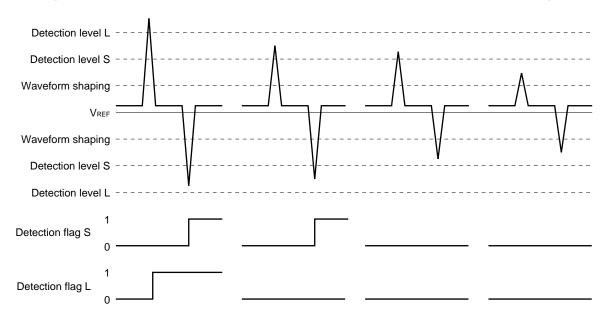

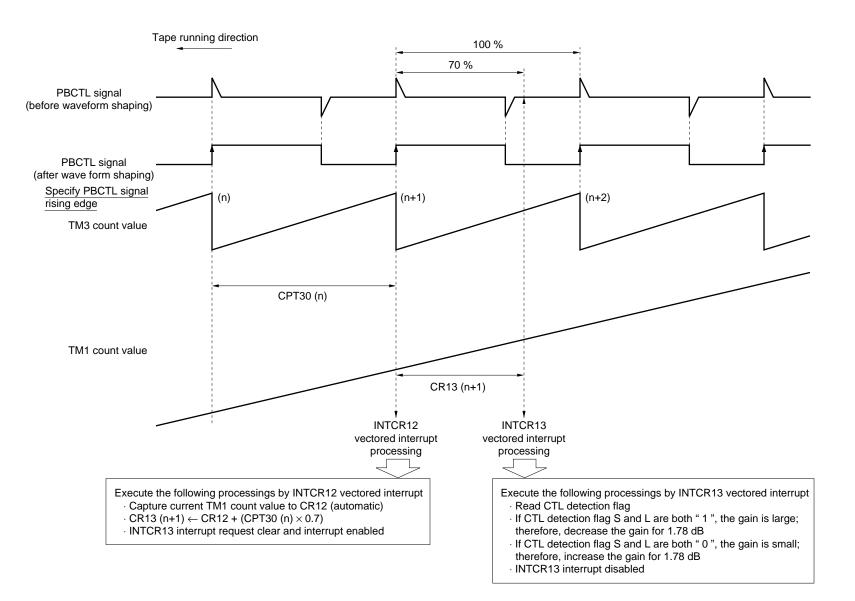

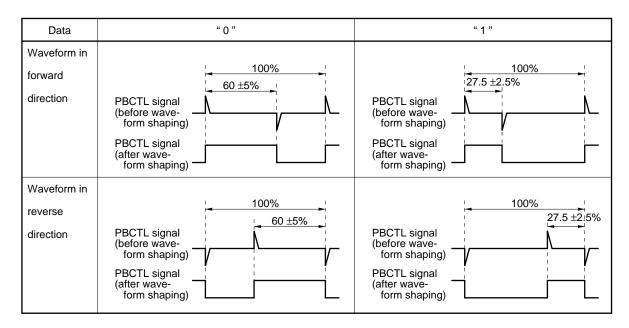

| PBCTL duty discrimination                                   |                                                                                                                     |                     | Duty discrimination for Play control signal                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |                                                                                                                                                          |                                                         |              |                                       |  |  |  |