###

### 2.4GHz 802.11b Zero-IF Transceiver with Integrated PA and Tx/Rx Switch

### General Description

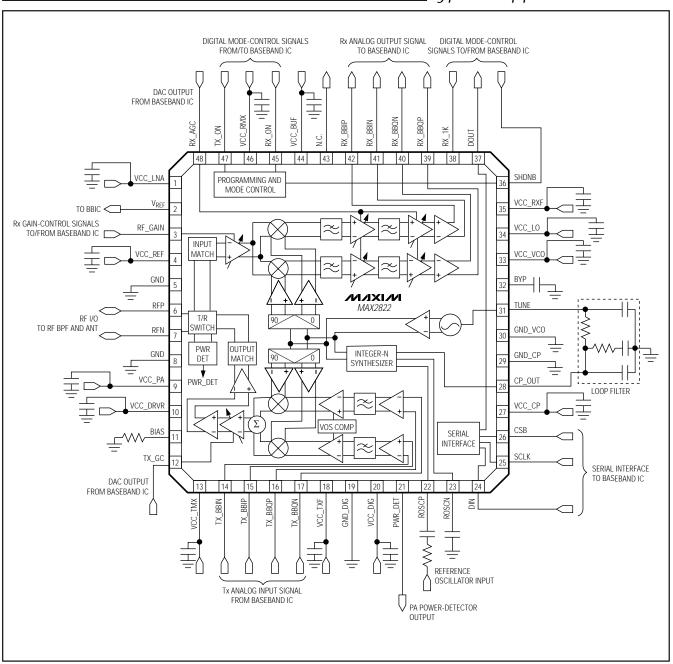

The MAX2822 single-chip transceiver is designed for 802.11b (11Mbps) applications operating in the 2.4GHz to 2.5GHz ISM band. The transceiver includes all the circuitry required to implement an 802.11b RF-to-baseband transceiver solution, including the power amplifier, transmit/receive switch, and  $50\Omega$  matching. The fully integrated receive path, transmit path, VCO, frequency synthesis, and baseband/control interface provide all the required active RF circuitry. Only a small number of passive components are needed to form the complete radio front-end solution.

The IC eliminates the need for external IF SAW and RF image-reject filters by utilizing a direct-conversion radio architecture and monolithic baseband filters for both receiver and transmitter. It is specifically optimized for 802.11b (11Mbps CCK) and 22Mbps PBCC<sup>™</sup> applications. The baseband filtering and Rx and Tx signal paths support the CCK modulation scheme for BER = 10<sup>-5</sup> at the required sensitivity levels.

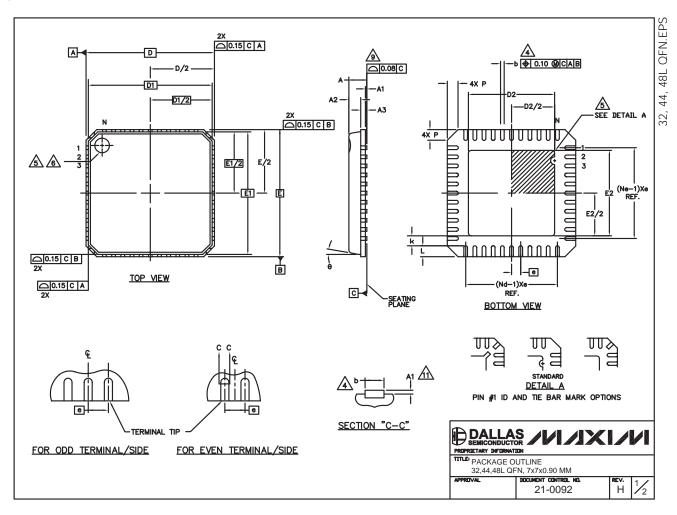

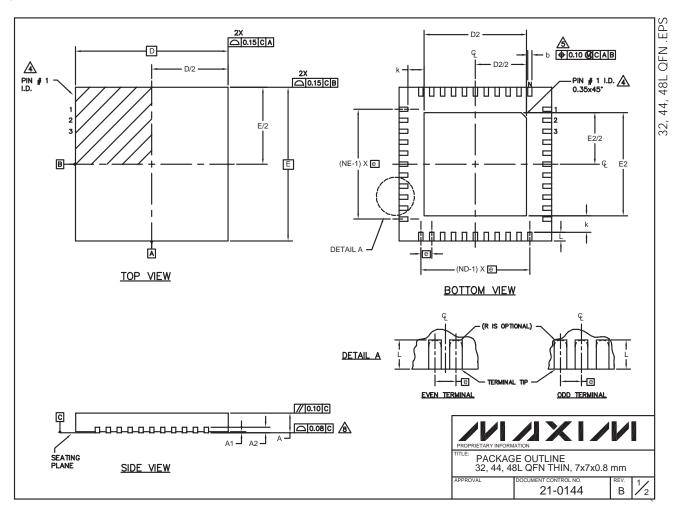

The transceiver is suitable for the full range of 802.11b data rates (1Mbps, 2Mbps, 5.5Mbps, and 11Mbps) as well as the higher-rate 22Mbps PBCC standard. The MAX2822 is available in the very small 7mm x 7mm 48lead QFN or thin QFN packages. The small solution size makes it ideal for small form-factor 802.11b applications such as PDAs, SmartPhones, and embedded modules.

Features

- ♦ 2.4GHz to 2.5GHz ISM Band Operation

- ♦ 802.11b (11Mbps CCK and 22Mbps PBCC) PHY Compatible

- ♦ Integrated +17dBm PA

- ♦ Integrated PA Power Detector

- ♦ Integrated Transmit/Receive Switch

- **♦ Complete RF-to-Baseband Transceiver Direct Up/Down Conversion** Monolithic Low-Phase-Noise VCO **Integrated Baseband Lowpass Filters** Integrated PLL with 3-Wire Serial Interface **Digital Bias Control for PA Transmit Power Control Receive Baseband AGC Complete Baseband Interface** Digital Tx/Rx Mode Control

- ◆ -95dBm Rx Sensitivity at 1Mbps

- ◆ -85dBm Rx Sensitivity at 11Mbps

- ♦ Single +2.7V to +3.0V Supply

- ♦ 2µA Shutdown Mode

- ♦ Very Small 48-Pin QFN Package

### **Applications**

802.11b PDAs and SmartPhones 802.11b Embedded Modules 802.11b PC Cards, Mini-PCI Cards

### Ordering Information

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX2822EGM | -40°C to +85°C | 48 QFN      |

| MAX2822ETM | -40°C to +85°C | 48 Thin QFN |

Pin Configuration/Functional Diagram appears at end of data sheet.

PBCC is a trademark of Texas Instruments, Inc.

#### ABSOLUTE MAXIMUM RATINGS

| V <sub>CC</sub> Pins to GNDRF I/O: RFP, RFN (current into pin)<br>Baseband Inputs: TX_BBIP, TX_BBIN | 50mA<br>N, TX_BBQP,              | Bias Voltages:<br>Short-Circuit Do<br>RF Input Power |

|-----------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------|

| TX_BBQN to GND                                                                                      | 0.3V to (VCC + 0.3V)             | Continuous Pov                                       |

| Baseband Outputs: RX_BBIP, RX_BE                                                                    |                                  | 48-Lead QFI                                          |

| RX_BBQN to GND                                                                                      | 0.3V to (Vcc + 0.3V)             | Operating Tem                                        |

| Analog Inputs: RX_AGC, TX_GC, TUI                                                                   |                                  | Junction Temp                                        |

| ROSCP to GND                                                                                        | 0.3V to (V <sub>CC</sub> + 0.3V) | Storage Tempe                                        |

| Analog Outputs: PWR_DET, CP_OUT                                                                     | -                                | Lead Temperat                                        |

| to GND                                                                                              | 0.3V to (V <sub>CC</sub> + 0.3V) |                                                      |

| Digital Inputs: RX_ON, TX_ON, SHDN                                                                  | NB, CSB, SCLK,                   |                                                      |

| DIN, RF_GAIN, RX_1K to GND                                                                          |                                  |                                                      |

|                                                                                                     |                                  |                                                      |

| Bias Voltages: RBIAS, BYP+0.9V to                     |        |

|-------------------------------------------------------|--------|

| Short-Circuit Duration Digital Output: DOUT           | 10s    |

| RF Input Power+                                       | 10dBm  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |        |

| 48-Lead QFN (derate 27.0mW/°C above +70°C)21          | 62mW   |

| Operating Temperature Range40°C to                    | +85°C  |

| Junction Temperature                                  | -150°C |

| Storage Temperature Range65°C to +                    | -160°C |

| Lead Temperature (soldering, 10s)                     | -300°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

(MAX2822 EV kit:  $V_{CC} = +2.7V$  to +3.0V, RF\_GAIN =  $V_{IH}$ ,  $0V \le V_{TX\_GC} \le +2.0V$ ,  $0V \le V_{RX\_AGC} \le +2.0V$ ,  $R_{BIAS} = 12k\Omega$ , no input signals at RF and baseband inputs, RF I/O terminated into  $50\Omega$  though a 2:1 balun, receiver baseband outputs are open, transmitter baseband inputs biased at +1.2V, registers set to default power-up settings,  $T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are for  $V_{CC} = +2.7V$ ,  $T_{A} = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETERS                                     |                                             | CONDITIO                  | ONS                                           | MIN                    | TYP | MAX | UNITS |  |

|------------------------------------------------|---------------------------------------------|---------------------------|-----------------------------------------------|------------------------|-----|-----|-------|--|

| Supply Voltage                                 |                                             |                           | 2.7                                           |                        | 3.0 | V   |       |  |

| Shutdown Current                               | SHDNB = V <sub>IL</sub> , R                 | $RX_ON = V_{IL}, TX$      | ON = VIL                                      |                        | 2   | 50  | μΑ    |  |

| Standby-Mode Supply Current                    | SHDNB = V <sub>IH</sub> , F                 | RX_ON = V <sub>IL</sub> , | $T_A = +25^{\circ}C$                          |                        | 25  | 35  | mA    |  |

| Standby-wode Supply Current                    | TX_ON = V <sub>IL</sub>                     |                           | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                        |     | 40  | IIIA  |  |

| Receive-Mode Supply Current                    | SHDNB = V <sub>IH</sub> , F                 | $RX_ON = V_{IH}$ ,        | $T_A = +25^{\circ}C$                          |                        | 80  | 100 | mA    |  |

| Receive-ivioue Supply Current                  | TX_ON = V <sub>IL</sub>                     |                           | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                        |     | 110 | IIIA  |  |

|                                                | SHDNB = V <sub>IH</sub> ,                   | POUT = +3dBr              | n                                             |                        | 98  |     |       |  |

| T " " A                                        | $RX_ON = V_{ L}$                            | Pout =                    | T <sub>A</sub> = +25°C                        |                        | 157 | 175 | 1     |  |

| Transmit-Mode Supply Current                   | TX_ON = V <sub>IH</sub> ,<br>bias registers | +12dBm                    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                        |     | 185 | mA    |  |

|                                                | set as in Table 9                           | Pout = +17dE              | 3m                                            |                        | 220 |     |       |  |

| LOGIC INPUTS: SHDNB, RX_ON                     | TX_ON, SCLK,                                | DIN, CSB, RF_0            | GAIN                                          | 1                      |     |     |       |  |

| Digital Input Voltage High (V <sub>IH</sub> )  |                                             |                           |                                               | V <sub>C</sub> C - 0.5 |     |     | V     |  |

| Digital Input Voltage Low (VIL)                |                                             |                           |                                               |                        |     | 0.5 | V     |  |

| Digital Input Current High (I <sub>IH</sub> )  |                                             |                           |                                               | -5                     |     | +5  | μΑ    |  |

| Digital Input Current Low (IIL)                |                                             |                           |                                               | -5                     |     | +5  | μΑ    |  |

| LOGIC OUTPUT: DOUT                             |                                             |                           |                                               |                        |     |     |       |  |

| Digital Output Voltage High (V <sub>OH</sub> ) | Sourcing 100μA                              |                           |                                               | V <sub>CC</sub> - 0.5  |     |     | V     |  |

| Digital Output Voltage Low (VOL)               | Sinking 100µA                               |                           |                                               |                        |     | 0.5 | V     |  |

| ANALOG OUTPUT: PWR_DET                         |                                             |                           |                                               |                        |     |     |       |  |

| Power-Detector Output<br>Impedance             |                                             |                           |                                               |                        | 400 |     | Ω     |  |

### DC ELECTRICAL CHARACTERISTICS (continued)

(MAX2822 EV kit:  $V_{CC}$  = +2.7V to +3.0V, RF\_GAIN =  $V_{IH}$ , 0V  $\leq$   $V_{TX\_GC}$   $\leq$  +2.0V, 0V  $\leq$   $V_{RX\_AGC}$   $\leq$  +2.0V, R<sub>BIAS</sub> = 12k $\Omega$ , no input signals at RF and baseband inputs, RF I/O terminated into 50 $\Omega$  though a 2:1 balun, receiver baseband outputs are open, transmitter baseband inputs biased at +1.2V, registers set to default power-up settings, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are for V<sub>CC</sub> = +2.7V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETERS                              | CONDITIONS                     | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------|--------------------------------|------|------|------|-------|

| RX BASEBAND I/O                         | ·                              |      |      |      | •     |

| RX_AGC Input Resistance                 | $0V \le V_{RX\_AGC} \le +2.0V$ |      | 50   |      | kΩ    |

| Rx I/Q Common-Mode Voltage              |                                |      | 1.25 |      | V     |

| Rx I/Q Output DC Offsets                | $3\sigma$ limit                |      | ±15  |      | mV    |

| TX BASEBAND I/O                         |                                |      |      |      | 1     |

| TX BB Input Common-Mode<br>Range        |                                | 1.0  | 1.2  | 1.4  | V     |

| TX BBI and BBQ Input Bias<br>Current    |                                |      | -10  |      | μА    |

| TX BB Input Impedance                   | Differential resistance        |      | 100  |      | kΩ    |

| TX_GC Input Bias Current                | $0V \le V_{TX\_GC} \le +2.0V$  |      | 10   |      | μΑ    |

| TX_GC Input Impedance                   | Resistance                     |      | 250  |      | kΩ    |

| REFERENCE OSCILLATOR IN                 | PUT                            |      |      |      |       |

| Reference Oscillator Input<br>Impedance |                                |      | 20   |      | kΩ    |

| VOLTAGE REFERENCE                       | ·                              |      |      |      | •     |

| Reference Voltage                       | $I_{LOAD} = \pm 2mA$           | 1.10 | 1.20 | 1.30 | V     |

#### AC ELECTRICAL CHARACTERISTICS—RECEIVE MODE

(MAX2822 EV kit:  $V_{CC} = +2.7V$  to +3.0V,  $f_{RF}$  and  $f_{LO} = 2400MHz$  to 2499MHz,  $f_{OSC} = 22MHz$  or 44MHz, receive baseband output levels =  $500mV_{P-P}$ ,  $V_{SHDNB} = V_{RX\_ON} = V_{IH}$ ,  $V_{TX\_ON} = V_{IL}$ ,  $V_{CSB} = V_{IH}$ ,  $V_{SCLK} = V_{DIN} = V_{IL}$ ,  $V_{RF\_GAIN} = V_{IH}$ ,  $0V \le V_{RX\_AGC} \le +2.0V$ ,  $V_{RBIAS} = 12k\Omega$ ,  $V_{RS} = V_{RS} = V_{R$

| PARAMETER                                                   | CON                                         | CONDITIONS                                              |      | TYP | MAX  | UNITS |  |  |

|-------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------|------|-----|------|-------|--|--|

| RECEIVER CASCADED PERFORMANCE (RF INPUT TO BASEBAND OUTPUT) |                                             |                                                         |      |     |      |       |  |  |

| RF Frequency Range                                          |                                             |                                                         | 2400 |     | 2499 | MHz   |  |  |

| LO Frequency Range                                          |                                             |                                                         | 2400 |     | 2499 | MHz   |  |  |

|                                                             | RF_GAIN = V <sub>IH</sub> ,                 | $T_A = +25^{\circ}C$                                    | 97   | 105 |      |       |  |  |

|                                                             | $V_{RX\_AGC} = 0V$                          | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$           | 95   |     |      |       |  |  |

| Voltage Gain (Note 3)                                       | $RF\_GAIN = V_{IH}, V_{RX}$                 | RF_GAIN = V <sub>IH</sub> , V <sub>RX_AGC</sub> = +2.0V |      | 35  |      | dB    |  |  |

|                                                             | RF_GAIN = V <sub>IL</sub> , V <sub>RX</sub> | RF_GAIN = V <sub>IL</sub> , V <sub>RX_AGC</sub> = 0V    |      | 75  |      |       |  |  |

|                                                             | RF_GAIN = V <sub>IL</sub> , V <sub>RX</sub> | $RF\_GAIN = V_{IL}, V_{RX\_AGC} = +2.0V$                |      | 3   |      | 1     |  |  |

| RF Gain Step                                                | From RF_GAIN = VII                          | to RF_GAIN = VIL                                        |      | 32  |      | dB    |  |  |

### AC ELECTRICAL CHARACTERISTICS—RECEIVE MODE (continued)

(MAX2822 EV kit:  $V_{CC} = +2.7V$  to +3.0V,  $f_{RF}$  and  $f_{LO} = 2400$ MHz to 2499MHz,  $f_{OSC} = 22$ MHz or 44MHz, receive baseband output levels = 500mVp-p,  $V_{SHDNB} = V_{RX}$ \_ON =  $V_{IH}$ ,  $V_{TX}$ \_ON =  $V_{IL}$ ,  $V_{CSB} = V_{IH}$ ,  $V_{SCLK} = V_{DIN} = V_{IL}$ ,  $V_{RF}$ \_GAIN =  $V_{IH}$ ,  $0V \le V_{RX}$ \_AGC  $\le +2.0V$ ,  $V_{RB}$

| PARAMETER                                   | CONDITIONS                                                                                       | MIN | TYP | MAX | UNITS   |

|---------------------------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|---------|

|                                             | RF_GAIN = V <sub>IH</sub> , RX gain ≥ 80dB                                                       |     | 5.5 | 6.0 |         |

| DSB Noise Figure (Note 4)                   | RF_GAIN = V <sub>IH</sub> , RX gain = 50dB                                                       |     | 8   |     | dB      |

|                                             | RF_GAIN = V <sub>IL</sub> , RX gain = 50dB                                                       |     | 35  |     | ]       |

| Adjacent Channel Rejection                  | RX gain = 70dB (Note 5)                                                                          |     | 45  |     | dB      |

| Input Third Order Intercent Deint (Note ()  | RF_GAIN = V <sub>IH</sub> , RX gain = 80dB                                                       |     | -13 |     | dBm     |

| Input Third-Order Intercept Point (Note 6)  | RF_GAIN = V <sub>IL</sub> , RX gain = 50dB                                                       |     | +19 |     | abin    |

|                                             | RF_GAIN = V <sub>IH</sub> , RX gain = 80dB                                                       |     | +23 |     | dD.m    |

| Input Second-Order Intercept Point (Note 7) | RF_GAIN = V <sub>IL</sub> , RX gain = 50dB                                                       |     | +60 |     | dBm     |

| LO Leakage                                  | At balun input                                                                                   |     | -65 |     | dBm     |

| Input Return Loss                           |                                                                                                  |     | 15  |     | dB      |

|                                             | RECEIVER BASEBAND                                                                                |     |     |     |         |

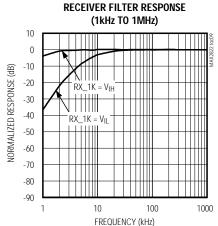

| BASEBAND FILTER RESPONSE                    |                                                                                                  |     |     |     |         |

| -3dB Frequency                              | Default bandwidth setting BW(2:0) = (010)                                                        |     | 7   |     | MHz     |

|                                             | At 12.5MHz                                                                                       |     | 40  |     |         |

| Attenuation Relative to Passband            | At 16MHz                                                                                         |     | 65  |     | dB      |

| Attenuation Relative to Passband            | At 20MHz                                                                                         |     | 70  |     | ub ub   |

|                                             | At 25MHz                                                                                         |     | 85  |     |         |

| BASEBAND OUTPUT CHARACTERISTICS             |                                                                                                  |     |     |     |         |

| Rx I/Q Gain Imbalance                       | 3σ limit                                                                                         |     | ±1  |     | dB      |

| Rx I/Q Phase Quadrature Imbalance           | 3σ limit                                                                                         |     | ±5  |     | Degrees |

| Rx I/Q Output 1dB Compression               | Differential voltage into $5k\Omega$                                                             |     | 1   |     | VP-P    |

| Rx I/Q Output THD                           | $V_{OUT} = 500 \text{mV}_{P-P} \text{ at } 5.5 \text{MHz}, Z_L = 5 \text{k}\Omega   5 \text{pF}$ |     | -35 |     | dBc     |

| BASEBAND AGC AMPLIFIER                      |                                                                                                  |     |     |     |         |

| AGC Range                                   | $V_{RX\_AGC} = 0 \text{ to } +2.0V$                                                              |     | 70  |     | dB      |

| AGC Slope                                   | Peak gain slope                                                                                  |     | 60  |     | dB/V    |

| AGC Response Time                           | 20dB gain step (80dB to 60dB),<br>settling to ±1dB                                               |     | 2   |     | μs      |

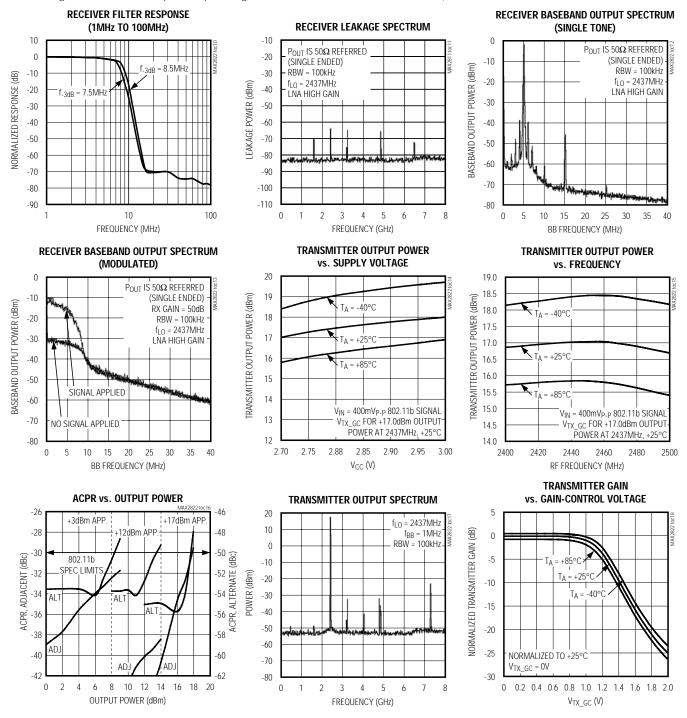

### AC ELECTRICAL CHARACTERISTICS—TRANSMIT MODE

(MAX2822 EV kit, characteristics relative to RFP/RFN:  $V_{CC} = +2.7V$  to +3.0V,  $f_{RF}$  and  $f_{LO} = 2400MHz$  to 2499MHz,  $f_{OSC} = 22MHz$  or 44MHz, transmit baseband input signal:  $500mV_{P-P}$  at 5.5MHz,  $V_{SHDNB} = V_{RX\_ON} = V_{IL}$ ,  $V_{TX\_ON} = V_{IH}$ ,  $V_{CSB} = V_{IH}$ ,  $V_{SCLK} = V_{DIN} = V_{IL}$ ,  $V_{RF\_GAIN} = V_{IH}$ ,  $0V \le V_{TX\_AGC} \le +2.0V$ ,  $V_{RBIAS} = 12k\Omega$ ,  $V_{RBIAS$

| PARAMETER                                    | COND                                                                                                                     | ITIONS                                        | MIN   | TYP   | MAX  | UNITS  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------|-------|------|--------|

| TRANSMIT SIGNAL PATH: BASEBAND INPU          | JT TO RF OUTPUT                                                                                                          |                                               |       |       |      |        |

| RF Output Frequency Range                    |                                                                                                                          |                                               | 2400  |       | 2499 | MHz    |

| LO Output Frequency Range                    |                                                                                                                          |                                               | 2400  |       | 2499 | MHz    |

| Tx RF Output Power                           | 11Mbps CCK signal,<br>ACPR (adj) ≤ -30dBc,                                                                               | T <sub>A</sub> = +25°C                        | +16.5 | +17.5 |      | - dBm  |

| 1x Ki Gulput i owei                          | ACPR (alt) ≤ -50dBc<br>(Note 4)                                                                                          | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | +15.5 |       |      | abiii  |

| Ty DE ACDD (Note 9)                          | Adjacent (adj):<br>$-22MHz \le f_{OFFSET} \le -1$<br>$11MHz \le f_{OFFSET} \le 22$<br>$P_{OUT} = +16.5dBm$               | OFFSET ≤ -11MHz,<br>OFFSET ≤ 22MHz,           |       | -33   |      | dDo    |

| Tx RF ACPR (Note 8)                          | Alternate (alt): -33MHz ≤ f <sub>OFFSET</sub> < -22MHz, 22MHz < f <sub>OFFSET</sub> ≤ 33MHz, P <sub>OUT</sub> = +16.5dBm |                                               |       | -56   |      | dBc    |

|                                              | f <sub>RF</sub> = 2400MHz to                                                                                             | Unwanted sideband                             |       | -40   |      |        |

| In-Band Spurious Signals Relative to Carrier | 2483MHz                                                                                                                  | LO signal                                     |       | -30   | di   | dBc    |

|                                              | (Note 9)                                                                                                                 | Spurs > ±22MHz                                |       | -80   |      | Ĭ      |

| Tx RF Harmonics                              | 11Mbps CCK at                                                                                                            | $2 \times f_{RF}$                             |       | -45   |      | dBm    |

| TX RF Halfflorites                           | +16.5dBm                                                                                                                 | $3 \times f_{RF}$                             |       | -30   |      | UDIII  |

| Tx RF Spurious Signal Emissions              | < 2400MHz                                                                                                                |                                               |       | -50   |      |        |

| (Outside 2400MHz to 2483.5MHz)               | 2500MHz to 3350MHz                                                                                                       | •                                             |       | -35   |      | dBm    |

| Nonharmonic Signals                          | > 3350MHz                                                                                                                |                                               |       | -40   |      |        |

| Tx RF Output Noise                           | f <sub>OFFSET</sub> ≥ 22MHz, 0V                                                                                          | $\leq$ V <sub>TX_GC</sub> $\leq$ +2.0V        |       | -125  |      | dBm/Hz |

| Tx RF Output Return Loss                     | 100Ω balanced outpu<br>P <sub>OUT</sub> = +17dBm                                                                         | t impedance,                                  |       | 10    |      | dB     |

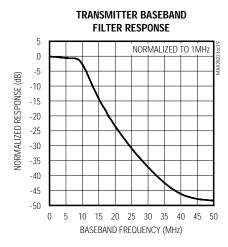

| Tx BASEBAND FILTER RESPONSE                  | •                                                                                                                        |                                               |       |       |      |        |

| -3dB Frequency                               |                                                                                                                          |                                               |       | 10    |      | MHz    |

| Attanuation Dalative to December 4           | At 22MHz                                                                                                                 |                                               |       | 25    |      | ٩D     |

| Attenuation Relative to Passband             | At 44MHz                                                                                                                 |                                               |       | 50    |      | dB     |

| Tx GAIN-CONTROL CHARACTERISTICS              |                                                                                                                          |                                               |       |       |      |        |

| Gain-Control Range                           | $0V \le V_{TX\_GC} \le +2.0V$                                                                                            |                                               |       | 20    |      | dB     |

| Gain-Control Slope                           | Peak gain slope                                                                                                          |                                               |       | 30    |      | dB/V   |

| Gain-Control Response Time                   | $V_{TX\_GC} = +2.0V \text{ to } 0V$<br>±1dB                                                                              | step, settled to within                       |       | 0.3   |      | μs     |

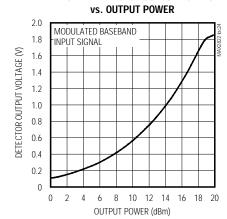

### AC ELECTRICAL CHARACTERISTICS—TRANSMIT MODE (continued)

(MAX2822 EV kit, characteristics relative to RFP/RFN:  $V_{CC} = +2.7V$  to +3.0V,  $f_{RF}$  and  $f_{LO} = 2400MHz$  to 2499MHz,  $f_{OSC} = 22MHz$  or 44MHz, transmit baseband input signal:  $500mV_{P-P}$  at 5.5MHz,  $V_{SHDNB} = V_{RX\_ON} = V_{IL}$ ,  $V_{TX\_ON} = V_{IH}$ ,  $V_{CSB} = V_{IH}$ ,  $V_{SCLK} = V_{DIN} = V_{IL}$ ,  $V_{RF\_GAIN} = V_{IH}$ ,  $0V \le V_{TX\_AGC} \le +2.0V$ ,  $R_{BIAS} = 12k\Omega$ ,  $I_{CP} = +2mA$ ,  $BW_{PLL} = 45kHz$ , baseband inputs DC biased to +1.2V, registers set to default power-up settings, measurements taken within 1s of TXON rising edge,  $T_{A} = +25^{\circ}C$ , unless otherwise noted. Typical values are for  $V_{CC} = +2.7V$ ,  $f_{LO} = 2437MHz$ ,  $f_{OSC} = 22MHz$ , unless otherwise noted.) (Note 2)

| PARAMETER                                           | CON                                                 | IDITIONS                            | MIN | TYP  | MAX | UNITS |

|-----------------------------------------------------|-----------------------------------------------------|-------------------------------------|-----|------|-----|-------|

| POWER DETECTOR                                      |                                                     |                                     |     |      |     |       |

| Power-Detection Range                               | 0.1V ≤ V <sub>PWR_DET</sub> ≤                       | 0.1V ≤ V <sub>PWR_DET</sub> ≤ 1.5V  |     | 17   |     | dB    |

| D                                                   | Fixed V <sub>PWR_DET</sub> ,                        | POUT = +3dBm                        |     | ±0.7 |     | dB    |

| Power-Detection Error (3σ Limit)                    | $T_A = +25^{\circ}C$                                | POUT = +17dBm                       |     | ±0.5 |     | UБ    |

| Power-Detection Error Variation with<br>Temperature | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | C, relative to $T_A = +25^{\circ}C$ |     | ±0.3 |     | dB    |

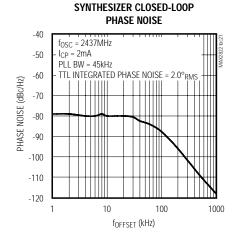

### AC ELECTRICAL CHARACTERISTICS—SYNTHESIZER

(MAX2822 EV kit:  $V_{CC} = +2.7V$  to +3.0V, f<sub>RF</sub> and f<sub>LO</sub> = 2400MHz to 2499MHz, f<sub>OSC</sub> = 22MHz or 44MHz, SHDNB = V<sub>IH</sub>, CSB = V<sub>IH</sub>, R<sub>BIAS</sub> =  $12k\Omega$ , I<sub>CP</sub> = +2mA, BW<sub>PLL</sub> = 45kHz, registers set to default power-up settings, T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted. Typical values are for V<sub>CC</sub> = +2.7V, f<sub>LO</sub> = 2437MHz, f<sub>OSC</sub> = 22MHz, unless otherwise noted.) (Note 2)

| PARAMETER                          | CONDITIONS                                                                    | MIN  | TYP | MAX                   | UNITS             |

|------------------------------------|-------------------------------------------------------------------------------|------|-----|-----------------------|-------------------|

| FREQUENCY SYNTHESIZER              |                                                                               | I    |     |                       | - I               |

| LO Frequency Range                 |                                                                               | 2400 |     | 2499                  | MHz               |

| Deference Fraguency                | SYNTH:R(0) = 0                                                                |      | 22  | MHz                   |                   |

| Reference Frequency                | SYNTH:R(0) = 1                                                                |      | 44  |                       | IVIHZ             |

| Minimum Channel Spacing            |                                                                               |      | 1   |                       | MHz               |

| Charge-Pump Output Current         |                                                                               |      | ±2  |                       | mA                |

| Charge-Pump Compliance Range       |                                                                               | 0.4  |     | V <sub>CC</sub> - 0.4 | V                 |

|                                    | -11MHz ≤ f <sub>OFFSET</sub> ≤ 11MHz                                          |      | -41 |                       |                   |

| Reference Spur Level (Note 10)     | -22MHz ≤ f <sub>OFFSET</sub> < -11MHz,<br>11MHz < f <sub>OFFSET</sub> ≤ 22MHz |      | -75 |                       | dBc               |

|                                    | foffset < -22MHz, foffset > 22MHz                                             |      | -90 |                       | 1                 |

| Classed Laster Dhases Nation       | foffset = 10kHz                                                               |      | -80 |                       | -ID - /I I-       |

| Closed-Loop Phase Noise            | foffset = 100kHz                                                              |      | -87 |                       | dBc/Hz            |

| Closed-Loop Integrated Phase Noise | Noise integrated from 100Hz to 10MHz, measured at the TX_RF output            |      | 2.5 |                       | °RMS              |

| Reference Oscillator Input Level   | AC-coupled sine wave input                                                    | 200  | 300 | 500                   | mV <sub>P-P</sub> |

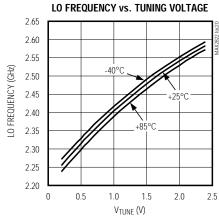

| VOLTAGE-CONTROLLED OSCILLATOR      |                                                                               |      |     |                       |                   |

| VCO Tuning Valtage Dange           | f <sub>LO</sub> = 2400MHz                                                     | 0.4  |     |                       | V                 |

| VCO Tuning Voltage Range           | $f_{LO} = 2499MHz$                                                            |      |     | 2.3                   | V                 |

| VCO Tuning Cain                    | fLO = 2400MHz                                                                 |      | 170 |                       | MHz/V             |

| VCO Tuning Gain                    | fLO = 2499MHz                                                                 |      | 130 |                       | IVIMZ/V           |

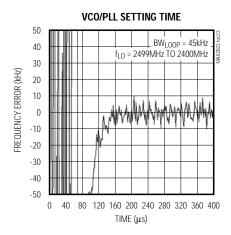

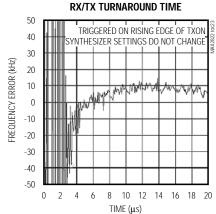

#### AC ELECTRICAL CHARACTERISTICS—SYSTEM TIMING

(MAX2822 EV kit:  $V_{CC}$  = +2.7V to +3.0V,  $f_{RF}$  and  $f_{LO}$  = 2400MHz to 2499MHz,  $f_{OSC}$  = 22MHz or 44MHz, SHDNB = V<sub>IH</sub>, CSB = V<sub>IH</sub>, R<sub>BIAS</sub> = 12k $\Omega$ , I<sub>CP</sub> = +2mA, BW<sub>PLL</sub> = 45kHz, registers set to default power-up settings, T<sub>A</sub> = +25°C, unless otherwise noted. Typical values are for V<sub>CC</sub> = +2.7V,  $f_{LO}$  = 2437MHz,  $f_{OSC}$  = 22MHz, unless otherwise noted.) (Note 2)

| PARAMETER                | CONDITIONS                                                                               | MIN | TYP | MAX | UNITS |

|--------------------------|------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Channel-Switching Time   | $f_{LO} = 2400 MHz \leftrightarrow 2499 MHz$ ,<br>$f_{LO}$ settles to ±10kHz (Note 11)   |     | 150 | 200 | μs    |

| Du/Ty Tyrnarayad Time    | Rx to Tx, $f_{LO}$ settles to within $\pm 30 kHz$ , relative to the rising edge of TX_ON |     | 5   |     |       |

| Rx/Tx Turnaround Time    | Tx to Rx, fLO settles to within ±30kHz, relative to the rising edge of RX_ON             |     |     | 10  | μs    |

| Standby-to-Receive Mode  | Standby to Rx, fLO settles to within ±30kHz, relative to the rising edge of RX_ON        |     |     | 10  | μs    |

| Standby-to-Transmit Mode | Standby to Tx, fLO settles to within ±30kHz, relative to the rising edge of TX_ON        |     |     | 5   | μs    |

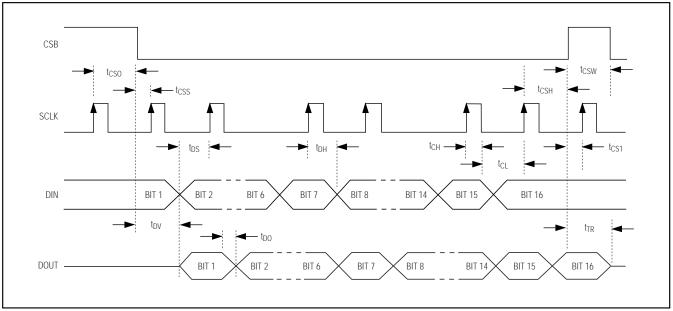

### AC ELECTRICAL CHARACTERISTICS—SERIAL INTERFACE TIMING

(MAX2822 EV kit: V<sub>CC</sub> = +2.7V to +3.0V, registers set to default power-up settings, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER        | CONDITIONS                                                           | MIN | TYP | MAX | UNITS |

|------------------|----------------------------------------------------------------------|-----|-----|-----|-------|

| SERIAL INTERFAC  | CE TIMING (SEE FIGURE 1)                                             |     |     |     |       |

| tcso             | SCLK rising edge to CSB falling edge wait time                       | 5   |     |     | ns    |

| tcss             | Falling edge of CSB to rising edge of first SCLK time                | 5   |     |     | ns    |

| t <sub>DS</sub>  | Data-to-serial clock setup time                                      | 5   |     |     | ns    |

| tDH              | Data-to-clock hold time                                              | 10  |     |     | ns    |

| tсн              | Serial clock pulse-width high                                        | 10  |     |     | ns    |

| t <sub>CL</sub>  | Clock pulse-width low                                                | 10  |     |     | ns    |

| tсsн             | Last SCLK rising edge to rising edge of CSB                          | 5   |     |     | ns    |

| tcsw             | CSB high pulse width                                                 | 10  |     |     | ns    |

| t <sub>CS1</sub> | Time between the rising edge of CSB and the next rising edge of SCLK | 5   |     |     | ns    |

| f <sub>CLK</sub> | Clock frequency                                                      |     |     | 50  | MHz   |

- Note 1: Parameters are production tested at +25°C only. Min/max limits over temperature are guaranteed by design and characterization.

- **Note 2:** Guaranteed by design and characterization.

- Note 3: Defined as the baseband differential RMS output voltage divided by the RMS input voltage (at the RF balun input).

- Note 4: Specification excludes the loss of the external balun. The external balun loss is typically ~0.5dB.

- **Note 5:** CCK interferer at 25MHz offset. Desired signal equals -73dBm. Interferer amplitude increases until baseband output from interferer is 10dB below desired signal. Adjacent channel rejection = PINTERFERER PDESIRED.

- Note 6: Measured at balun input. Two CW tones at -43dBm with 15MHz and 25MHz offset from the MAX2822 channel frequency. IP3 is computed from 5MHz IMD3 product measured at the Rx I/Q output.

- Note 7: Two CW interferers at -38dBm with 24.5MHz and 25.5MHz offset from the MAX2822 channel frequency. IP2 is computed from the 1MHz IMD2 product measured at the RX I/Q output.

- **Note 8:** VTXGC adjusted for +16.5dBm output power; adjacent and alternate channel power relative to the desired signal. Power measured with 100kHz video BW and 100kHz resolution BW.

- Note 9: CW tone at 2.25MHz offset from carrier with VTXGC set for maximum modulated POUT at -30dBc/-50dBc (ADJ/ALT) ACPR limits. Unwanted sideband refers to suppressed image resulting from I/Q baseband input tones.

- **Note 10:** Relative amplitude of reference spurious products appearing in the Tx RF output spectrum relative to a CW tone at 2.25MHz offset from the LO.

- Note 11: Time required to reprogram the PLL, change the operating channel, and wait for the operating channel center frequency to settle within ±10kHz of the nominal (final) channel frequency.

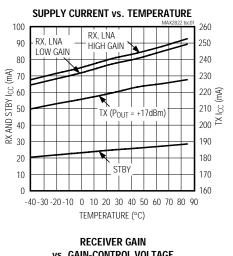

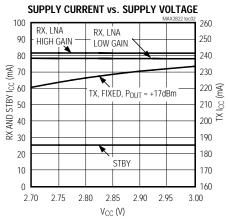

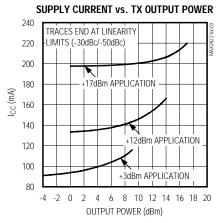

### Typical Operating Characteristics

(MAX2822 EV kit,  $V_{CC}$  = +2.7V,  $f_{BB}$  = 1MHz,  $f_{LO}$  = 2437MHz, receive baseband outputs = 500mV<sub>P-P</sub>, transmit baseband inputs = 400mV<sub>P-P</sub>, ICP = +2mA, BWPLL = 45kHz, differential RF input/output matched to 50 $\Omega$  through a balun, baseband input biased at +1.2V, registers set to default power-up settings,  $T_A$  = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(MAX2822 EV kit,  $V_{CC}$  = +2.7V,  $f_{BB}$  = 1MHz,  $f_{LO}$  = 2437MHz, receive baseband outputs = 500mV<sub>P-P</sub>, transmit baseband inputs = 400mV<sub>P-P</sub>, ICP = +2mA, BWPLL = 45kHz, differential RF input/output matched to 50 $\Omega$  through a balun, baseband input biased at +1.2V, registers set to default power-up settings,  $T_A$  = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(MAX2822 EV kit,  $V_{CC}$  = +2.7V,  $f_{BB}$  = 1MHz,  $f_{LO}$  = 2437MHz, receive baseband outputs = 500mV<sub>P-P</sub>, transmit baseband inputs = 400mV<sub>P-P</sub>, ICP = +2mA, BWPLL = 45kHz, differential RF input/output matched to 50 $\Omega$  through a balun, baseband input biased at +1.2V, registers set to default power-up settings,  $T_A$  = +25°C, unless otherwise noted.)

PA POWER-DETECTOR OUTPUT VOLTAGE

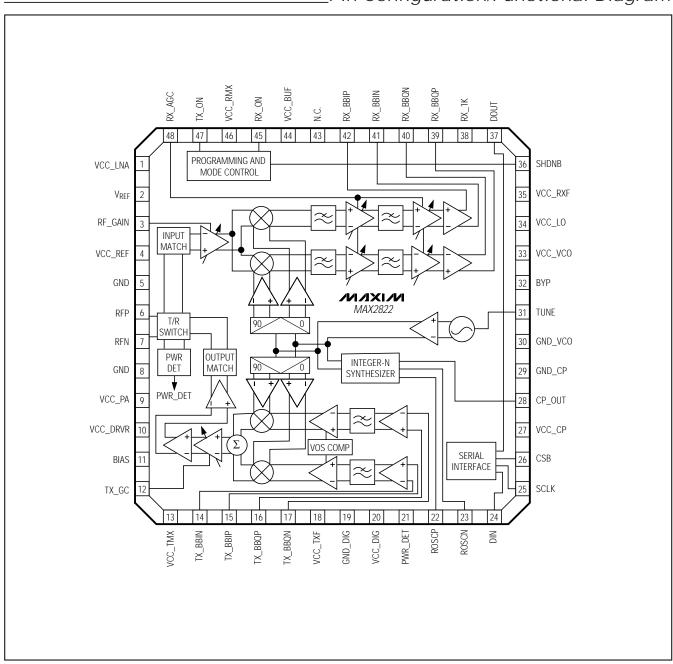

Pin Configuration/Functional Diagram

\_\_\_\_Pin Description

| PIN  | NAME             | FUNCTION                                                                                                                                                                                                |

|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VCC_LNA          | Supply Voltage Connection for LNA. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with other branches.                                          |

| 2    | V <sub>REF</sub> | Voltage Reference Output for Baseband IC. Requires external RF bypass to GND.                                                                                                                           |

| 3    | RF_GAIN          | LNA Gain-Select Logic Input. Logic high for LNA high-gain mode, logic low for LNA low-gain mode.                                                                                                        |

| 4    | VCC_REF          | Supply Voltage for Bias Circuitry and Autotuner. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with other branches.                            |

| 5, 8 | GND              | Ground                                                                                                                                                                                                  |

| 6    | RFP              | RF Balanced I/O Port (Positive). On-chip matched for $100\Omega$ balanced.                                                                                                                              |

| 7    | RFN              | RF Balanced I/O Port (Negative). On-chip matched for $100\Omega$ balanced.                                                                                                                              |

| 9    | VCC_PA           | Supply Voltage Connection for Power Amplifier. Requires external RF bypass to GND.                                                                                                                      |

| 10   | VCC_DRVR         | Supply Voltage Connection for PA Driver. Requires external RF bypass to GND.                                                                                                                            |

| 11   | BIAS             | Precision Bias Resistor Pin. Connect a 12kΩ precision resistor (≤ 2%) to GND.                                                                                                                           |

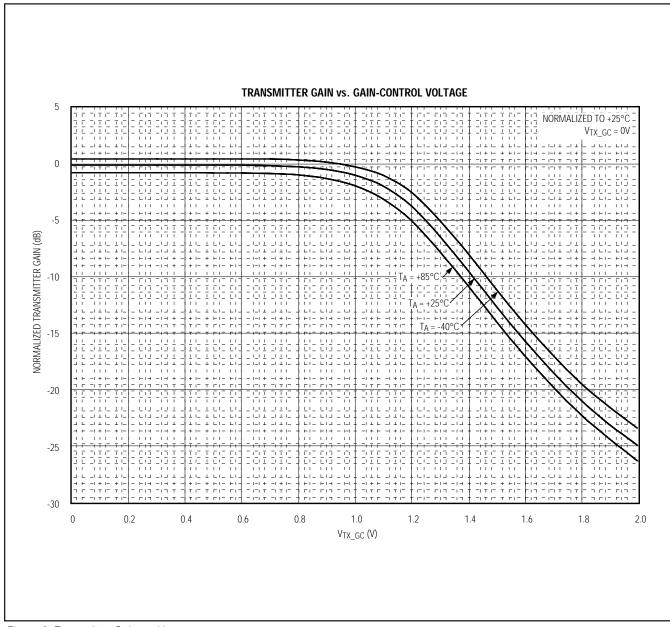

| 12   | TX_GC            | Transmit Gain-Control Input. Analog high-impedance input. Connect directly to baseband IC DAC output. See Figure 3 for transmitter gain vs. gain-control voltage.                                       |

| 13   | VCC_TMX          | Supply Voltage for Transmit Mixer and VGA. Bypass with a capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with other branches.                                  |

| 14   | TX_BBIN          | Transmit Negative In-Phase Baseband Input. Analog high-impedance differential input. Connect directly to baseband IC DAC voltage output. Requires a 1.2V common-mode voltage.                           |

| 15   | TX_BBIP          | Transmit Positive In-Phase Baseband Input. Analog high-impedance differential input. Connect directly to baseband IC DAC voltage output. Requires a 1.2V common-mode voltage.                           |

| 16   | TX_BBQP          | Transmit Positive Quadrature Baseband Input. Analog high-impedance differential input. Connect directly to baseband IC DAC voltage output. Requires a 1.2V common-mode voltage.                         |

| 17   | TX_BBQN          | Transmit Negative Quadrature Baseband Input. Analog high-impedance differential input. Connect directly to baseband IC DAC voltage output. Requires a 1.2V common-mode voltage.                         |

| 18   | VCC_TXF          | Supply Voltage for Transmit Baseband Filter. Bypass with capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with other branches.                                  |

| 19   | GND_DIG          | Digital Ground                                                                                                                                                                                          |

| 20   | VCC_DIG          | Supply Voltage for Digital Circuitry. Bypass with capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with other branches.                                         |

| 21   | PWR_DET          | Transmitter Power-Detector Output                                                                                                                                                                       |

| 22   | ROSCP            | Reference Oscillator Positive Input. Analog high-impedance differential input. DC-coupled. Requires external AC-coupling. Connect an external reference oscillator to this analog input.                |

| 23   | ROSCN            | Reference Oscillator Negative Input. Analog high-impedance differential input. DC-coupled. Requires external AC-coupling. Bypass this analog input to ground with capacitor for single-ended operation. |

| 24   | DIN              | 3-Wire Serial Interface Data Input. Digital high-impedance input. Connect directly to baseband IC serial interface CMOS output (SPI™/QSPI™/MICROWIRE™ compatible).                                      |

| 25   | SCLK             | 3-Wire Serial Interface Clock Input. Digital high-impedance input. Connect this digital input directly to baseband IC serial interface CMOS output (SPI/QSPI/MICROWIRE compatible).                     |

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

\_Pin Description (continued)

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                                                         |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26  | CSB     | 3-Wire Serial Interface Enable Input. Digital high-impedance input. Connect directly to baseband IC serial interface CMOS output (SPI/QSPI/MICROWIRE compatible).                                                                                                                                |

| 27  | VCC_CP  | Supply Voltage for PLL Charge Pump. Bypass with capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with other branches.                                                                                                                                    |

| 28  | CP_OUT  | PLL Charge-Pump Output. Analog high-impedance output. Current source. Connect directly to the PLL loop filter input.                                                                                                                                                                             |

| 29  | GND_CP  | PLL Charge-Pump Ground. Connect to PC board ground plane.                                                                                                                                                                                                                                        |

| 30  | GND_VCO | VCO Ground. Connect to PC board ground plane.                                                                                                                                                                                                                                                    |

| 31  | TUNE    | VCO Frequency Tuning Input. Analog high-impedance voltage input. Connect directly to the PLL loop filter output.                                                                                                                                                                                 |

| 32  | BYP     | VCO Bias Bypass. Bypass with a 2000pF capacitor to ground.                                                                                                                                                                                                                                       |

| 33  | VCC_VCO | Supply Voltage for VCO. Bypass with capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with other branches. <b>Important note:</b> Operate from separate regulated supply voltage.                                                                         |

| 34  | VCC_LO  | Supply Voltage for VCO, LO Buffers, and LO Quadrature Circuitry. Bypass with capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with other branches.                                                                                                       |

| 35  | VCC_RXF | Supply Voltage for Receiver Baseband Filter. Bypass with capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with other branches.                                                                                                                           |

| 36  | SHDNB   | Active-Low Shutdown Input. Digital high-impedance CMOS input. Connect directly to baseband IC mode-control CMOS output. Logic low to disable all device functions. Logic high to enable normal chip operation.                                                                                   |

| 37  | DOUT    | Serial Interface Data Output. Digital CMOS output. Optional connection.                                                                                                                                                                                                                          |

| 38  | RX_1K   | Receiver 1kHz Highpass Bandwidth Control. Digital CMOS input. Connect directly to baseband IC CMOS output. Controls receiver baseband highpass -3dB corner frequency; logic low for 10kHz, logic high for 1kHz. See the <i>Applications Information</i> section for proper use of this function. |

| 39  | RX_BBQP | Receive Positive Quadrature Baseband Output. Analog low-impedance differential buffer output. Connect output directly to baseband ADC input. Internally biased to 1.2V common-mode voltage and can drive loads up to $5k\Omega \parallel 5pF$ .                                                  |

| 40  | RX_BBQN | Receive Negative Quadrature Baseband Output. Analog low-impedance differential buffer output. Connect output directly to baseband ADC input. Internally biased to 1.2V common-mode voltage and can drive loads up to $5k\Omega \parallel 5pF$ .                                                  |

| 41  | RX_BBIN | Receive Negative In-Phase Baseband Output. Analog low-impedance differential buffer output. Connect output directly to baseband ADC input. Internally biased to 1.2V common-mode voltage and can drive loads up to $5k\Omega \parallel 5pF$ .                                                    |

| 42  | RX_BBIP | Receive Positive In-Phase Baseband Output. Analog low-impedance differential buffer output. Connect output directly to baseband ADC input. Internally biased to 1.2V and can drive loads up to $5k\Omega \parallel 5pF$ .                                                                        |

| 43  | N.C.    | No Connection. Make no connections to this pin.                                                                                                                                                                                                                                                  |

| 44  | VCC_BUF | Supply Voltage for Receiver Baseband Buffer. Bypass with capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with other branches.                                                                                                                           |

Pin Description (continued)

| PIN            | NAME    | FUNCTION                                                                                                                                                             |

|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45             | RX_ON   | Receiver-On Control Input. Digital CMOS input. Connect to baseband IC mode-control CMOS output.                                                                      |

| 46             | VCC_RMX | Supply Voltage for Receiver Downconverter. Bypass with capacitor as close to the pin as possible. Do not share the bypass capacitor ground vias with other branches. |

| 47             | TX_ON   | Transmitter-On Control Input. Digital CMOS input. Connect directly to baseband IC mode-control CMOS output.                                                          |

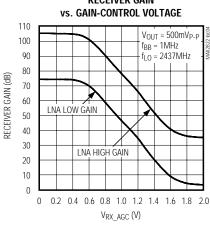

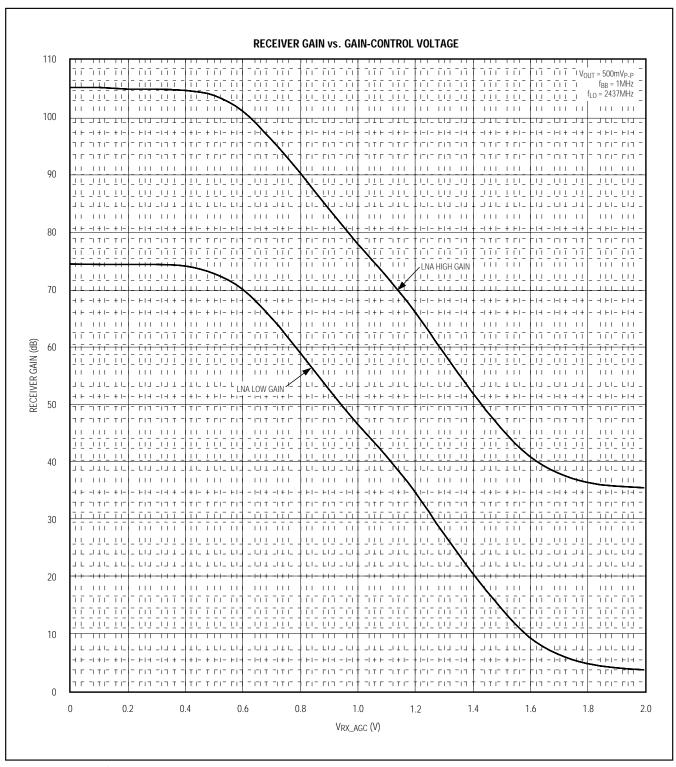

| 48             | RX_AGC  | Receive AGC Control. Analog high-impedance input. Connect directly to baseband IC DAC voltage output. See Figure 2 for gain vs. V <sub>RX_AGC</sub> .                |

| Exposed Paddle | GND     | DC and AC Ground Return for IC. Connect to PC board ground plane using multiple vias.                                                                                |

### **Table 1. Operating Mode Truth Table**

| ODEDATING MODE | MODE- | CONTROLI | NPUTS | CIRCUIT BLOCK STATES |         |                |  |

|----------------|-------|----------|-------|----------------------|---------|----------------|--|

| OPERATING MODE | SHDNB | TX_ON    | RX_ON | RX_PATH              | TX_PATH | PLL/VCO/LO GEN |  |

| Shutdown       | 0     | Χ        | Χ     | OFF                  | OFF     | OFF            |  |

| Standby        | 1     | 0        | 0     | OFF                  | OFF     | ON             |  |

| Receive        | 1     | 0        | 1     | ON                   | OFF     | ON             |  |

| Transmit       | 1     | 1        | 0     | OFF                  | ON      | ON             |  |

| Not Allowed    | 1     | 1        | 1     | _                    | _       | _              |  |

### \_Detailed Description

#### Operating Modes

The MAX2822 has four primary modes of operation: shutdown, standby, receive active, and transmit active. The modes are controlled by the digital inputs SHDNB, TX\_ON, and RX\_ON. Table 1 shows the operating mode vs. the digital mode-control inputs.

#### Shutdown Mode

Shutdown mode is enabled by driving SHDNB low. In shutdown mode, all circuit blocks are powered down, except for the serial interface circuitry. While the device is in shutdown, the serial interface registers can still be loaded by applying  $V_{CC}$  to the digital supply voltage (VCC\_DIG). All previously programmed register values are preserved during the shutdown mode, as long as VCC\_DIG is applied.

#### Standby Mode

Standby mode is achieved by driving SHDNB high, and RX\_ON and TX\_ON low. In standby mode, the PLL, VCO, LO generation circuitry, and filter autotuner are powered on by default. The standby mode is intended to provide time for the slower-settling circuitry (PLL and autotuner) to turn on and settle to the correct frequency before making Rx or Tx active. The 3-wire serial inter-

face is active and can load register values at any time. Refer to the serial interface specifications for details.

#### Receive Mode

Receive mode is enabled by driving SHDNB high, RX\_ON high, and TX\_ON low. In receive mode, all receive circuit blocks are powered on and all VCO, PLL, and autotuner circuits are powered on. None of the transmit path blocks are active in this mode. Although the receiver blocks turn on quickly, the DC offset nulling requires ~10µs to settle. The receiver signal path is ready ~10µs after a low-to-high transition on RX\_ON.

#### Transmit Mode

Transmit mode is enabled by driving the digital inputs SHDNB high, RX\_ON low, and TX\_ON high. In transmit mode, all transmit circuit blocks are powered on and all VCO, PLL, and autotuner circuits are powered on. None of the receive path blocks are active in this mode. Although the transmitter blocks turn on quickly, the baseband DC offset calibration requires  $\sim\!2.2\mu s$  to complete. In addition, the Tx driver amplifier is ramped from the low-gain state (minimum RF output) to highgain state (peak RF output) over the next  $1\mu s$  to  $2\mu s$ . Also, the LO takes a few microseconds after TX\_ON rises to resettle. The transmit signal path is ready  $\sim\!5\mu s$  after a low-to-high transition on TX\_ON.

### Programmable Registers

The MAX2822 contains programmable registers to control various modes of operation for the major circuit blocks. The registers can be programmed through the 3-wire SPI/QSPI/MICROWIRE-compatible serial port. The MAX2822 includes five programmable registers:

- 1) Block-enable register

- 2) Synthesizer register

- 3) Channel frequency register

- 4) Receiver settings register

- 5) Transmitter settings register

Each register consists of 16 bits. The four most significant bits (MSBs) are the register's address. The twelve least significant bits (LSBs) are used for register data. Table 2 summarizes the register configuration. A detailed description of each register is provided in Tables 4–8

Data bits are shifted in the MSB first. The data sent to the MAX2822, in 16-bit words, is framed by CSB. When CSB is low, the clock is active and data is shifted with the rising edge of the clock. When CSB transitions to high, the shift register is latched into the register selected by the contents of the address bits. Only the last 16 bits shifted into the MAX2822 are retained in the shift register. No check is made on the number of clock pulses. Figure 1 documents the serial interface timing for the MAX2822.

#### Power-Up Default States

The MAX2822 provides power-up loading of default states for each of the registers. The states are loaded on a VCC\_DIG supply voltage transition from 0V to  $V_{CC}$ . The default values are retained until reprogrammed through the serial interface or the power-supply voltage is taken to 0V. The default state of each register is described in Table 3. **Note:** Putting the IC in shutdown mode does not change the contents of the programming registers.

#### Block-Enable Register

The block-enable register permits individual control of the enable state for each major circuit block in the MAX2822. The actual enable condition of the circuit block is a logical function of the block-enable bit setting and other control input states. Table 4 documents the logical definition of state for each major circuit block.

#### Synthesizer Register

The synthesizer register (SYNTH) controls the reference frequency divider and charge-pump current of the PLL. See Table 5 for a description of the bit settings.

#### Channel Frequency Register

The channel frequency register (CHANNEL) sets the RF carrier frequency for the MAX2822. The channel is programmed as a number from 0 to 99. The actual frequency is 2400 + channel in MHz. The default setting is 37 for 2437MHz. See Table 6 for a description of the bit settings.

Figure 1. MAX2822 Serial Interface Timing Diagram

### Receiver Settings Register

The receiver settings register (RECEIVE) controls the receive filter -3dB corner frequency and VGA DC offset nulling parameters. The defaults are intended to provide proper operation. However, the filter frequency and detector can be modified if desired. Do not reprogram VGA DC offset nulling parameters. These settings were optimized during development. See Table 7 for a description of the bit settings.

Transmitter Settings Register

The transmitter settings register (TRANSMIT) provides a 6-bit digital control of the PA bias and 1-bit enable for the transmit power detector. Bits D0:D3 control the PA output stage bias current (0000 lowest, 1111 highest) and PA driver stage bias current (00 lowest, 11 highest). The appropriate values vs. target output power are given in Table 9. The detector enable bit allows independent turn-on of the detector for testing purposes.

**Table 2. Programming Register Definition Summary**

|                  | 4 ADDRESS BITS |    |    |    |     | 12 DATA BITS |     |     |     |     |     |     |     |     |     |     |

|------------------|----------------|----|----|----|-----|--------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| REGISTER<br>NAME | А3             | A2 | A1 | A0 | D11 | D10          | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| NAME             | MSB            | 15 | 14 | 13 | 12  | 11           | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | LSB |

| ENABLE           | 0              | 0  | 0  | 1  | E11 | E10          | E9  | E8  | E7  | E6  | E5  | E4  | E3  | E2  | E1  | E0  |

| SYNTH            | 0              | 0  | 1  | 0  | Χ   | Χ            | Χ   | Χ   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | R0  |

| CHANNEL          | 0              | 0  | 1  | 1  | Χ   | Χ            | Χ   | Χ   | Χ   | CF6 | CF5 | CF4 | CF3 | CF2 | CF1 | CF0 |

| RECEIVE          | 0              | 1  | 0  | 0  | 2C2 | 2C1          | 2C0 | 1C2 | 1C1 | 1C0 | DL1 | DL0 | SF  | BW2 | BW1 | BW0 |

| TRANSMIT         | 0              | 1  | 0  | 1  | Χ   | Χ            | Χ   | Χ   | Χ   | DE  | DR1 | DR0 | PA3 | PA2 | PA1 | PA0 |

X = Don't care.

**Table 3. Register Power-Up Defaults States**

| REGISTER | ADDRESS             | DEFAULT        | FUNCTION                                                                              |

|----------|---------------------|----------------|---------------------------------------------------------------------------------------|

| ENABLE   | 0001                | 0000 0001 1110 | Block-Enable Control Settings (E)                                                     |

| SYNTH    | 0010                | 0000 0100 0000 | Synthesizer Settings: • Reference frequency (R)                                       |

| CHANNEL  | 0011 0000 0010 0101 |                | Channel frequency settings (CF)                                                       |

| RECEIVE  | 0100                | 1111 1101 0010 | Receiver Settings:  - 3dB lowpass filter bandwidth (BW)  Detector midpoint level (DL) |

| TRANSMIT | 0101                | 0000 0010 1101 | Transmit Settings:  PA bias (PA)  PA driver bias (D)  PA driver enable (DE)           |

Table 4. Block-Enable Register (ENABLE)

| ADDRESS | DATA BIT | CONTENT | DEFAULT | DESCRIPTION AND LOGICAL DEFINITION                                                           |

|---------|----------|---------|---------|----------------------------------------------------------------------------------------------|

|         | D11      | E(11)   | 0       | Reserved                                                                                     |

|         | D10      | E(10)   | 0       | PA Bias-Control Enable (PAB_EN) PAB_EN = SHDNB • (E(10) + TX_ON)                             |

|         | D9       | E(9)    | 0       | Transmit Baseband Filters Enable (TXFLT_EN)  TXFLT_EN = SHDNB • (E(9) + TX_ON)               |

|         | D8       | E(8)    | 0       | Tx Upconverter + VGA + Driver Amp Enable (TXUVD_EN) TXUVD_EN = SHDNB • (E(8) + TX_ON)        |

|         | D7       | E(7)    | 0       | Reserved                                                                                     |

|         | D6       | E(6)    | 0       | Rx Downconverter + Filters + AGC Amps Enable (RXDFA_EN)<br>RXDFA_EN = SHDNB • (E(6) + RX_ON) |

| 0001    | D5       | E(5)    | 0       | Receive LNA Enable (RXLNA_EN)<br>RXLNA_EN = SHDNB • (E(5) + RX_ON )                          |

|         | D4       | E(4)    | 1       | Autotuner Enable (AT_EN)<br>AT_EN = SHDNB • (E(4) + RX_ON + TX_ON)                           |

|         | D3       | E(3)    | 1       | PLL Charge-Pump Enable (CP_EN) CP_EN = SHDNB • E(3)                                          |

|         | D2       | E(2)    | 1       | PLL Enable (PLL_EN) PLL_EN = SHDNB • E(2)                                                    |

|         | D1       | E(1)    | 1       | VCO Enable (VCO_EN) VCO_EN = SHDNB • E(1)                                                    |

|         | D0       | E(0)    | 0       | Reserved                                                                                     |

### **Table 5. Synthesizer Settings Register (SYNTH)**

| ADDRESS | DATA BIT | CONTENT | DEFAULT | DESCRIPTION                                                      |  |

|---------|----------|---------|---------|------------------------------------------------------------------|--|

|         | D11:D8 X |         | 0000    | Reserved                                                         |  |

|         | D7       | _       | 0       | Must be 0 for proper operation                                   |  |

| 0010    | D6       | _       | 1       | Must be 1 for proper operation                                   |  |

| 0010    | D5:D0    | R(5:0)  | 000000  | Reference Frequency Divider:  • 000000 = 22MHz  • 000001 = 44MHz |  |

### **Table 6. Channel Frequency Register (CHANNEL)**

| ADDRESS | DATA BIT | CONTENT | DEFAULT | DESCRIPTION                                                                                                  |

|---------|----------|---------|---------|--------------------------------------------------------------------------------------------------------------|

|         | D11:D7   | X       | 00000   | Reserved                                                                                                     |

| 0011    | D6:D0    | CF(6:0) | 0100101 | Channel Frequency Select: f <sub>LO</sub> = (2400 + CF(6:0))MHz  • 0000000 = 2400MHz  • 0000001 = 2401MHz  • |

Table 7. Receiver Settings Register (RECEIVE)

| ADDRESS | DATA BIT | CONTENT | DEFAULT  | DESCRIPTION                                                                                                                                                         |

|---------|----------|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | D11:D4   | _       | 11111111 | Must be 11111111 for proper operation                                                                                                                               |

|         | D3       | _       | 0        | Must be 0 for proper operation                                                                                                                                      |

| 0100    | D2:D0    | BW(2:0) | 010      | Receive Filter -3dB Frequency Select (frequencies are approximate):  • 000 = 8.5MHz  • 001 = 8.0MHz  • 010 = 7.5MHz  • 011 = 7.0MHz  • 100 = 6.5MHz  • 101 = 6.0MHz |

Table 8. Transmit Settings Register (TRANSMIT)

| ADDRESS | DATA BIT     | CONTENT | DEFAULT | DESCRIPTION                                                                 |

|---------|--------------|---------|---------|-----------------------------------------------------------------------------|

|         | D11:D7       | Χ       | X       | Reserved                                                                    |

|         | D6           | DE      | 0       | Transmit Power-Detector Enable                                              |

| 0101    | D5:D4 D(1:0) |         | 10      | PA Predriver Bias:  11 = Highest predriver bias  00 = Lowest predriver bias |

|         | D3:D0        | PA(3:0) | 1101    | PA Bias Select:  1111 = Highest PA bias  0000 = Lowest PA bias              |

### \_Applications Information

#### RF I/O and Tx/Rx Switching

The MAX2822 completely integrates the power amplifier, low-noise amplifier, transmit/receive (Tx/Rx) switch, as well as all matching components, to allow direct connection to the antenna through a balun or combination balun/filter. This single RF interface (RFP and RFN) is internally matched to form a  $100\Omega$  balanced port—no additional components are required to impedance-match the I/O. Most applications employ a  $100\Omega$  balanced to  $50\Omega$  single-ended RF bandpass filter between the RF port and the antenna.

### Receive Path

#### LNA

Given the LNA input is internally matched to  $100\Omega$  differential, it is important that the differential pair from RFP/RFN to the RF BPF be an identical pair of transmission lines to present a  $100\Omega$  differential impedance to the balun. Identical line layout on the differential input traces is important in maintaining good IP2 performance and RF common-mode noise rejection.

The MAX2822 has two LNA gain modes that are digitally controlled by the logic signal applied to RF\_GAIN. RF\_GAIN high enables the high-gain mode, and RF\_GAIN low enables the low-gain mode. The LNA gain step is nominally 32dB. In most applications, RF\_GAIN is connected directly to a CMOS output of the baseband IC, and the baseband IC controls the state of the LNA gain based on the detected signal amplitude.

#### Receiver Baseband Lowpass Filtering

The MAX2822 on-chip receive lowpass filters provide the steep filtering necessary to attenuate the out-ofband (> 11MHz) interfering signals to sufficiently low levels to preserve receiver sensitivity. The filter frequency response is precisely controlled on-chip and does not require user adjustment. However, a provision is made to permit the -3dB corner frequency and entire response to be slightly shifted up or down in frequency. This is intended to offer some flexibility in trading off adjacent channel rejection vs. passband distortion. The filter -3dB frequency is programmed through the serial interface. The specific bit setting vs. -3dB frequency is shown in Table 7. The typical receive baseband filter gain vs. frequency profile is shown in the Typical Operating Characteristics. Default filter settings are optimal (-3dB corner at 7.5MHz)—this provides the best trade-off between noise filtering and baseband distortion to obtain best receive sensitivity. No user adjustment is required.

#### Receive Gain Control

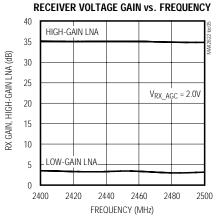

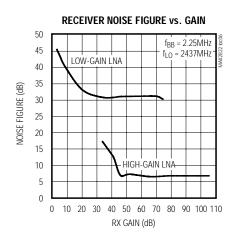

The MAX2822 receive path gain is varied through an external voltage applied to the pin RX\_AGC. Maximum gain is at VRX\_AGC = 0V and minimum gain is at VRX\_AGC = 2V. The RX\_AGC input is a high-impedance analog input designed for direct connection to the RX\_AGC DAC output of the baseband IC. The gain-control range, which is continuously variable, is typically 70dB. The gain-control characteristic is shown in the *Typical Operating Characteristics* Receiver Voltage Gain vs. Gain-Control Voltage graph and again as a full-page plot in Figure 2.

Some local noise filtering through a simple RC network at the input is permissible. However, the time constant of this network should be kept sufficiently low to not limit the desired response time of the Rx gain-control function.

#### Receiver Baseband Amplifier Outputs

The MAX2822 receiver baseband outputs (RX\_BBIP, RX\_BBIN, RX\_BBQP, and RX\_BBQN) are differential low-impedance buffer outputs. The outputs are designed to be directly connected (DC-coupled) to the in-phase (I) and quadrature-phase (Q) ADC inputs of the baseband IC. The Rx I/Q outputs are internally biased to +1.2V common-mode voltage. The outputs are capable of driving loads up to  $5k\Omega$  || 5pF with the full bandwidth baseband signals at a differential amplitude of  $500mV_{P-P}$ .

Proper board layout is essential to maintain good balance between I/Q traces. This provides good quadrature phase accuracy.

Transmit Path

### Transmitter Baseband Inputs

The MAX2822 transmitter baseband inputs (TX\_BBIP, TX\_BBIN, TX\_BBQP, and TX\_BBQN) are high-impedance differential analog inputs. The inputs are designed to be directly connected (DC-coupled) to the in-phase (I) and quadrature-phase (Q) DAC outputs of the baseband IC. The inputs must be externally biased to +1.2V common-mode voltage. Typically, the DAC outputs are current outputs with external resistor loads to ground. I and Q are driven by a 400mVP-P (nominal) differential baseband signal.

Proper board layout is essential to maintain good balance between I/Q traces. This provides good quadrature phase accuracy by maintaining equal parasitic capacitance on the lines. In addition, it is important not to expose the Tx I/Q circuit board traces going from the digital baseband IC to the MAX2822. The lines should be shielded on an inner layer to prevent coupling of RF to these Tx I/Q inputs and possible envelope demodulation of the RF signal.

#### Transmit Path Baseband Lowpass Filtering

The MAX2822 on-chip transmit lowpass filters provide the filtering necessary to attenuate the unwanted higher-frequency spurious signal content that arises from the DAC clock feedthrough and sampling images. In addition, the filter provides additional attenuation of the second sidelobe of signal spectrum. The filter frequency response is set on-chip. No user adjustment or programming is required. The Typical Gain vs. Frequency profile is shown in the *Typical Operating Characteristics*.

#### Transmitter DC Offset Calibration

In a zero-IF system, the DC offset of the Tx baseband signal path must be reduced to as near zero as possible to minimize LO leakage at the RF output. Given that the amplifier stages, baseband filters, and Tx DAC possess some finite DC offset that is too large for the required LO leakage specification, it is necessary to null the DC offset. The MAX2822 accomplishes this through an on-chip calibration sequence. During this sequence, the net Tx baseband signal path offsets are sampled and cancelled in the baseband amplifiers. This calibration occurs in the first  $\sim\!2.2\mu s$  after TX\_ON is taken high. The calibration corrects for any DC offset from the DAC, but this DC offset must not change after this cal sequence. Be sure the DAC outputs are set to zero state before taking TX\_ON high.

Figure 2. Receiver Gain vs. VRX\_AGC

Figure 3. Transmitter Gain vs. VTX\_GC

The DC offset circuitry uses a sample-and-hold technique to accomplish this DC offset nulling. Over time (many seconds), the sample-and-hold storage cap slowly discharges, causing the DC value at the Tx BB to slowly increase, and the LO level in the RF output to slowly increase. This can be seen on the bench during evaluation, when the transceiver is left in Tx mode for more than 30 to 60 seconds. Even under worst-case conditions, however, the DC null value changes very little during the longest 802.11b Tx burst of 20ms—LO suppression in 802.11b applications always remains around the -30dBc typical level specified in the *Electrical Characteristics* table.

#### **Transmit Gain Control**