# TECHNICAL MANUAL

LSI53C895 PCI to Ultra2 SCSI I/O Processor with LVD Link<sup>™</sup> Universal Transceivers

Version 3.2

December 2000

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

LSI Logic products are not intended for use in life-support appliances, devices, or systems. Use of any LSI Logic product in such applications without written consent of the appropriate LSI Logic officer is prohibited.

Document DB14-000112-01, Second Edition (December 2000) This document describes the LSI Logic LSI53C895 PCI to Ultra2 SCSI I/O Processor with LVD Link Universal Transceivers and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

#### To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1996–2000 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, SCRIPTS, LVD Link, and TolerANT are registered trademarks or trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

# Preface

This book is the primary reference and technical manual for the LSI53C895 PCI to Ultra2 SCSI I/O Processor with LVD Link<sup>™</sup> Universal Transceivers. It contains a complete functional description for the product and includes complete physical and electrical specifications.

This technical manual assumes the user is familiar with the current and proposed standards for SCSI and PCI. For additional background information on these topics, please refer to the list of reference materials provided below.

#### Audience

This document was prepared for system designers and programmers who are using this device to design an Ultra2 SCSI port for PCI-based personal computers, workstations, servers, or embedded applications.

### Organization

This document has the following chapters and appendixes:

- Chapter 1, Introduction contains the general description about the LSI53C895.

- Chapter 2, Functional Description contains details about the three functional blocks: the SCSI Core, the DMA Core, and the SCRIPTS processor.

- Chapter 3, PCI Functional Description contains the PCI bus commands and functions supported.

- Chapter 4, **Signal Descriptions** contains information about the signal definitions using tables and illustrations.

- Chapter 5, **Registers** contains descriptions of the PCI registers and the LSI53C895 operating registers.

- Chapter 6, SCSI SCRIPTS Instruction Set contains detailed information about utilizing SCSI SCRIPTS mode.

- Chapter 7, Electrical Characteristics contains information pertaining to DC and AC Characteristics for the LSI53C895.

- Appendix A, Register Summary contains a quick reference to the registers used for the LSI53C895.

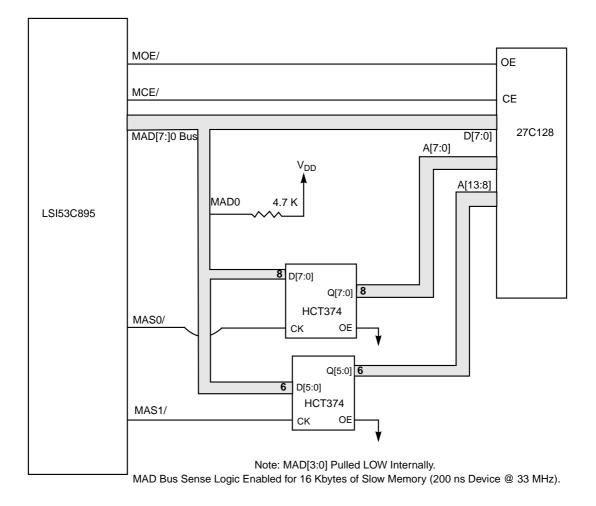

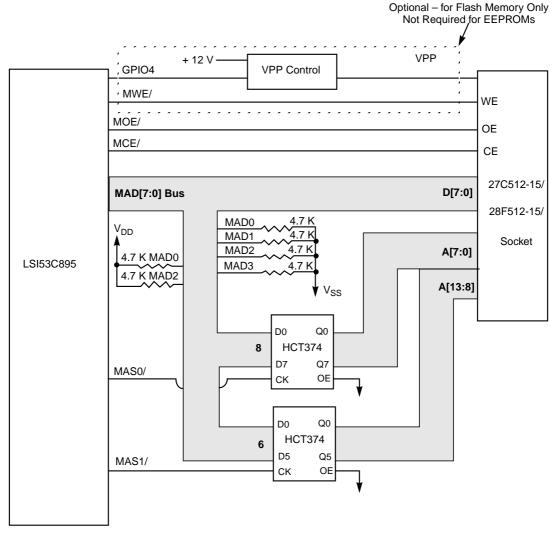

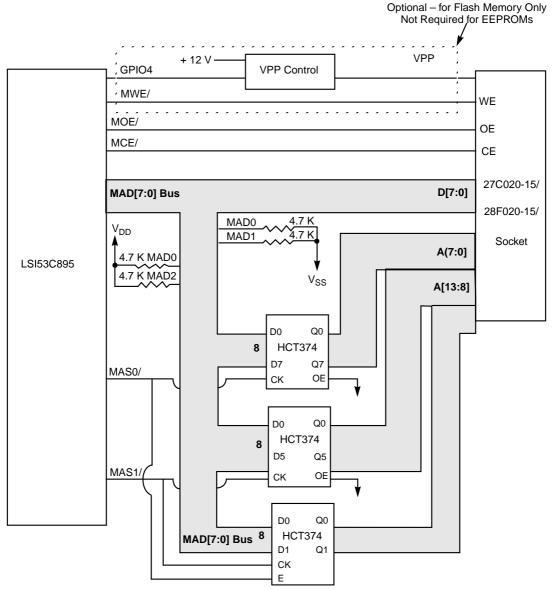

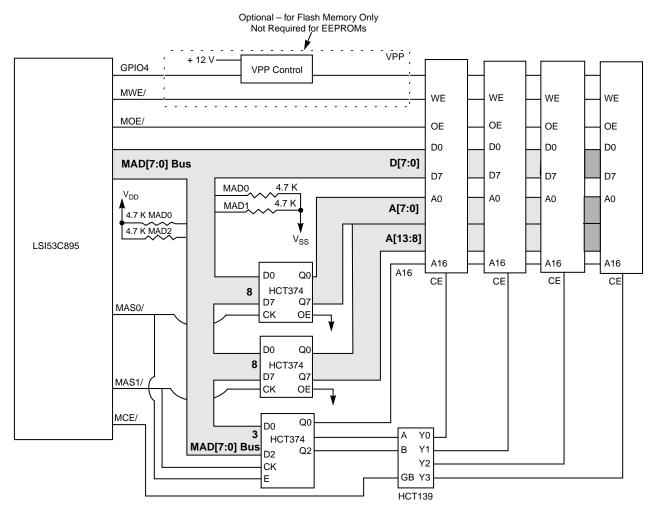

- Appendix B, External Memory Interface Diagram Examples contains four diagram examples pertaining to the interface of the external memory.

- Appendix C, Circuit Board Layout Issues provides details concerning signals and other considerations specific to the LSI53C895.

#### **Related Publications**

For background information, please contact:

#### ANSI

11 West 42nd Street New York, NY 10036 (212) 642-4900 Ask for document number X3.131-1994 (SCSI-2)

#### **Global Engineering Documents**

15 Inverness Way East Englewood, CO 80112 (800) 854-7179 or (303) 7956 (outside U.S.) FAX (303) 397-2740 Ask for document number X3.131-1994 (SCSI-2) or X3.253 (*SCSI-3 Parallel Interface*)

#### **ENDL** Publications

14426 Black Walnut Court

Saratoga, CA 95070

(408) 867-6642

Document names: SCSI Bench Reference, SCSI Encyclopedia, SCSI Tutor

### **Prentice Hall**

113 Sylvan Avenue

Englewood Cliffs, NJ 07632

(800) 947-7700

Ask for document number ISBN 0-13-796855-8, SCSI: Understanding the Small Computer System Interface

### LSI Logic World Wide Web Home Page

www.lsilogic.com

SCSI SCRIPTS<sup>™</sup> Processors Programming Guide, Version 2.2, Order number S14044.A

#### **PCI Special Interest Group**

PCI Local Bus Specification, Revision 2.1 2575 N.E. Katherine Hillsboro, OR 97214 (800) 433-5177; (503) 693-6232 (International); FAX (503) 693-8344

#### **Conventions Used in This Manual**

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

## **Revision Record**

| Revision | Date  | Remarks                                                                                                                                                                                                                                                                                                |

|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 7/96  | Initial release.                                                                                                                                                                                                                                                                                       |

| 2.0      | 1/97  | Added serial EEPROM interface; changed operation of parallel EPROM interface; added information on Ultra2 SCSI termination; added LVD electrical specifications and Ultra2 SCSI timings; added PCI configuration registers for Subsystem ID and Subsystem Vendor ID; pinout/pin numbering corrections. |

| 3.0      | 9/98  | Merged addendum; merged SEN892<br>(DIFFSENS) in Chapter 2; Chapter 3 - added 292-BGA figure/tables<br>and updated MAD[3:1] signals;Chapter 7 - substituted source and sink<br>values, and changed other values. Merged SEN893 and SEN898 into<br>Appendix D.                                           |

| 3.1      | 12/99 | LSI Logic formats applied. Changes to Chapter 4 regarding PBGA from 292 to 272. Updated Chapter 6, SCSI SCRIPTS with current information.                                                                                                                                                              |

| 3.2      | 12/00 | All product names changed from SYM to LSI.                                                                                                                                                                                                                                                             |

# Contents

| Chapter 1 | Introduction           |         |                                                   |              |  |

|-----------|------------------------|---------|---------------------------------------------------|--------------|--|

|           | 1.1                    | Genera  | al Description                                    | 1-1          |  |

|           |                        | 1.1.1   | New Features in the LSI53C895                     | 1-2          |  |

|           | 1.2                    | Benefit | s of LVD Link                                     | 1-3          |  |

|           | 1.3                    | Benefit | s of Ultra2 SCSI                                  | 1-4          |  |

|           | 1.4                    | TolerAl | NT <sup>®</sup> Technology                        | 1-4          |  |

|           | 1.5                    | LSI53C  | C895 Benefits Summary                             | 1-5          |  |

|           |                        | 1.5.1   | SCSI Performance                                  | 1-5          |  |

|           |                        | 1.5.2   | PCI Performance                                   | 1-6          |  |

|           |                        | 1.5.3   | Integration                                       | 1-7          |  |

|           |                        | 1.5.4   | Ease of Use                                       | 1-7          |  |

|           |                        | 1.5.5   | Flexibility                                       | 1-8          |  |

|           |                        | 1.5.6   | Reliability                                       | 1-8          |  |

|           |                        | 1.5.7   | Testability                                       | 1-9          |  |

| Chapter 2 | Functional Description |         |                                                   |              |  |

|           | 2.1                    | SCSI (  | Core                                              | 2-2          |  |

|           | 2.2                    | DMA C   | Core                                              | 2-2          |  |

|           |                        | 2.2.1   | DMA FIFO                                          | 2-3          |  |

|           | 2.3                    | SCRIP   | TS Processor                                      | 2-7          |  |

|           |                        | 2.3.1   | Internal SCRIPTS RAM                              | 2-8          |  |

|           | 2.4                    | Prefeto | hing SCRIPTS Instructions                         | 2-8          |  |

|           |                        | 2.4.1   | Op Code Fetch Burst Capability                    | 2-10         |  |

|           | 2.5                    | Design  | ing an Ultra2 SCSI System                         | 2-10         |  |

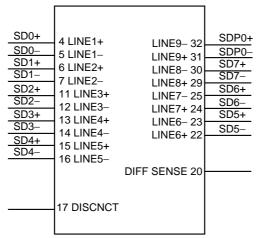

|           |                        | 2.5.1   | Using the SCSI Clock Quadrupler                   | 2-11         |  |

|           | 0.0                    | L SI530 | C895 Interfaces                                   | 2-11         |  |

|           | 2.6                    | 201000  |                                                   |              |  |

|           | 2.6                    | 2.6.1   | Parallel ROM Interface                            | 2-11         |  |

|           | 2.6                    |         | Parallel ROM Interface<br>Serial EEPROM Interface | 2-11<br>2-13 |  |

|           | 2.6                    | 2.6.1   |                                                   |              |  |

|           | 2.7   | LSI53C   | 895 Modes                                | 2-20 |

|-----------|-------|----------|------------------------------------------|------|

|           |       | 2.7.1    | PCI Cache Mode                           | 2-20 |

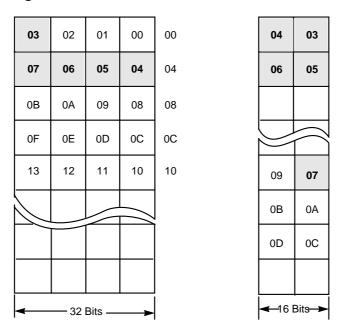

|           |       | 2.7.2    | Big and Little Endian Modes              | 2-20 |

|           |       | 2.7.3    | Loopback Mode                            | 2-22 |

|           | 2.8   | Parity C | Options                                  | 2-22 |

|           |       | 2.8.1    | SCSI Termination                         | 2-24 |

|           |       | 2.8.2    | System Engineering Note                  | 2-25 |

|           |       | 2.8.3    | (Re)Select During (Re)Selection          | 2-28 |

|           | 2.9   | Synchro  | onous Operation                          | 2-28 |

|           |       | 2.9.1    | Determining the Data Transfer Rate       | 2-29 |

|           |       | 2.9.2    | Ultra2 SCSI Synchronous Data Transfers   | 2-29 |

|           | 2.10  | Interrup | ot Handling                              | 2-32 |

|           |       | 2.10.1   | Polling and Hardware Interrupts          | 2-32 |

|           |       | 2.10.2   | Registers                                | 2-32 |

|           |       | 2.10.3   | Fatal vs. Nonfatal Interrupts            | 2-34 |

|           |       | 2.10.4   | Masking                                  | 2-35 |

|           |       | 2.10.5   | Stacked Interrupts                       | 2-36 |

|           |       | 2.10.6   | Halting in an Orderly Fashion            | 2-37 |

|           |       | 2.10.7   | Sample Interrupt Service Routine         | 2-38 |

|           | 2.11  | Chaine   | d Block Moves                            | 2-39 |

|           |       | 2.11.1   | Wide SCSI Send Bit (WSS)                 | 2-40 |

|           |       | 2.11.2   | Wide SCSI Receive Bit (WSR)              | 2-41 |

|           |       | 2.11.3   | SCSI Wide Residue (SWIDE) Register       | 2-41 |

|           |       | 2.11.4   | SCSI Output Data Latch (SODL) Register   | 2-41 |

|           |       | 2.11.5   | Chained Block Move SCRIPTS Instruction   | 2-42 |

| Chapter 3 | PCI I | Function | al Description                           |      |

|           | 3.1   | PCI Ad   | dressing                                 | 3-1  |

|           | 3.2   | PCI Bu   | s Commands and Functions Supported       | 3-2  |

|           | 3.3   |          | che Mode                                 | 3-4  |

|           |       | 3.3.1    | Support for PCI Cache Line Size Register | 3-4  |

|           |       | 3.3.2    | Selection of Cache Line Size             | 3-4  |

|           |       | 3.3.3    | Alignment                                | 3-4  |

|           |       | 3.3.4    | Memory Move Misalignment                 | 3-5  |

|           |       | 3.3.5    | Memory Write and Invalidate Command      | 3-6  |

|           |       | 3.3.6    | Memory Read Multiple Command             | 3-8  |

|           | 3.4   |          | iration Registers                        | 3-10 |

|           |       | •        |                                          |      |

| Chapter 4 | Sign                                     | al Descr | iptions                                |      |

|-----------|------------------------------------------|----------|----------------------------------------|------|

|           | 4.1 Voltage Capabilities and Limitations |          |                                        | 4-3  |

|           | 4.2                                      | Interna  | I Pull-ups on LSI53C895 Pins           | 4-4  |

|           | 4.3                                      | Pin De   | scriptions                             | 4-5  |

| Chapter 5 | Regi                                     | sters    |                                        |      |

|           | 5.1                                      | PCI Co   | onfiguration Registers                 | 5-1  |

|           | 5.2                                      | SCSI F   | Registers                              | 5-15 |

| Chapter 6 | SCS                                      |          | TS Instruction Set                     |      |

|           | 6.1                                      | Low-Le   | evel Register Interface Mode           | 6-2  |

|           | 6.2                                      | High-L   | evel SCSI SCRIPTS Mode                 | 6-2  |

|           |                                          | 6.2.1    | Sample Operation                       | 6-3  |

|           | 6.3                                      | Block I  | Move Instruction                       | 6-6  |

|           |                                          | 6.3.1    | First Dword                            | 6-6  |

|           |                                          | 6.3.2    | Second Dword                           | 6-12 |

|           | 6.4                                      | I/O Ins  | truction                               | 6-13 |

|           |                                          | 6.4.1    | First Dword                            | 6-13 |

|           |                                          | 6.4.2    | Second Dword                           | 6-21 |

|           | 6.5                                      | Read/V   | Vrite Instructions                     | 6-22 |

|           |                                          | 6.5.1    | First Dword                            | 6-22 |

|           |                                          | 6.5.2    | Second Dword                           | 6-23 |

|           |                                          | 6.5.3    | Read-Modify-Write Cycles               | 6-23 |

|           |                                          | 6.5.4    | Move To/From SFBR Cycles               | 6-24 |

|           | 6.6                                      | Transfe  | er Control Instruction                 | 6-26 |

|           |                                          | 6.6.1    | First Dword                            | 6-26 |

|           |                                          | 6.6.2    | Second Dword                           | 6-32 |

|           | 6.7                                      | Memor    | y Move Instructions                    | 6-33 |

|           |                                          | 6.7.1    | First Dword                            | 6-34 |

|           |                                          | 6.7.2    | Read/Write System Memory from a SCRIPT | 6-34 |

|           |                                          | 6.7.3    | Second Dword                           | 6-35 |

|           |                                          | 6.7.4    | Third Dword                            | 6-35 |

|           | 6.8                                      | Load a   | nd Store Instructions                  | 6-36 |

|           |                                          | 6.8.1    | First Dword                            | 6-37 |

|           |                                          | 6.8.2    | Second Dword                           | 6-38 |

|           |                                          | 6.8.3    | Third Dword                            | 6-38 |

| Chapter 7  | Electrical Characteristics |           |                                          |      |  |

|------------|----------------------------|-----------|------------------------------------------|------|--|

| -          | 7.1                        | DC Cha    | racteristics                             | 7-1  |  |

|            | 7.2                        | 3.3 Volt  | PCI DC Characteristics                   | 7-7  |  |

|            | 7.3                        | TolerAN   | T Technology Electrical Characteristics  | 7-8  |  |

|            | 7.4                        | AC Cha    | racteristics                             | 7-12 |  |

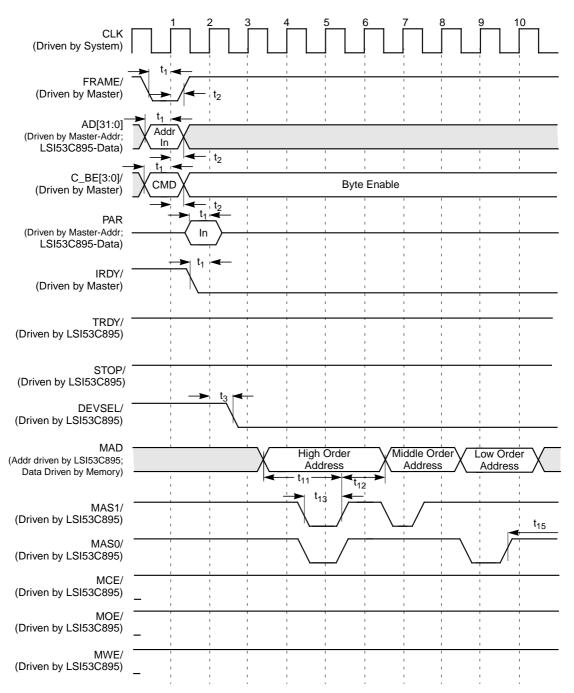

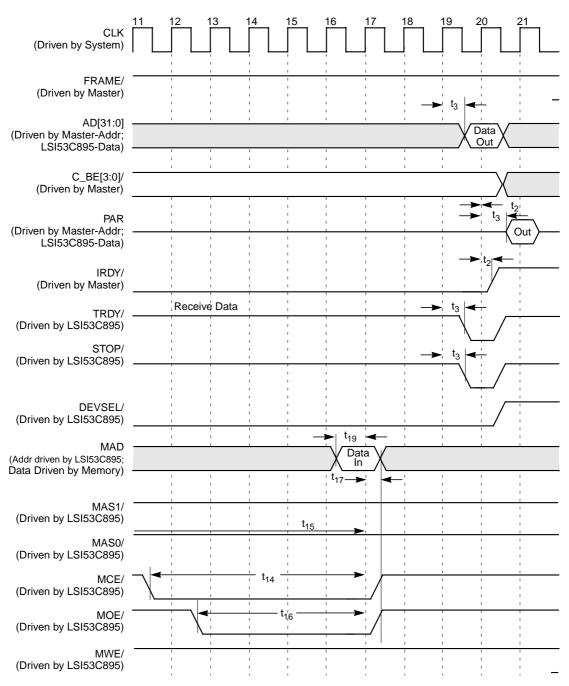

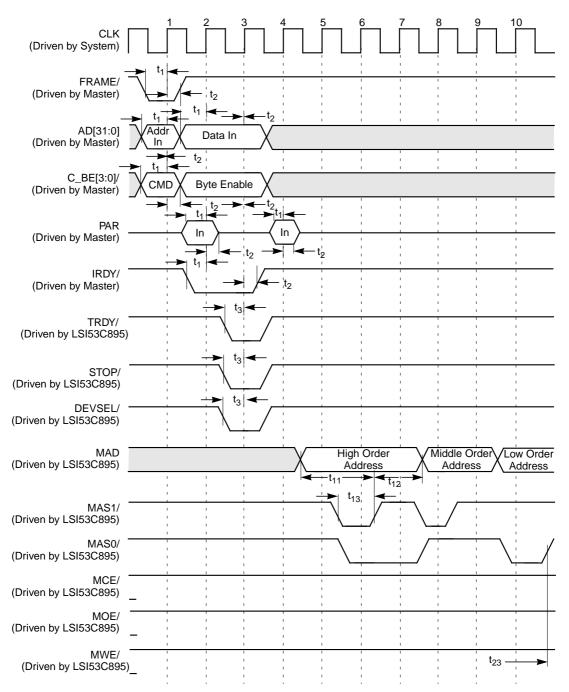

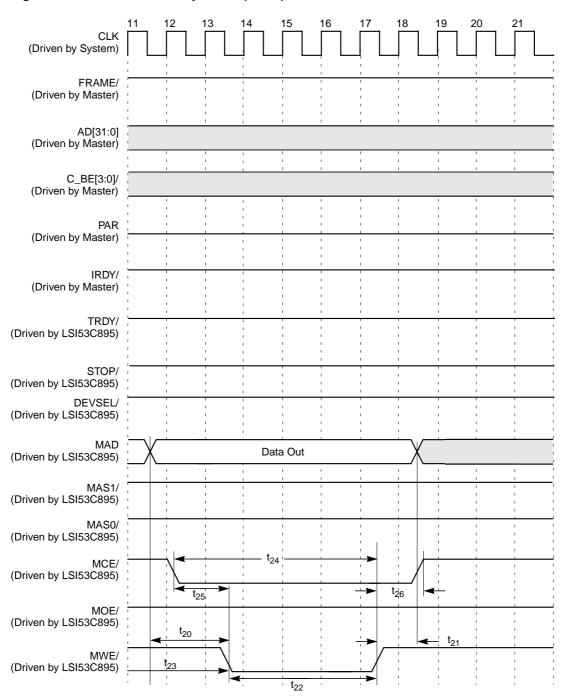

|            | 7.5                        | PCI and   | External Memory Interface Timing Diagram | 7-14 |  |

|            |                            | 7.5.1     | Target Timing                            | 7-16 |  |

|            |                            | 7.5.2     | Initiator Timing                         | 7-21 |  |

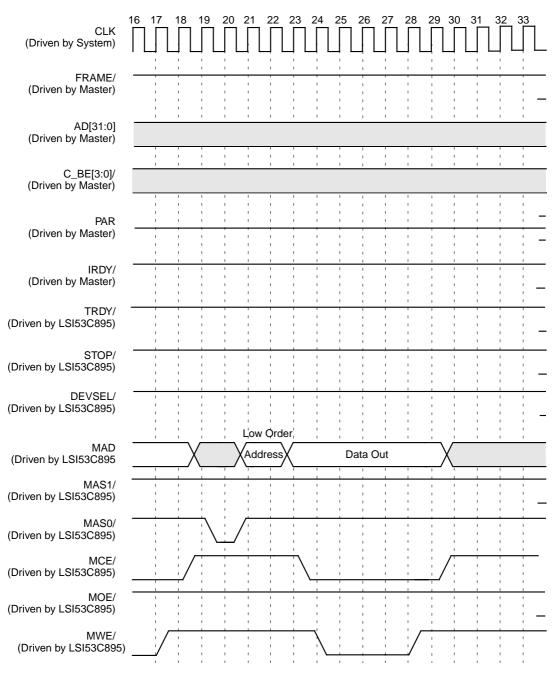

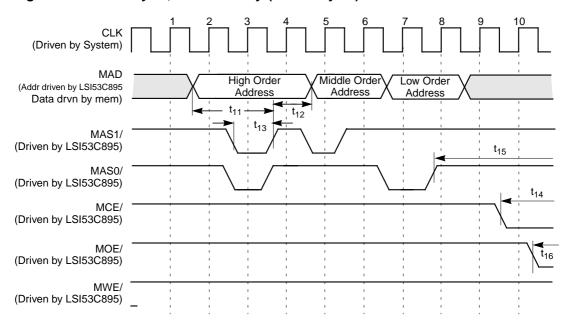

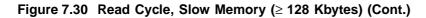

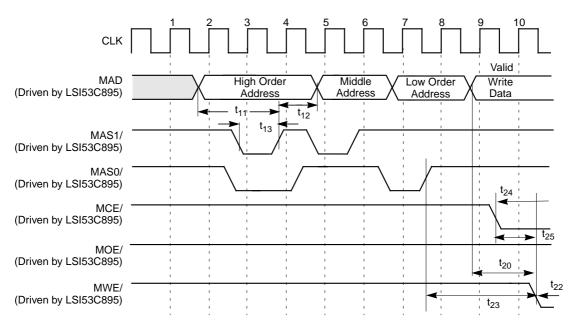

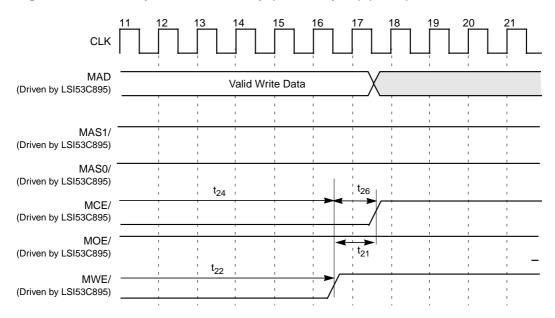

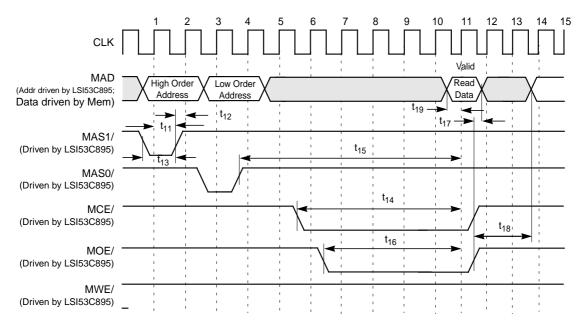

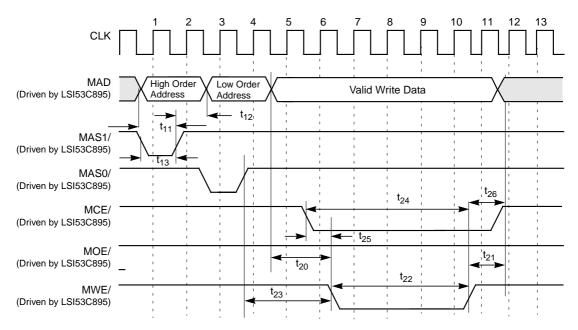

|            |                            | 7.5.3     | External Memory Timing                   | 7-35 |  |

|            | 7.6                        | SCSI Ti   | ming                                     | 7-56 |  |

|            | 7.7                        | Package   | e Diagrams                               | 7-63 |  |

| Appendix A | Regi                       | ster Sum  | mary                                     |      |  |

| Appendix B | Exte                       | rnal Mem  | ory Interface Diagram Examples           |      |  |

| Appendix C | Circu                      | uit Board | Layout Issues                            |      |  |

|            | C.1                        | Signal S  | Separation                               | C-1  |  |

|            | C.2                        | Routing   | Signal Lines                             | C-2  |  |

|            | C.3                        | Impedar   | nce Matching                             | C-2  |  |

|            | C.4                        | Termina   | tion and Stub Length                     | C-2  |  |

|            | C.5                        | Decoupl   | ling                                     | C-3  |  |

|            | <b>C.6</b>                 | Dielectri | С                                        | C-3  |  |

|            | C.7                        |           | rations Specific to the LSI53C895        | C-3  |  |

|            |                            | C.7.1     | RBIAS +/- Pins                           | C-3  |  |

|            |                            | C.7.2     | Physical Dimensions                      | C-3  |  |

|            |                            | C.7.3     | Power Requirements                       | C-4  |  |

|            |                            | C.7.4     | V <sub>DD-A</sub> Pin                    | C-4  |  |

|            |                            | C.7.5     | Terminators                              | C-4  |  |

|            |                            | C.7.6     | Capacitive Load                          | C-4  |  |

|            |                            | C.7.7     | SPI-2 Document                           | C-5  |  |

|            |                            |           |                                          |      |  |

# Index

### **Customer Feedback**

## Figures

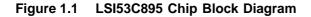

| 1.1  | LSI53C895 Chip Block Diagram                   | 1-2  |

|------|------------------------------------------------|------|

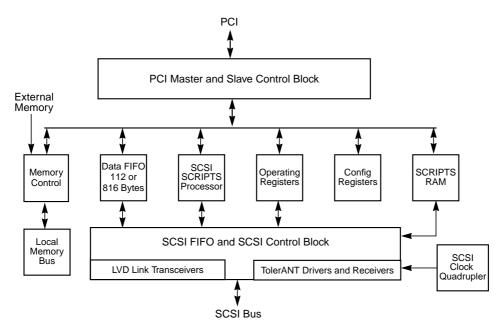

| 2.1  | DMA FIFO Sections                              | 2-3  |

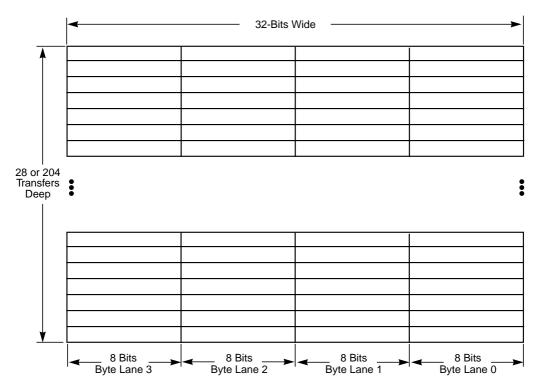

| 2.2  | LSI53C895 Host Interface SCSI Datapath         | 2-7  |

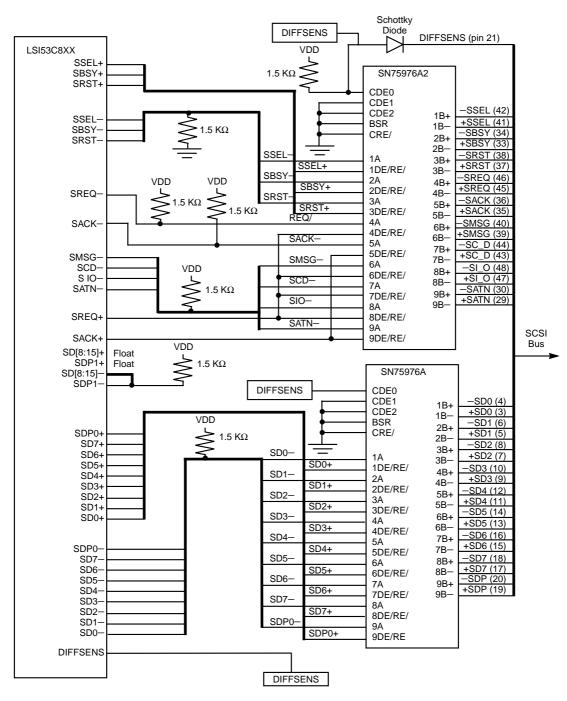

| 2.3  | 8-Bit HVD Wiring Diagram for Ultra2 SCSI       | 2-19 |

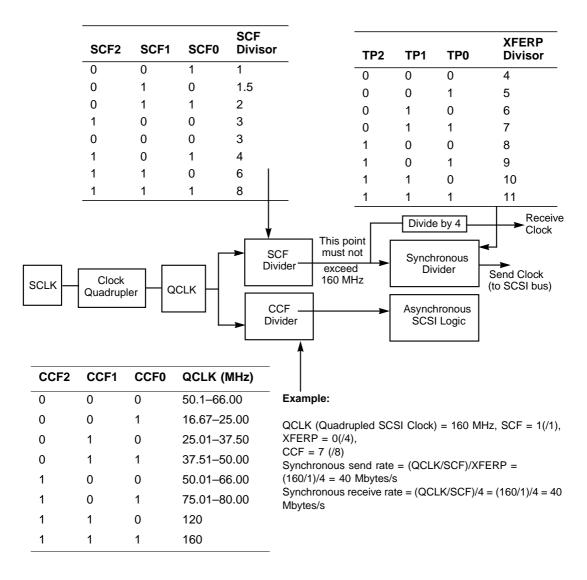

| 2.4  | Regulated Termination for Ultra2 SCSI          | 2-25 |

| 2.5  | Determining the Synchronous Transfer Rate      | 2-31 |

| 2.6  | Block Move and Chained Block Move Instructions | 2-40 |

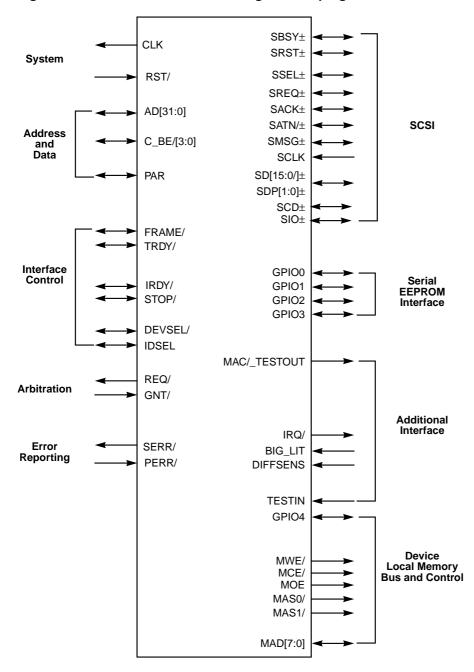

| 4.1  | LSI53C895 Functional Signal Grouping           | 4-2  |

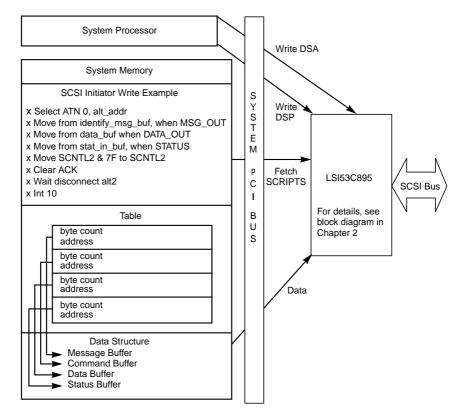

| 6.1  | SCRIPTS Overview                               | 6-5  |

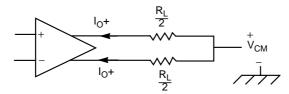

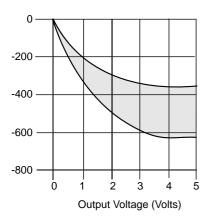

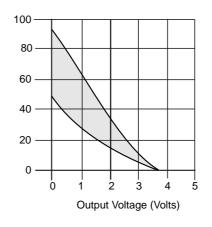

| 7.1  | LVD Transmitter                                | 7-3  |

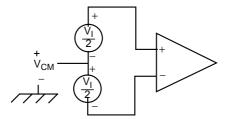

| 7.2  | LVD Receiver                                   | 7-4  |

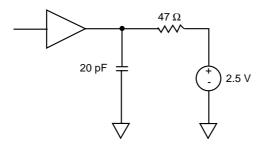

| 7.3  | Rise and Fall Time Test Conditions             | 7-10 |

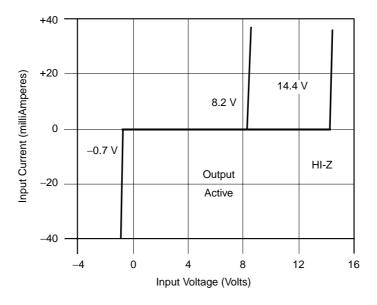

| 7.4  | Input Filtering                                | 7-10 |

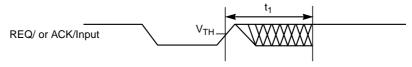

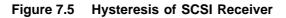

| 7.5  | Hysteresis of SCSI Receiver                    | 7-10 |

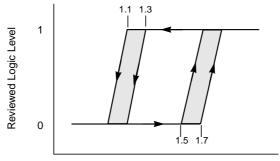

| 7.6  | Input Current as a Function of Input Voltage   | 7-11 |

| 7.7  | Output Current as a Function of Output Voltage | 7-11 |

| 7.8  | External Clock                                 | 7-12 |

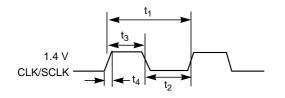

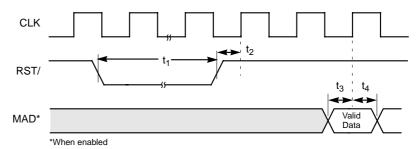

| 7.9  | Reset Input                                    | 7-13 |

| 7.10 | Interrupt Output                               | 7-14 |

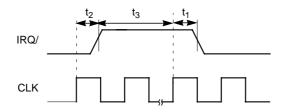

| 7.11 | PCI Configuration Register Read                | 7-17 |

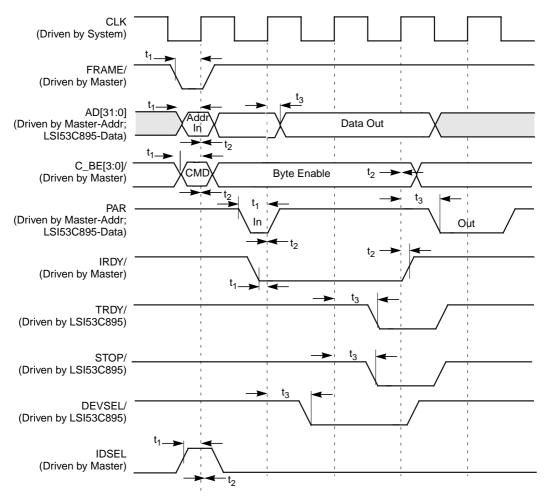

| 7.12 | PCI Configuration Register Write               | 7-18 |

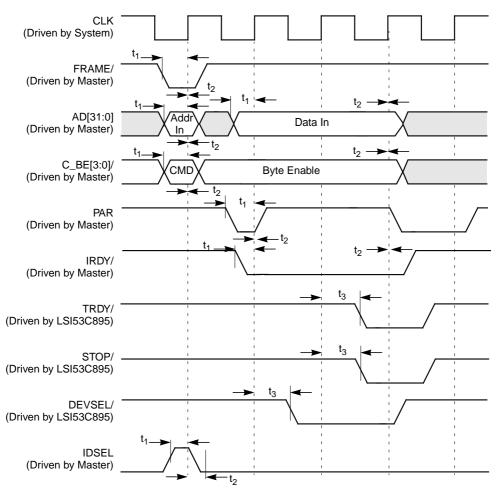

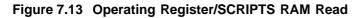

| 7.13 | Operating Register/SCRIPTS RAM Read            | 7-19 |

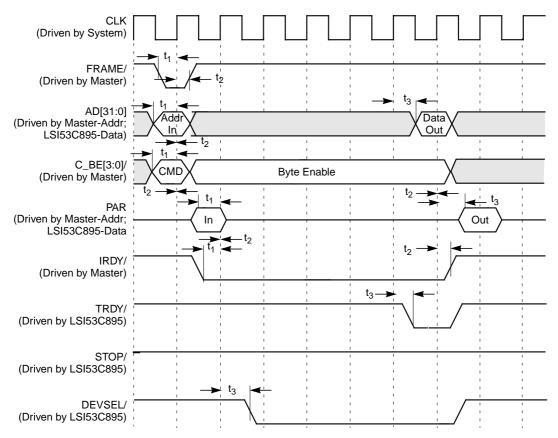

| 7.14 | Operating Register/SCRIPTS RAM Write           | 7-20 |

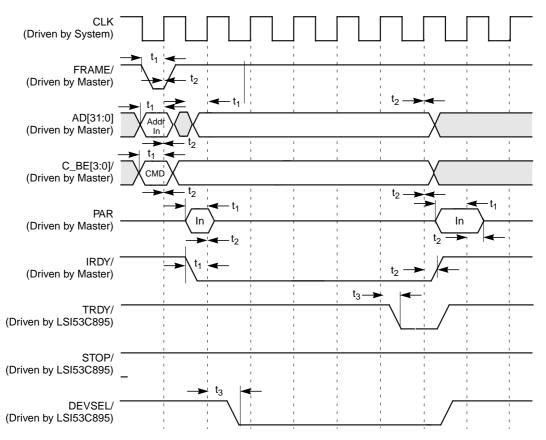

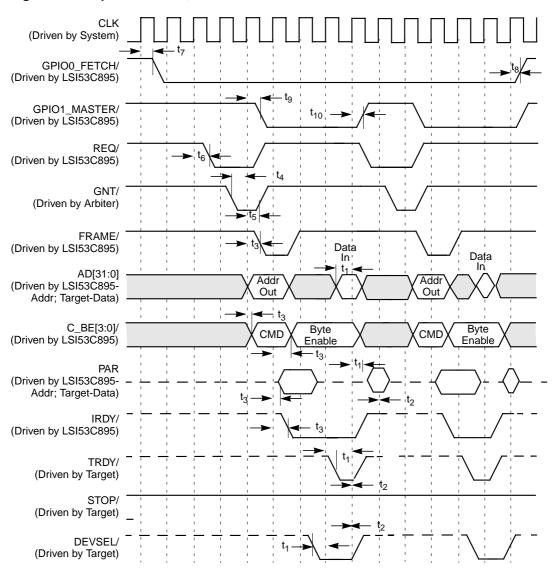

| 7.15 | Op Code Fetch, Nonburst                        | 7-23 |

| 7.16 | Burst Op Code Fetch                            | 7-25 |

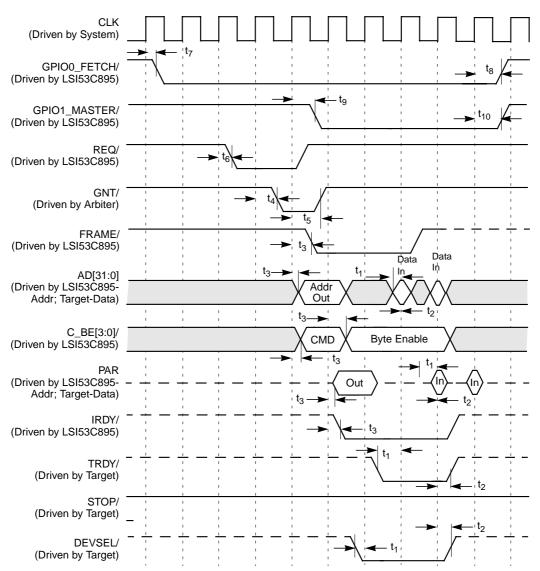

| 7.17 | Back to Back Read                              | 7-27 |

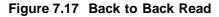

| 7.18 | Back to Back Write                             | 7-29 |

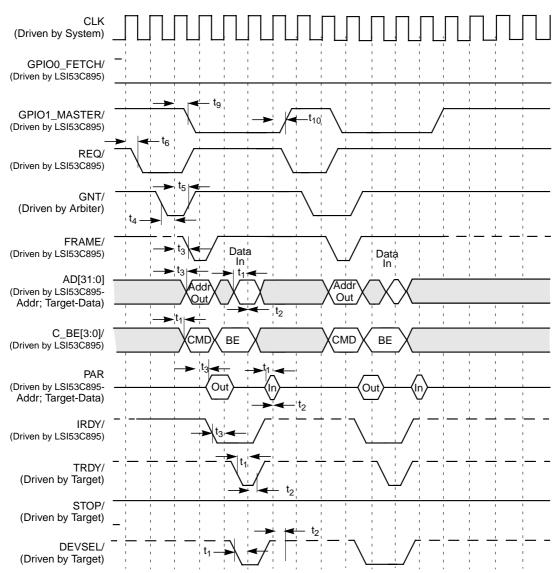

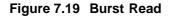

| 7.19 | Burst Read                                     | 7-31 |

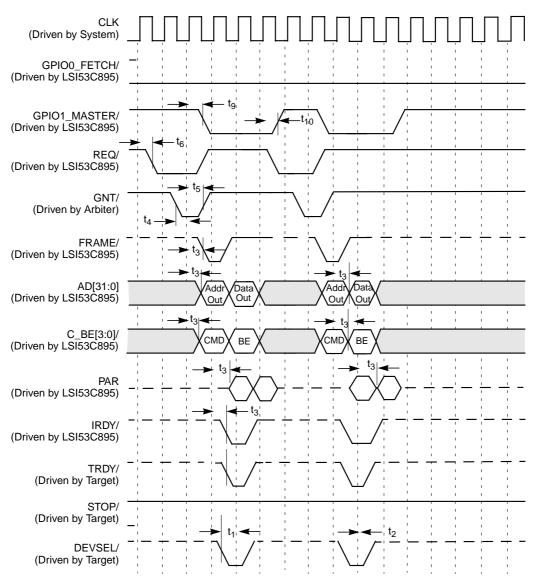

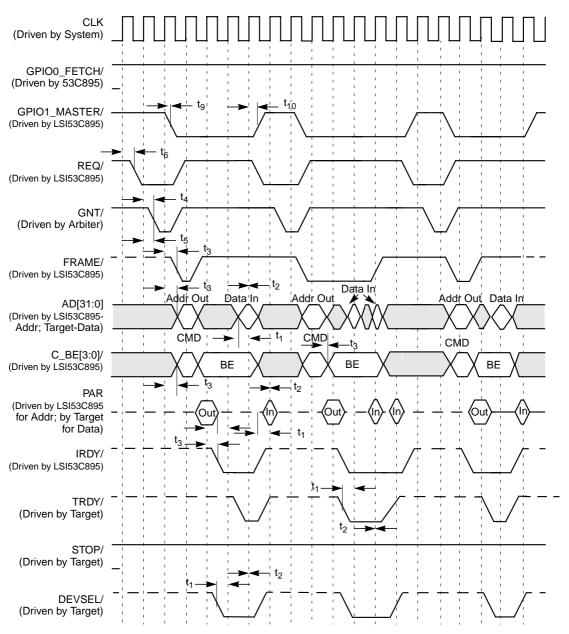

| 7.20 | Burst Write                                    | 7-33 |

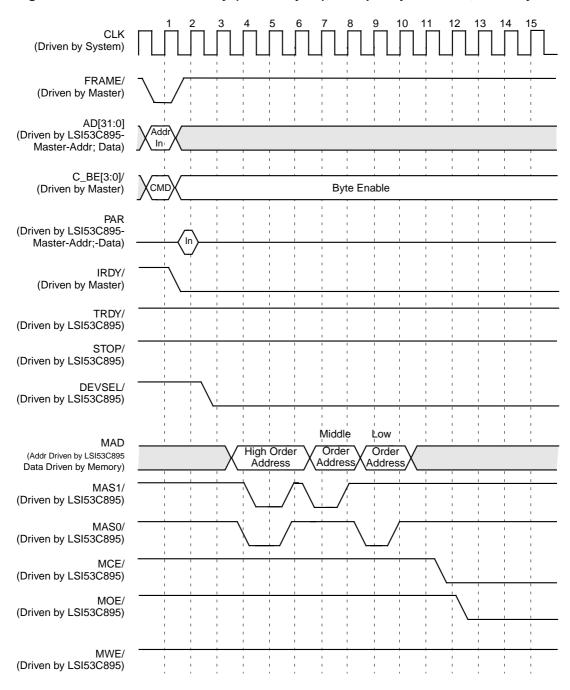

| 7.21 | External Memory Read                           | 7-36 |

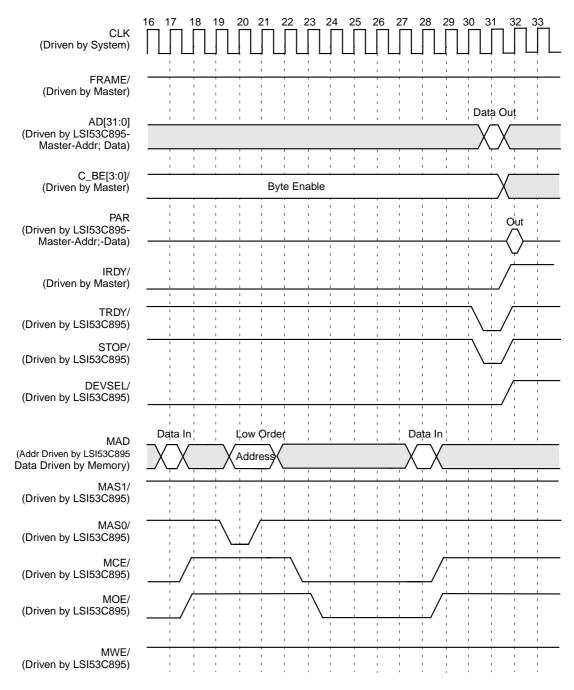

| 7.22 | External Memory Read (Cont.)                   | 7-37 |

| 7.23 | External Memory Write                          | 7-40 |

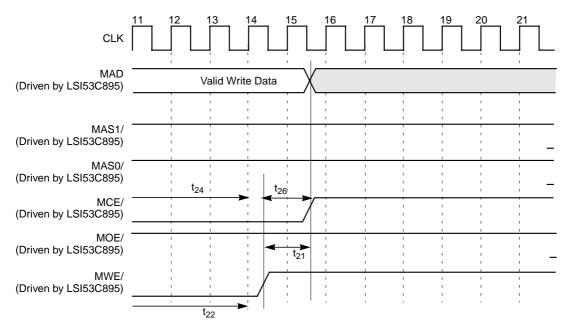

| 7.24 | External Memory Write (Cont.)                  | 7-41 |

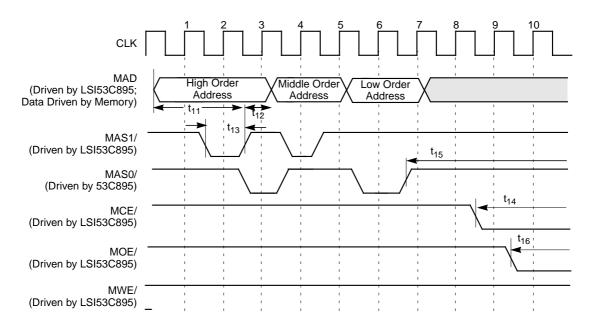

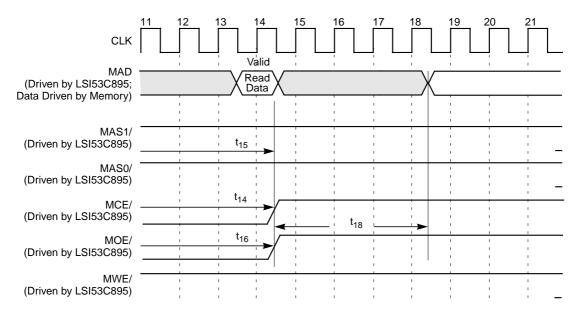

| 7.25 | Read Cycle, Normal/Fast Memory (≥ 128 Kbytes), |      |

|      | Single Byte Access                             | 7-42 |

|      |                                                |      |

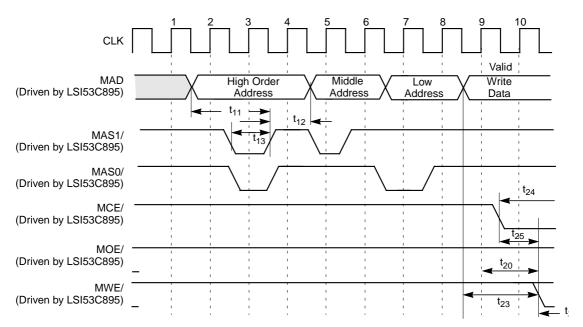

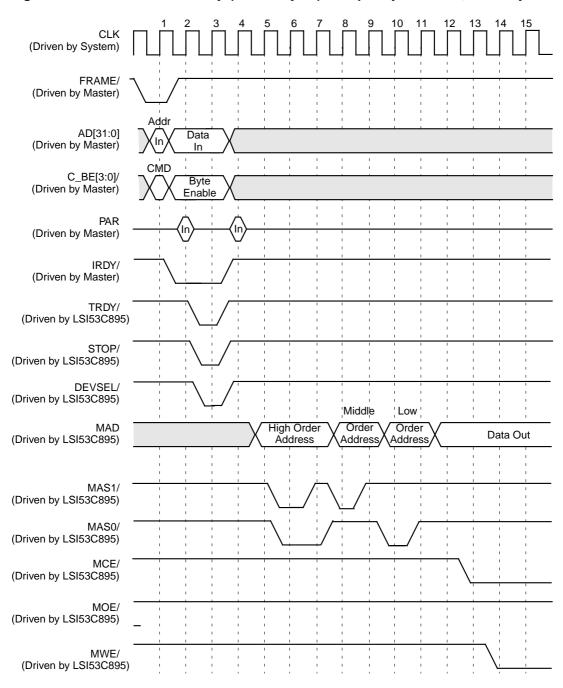

| 7.26 | Normal/Fast Memory (≥ 128 Kbytes), Single Byte<br>Access, Write Cycle | 7-44 |

|------|-----------------------------------------------------------------------|------|

| 7.27 | Normal/Fast Memory (≥ 128 Kbytes), Multiple Byte                      |      |

|      | Access, Read Cycle                                                    | 7-46 |

| 7.28 | Normal/Fast Memory (≥ 128 Kbytes) Multiple Byte                       |      |

|      | Access, Write Cycle                                                   | 7-48 |

| 7.29 | Read Cycle, Slow Memory (≥ 128 Kbytes)                                | 7-50 |

| 7.30 | Read Cycle, Slow Memory (≥ 128 Kbytes) (Cont.)                        | 7-51 |

| 7.31 | Write Cycle, Slow Memory (≥ 128 Kbytes)                               | 7-52 |

| 7.32 | Read cycle, ≤ 64 Kbytes ROM                                           | 7-54 |

| 7.33 | Write Cycle, ≤ 64 Kbytes ROM                                          | 7-55 |

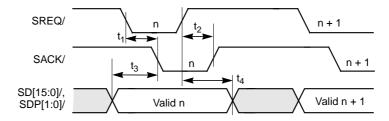

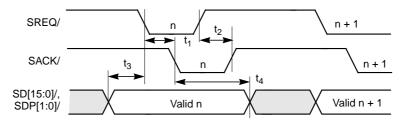

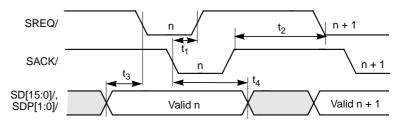

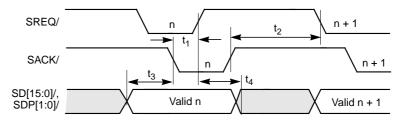

| 7.34 | Initiator Asynchronous Send                                           | 7-56 |

| 7.35 | Initiator Asynchronous Receive                                        | 7-57 |

| 7.36 | Target Asynchronous Send                                              | 7-57 |

| 7.37 | Target Asynchronous Receive                                           | 7-58 |

| 7.38 | Initiator and Target Synchronous Transfers                            | 7-58 |

| 7.39 | LSI53C895 Pin Diagram, 272-Ball BGA (Top View)                        | 7-64 |

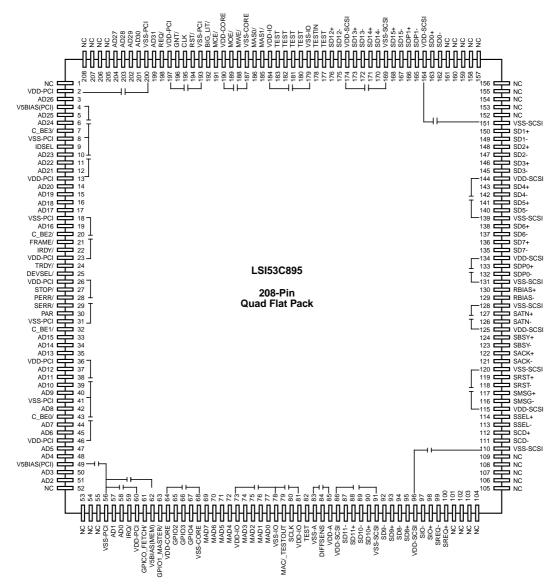

| 7.40 | LSI53C895 Pin Diagram, 208-Pin QFP                                    | 7-68 |

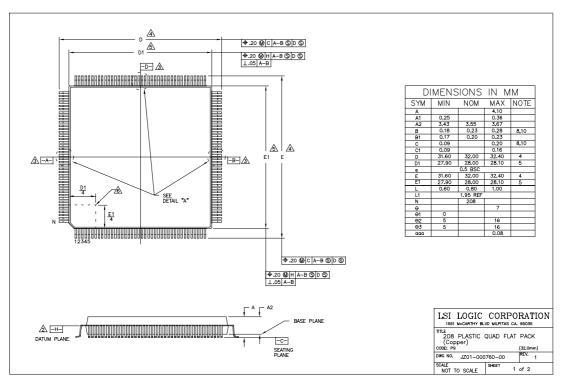

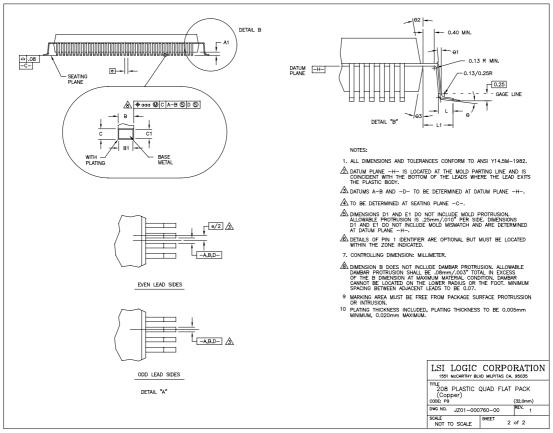

| 7.41 | LSI53C895 Mechanical Drawing, 208-Pin QFP                             | 7-72 |

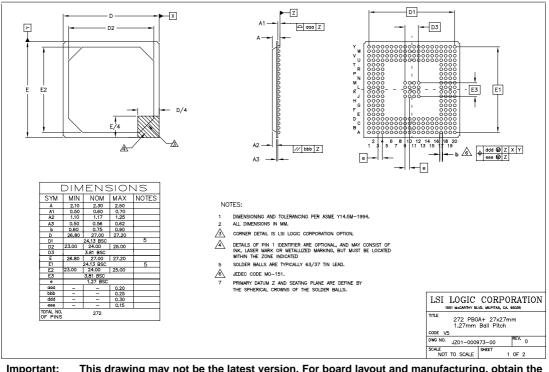

| 7.42 | LSI53C895 Mechanical Drawing, 272 BGA                                 | 7-74 |

| B.1  | 16 Kbytes Interface with 200 ns Memory                                | B-1  |

| B.2  | 64 Kbytes Interface with 200 ns Memory                                | B-2  |

| B.3  | 256 Kbytes Interface with 150 ns Memory                               | B-3  |

| B.4  | 512 Kbytes Interface with 150 ns Memory                               | B-4  |

|      |                                                                       |      |

### Tables

| 2.1 | External Memory Support                     | 2-12 |

|-----|---------------------------------------------|------|

| 2.2 | Mode A Serial EEPROM Data Format            | 2-14 |

| 2.3 | Mode C Serial EEPROM Data Format            | 2-15 |

| 2.4 | HVD Operation                               | 2-17 |

| 2.5 | Bits Used for Parity Control and Generation | 2-22 |

| 2.6 | SCSI Parity Control                         | 2-23 |

| 2.7 | SCSI Parity Errors and Interrupts           | 2-24 |

| 2.8 | Transmission Mode                           | 2-25 |

| 3.1 | PCI Bus Commands Supported                  | 3-3  |

| 4.1 | LSI53C895 Internal Pull-ups                 | 4-4  |

| 4.2 | LSI53C895 Power and Ground Signals          | 4-5  |

| 4.3 | System Signals                              | 4-6  |

|     |                                             |      |

| 4.4  | Address and Data Signals                            | 4-7  |

|------|-----------------------------------------------------|------|

| 4.5  | Interface Control Pins                              | 4-8  |

| 4.6  | Arbitration Signals                                 | 4-9  |

| 4.7  | Error Reporting Signals                             | 4-9  |

| 4.8  | SCSI Signals, LVD Link Mode                         | 4-10 |

| 4.9  | SCSI Pins, SE Mode                                  | 4-12 |

| 4.10 | SCSI Signals, High Voltage Differential Mode        | 4-13 |

| 4.11 | Additional Signals                                  | 4-15 |

| 4.12 | External Memory Interface Signals                   | 4-17 |

| 5.1  | PCI Configuration Register Map                      | 5-2  |

| 5.2  | SCSI Register Map                                   | 5-16 |

| 5.3  | Synchronous Clock Conversion Factor                 | 5-26 |

| 5.4  | Asynchronous Clock Conversion Factor                | 5-27 |

| 5.5  | Examples of Synchronous Transfer Periods and Rates  |      |

|      | for SCSI-1                                          | 5-30 |

| 5.6  | Example Synchronous Transfer Periods and Rates for  |      |

|      | Fast SCSI, Ultra SCSI, and Ultra2 SCSI              | 5-31 |

| 5.7  | Maximum Synchronous Offset                          | 5-32 |

| 5.8  | Timeout Periods                                     | 5-80 |

| 5.9  | Timeout Periods, 50 MHz Clock                       | 5-81 |

| 5.10 | Timeout Periods, 40/160 MHz Clock                   | 5-82 |

| 5.11 | DIFFSENS Voltage Levels and SCSI Operating Modes    | 5-92 |

| 6.1  | SCRIPTS Instructions                                | 6-3  |

| 6.2  | SCSI Information Transfer Phase                     | 6-12 |

| 6.3  | Read/Write Instructions                             | 6-24 |

| 6.4  | Transfer Control Instructions                       | 6-26 |

| 6.5  | SCSI Phase Comparisons                              | 6-29 |

| 7.1  | Absolute Maximum Stress Ratings                     | 7-2  |

| 7.2  | Operating Conditions                                | 7-2  |

| 7.3  | SCSI Signals, LVD Drivers—SD[15:0]+/-, SDP[1:0]+/-, |      |

|      | SREQ+/-, SACK+/-, SMSG+/-, SIO+/-, SCD+/-,          |      |

|      | SATN+/-, SBSY+/-, SSEL+/-, SRST+/-*                 | 7-3  |

| 7.4  | SCSI Signals, LVD Receivers—SD[15:0]+/-,            |      |

|      | SDP[1:0]+/-, SREQ+/-, SACK+/-, SMSG+/-, SIO+/-,     |      |

|      | SCD+/-, SATN+-, SBSY+/-, SSEL+/-, SRST+/-           | 7-3  |

| 7.5  | SCSI Signal—DIFFSENS                                | 7-4  |

| 7.6  | SCSI Signals—RBIAS+/-                               | 7-4  |

| 7.7  | Capacitance                                         | 7-4  |

| 7.8  | Output Signal—MAC/_TESTOUT                                | 7-5  |

|------|-----------------------------------------------------------|------|

| 7.9  | Input Signals—CLK, RST/ <sup>1</sup> , IDSEL, GNT/, SCLK/ | 7-5  |

| 7.10 | Bidirectional Signals—AD[31:0], C_BE/[3:0], FRAME/,       |      |

|      | IRDY/, TRDY/, DEVSEL/, STOP/, PERR/, PAR, REQ/,           |      |

|      | IRQ/, SERR/                                               | 7-5  |

| 7.11 | Bidirectional Signals—GPIO0_FETCH/, GPIO1_MASTER/,        |      |

|      | GPIO2, GPIO3, GPIO4, MAD[7:0]                             | 7-6  |

| 7.12 | Bidirectional Signals—MAS/[1:0], MCE/, MOE/, MWE/         | 7-6  |

| 7.13 | Input Signal—BIG_LIT/                                     | 7-6  |

| 7.14 | Bidirectional Signals—AD[31:0], C_BE[3:0]/, FRAME/,       |      |

|      | IRDY/, TRDY/, DEVSEL/, STOP/, PERR/, PAR,                 |      |

|      | BYTEPAR[3:0]                                              | 7-7  |

| 7.15 | Input Signals—CLK, GNT/, IDSEL, RST/                      | 7-7  |

| 7.16 | Output Signals—IRQ/, REQ/                                 | 7-7  |

| 7.17 | Output Signal—SERR/                                       | 7-8  |

| 7.18 | TolerANT Technology Electrical Characteristics            | 7-8  |

| 7.19 | External Clock                                            | 7-12 |

| 7.20 | Reset Input                                               | 7-13 |

| 7.21 | Interrupt Output                                          | 7-14 |

| 7.22 | Configuration Register Read                               | 7-17 |

| 7.23 | Configuration Register Write                              | 7-18 |

| 7.24 | Operating Register/SCRIPTS RAM Read                       | 7-19 |

| 7.25 | Operating Register/SCRIPTS RAM Write                      | 7-20 |

| 7.26 | Op Code Fetch, Nonburst                                   | 7-22 |

| 7.27 | Burst Op Code Fetch                                       | 7-24 |

| 7.28 | Back to Back Read                                         | 7-26 |

| 7.29 | Back to Back Write                                        | 7-28 |

| 7.30 | Burst Read                                                | 7-30 |

| 7.31 | Burst Write                                               | 7-32 |

| 7.32 | External Memory Read                                      | 7-35 |

| 7.33 | External Memory Write                                     | 7-39 |

| 7.34 | Read Cycle TIming, Normal/Fast Memory                     |      |

|      | (≥ 128 Kbytes), Single Byte Access                        | 7-42 |

| 7.35 | Write Cycle Timing, Normal/Fast Memory                    |      |

|      | (≥ 128 Kbytes), Single Byte Access                        | 7-44 |

| 7.36 | Read Cycle, Slow Memory (≥ 128 Kbytes)                    | 7-50 |

| 7.37 | Write Cycle Timing, Slow Memory (≥ 128 Kbytes)            | 7-52 |

| 7.38 | Read Cycle Timing, $\leq$ 64 Kbytes ROM                   | 7-54 |

| 7.39 | Write Cycle Timing, ≤ 64 Kbytes ROM                      | 7-55 |

|------|----------------------------------------------------------|------|

| 7.40 | Initiator Asynchronous Send                              | 7-56 |

| 7.41 | Initiator Asynchronous Receive                           | 7-57 |

| 7.42 | Target Asynchronous Send                                 | 7-57 |

| 7.43 | Target Asynchronous Receive                              | 7-58 |

| 7.44 | SCSI-1 Transfers (SE, 5.0 Mbytes/s)                      | 7-59 |

| 7.45 | SCSI-1 Transfers (Differential, 4.17 Mbytes/s)           | 7-59 |

| 7.46 | SCSI-2 Fast Transfers 10.0 Mbytes/s (8-Bit Transfers)    |      |

|      | or 20.0 Mbytes/s (16-Bit Transfers), 40 MHz Clock        | 7-60 |

| 7.47 | SCSI-2 Fast Transfers 10.0 Mbytes/s (8-Bit Transfers)    |      |

|      | or 20.0 Mbytes/s                                         |      |

|      | (16-Bit Transfers), 50 MHz Clock                         | 7-60 |

| 7.48 | Ultra SCSI SE Transfers 20.0 Mbytes/s (8-Bit Transfers)  |      |

|      | or 40.0 Mbytes/s (16-Bit Transfers), Quadrupled 40 MHz   |      |

|      | Clock                                                    | 7-61 |

| 7.49 | Ultra SCSI HVD Transfers 20.0 Mbytes/s (8-Bit Transfers) |      |

|      | or 40.0 Mbytes/s (16-Bit Transfers), 80 MHz Clock        | 7-61 |

| 7.50 | Ultra2 SCSI Transfers 40.0 Mbytes/s (8-Bit Transfers)    |      |

|      | or 80.0 Mbytes/s                                         |      |

|      | (16-Bit Transfers), Quadrupled 40 MHz Clock              | 7-62 |

| 7.51 | BGA Position and Signal Name Alphabetically              | 7-66 |

| 7.52 | BGA Position Numerically and Signal Name                 | 7-67 |

| 7.53 | Signal Name by Pin Number QFP                            | 7-70 |

| 7.54 | Alphabetical Signal Name and Pin Number QFP              | 7-71 |

| A.1  | LSI53C895 Register Map                                   | A-1  |

# Chapter 1 Introduction

This chapter provides a general overview on the LSI53C895 PCI to Ultra2 SCSI I/O Processor and other members of the LSI53C8XX family of PCI to SCSI I/O Processors. This chapter contains these topics:

- Section 1.1, "General Description," page 1-1

- Section 1.2, "Benefits of LVD Link," page 1-3

- Section 1.3, "Benefits of Ultra2 SCSI," page 1-4

- Section 1.4, "TolerANT<sup>®</sup> Technology," page 1-4

- Section 1.5, "LSI53C895 Benefits Summary," page 1-5

# **1.1 General Description**

The LSI53C895 brings Ultra2 SCSI performance to host adapter, workstation, and general computer designs, making it easy to add a high-performance SCSI bus to any PCI system. It supports Ultra2 SCSI transfer rates and allows you to increase SCSI connectivity and cable length with Low Voltage Differential (LVD) signaling for SCSI.

The LSI53C895 has a local memory bus for local storage of the device BIOS ROM in flash memory or standard EEPROMs. The LSI53C895 supports big and little endian byte addressing to accommodate a variety of data configurations. The LSI53C895 supports programming of local flash memory for updates to BIOS or SCRIPTS<sup>™</sup> programs. The chip is packaged in a 208-pin quad flat pack or a 272-ball Ball Grid Array (BGA). System diagrams showing the connections of the LSI53C895 with an external ROM or flash memory are pictured in Appendix C. A block diagram of the LSI53C895 is pictured in Figure 1.1 on page 1-2.

LSI Logic LVD Link<sup>™</sup> technology is the LSI Logic implementation of LVD. LVD Link transceivers allow the LSI53C895 to perform Single-Ended (SE) and LVD transfers, and support external High Voltage Differential (HVD) transceivers. The LSI53C895 integrates a high performance SCSI core, a PCI bus master DMA core, and the LSI Logic SCSI SCRIPTS processor to meet the flexibility requirements of SCSI-3 and Ultra2 SCSI standards. It is designed to implement multithreaded I/O algorithms with a minimum of processor intervention, solving the protocol overhead problems of previous intelligent and nonintelligent adapter designs.

### 1.1.1 New Features in the LSI53C895

The LSI53C895 is functionally similar to the LSI53C875 PCI to SCSI I/O processor, with added support for Ultra2 SCSI. Some software enhancements, and use of LVD, enable the LSI53C895 to transfer data at Ultra2 SCSI transfer rates. Most of the feature enhancements in the LSI53C895 are included to enable the chip to take advantage of Ultra2 SCSI transfer rates.

• Optional 816-byte DMA FIFO supports large block transfers at Ultra2 SCSI speeds. The default FIFO size is 112 bytes.

- Thirty-one levels of SCSI Synchronous Offset increases the pace of synchronous transfers to match Ultra2 SCSI transfer speeds.

- On-chip LVD Link transceivers allow increased connectivity, longer cable length, and improved performance. They also automatically sense the type of device connected to the SCSI bus and switch as needed to SE, LVD, or HVD mode (if the chip is connected to external transceivers).

- On-chip SCSI clock quadrupler can achieve 160 MHz frequency with an external 40 MHz oscillator.

- Supports Subsystem ID and Subsystem Vendor ID registers in PCI configuration space.

- Support for serial EEPROM interface.

# 1.2 Benefits of LVD Link

The LSI53C895 supports LVD for SCSI, a signaling technology that increases the reliability of SCSI data transfers over longer distances than supported by SE SCSI. The low current output of LVD allows the I/O transceivers to be integrated directly onto the chip. LVD provides the reliability of HVD SCSI without the added cost of external differential transceivers. Ultra2 SCSI with LVD allows a longer SCSI cable and more devices on the bus, using the same cables defined in the SCSI-3 Parallel Interface standard for Ultra SCSI. LVD provides a long-term migration path to even faster SCSI transfer rates without compromising signal integrity, cable length, or connectivity.

For backward compatibility to existing SE devices, the LSI53C895 features universal LVD Link transceivers that can switch between LVD and SE SCSI modes. The LVD Link technology also supports high power differential signaling in legacy systems when external transceivers are connected to the LSI53C895. This allows the LSI53C895 to be used in both legacy and Ultra2 SCSI applications.

# 1.3 Benefits of Ultra2 SCSI

Ultra2 SCSI is an extension of the SPI-2 draft standard that allows faster synchronous SCSI transfer rates and defines a new physical layer, LVD SCSI. LVD SCSI provides an incremental evolution from SCSI-2 and Ultra SCSI. When enabled, Ultra2 SCSI performs 40 megatransfers per second, which results in approximately double the synchronous transfer rates of Ultra SCSI. The LSI53C895 can perform 16 bit, Ultra2 SCSI synchronous transfers as fast as 80 Mbytes/s. This advantage is most noticeable in heavily loaded systems or large-block size applications such as video on-demand and image processing.

One advantage of Ultra2 SCSI is that it significantly improves SCSI bandwidth while preserving existing hardware and software investments. The primary software changes enable the chip to perform synchronous negotiations for Ultra2 SCSI rates, and to enable the clock quadrupler. Ultra2 SCSI uses the same connectors as Ultra SCSI, but can operate with longer cables and more devices on the bus. Chapter 2 contains more information on migrating from an Ultra SCSI design to support Ultra2 SCSI.

# 1.4 TolerANT® Technology

The LSI53C895 features TolerANT technology, which includes active negation on the SCSI drivers and input signal filtering on the SCSI receivers. Active negation drives the SCSI Request, Acknowledge, Data, and Parity signals active HIGH rather than allowing them to be passively pulled up by terminators. Active negation is enabled by setting bit 7 in the SCSI Test Three (STEST3) register.

TolerANT receiver technology improves data integrity in unreliable cabling environments, where other devices would be subject to data corruption. TolerANT receivers filter the SCSI bus signals to eliminate unwanted transitions without the long signal delay associated with RC-type input filters. This improved driver and receiver technology helps eliminate double clocking of data, the single biggest reliability issue with SCSI operations. TolerANT input signal filtering is a built in feature of the LSI53C895 and all LSI Logic Fast SCSI, Ultra SCSI, and Ultra2 SCSI devices. On the LSI53C895, the user can select a filtering period of 30 or 60 ns, with bit 1 in the SCSI Test Two (STEST2) register.

The benefits of TolerANT technology include increased immunity to noise when the signal is going HIGH, better performance due to balanced duty cycles, and improved fast SCSI transfer rates. In addition, TolerANT SCSI devices do not cause glitches on the SCSI bus at power up or power down, so other devices on the bus are also protected from data corruption. When it is used with the LVD Link transceivers, TolerANT technology provides excellent signal quality and data reliability in real world cabling environments. TolerANT technology is compatible with both the Alternative One and Alternative Two termination schemes proposed by the American National Standards Institute.

# 1.5 LSI53C895 Benefits Summary

This section provides an overview of the LSI53C895 benefits and features. It includes these topics:

- SCSI Performance

- PCI Performance

- Integration

- Ease of Use

- Flexibility

- Reliability

- Testability

### 1.5.1 SCSI Performance

To improve SCSI performance, the LSI53C895:

- Has integrated LVD Link universal transceivers which:

- Support SE, LVD, and HVD signals (with external transceivers)

- Allow greater device connectivity and longer cable length

- LVD Link transceivers save the cost of external differential transceivers

- Support a long-term performance migration path

- Bursts up to 512 bytes across the PCI bus through its 816 byte FIFO

- Performs wide Ultra2 SCSI synchronous transfers as fast as 80 Mbytes/s

- Includes an on-chip SCSI clock quadrupler that allows the chip to achieve Ultra2 SCSI transfer rates with a 40 MHz clock

- Includes 4 Kbytes internal RAM for SCRIPTS instruction storage

- Has 31 levels of SCSI synchronous offset

- Supports variable block size and scatter/gather data transfers.

- Performs sustained memory-to-memory DMA transfers faster than 47 Mbytes/s (@ 33 MHz)

- Minimizes SCSI I/O start latency

- Performs complex bus sequences without interrupts, including restore data pointers

- Reduces Interrupt Service Routine (ISR) overhead through a unique interrupt status reporting method

- Includes Load and Store SCRIPTS instructions to increase performance of data transfers to and from chip registers

- Supports target disconnect and later reconnect with no interrupt to the system processor

- Supports multithreaded I/O algorithms in SCSI SCRIPTS with fast I/O context switching

- Supports expanded register Move instructions for additional arithmetic capability

### 1.5.2 PCI Performance

To improve PCI performance, the LSI53C895:

- Complies with PCI 2.1 specification

- Supports 32-bit 33 MHz PCI interface

- Bursts 2, 4, 8, 16, 32, 64, or 128 Dwords across the PCI bus

- Supports 32-bit word data bursts with variable burst lengths

- Prefetches up to 8 Dwords of SCRIPTS instructions

- Bursts SCRIPTS op code fetches across the PCI bus

- Performs zero wait-state bus master data bursts faster than 110 Mbytes/s (@ 33 MHz)

- Supports PCI Cache Line Size register

- Supports PCI Write and Invalidate, Read Line, and Read Multiple commands

## 1.5.3 Integration

The LSI53C895 contains these integration features:

- Integrated LVD transceivers

- Full 32-bit PCI DMA bus master

- Memory to Memory Move instructions to allow use as a third-party PCI bus DMA controller

- High performance SCSI core

- Integrated SCRIPTS processor

## 1.5.4 Ease of Use

The LSI53C895 provides ease of use by having:

- Up to one megabyte of add-in memory support for BIOS and SCRIPTS storage

- Direct PCI to SCSI connection

- Reduced SCSI development effort

- Compiler-compatible with existing LSI53C7XX and LSI53C8XX family SCRIPTS

- Direct connection to PCI, and SCSI SE and differential buses

- Development tools and sample SCSI SCRIPTS available

- Maskable and pollable interrupts

- Wide SCSI, A or P cable, and up to 16 devices supported

- Three programmable SCSI timers: Select/Reselect, Handshake-to-Handshake, and General Purpose. The time-out period is programmable from 100 μs to greater than 25.6 seconds

- Software for PC-based operating system support

- Support for relative jumps

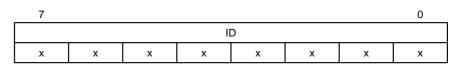

- SCSI selected as ID bits for responding with multiple IDs

## 1.5.5 Flexibility

The LSI53C895 contains these flexibility features:

- Universal LVD transceivers that are backward compatible with SE or high power differential devices

- High level programming interface (SCSI SCRIPTS)

- Programs local memory bus flash memory

- Big/Little endian support

- Selectable 112 or 816 byte DMA FIFO for backward compatibility

- Tailored SCSI sequences execute from main system RAM or internal SCRIPTS RAM

- Flexible programming interface to tune I/O performance or to adapt to unique SCSI devices

- Support for changes in the logical I/O interface definition

- Low level access to all registers and all SCSI bus signals

- Fetch, Master, and Memory Access control pins

- Separate SCSI and system clocks

- SCSI clock quadrupler bits enable Ultra2 SCSI transfer rates with a 40 MHz SCSI clock

- Selectable IRQ pin disable bit

- Ability to route system clock to SCSI clock

### 1.5.6 Reliability

The LSI53C895 contains these reliability features:

- 2 kV ESD protection on SCSI signals

- Protection against bus reflections due to impedance mismatches

- Controlled bus assertion times (reduces RFI, improves reliability, and eases FCC certification)

- Latch-up protection greater than 150 mA

- Voltage feed through protection (minimum leakage current through SCSI pads)

- More than 25% of pins are power and ground

- Power and ground isolation of I/O pads and internal chip logic

- TolerANT technology provides:

- Active negation of SCSI data, parity, request, and acknowledge signals for improved fast SCSI transfer rates

- Input signal filtering on SCSI receivers improves data integrity, even in noisy cabling environments

## 1.5.7 Testability

The LSI53C895 contains these testability features:

- All SCSI signals accessible through programmed I/O

- SCSI loopback diagnostics

- SCSI bus signal continuity checking

- Support for single-step mode operation

- Test mode (AND tree) to check pin continuity to the board

# Chapter 2 Functional Description

This chapter provides information about three functional blocks for the LSI53C895 processor: SCSI core, DMA core, and SCRIPTS processor. Other topics include specific interfaces, modes, and various options. Chapter 2 contains these sections:

- Section 2.1, "SCSI Core," page 2-2

- Section 2.2, "DMA Core," page 2-2

- Section 2.3, "SCRIPTS Processor," page 2-7

- Section 2.4, "Prefetching SCRIPTS Instructions," page 2-8

- Section 2.5, "Designing an Ultra2 SCSI System," page 2-10

- Section 2.6, "LSI53C895 Interfaces," page 2-11

- Section 2.7, "LSI53C895 Modes," page 2-20

- Section 2.8, "Parity Options," page 2-22

- Section 2.9, "Synchronous Operation," page 2-28

- Section 2.10, "Interrupt Handling," page 2-32

- Section 2.11, "Chained Block Moves," page 2-39

Note that LSI Logic supplies software that supports the LSI53C895 and the entire LSI Logic product line of SCSI processors and controllers.

# 2.1 SCSI Core

The SCSI core supports an 8-bit or 16-bit data bus. It supports Ultra2 SCSI synchronous transfer rates up to 80 Mbytes/s on a 16-bit, LVD SCSI bus. The SCSI core can be programmed with SCSI SCRIPTS, making it easy to "fine tune" the system for specific mass storage devices or SCSI-3 requirements.

The SCSI core offers low-level register access or a high-level control interface. Like first generation SCSI devices, the LSI53C895 SCSI core can be accessed as a register-oriented device. The ability to sample and/or assert any signal on the SCSI bus is useful for error recovery and diagnostic procedures. In support of loopback diagnostics, the SCSI core could perform a self-selection and operate as both an initiator and a target.

The integrated SCRIPTS processor controls the LSI53C895 SCSI core through a high-level logical interface. Commands controlling the SCSI core are fetched out of the main host memory or local memory. These commands instruct the SCSI core to transfer information, change bus phases and, in general, implement all aspects of the SCSI protocol. The SCRIPTS processor is a special high-speed processor optimized for SCSI protocol.

# 2.2 DMA Core

The DMA core is a bus master DMA device that attaches directly to the industry standard PCI Bus. The DMA core is tightly coupled to the SCSI core through the SCRIPTS processor, which supports uninterrupted scatter/gather memory operations.

The LSI53C895 supports 32-bit memory and automatically supports misaligned DMA transfers. A 112 or 816 byte FIFO allows the LSI53C895 to support 2, 4, 8, 16, 32, 64, or 128 Dword bursts across the PCI bus interface.

# 2.2.1 DMA FIFO

The DMA FIFO is 4-bytes wide and 28 or 204 transfers deep. The DMA FIFO is illustrated in Figure 2.1. To assure compatibility with older products in the LSI53C8XX family, the user may set the DMA FIFO size to 112 bytes by clearing the DMA FIFO Size bit, bit 5 in the Chip Test Five (CTEST5) register.

The 816-byte FIFO size is related to the LSI53C895 FIFO architecture. It does not reflect any specific system design parameters or expectations.

#### 2.2.1.1 Data Paths

The data path through the LSI53C895 is dependent on whether data is being moved into or out of the chip. It also depends on whether SCSI data is being transferred asynchronously or synchronously.

Figure 2.2 shows how data is moved to/from the SCSI bus in each of the different modes. To determine if any bytes remain in the data path when the chip halts an operation, follow the detailed instructions in the next sections.

**Asynchronous SCSI Send** – Follow these steps for asynchronous SCSI send operations:

Step 1. To calculate DMA FIFO size:

If the DMA FIFO size is set to 112 bytes, look at the DMA FIFO (DFIFO) and DMA Byte Counter (DBC) registers and calculate if there are bytes left in the DMA FIFO. To make this calculation, subtract the seven least significant bits of the DMA Byte Counter (DBC) register from the 7-bit value of the DMA FIFO (DFIFO) register. AND the result with 0x7F for a byte count between zero and 112.

If the DMA FIFO size is set to 816 bytes (using bit 5 of the Chip Test Five (CTEST5) register), subtract the 10 least significant bits of the DMA Byte Counter (DBC) register from the 10-bit value of the DMA FIFO Byte Offset Counter, which consists of bits [1:0] in the Chip Test Five (CTEST5) register and bits [7:0] of the DMA FIFO (DFIFO) register. AND the result with 0x3FF for a byte count between zero and 816.

Step 2. To determine if any bytes are left in the SCSI Output Data Latch (SODL) register, read bit 5 in the SCSI Status Zero (SSTAT0) and SCSI Status Two (SSTAT2) registers.

If bit 5 is set in the SCSI Status Zero (SSTAT0) or SCSI Status Two (SSTAT2), then the least significant byte or the most significant byte in the SCSI Output Data Latch (SODL) register is full, respectively. Checking this bit also reveals bytes left in the SCSI Output Data Latch (SODL) register from a Chained Move operation with an odd byte count.

**Synchronous SCSI Send** – Follow these steps for synchronous SCSI send:

Step 1. To calculate DMA FIFO size:

If the DMA FIFO size is set to 112 bytes, look at the DMA FIFO (DFIFO) and DMA Byte Counter (DBC) registers and calculate if there are bytes left in the DMA FIFO. To make this calculation,

subtract the seven least significant bits of the DMA Byte Counter (DBC) register from the 7-bit value of the DMA FIFO (DFIFO) register. AND the result with 0x7F for a byte count between zero and 112.

If the DMA FIFO size is set to 816 bytes (using bit 5 of the Chip Test Five (CTEST5) register), subtract the 10 least significant bits of the DMA Byte Counter (DBC) register from the 10-bit value of the DMA FIFO Byte Offset Counter, which consists of bits [1:0] in the Chip Test Five (CTEST5) register and bits [7:0] of the DMA FIFO (DFIFO) register. AND the result with 0x3FF for a byte count between zero and 816.

Step 2. To determine if any bytes are left in the SCSI Output Data Latch (SODL) register, read bit 5 in the SCSI Status Zero (SSTAT0) and SCSI Status Two (SSTAT2) registers.

> If bit 5 is set in the SCSI Status Zero (SSTAT0) or SCSI Status Two (SSTAT2), then the least significant byte or the most significant byte in the SCSI Output Data Latch (SODL) register is full, respectively. Checking this bit also reveals bytes left in the SCSI Output Data Latch (SODL) register from a Chained Move operation with an odd byte count.

Step 3. To determine if any bytes are left in the SODR register (a hidden buffer register which is not accessible), read bit 6 in the SCSI Status Zero (SSTAT0) and SCSI Status Two (SSTAT2) registers.

If bit 6 is set in the SCSI Status Zero (SSTAT0) or SCSI Status Two (SSTAT2), then the least significant byte or the most significant byte in the SODR register is full.

**Asynchronous SCSI Receive** – Follow these steps for asynchronous SCSI receive:

Step 1. To calculate DMA FIFO size:

If the DMA FIFO size is set to 112 bytes, look at the DMA FIFO (DFIFO) and DMA Byte Counter (DBC) registers and calculate if there are bytes left in the DMA FIFO. To make this calculation, subtract the seven least significant bits of the DMA Byte Counter (DBC) register from the 7-bit value of the DMA FIFO (DFIFO) register. AND the result with 0x7F for a byte count between zero and 112.

If the DMA FIFO size is set to 816 bytes (using bit 5 of the Chip Test Five (CTEST5) register), subtract the 10 least significant bits of the DMA Byte Counter (DBC) register from the 10-bit value of the DMA FIFO Byte Offset Counter, which consists of bits [1:0] in the Chip Test Five (CTEST5) register and bits [7:0] of the DMA FIFO (DFIFO) register. AND the result with 0x3FF for a byte count between zero and 816.

- Step 2. To determine if any bytes are left in the SCSI Input Data Latch (SIDL) register, read bit 7 in the SCSI Status Zero (SSTAT0) and SCSI Status Two (SSTAT2) register. If bit 7 is set in the SCSI Status Zero (SSTAT0) or SCSI Status Two (SSTAT2), then the least significant byte or the most significant byte is full.

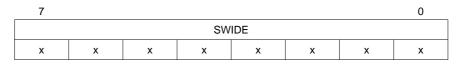

- Step 3. To determine whether a byte is left in the SCSI Wide Residue (SWIDE) register, read the Wide SCSI Receive bit (SCSI Control Two (SCNTL2), bit 0) Synchronous SCSI Receive.

This applies toward any wide transfers that have been performed using the Chained Move instruction.

Follow these steps for synchronous SCSI receive:

Step 1. To calculate DMA FIFO size:

If the DMA FIFO size is set to 112 bytes, subtract the seven least significant bits of the DMA Byte Counter (DBC) register from the 7-bit value of the DMA FIFO (DFIFO) register. AND the result with 0x7F for a byte count between zero and 112.

If the DMA FIFO size is set to 816 bytes (using bit 5 of the Chip Test Five (CTEST5) register), subtract the 10 least significant bits of the DMA Byte Counter (DBC) register from the 10-bit value of the DMA FIFO Byte Offset Counter, which consists of bits [1:0] in the Chip Test Five (CTEST5) register and bits [7:0] of the DMA FIFO (DFIFO) register. AND the result with 0x3FF for a byte count between zero and 816.

- Step 2. Read bits [7:4] of the SCSI Status One (SSTAT1) register and bit 4 of the SCSI Status Two (SSTAT2) register, the binary representation of the number of valid bytes in the SCSI FIFO, to determine if any bytes are left in the SCSI FIFO.

- Step 3. To determine whether a byte is left in the SCSI Wide Residue (SWIDE) register, read the Wide SCSI Receive bit (SCSI

Control Two (SCNTL2), bit 0) LSI53C895 Host Interface Data Paths.

This applies toward any wide transfers that have been performed using the Chained Move instruction.

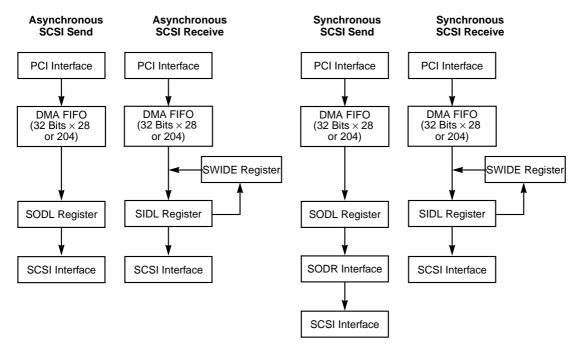

### Figure 2.2 LSI53C895 Host Interface SCSI Datapath

# 2.3 SCRIPTS Processor

The SCSI SCRIPTS processor allows both DMA and SCSI commands to be fetched from host memory or internal SCRIPTS RAM. Algorithms written in SCSI SCRIPTS control the actions of the SCSI and DMA cores and are executed from 32-bit system RAM or internal SCRIPTS RAM. The SCRIPTS processor executes complex SCSI bus sequences independently of the host CPU.

The SCRIPTS processor can begin a SCSI I/O operation in approximately 500 ns. Algorithms may be designed to tune SCSI bus performance to adjust to new bus device types (such as scanners, communication gateways, etc.), or to incorporate changes in the SCSI-2 or SCSI-3 logical bus definitions without sacrificing I/O performance. SCSI SCRIPTS are hardware independent, so they can be used interchangeably on any host or CPU system bus.

## 2.3.1 Internal SCRIPTS RAM

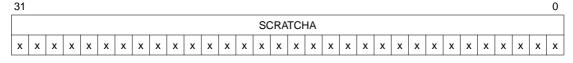

The LSI53C895 has 4 Kbytes (1024 x 32 bits) of internal, general purpose RAM. The RAM is designed for SCRIPTS program storage, but is not limited to this type of information. When the chip fetches SCRIPTS instructions or Table Indirect information from the internal RAM, these fetches remain internal to the chip and do not use the PCI bus. Other types of access to the RAM by the LSI53C895 use the PCI bus as if they were external accesses. The MAD5 pin enables the 4 Kbytes internal RAM, when it is connected to V<sub>DD</sub> through a 4.7 K $\Omega$  resistor. To disable the internal RAM, connect a 4.7 K $\Omega$  resistor between the MAD5 pin and V<sub>SS</sub>.

The PCI system BIOS can relocate the RAM anywhere in a 32-bit address space. The RAM Base Address register in PCI configuration space contains the base address of the internal RAM. This register is similar to the ROM Base Address register in PCI configuration space. To simplify loading of SCRIPTS instructions, the base address of the RAM appears in the Scratch Register B (SCRATCHB) register when bit 3 of the Chip Test Two (CTEST2) register is set. The RAM is byte-accessible from the PCI bus and is visible to any bus-mastering device on the bus. External accesses to the RAM (that is, by the CPU) follow the same timing sequence as a standard slave register access, except that the target wait-states required drops from 5 to 3.

A complete set of development tools is available for writing custom drivers with SCSI SCRIPTS. For more information on the SCSI SCRIPTS instructions supported by the LSI53C895, see Chapter 6, "SCSI SCRIPTS Instruction Set."

# 2.4 Prefetching SCRIPTS Instructions

To enable the prefetch logic, set the Prefetch Enable bit in the DMA Control (DCNTL) register. After doing so, the prefetch logic in the LSI53C895 fetches 8 Dwords of instructions. The prefetch logic automatically determines the maximum burst size that it can perform, based on the burst length as determined by the values in the DMA Mode (DMODE) register. If the burst size is less than four Dwords, the LSI53C895 performs normal instruction fetches. While the LSI53C895 is prefetching SCRIPTS instructions, the PCI Cache Line Size register value does not have any effect and the Memory Read Line, Memory Read Multiple, and Memory Write and Invalidate commands are not used.

The LSI53C895 may flush the contents of the prefetch buffer under certain conditions, listed below, to ensure that the chip always operates from the most current version of the software. When one of these conditions apply, the contents of the prefetch buffer are flushed automatically.

1. On every Memory Move instruction.

The Memory Move instruction is often used to place modified code directly into memory. To make sure that the chip executes all recent modifications, the prefetch buffer flushes its contents and loads the modified code every time an instruction is issued. To avoid inadvertently flushing the prefetch buffer contents, use the No Flush option for all Memory Move operations that do not modify code within the next 8 Dwords. For more information on this instruction, refer to Chapter 6.

2. On every Store instruction.

The Store instruction may also be used to place modified code directly into memory. To avoid inadvertently flushing the prefetch buffer contents, use the No Flush option for all Store operations that do not modify code within the next 8 Dwords.

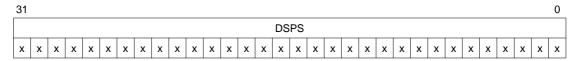

- 3. On every write to the DSP.

- 4. On all Transfer Control instructions.

When the transfer conditions are met, the prefetch buffer is flushed. This is necessary because the next instruction to be executed is not the sequential next instruction in the prefetch buffer.

5. Prefetch Flush bit (DMA Control (DCNTL), bit 6) is set.

The buffer flushes whenever this bit is set. The bit is self-clearing.

## 2.4.1 Op Code Fetch Burst Capability

Setting the Burst Op Code Fetch Enable bit in the DMA Mode (DMODE) register (0x38) causes the LSI53C895 to burst in the first two Dwords of all instruction fetches. If the instruction is a Memory to Memory move, the third Dword is accessed in a separate ownership. If the instruction is an indirect type, the additional Dword is accessed in a subsequent bus ownership. If the instruction is a table indirect block move, the LSI53C895 uses two accesses to obtain the four Dwords required, in two bursts of two Dwords each.

<u>Note:</u> This feature only works if prefetching is disabled.

# 2.5 Designing an Ultra2 SCSI System

Since Ultra2 SCSI is based on existing SCSI standards, it can use existing driver programs as long as the software is able to negotiate for Ultra2 SCSI synchronous transfer rates. Additional software modifications may be needed to take advantage of the new features in the LSI53C895.

In the area of hardware, LVD SCSI is required to achieve Ultra2 SCSI transfer rates and to support the longer cable and additional devices on the bus. All devices on the bus must have LVD SCSI to guarantee Ultra2 SCSI transfer rates. Chapter 7, "Electrical Characteristics," contains Ultra2 SCSI timing information. In addition to the guidelines in the draft standard, make the following software and hardware adjustments to accommodate Ultra2 SCSI transfers:

- Step 1. Set the Ultra Enable bit, bit 7 in the SCSI Control Three (SCNTL3) register, to enable Ultra2 SCSI transfers.

- Step 2. Set the TolerANT Enable bit, bit 7 in the SCSI Test Three (STEST3) register, whenever the Ultra Enable bit is set.

- Step 3. Do not extend the SREQ/SACK filtering period with SCSI Test Two (STEST2), bit 1. When the Ultra Enable bit is set, the filtering period is fixed at 8 ns for Ultra2 SCSI or 15 ns for Ultra SCSI, regardless of the value of the SREQ/SACK Filtering bit.

- Step 4. Use the SCSI clock quadrupler.

# 2.5.1 Using the SCSI Clock Quadrupler

The LSI53C895 can quadruple the frequency of a 40 MHz SCSI clock, allowing the system to perform Ultra2 SCSI transfers. This option is user-selectable with bit settings in the SCSI Test One (STEST1), SCSI Test Three (STEST3), and SCSI Control Three (SCNTL3) registers. At power-on or reset, the quadrupler is disabled and powered down. Follow these steps to use the clock quadrupler:

- Step 1. Set the SCLK Quadrupler Enable bit (SCSI Test One (STEST1), bit 3).

- Step 2. Poll bit 5 of the SCSI Test 4 (STEST4) register. The LSI53C895 sets this bit as soon as it locks in the 160 MHz frequency. The frequency lockup takes approximately 100 microseconds.

- Step 3. Halt the SCSI clock by setting the Halt SCSI Clock bit (SCSI Test Three (STEST3), bit 5).

- Step 4. Set the clock conversion factor using the SCF (bits [6:4]) and CCF (bits [2:0]) fields in the SCSI Control Three (SCNTL3) register.

- Step 5. Set the SCLK Quadrupler Select bit (SCSI Test One (STEST1), bit 2).

- Step 6. Clear the Halt SCSI Clock bit (SCSI Test Three (STEST3), bit 5).

# 2.6 LSI53C895 Interfaces

This section contains information about:

- Parallel ROM Interfaces

- Serial EEPROM Interfaces

- SCSI Bus Interfaces

#### 2.6.1 Parallel ROM Interface

The LSI53C895 supports up to one megabyte of external memory in binary increments from 16 Kbytes, to allow the use of expansion ROM for add-in PCI cards. The device also supports flash ROM updates through the add-in interface and the GPIO4 pin (used to control  $V_{PP}$

which is the power supply for programming external memory). This interface is designed for low-speed operations such as downloading instruction code from ROM; it is not intended for dynamic activities such as executing instructions.

System requirements include the LSI53C895, two or three external 8-bit address holding registers (HCT273 or HCT374), and the appropriate memory device. The 4.7 K $\Omega$  resistors on the Memory Address/Data (MAD) bus require use of HC or HCT external components. If in-system flash ROM updates are required, a 7406 inverter (high voltage open collector inverter), an MTD4P05, and several passive components are also needed. The memory size and speed is determined by pull-up/pull-down configuration on the 8-bit bidirectional memory bus at power up. The LSI53C895 senses this bus shortly after the release of the Reset signal and configures the ROM Base Address register and the memory cycle state machines for the appropriate conditions.

The LSI53C895 supports a variety of sizes and speeds of expansion ROM, using pull-up and pull-down resistors on the MAD[3:0]) pins. Pins MAD[3:1] allow the user to define how much external memory is available to the LSI53C895. Table 2.1 shows the memory space associated with the possible values of MAD[3:1]. The MAD[3:1] pins are fully defined in Chapter 4, "Signal Descriptions." Appendix C, "Circuit Board Layout Issues," shows an example set of interface drawings.

| MAD[3:1] | Available Memory Space     |  |

|----------|----------------------------|--|

| 0b000    | 16 Kbytes                  |  |

| 0b001    | 32 Kbytes                  |  |

| 0b010    | 64 Kbytes                  |  |

| 0b011    | 128 Kbytes                 |  |

| 0b100    | 256 Kbytes                 |  |

| 0b101    | 512 Kbytes                 |  |

| 0b110    | 1024 Kbytes                |  |

| 0b111    | No external memory present |  |

Table 2.1

External Memory Support

To use one of the configurations mentioned above in a host adapter board design, put 4.7 K $\Omega$  pull-up and pull-down resistors on the appropriate MAD pins, corresponding to the available memory space. For example, to connect to a 32 Kbytes external ROM, use pull-downs on MAD(3) and MAD(2) and a pull-up on MAD(1).

The LSI53C895 allows the system to determine the size of the available external memory using the Expansion ROM Base Address register in the PCI configuration space. For more information on how this works, refer to the PCI specification or the Expansion ROM Base Address register description in Chapter 5, "Registers."

MAD(0) is the slow ROM pin. When pulled down, it enables two extra clock cycles of data access time, which allows use of slower memory devices.

The external memory interface also supports updates to flash memory. The 12-volt power supply for flash memory,  $V_{PP}$  is enabled and disabled with the GPIO4 pin and the GPIO4 control bit. For more information on the GPIO4 pin, refer to Chapter 4, "Signal Descriptions."

## 2.6.2 Serial EEPROM Interface

The LSI53C895 implements an interface that allows attachment of a serial EEPROM device to the GPIO0 and GPIO1 pins. Four different modes of operation are possible; each one relates to different values for the serial EEPROM interface, the Subsystem ID register, and the Subsystem Vendor ID register. The modes are programmable through the MAD6 and MAD7 pins, which are sampled at power-up or hard reset.

#### 2.6.2.1 Mode A: 4.7 K $\Omega$ Pull-ups on MAD6 and MAD7

In this mode, GPIO0 is the Serial Data Signal (SDA) and GPIO1 is the Serial Clock Signal (SCL). Certain data in the serial EEPROM is automatically loaded into chip registers at power-up or hard reset.

The format of the serial EEPROM data is defined in Table 2.2. If the EEPROM is not present, or the checksum fails, the Subsystem ID and Subsystem Vendor ID registers read back all zeros. At power-up or hard reset, only five bytes are loaded into the chip from locations 0x00 through 0x04.

#### Table 2.2 Mode A Serial EEPROM Data Format

| Byte      | Description                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00      | Subsystem Vendor ID, LSB. This byte is loaded into the least significant byte of the Subsystem Vendor ID register in PCI configuration space at chip power-up or hard reset.      |

| 0x01      | Subsystem Vendor ID, MSB. This byte is loaded into the most significant byte of the Subsystem Vendor ID register in PCI configuration space at chip power-up or hard reset.       |

| 0x02      | Subsystem ID, LSB. This byte is loaded into the least significant byte of the Subsystem ID register in PCI configuration space at chip power-up or hard reset.                    |

| 0x03      | Subsystem ID, MSB. This byte is loaded into the most significant byte of the Subsystem ID register in PCI configuration space at chip power-up or hard reset.                     |

| 0x04      | Checksum. This 8-bit checksum is formed by adding, bytewise, each byte contained in locations 0x00–0x03 to the seed value 0x55, and then taking the 2's complement of the result. |

| 0x05–0xFF | Reserved.                                                                                                                                                                         |

| 0x100-EOM | Contains user data.                                                                                                                                                               |

#### 2.6.2.2 Mode B: 4.7 K $\Omega$ Pull-down on MAD6, and 4.7 K $\Omega$ Pull-up on MAD7

In this mode, GPIO0 and GPIO1 are each defined as either the SDA or the SCL, since both pins are controlled through software.

No data is automatically loaded into chip registers at power-up or hard reset. The Subsystem ID register and Subsystem Vendor ID registers are read/write, in violation of the PCI specification, with a default value of all zeros.

#### 2.6.2.3 Mode C: 4.7 K $\Omega$ Pull-downs on MAD6 and MAD7

In this mode, GPIO1 is the SDA and GPIO0 is the SCL. Certain data in the serial EEPROM is automatically loaded into chip registers at power-up or hard reset.

The format of the serial EEPROM data is defined in Table 2.3. If the EEPROM is not present, or the checksum fails, the Subsystem ID and Subsystem Vendor ID registers read back all zeros. At power-up or hard

reset, only five bytes are loaded into the chip from locations 0xFB through 0xFF.

| Byte      | Description                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00–0xFA | Contains user data.                                                                                                                                                               |

| 0xFB      | Subsystem Vendor ID, LSB. This byte is loaded into the least significant byte of the Subsystem Vendor ID register in PCI configuration space at chip power-up or hard reset.      |

| 0xFC      | Subsystem Vendor ID, MSB. This byte is loaded into the most significant byte of the Subsystem Vendor ID register in PCI configuration space at chip power-up or hard reset.       |

| 0xFD      | Subsystem ID, LSB. This byte is loaded into the least significant byte of the Subsystem ID register in PCI configuration space at chip power-up or hard reset.                    |

| 0xFE      | Subsystem ID, MSB. This byte is loaded into the most significant byte of the Subsystem ID register in PCI configuration space at chip power-up or hard reset.                     |

| 0xFF      | Checksum. This 8-bit checksum is formed by adding, bytewise, each byte contained in locations 0xFB–0xFE to the seed value 0x55, and then taking the 2's complement of the result. |

| 0x100-EOM | Contains user data.                                                                                                                                                               |

Table 2.3

Mode C Serial EEPROM Data Format

#### 2.6.2.4 Mode D: 4.7 K $\Omega$ Pull-up on MAD6, and 4.7 K $\Omega$ Pull-down on MAD7

This is a reserved mode and should not be used.

## 2.6.3 SCSI Bus Interface

The LSI53C895 performs SE and LVD transfers, and supports traditional (high power) differential operation when the chip is connected to external high power differential transceivers.

To support LVD SCSI, all SCSI data and control signals have a positive and a negative signal line, as in HVD. In SE and HVD operation, the negative signals perform the SCSI data and control function. In HVD mode, the positive signals provide directional control and in SE mode they are virtual ground drivers. TolerANT technology provides signal filtering at the inputs of SREQ/ and SACK/ to increase immunity to signal reflections.

#### 2.6.3.1 LVD Link Technology

To support greater device connectivity and a longer SCSI cable, the LSI53C895 features LVD Link technology, which is the LSI Logic implementation of LVD SCSI. LVD Link transceivers provide the inherent reliability of differential SCSI and a long-term migration path of faster SCSI transfer rates.

LVD Link technology is based on current drive; its low output current reduces the power needed to drive the SCSI bus, so that the I/O drivers can be integrated directly onto the chip. This reduces the cost and complexity compared to traditional (high power) differential designs. LVD Link lowers the amplitude of noise reflections and allows higher transmission frequencies.

The LSI Logic LVD Link transceivers operate in LVD and SE modes. They allow the chip to detect a HVD signal when the chip is connected to external HVD transceivers. The LSI53C895 automatically detects which type of signal is connected, based on voltage detected by the DIFFSENS pin. Bits 7 and 6 of the SCSI Test 4 (STEST4) register contain the encoded value for the type of signal that is detected (LVD, SE, or HVD). Refer to the SCSI Test 4 (STEST4) register description for encoding and other bit information.

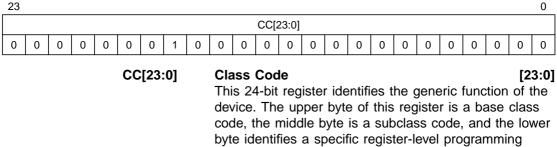

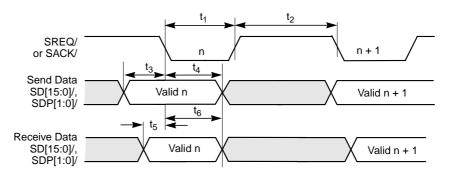

#### 2.6.3.2 HVD Mode