# SANYO Semiconductors DATA SHEET

# LA75521VA—IF Signal Processing (VIF+SIF) IC that Supports the PAL Video Standard for TV Sets and VCRs

#### Overview

The LA75521VA is a fully adjustment-free VIF + SIF signal processing IC for TV sets and VCRs that supports the PAL video standard. It supports 38.0MHz, 38.9MHz, and 39.5MHz as the IF frequencies, as well as PAL sound multi-system (M/N, B/G, I and D/K), and contains an on-chip sound carrier trap. The IC employs a 4MHz frequency (which can be switched to 4.43MHz) as the reference frequency of the adjustment free circuit, and controls the VCO, AFT, and sound filter using an external input signal.

Monolithic Linear IC

#### **Features**

- Internal VCO adjustment free circuit eliminating the need for an external VCO coil.

- Internal sound carrier trap enables easy configuration of PAL sound multi-system at low cost.

- Considerably reduces the number of required peripheral parts.

- Use of digital AFT eliminates a problem of AFT tolerance.

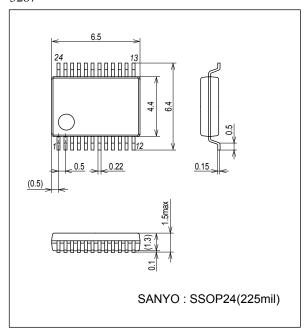

- Package: SSOP24(225mil)

#### **Functions**

- VIF amplifier

- Adjustment-free VCO and PLL detector circuit

- Digital AFT circuit

- RF AGC

- Buzz canceller

- EOAMP

- Internal sound carrier trap

- First SIF detector circuit

- PLL-FM detector circuit

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications of our customer who is considering such use and/or outside the scope of our intended standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

### **Specifications**

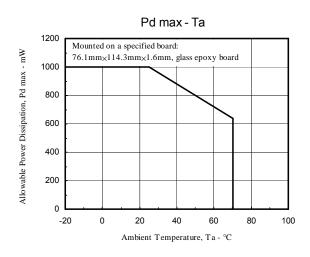

## Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol | Conditions                                | Ratings     | Unit |

|-----------------------------|--------|-------------------------------------------|-------------|------|

| Maximum supply voltage      | VCC    |                                           | 6           | V    |

| Allowable power dissipation | Pd max | Ta ≤ 70°C, Mounted on a specified board.* | 640         | mW   |

| Operating temperature       | Topr   |                                           | -20 to +70  | °C   |

| Storage temperature         | Tstg   |                                           | -55 to +150 | °C   |

<sup>\*:</sup> Mounted on a specified board: 76.1mm×114.3mm×1.6mm, glass epoxy board

### Operating Conditions at $Ta = 25^{\circ}C$

| Parameter                  | Symbol             | Conditions | Ratings    | Unit |

|----------------------------|--------------------|------------|------------|------|

| Recommended supply voltage | V <sub>CC</sub>    |            | 5.0        | V    |

| Operating supply voltage   | V <sub>CC</sub> op |            | 4.5 to 5.5 | V    |

### **Electrical Characteristics** at Ta = 25°C, $V_{CC} = 5.0V$ , fp = 38.9MHz

| Parameter                      | Symbol             | Symbol Conditions        |     |     | Ratings |      | Unit   |

|--------------------------------|--------------------|--------------------------|-----|-----|---------|------|--------|

| raianietei                     | Symbol             | Conditions               | No. | min | typ     | max  | Offic  |

| VIF block                      |                    |                          |     |     |         |      |        |

| Circuit current                | 14                 |                          | V1  | 75  | 85      | 95   | mA     |

| Max RF AGC voltage             | V <sub>14</sub> H  |                          | V2  | 4.0 | 4.5     | 5.0  | V      |

| Min RF AGC voltage             | V <sub>14</sub> L  |                          | V3  | 0.0 | 0.5     | 1.0  | V      |

| Input sensitivity              | Vi                 | Video out 2              | V4  | 26  | 32      | 38   | dBμV   |

| AGC range                      | GR                 |                          | V5  | 58  | 63      |      | dB     |

| Max allowable input            | V <sub>i</sub> max |                          | V6  | 95  | 100     |      | dBμV   |

| Quiescent video output voltage | V <sub>5</sub>     |                          | V7  | 2.2 | 2.5     | 2.8  | V      |

| Sync signal edge voltage       | V <sub>5</sub> tip |                          | V8  | 0.8 | 1.0     | 1.2  | V      |

| Video output level             | v <sub>O</sub>     |                          | V9  | 1.0 | 1.2     | 1.4  | Vp-p   |

| Black noise threshold voltage  | V <sub>BTH</sub>   |                          | V10 | 0.5 | 0.8     | 1.1  | V      |

| Black noise clamp voltage      | $V_{BCL}$          |                          | V11 | 1.2 | 1.5     | 1.8  | ٧      |

| Video S/N                      | S/N                | B/G                      | V12 | 46  | 50      |      | dB     |

| C-S best                       | IC-S               | P/S = 10dB               | V13 | 38  | 43      |      | dB     |

| Differential gain              | DG                 | V <sub>IN</sub> = 80dBμ  | V14 |     | 3       | 6.5  | %      |

| Differential phase             | DP                 |                          | V15 |     | 3       | 5    | deg    |

| Quiescent AFT voltage          | V <sub>12</sub>    | 15pin to V <sub>CC</sub> | V16 | 2.0 | 2.5     | 3.0  | V      |

| Max AFT voltage                | V <sub>12</sub> H  | LOAD 22kΩ/22kΩ           | V17 | 4   | 4.5     | 5    | V      |

| Min AFT voltage                | V <sub>12</sub> L  | LOAD 22kΩ/22kΩ           | V18 | 0   | 0.5     | 1    | V      |

| AFT sensitivity                | SF                 | LOAD 22kΩ/22kΩ           | V19 | 8.5 | 12.5    | 16.5 | mV/kHz |

| APC pull-in range (U)          | Fpu                |                          | V20 | 2.0 | 2.4     |      | MHz    |

| APC pull-in range (L)          | FpI                |                          | V21 |     | -2.4    | -2.0 | MHz    |

| VCO control sensitivity        | β                  |                          | V22 | 3   | 6       | 12   | kHz/mV |

| VIF input resistance           | Rį                 | 38.9MHz                  | V23 |     | 1.0     | 1.5  | kΩ     |

| VIF input capacity             | Ci                 | 38.9MHz                  | V24 |     | 3       | 6    | pF     |

| N trap1 (4.5M)                 | NT1                | wrt 1MHz                 | V25 | -30 | -35     |      | dB     |

| N trap2 (4.8M)                 | NT2                | wrt 1MHz                 | V26 | -19 | -24     |      | dB     |

| BG trap1 (5.5M)                | BT1                | wrt 1MHz                 | V27 | -27 | -32     |      | dB     |

| BG trap2 (5.85M)               | BT2                | wrt 1MHz                 | V28 | -20 | -25     |      | dB     |

| I trap1 (6.0M)                 | IT1                | wrt 1MHz                 | V29 | -25 | -30     |      | dB     |

| I trap2 (6.55M)                | IT2                | wrt 1MHz                 | V30 | -15 | -20     |      | dB     |

| DK trap1 (6.5M)                | DT1                | wrt 1MHz                 | V31 | -25 | -30     |      | dB     |

| Group delay 1 NTSC (3.0M)      | NGD1               | wrt 1MHz                 | V32 | 30  | 80      | 145  | ns     |

| Group delay 1-1 NTSC (3.5M)    | NGD1-1             | wrt 1MHz                 | V33 | 110 | 200     | 290  | ns     |

| Group delay 2 BG (4M)          | BGD2               | wrt 1MHz                 | V34 | 50  | 130     | 210  | ns     |

| Group delay 2-1 BG (4.4M)      | BGD2-1             | wrt 1MHz                 | V35 | 120 | 200     | 280  | ns     |

| Parameter                                   | Symbol                    | Conditions              | No. |      | Ratings |     | Unit      |

|---------------------------------------------|---------------------------|-------------------------|-----|------|---------|-----|-----------|

| Parameter                                   | Symbol                    | Conditions              | NO. | min  | typ     | max | Offic     |

| Group delay 3 I (4M)                        | IGD3                      | wrt 1MHz                | V36 | 0    | 80      | 130 | ns        |

| Group delay 3-1 I (4.4M)                    | IGD3-1                    | wrt 1MHz                | V37 | 80   | 120     | 160 | ns        |

| Group delay 4 DK (4M)                       | DGD4                      | wrt 1MHz                | V38 | 10   | 30      | 50  | ns        |

| Group delay 4-1 DK (4.4M)                   | DGD4-1                    | wrt 1MHz                | V39 | 30   | 60      | 90  | ns        |

| Video f characteristics MN1                 | VFMN1                     | M/N 1 to 2MHz           | V40 | -1.0 | 0.0     | 1.0 | dB        |

| Video f characteristics MN2                 | VFMN2                     | M/N 2 to 3MHz           | V41 | -1.0 | 0.0     | 1.0 | dB        |

| Video f characteristics MN3                 | VFMN3                     | M/N 3.58MHz             | V42 | -3.0 | -1.5    | 0.0 | dB        |

| Video f characteristics BG1                 | VFBG1                     | B/G 1 to 3MHz           | V43 | -1.0 | 0.0     | 1.5 | dB        |

| Video f characteristics BG2                 | VFBG2                     | B/G 3 to 4MHz           | V44 | -1.5 | 0.0     | 1.5 | dB        |

| Video f characteristics BG3                 | VFBG3                     | B/G 4.43MHz             | V45 | -2.5 | -1.0    | 0.5 | dB        |

| Video f characteristics I1                  | VFI1                      | I 1 to 3MHz             | V46 | -1.0 | 0.0     | 1.0 | dB        |

| Video f characteristics I2                  | VFI2                      | I 3 to 4MHz             | V47 | -1.0 | 0.0     | 1.5 | dB        |

| Video f characteristics I3                  | VFI3                      | I 4.43MHz               | V48 | -1.5 | 0.0     | 1.5 | dB        |

| Video f characteristics DK1                 | VFDK1                     | D/K 1 to 3MHz           | V49 | -1.0 | 0.0     | 1.0 | dB        |

| Video f characteristics DK2                 | VFDK2                     | D/K 3 to 4MHz           | V50 | -1.0 | 0.0     | 1.5 | dB        |

| Video f characteristics DK3                 | VFDK3                     | D/K 4.43MHz             | V51 | -1.5 | 0.0     | 1.5 | dB        |

| Group delay 2-2 BG shift (4M)               | BGD2-2                    | wrt 1MHz                | V52 | 50   | 100     | 150 | ns        |

| Group delay 2-3 BG shift (4.4M)             | BGD2-3                    | wrt 1MHz                | V53 | 110  | 180     | 250 | ns        |

| 1st SIF Block                               | <u>I</u>                  | <u>l</u>                |     | -    |         |     |           |

| SIF carrier output level 1                  | So1                       | V <sub>i</sub> = 1mV    | F1  | 21   | 43      | 86  | mVrms     |

| SIF carrier output level 2                  | So2                       | V <sub>i</sub> = 10mV   | F2  | 21   | 43      | 86  | mVrms     |

| 1st SIF max input                           | Si max                    | 1 10000                 | F3  | 110  | 120     |     | dΒμV      |

| 1st SIF input resistance                    | Ris                       | 33.4MHz                 | F4  | 110  | 2       | 2.4 | kΩ        |

| 1st SIF input capacity                      | Cis                       | 33.4MHz                 | F5  |      | 3       | 6   | pF        |

| SIF Block                                   |                           | 1 *********             |     |      | 0       | · · | · ·       |

| Limiting sensitivity (SPLIT)                | V <sub>i</sub> (lim) (SP) | P = 80dBμ CW            | S1  | 20   | 25      | 30  | dΒμV      |

| Limiting sensitivity (INTER)                | V <sub>i</sub> (lim) (IN) | P = 80dBμ P/S           | S2  | 29   | 35      | 41  | dB        |

| FM detection output voltage                 | V <sub>O</sub> (FM)       | f = 5.5MHz, ΔF = ±30kHz | S3  | 390  | 560     | 730 | mVrms     |

| AM removal ratio                            | AMR                       | ,                       | S4  | 50   | 60      |     | dB        |

| Distortion factor                           | THD                       |                         | S5  |      | 0.3     | 0.8 | %         |

| FM detection output S/N                     | S/N (FM)                  | P = 80dBµ CW            | S6  | 55   | 60      | 0.0 | dB        |

| PAL/NT audio voltage gain difference        | GD GD                     | . σσαμεστι              | S7  |      | 6       |     | dB        |

| PAL De-emphasis                             | Pdeem                     |                         | S8  |      | -3      |     | dB        |

| NT De-emphasis                              | Ndeem                     |                         | S9  |      | -3      |     | dB        |

| Control Block                               |                           |                         |     |      | · ·     |     |           |

| SIF system SW threshold voltage A/B         | V7_9th                    |                         | C1  | 2.2  | 2.5     | 2.8 | V         |

| 38MHz/38.9MHz threshold voltage             | V1_5ti1                   |                         | C2  | 0.7  | 1.0     | 1.3 |           |

| 38.9MHz/39.5MHz threshold voltage           | V10th2                    |                         | C3  | 3.7  | 4.0     | 4.3 |           |

| Inter-carrier system                        | V13th                     |                         | C4  | 5.1  | 4.0     | 0.3 |           |

| AFT mute level/SIF trap shift               | V15th1                    |                         | 04  |      |         | 0.5 | · ·       |

| threshold voltage 1                         | Violiti                   |                         | C5  | 0.7  | 1.0     | 1.3 | V         |

| AFT mute level/SIF trap shift               | V15th2                    |                         |     | 0.0  | 0.5     | 0.0 | V         |

| threshold voltage 2                         |                           |                         | C6  | 2.2  | 2.5     | 2.8 | V         |

| AFT mute level/SIF trap shift               | V15th3                    |                         | C7  | 3.7  | 4.0     | 4.3 | V         |

| threshold voltage 3                         |                           |                         |     |      |         |     |           |

| Others                                      | D.O.                      | 4 0 1 1 1 -             |     |      |         |     | .=        |

| Ref clock input level                       | Reflev                    | 4.0MHz                  | 01  | 83   | 90      | 95  | dBμV      |

| Reference frequency SW threshold resistance | R11                       |                         | O2  | 150  | 270     |     | $k\Omega$ |

### **Package Dimensions**

unit: mm (typ)

3287

### System changeover

#### a. SIF system SW

The SIF system changeover can be made by connecting both/either A (pin 7) and/or B (pin 9) to GND or by keeping both or either of them OPEN.

| А    | В    | BG | I | DK | MN | FM DET LEVEL | de-emphasis |

|------|------|----|---|----|----|--------------|-------------|

| GND  | GND  |    |   | 0  |    | 0dB          | 50µs        |

| GND  | OPEN | 0  |   |    |    | 0dB          | 50µs        |

| OPEN | GND  |    | 0 |    |    | 0dB          | 50µs        |

| OPEN | OPEN |    |   |    | 0  | 6dB          | 75µs        |

Note: O indicates that the system is selected.

#### b. IF system SW

The IF frequency becomes 38.9MHz when pin 10 is open.

The IF frequency changes to 38.0MHz when pin 10 is connected to GND.

This frequency also changes to 39.5MHz when pin 10 is set to V<sub>CC</sub>.

#### c. split/inter carrier SW

Inter carrier is selected by connecting the 1st SIF input (pin 13) to GND.

#### d. Reference frequency changeover SW

The frequency becomes 4.43MHz when pin 11 is open.

The frequency becomes 4.0 MHz when  $270 k\Omega$  is connected between pin 11 and GND.

#### e. AFT mute level, TRAP point shift

By changing the voltage of pin 15, the potential when AFT is muted and the TRAP point of either "just" or "shift" (about +220kHz) can be selected.

| Pin 15 potential      | AFT mute potential          | TRAP point shift |

|-----------------------|-----------------------------|------------------|

| V <sub>CC</sub> to 4V | MIDDLE (V <sub>CC</sub> /2) | Just             |

| 4V to 2.5V            | MIDDLE (V <sub>CC</sub> /2) | Shift            |

| 2.5V to 1V            | HI (V <sub>CC</sub> )       | Just             |

| 1V to GND             | HI (V <sub>CC</sub> )       | Shift            |

<sup>\*</sup> With  $V_{CC} = 5V$

When the SIF circuit is not used and the FM detection VCO is to be stopped, short-circuit pin 1 - GND with the resistance of  $1k\Omega$  or less.

f. When the FM detection function is not used

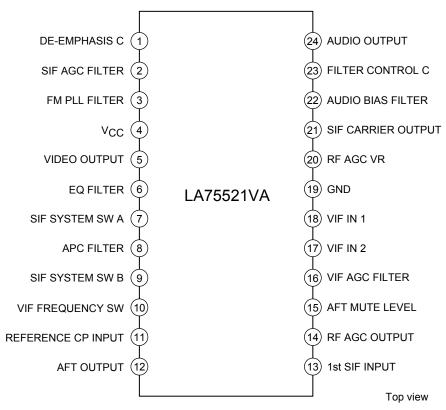

#### **Pin Assignment**

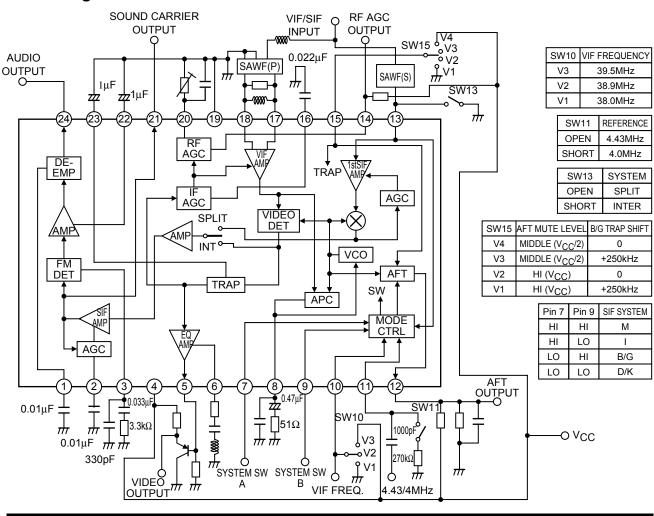

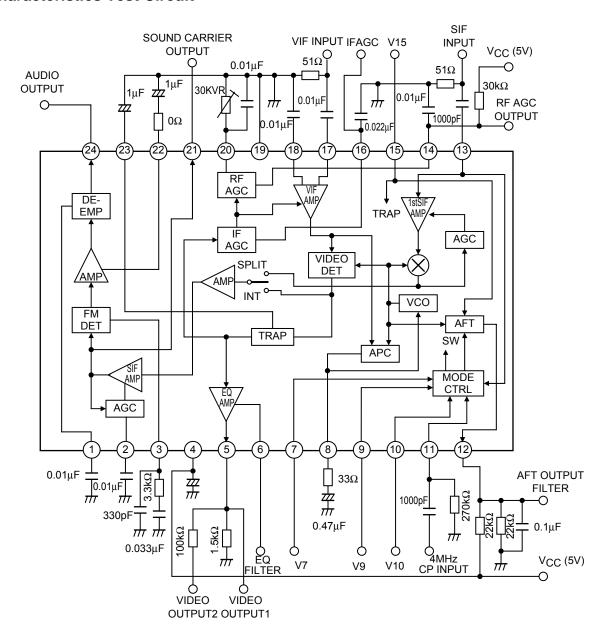

### **Block Diagram**

### **AC Characteristics Test Circuit**

## **Test Circuit**

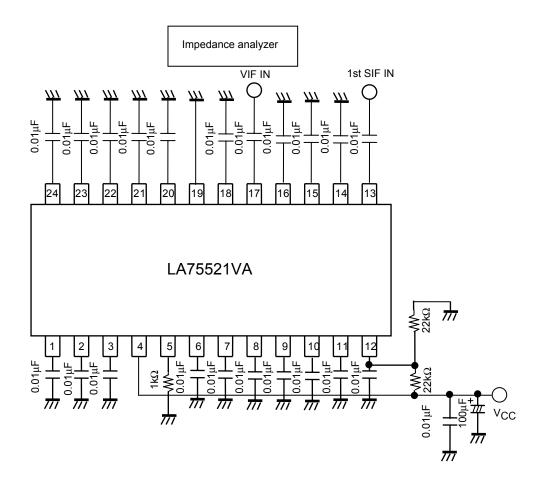

Input Impedance Test Circuit (VIF and first SIF input impedance)

#### **Pin Functions**

| ions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin name Function Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| This is used to switch the equivalent resistance $(5k\Omega \text{ or } 7.5k\Omega)$ internally in the IC to select the time constant.  This switching is linked to the SIF input switch.  To disable de-emphasis, disconnect the capacitor.  Connection of an external capacitance of $0.01\mu\text{F}$ enables switching between 50 and 75 $\mu\text{s}$ .  When the FM detector circuit is not to be used, the FM VCO can be stopped by connecting it to ground with a resistor of $1k\Omega$ or less.                                                                                                                                                                                                                                     |

| AGC FILTER AGC filter pin for SIF carrier $0.01\mu F$ is recommended for C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PLL filter pin of FM detector This is used to configure an external lag lead filter. Example: Connect 330pF in parallel with the filter $(0.033\mu\text{F} + 3.3\text{k}\Omega)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Power supply  Equalizer circuit. This circuit is used to correct the video signal frequency characteristics.  Notes on equalizer amplifier design  • The equalizer amplifier is designed as a voltage follower amplifier with a gain of about 0 dB. When used for frequency characteristics correction, a capacitor, inductor, and resistor must be connected in series between pin 6 and ground.  Equalizer amplifier gain AV = \frac{R1}{Z} + 1  R1 is the IC internal resistance, and is 1kΩ. In the application design, simply select Z to correspond to the desired characteristics. However, since the EQ amplifier gain will be maximum at the resonant point defined by Z, care is required to assure that distortion does not occur. |

| Power supply  Equalizer circuit. This circuit is used to correct the video signal frequency characteristics.  Notes on equalizer amplifier design  • The equalizer amplifier is designed as a voltage follower amplifier with a gain of about 0 dB. When used for frequency characteristics correction, a capacitor, inductor, and resistor must be connected in series between pin 6 and ground.  Equalizer amplifier gain AV = R1/Z + 1  R1 is the IC internal resistance, and is 1kΩ. In the application design, simply select Z to correspond to the desired characteristics. However, since the EQ amplifier gain will be maximum at the resonant point defined by Z, care is required to                                                |

Continued from preceding page. Pin name Function **Equivalent Circuit** No SIF SYSTEM SW A 7 SIF system selection switch pins. Combining the 9 SIF SYSTEM SW B settings of these two pins supports four systems. In M/N mode, the audio output level is increased ∫ ≨ 50kΩ  $50k\Omega$ by 6dB. ≸ 1kΩ 1kΩ The internal trap is also linked to these switches. The truth-values are as follows: MODE Pin 7 Pin 9 1kΩ  $1 k\Omega$ Н 80kΩ  $80k\Omega$ В 9 1 Н L L Н B/G L D/K  $30k\Omega$  $30k\Omega$ APC FILTER 8 PLL APC filter connection pin. The APC count is switched internally in the IC. The VCO is normally controlled by route A. **FROM** APC When unlocked and during weak field reception, DET the VCO is controlled by route B and the loop gain is increased.  $1k\Omega$ For this APC filter we recommend a resistor of  $51\Omega$ and capacitor of 0.47µF. The buzz characteristics can be improved by В connecting a capacitor of 100pF or so between pins 5 and 8. 8 VIF FREQUENCY SW 10 Switch pin for selecting the IF frequency When this pin is open,  $1/2V_{CC}$  exists.  $50k\Omega$ V<sub>CC</sub>: 39.5MHz Open: 38.9MHz GND: 38.0MHz  $11k\Omega$  $50k\Omega$ REFERENCE CP 11 Reference signal input pin necessary for adjusting INPUT the internal sound carrier trap, AFT, etc. Either 4.0 or 4.43MHz can be selected. Use the configuration shown in example 1 when using 4.43MHz and configuration shown in example 2 **≸** 200kΩ when using 4.0MHz. Since no oscillator can be configured simply by connecting the X'tal resonator to pin 11, input the reference signal from an external source without Example 1 Example 2 11 1000pF 1000pF  $270k\Omega$ 4.43M 4.0MHz

Continued from preceding page.

| Continued  | from preceding page. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                         |

|------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Pin<br>No. | Pin name             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Equivalent Circuit                                      |

| 12         | AFT OUTPUT           | AFT output pin. The AFT center voltage is generated by an external bleeder resistor. The AFT gain is increased by increasing the resistance of this external bleeder resistor. For the resistor we recommend a resistance equal to or greater than $22k\Omega.$ For the filter C1 we recommend a capacitance of $0.1\mu F.$                                                                                                                                                                                                                     | R \$ 500Ω R \$ TC1                                      |

| 13         | 1st SIF INPUT        | First SIF input pin. A DC cut capacitor must be used in the input circuit.  (a) If a SAW filter is used:  The first SIF sensitivity can be increased by inserting an inductor between the SAW filter and the IC to neutralize the SAW filter output capacitance and the IC input capacitance.  (b) When used in an intercarrier system:  Connect this pin to ground.                                                                                                                                                                            | 2kΩ / / / / / / / / / / / / / / / / / / /               |

| 14         | RF AGC OUTPUT        | RF AGC output pin. This output controls the tuner RF AGC. This is the open collector output and a protective $200\Omega$ resistor is inserted. Determine the external bleeder resistor value in accordance with the specifications of the tuner.                                                                                                                                                                                                                                                                                                | VCC 200Ω 14 200Ω 11 11 11 11 11 11 11 11 11 11 11 11 11 |

| 15         | AFT MUTE LEVEL       | A switch pin for selecting the mute potential when muting is applied to the AFT due to PLL unlock, etc. At the same time, it is used to control the trap point shift of the audio trap (in the B/G mode). When the frequency characteristics of the video band are to be made as flat as possible with the split input, the trap can be shifted to the high range although the attenuation of the sound carrier will drop. Therefore, when used in combination with the SAW filter, verify that the level is high enough before use.    Voltage | \$ 66kΩ<br>15<br>34kΩ                                   |

Continued from preceding page.

|            | from preceding page. |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

|------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Pin<br>No. | Pin name             | Function                                                                                                                                                                                                                                                                                                                                                                                                  | Equivalent Circuit                                                         |

| 16         | IF AGC               | IF AGC filter connection pin.  The signal peak-detected by the built-in AGC detector is converted to the AGC voltage at pin 16.  Additionally, a second AGC filter (a lag-lead filter) used to create the dual time constants is provided internally in the IC.  Use a 0.022μF capacitor as the external capacitor (C1), and adjust the value according to the sag, AGC speed, and other characteristics. | 16<br>16<br>1π<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10 |

| 17<br>18   | VIF IN1              | VIF amplifier input pin   The input circuit is a balanced circuit, and the input impedance is as follows: $R\approx 1.0 k\Omega$                                                                                                                                                                                                                                                                          | 17 \$1kΩ \$1kΩ<br>18 ### ### ### ### ### ### ### ### ### #                 |

| 19         | GND                  |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| 20         | RF AGC VR            | RF AGC volume connection pin This pin sets the tuner RF AGC operating point. Also, the FM output and the video output can both be muted at the same time by connecting this pin to ground.                                                                                                                                                                                                                | 1kΩ                                                                        |

| 21         | SIF CARRIER<br>OUT   | First SIF output pin This is an emitter-follower output with a $200\Omega$ resistor attached in series.                                                                                                                                                                                                                                                                                                   | 21<br>200Ω                                                                 |

Continued from preceding page.

| Continued  | from preceding page. |                                                                                                                                                                                                                                                                |                                         |

|------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Pin<br>No. | Pin name             | Function                                                                                                                                                                                                                                                       | Equivalent Circuit                      |

| 22         | AUDIO BIAS<br>FILTER | Connection pin for a filter used to hold the FM detector output DC voltage fixed. Normally, a 1µF electrolytic capacitor should be used. The capacitance (CI) should be increased if the low band (around 50Hz) frequency characteristics need to be improved. | 300Ω 40kΩ<br>40kΩ<br>## C1              |

| 23         | FILTER CONTROL C     | Internal filter (trap) control pin Connect a capacitor with a capacitance between 0.47 to 1 $\mu$ F, depending on the video S/N as well as the levels of the AM and PM noise.                                                                                  | 23                                      |

| 24         | AUDIO OUTPUT         | Sound output pin Emitter follower output                                                                                                                                                                                                                       | 24 ———————————————————————————————————— |

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of February, 2008. Specifications and information herein are subject to change without notice.