1 Pep 1 5 Van

# Extended PCM Interface Controller (EPIC™)

Data Sheet

Revision TM 8/89

Publications Rev. Amendment

11149D/0

lesue Date: May 1990

# O. GENERAL

Upstream:

Direction from the subscriber to the PCM highways in the exchange.

Downstream:

Direction from the PCM highways to the subscribers.

Time Slot:

Defined period of time in the PCM, IOM or SLD frame consisting of 8 bits. Time slots are allocated to the frames in such away that the time slot boundaries coincide with the frame boundaries. The time slots do not overlap. The lowest time slot number is 0. This time slot is the first in the frame.

Sub Time Slot:

A quarter or half a time slot. These are allocated to the time slots in such a way that time slot and subtime slot boundaries match. The subtime slots

are non overlapping.

Channel:

Sequence of bits which is exchanged between the subsriber, the exchange equipment and/or the microprocessor. It occupies a defined number of bits at a defined position within a frame as long as a connection pervails. Both time slots and subtime slots are channels and hence a channel may offer a bandwidth of 16, 32 or 64 kbps.

Bit Numbering:

The bits in a time slot are numbered 7 (MSB) through 0 (LSB). Bit 7 is the

first bit to be transmitted or received, bit 0 the last.

### 1. Introduction

### 1.1. Features

- Board Controller for up to 32 ISDN or 64 voice subscribers

- Nonblocking switch for 128 channels (16, 32, or 64 kbps bandwidth)

- \* Two consecutive 64 kbps channels can be switched as a single 128 kbps channel.

- Timesiot assignment freely programmable for all connected subscribers

- Two serial interfaces (PCM and Configurable)

- Programmable for a wide range of data rates (8 to 8192 kbps)

- Data rates of PCM and configurable interfaces independent from each other (data rate adaption)

- Single and double rate clock selectable

- PCM interface

- Tristate control signals for external drivers

- Programmable clock shift

- Configurable Interface

- Configurable for IOM compatible devices (4 duplex ports)

- Configurable for SLD compatible devices (8 bidirectional I/O ports)

- Configurable for PCM applications

- Standard μP interface with multiplexed address/data bus or seperate address and data buses (PLCC 44)

- Handling of layer 1 functions

- Change detection and last-look logic for C/I (IOM configuration) or feature control (SLD configuration) channels

- Buffered monitor (IOM configuration) or signaling channel (SLD configuration)

- Comfortable µP access to two selected channels

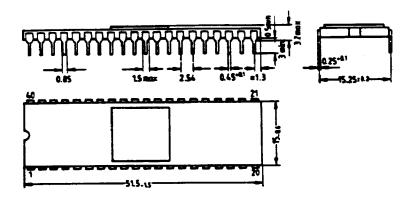

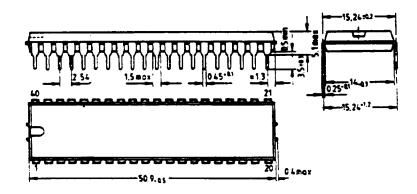

- 40 pin Dual in Line or 44 pin PLCC package

- Advanced low power CMOS technology

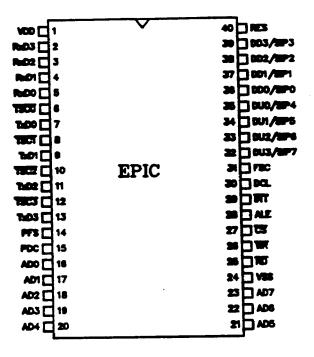

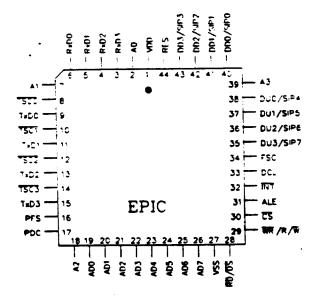

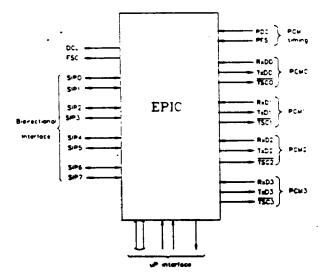

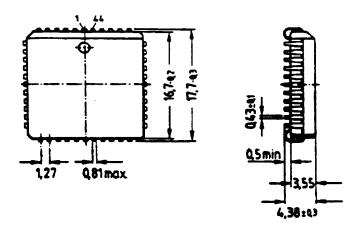

# 1.2. Pin Configuration

Fig. 1.1: Pin Configurations (top view)

### 1.3. General Device Overview

The Extended PCM Interface Controller EPIC™ (PEB 2055) is a monolithic switching device for the path control of up to 128 channels of 16, 32 or 64 kbps bandwidth. Two consecutive 64 kbps channels may also be handled as a quasi single 128 kbps channel. For these channels the EPIC performs nonblocking space time switching between two serial interfaces, the system and the configurable interface.

Both interfaces can be programmed to operate at different data rates between 8 and 8192 kbps. The system interface consists of up to four duplex ports with a tristate indication signal for each output line. The configurable interface can be selected to incorporate either four duplex or eight bidirectional I/O ports (SLD).

The EPIC can therefore be programmed to communicate either with SLD or with IOM (ISDN oriented modular) compatible devices. In both cases the device handles the layer 1 functions buffering the C/I and monitor channels for IOM compatible devices and the feature control and signaling channels for SLD compatible devices.

Due to its capability to switch channels of different bandwidths, the EPIC can handle up to 32 ISDN subscribers with their 2B + D channel structure in IOM configuration or up to 16 subscribers in SLD configuration. Since its interfaces can operate at different data rates, the EPIC is an ideal device for data rate adaption.

Moreover, the EPIC is one of the fundamental building blocks for networks with either central, decentral or mixed signaling and packet data handling architectures. The other key devices are the IDEC® (ISDN D-channel Exchange Controller, PEB 2075) and the HSCX (Enhanced High Level Serial communication Controller, SAB 82525).

Applications of the EPIC include communication multiplexers, concentrators, central switches as well as peripheral ISDN and analog line cards.

The EPIC is available in a DIP/DIC 40 or a PLCC 44 package.

The DIP/DIC 40 version is controlled by a standard 8 bit parallel microprocessor interface with a multiplexed address-data bus. In the PLCC 44 package the device may optionally be controlled by seperate address and data buses.

# 1.4. Pin Definitions and Functions

| Symbol                       | PIN No.<br>DIP     | Pin No.<br>PLCC     | Тур                                                 | Function                                                                                                                                                                                                                                        |  |

|------------------------------|--------------------|---------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                              |                    |                     | Input (I) Output (O) In/Output (IO) Open Drain (OD) |                                                                                                                                                                                                                                                 |  |

| VDD                          | 1                  | 1                   | 1                                                   | Supply Voltage 5V ± 5%                                                                                                                                                                                                                          |  |

| AO                           | -                  | 2                   | I                                                   | Address Bus Bit 0: This input interface to the system's address bus to select a internal register for a read or writ access. This pin is only provided in the PLCC package and only active if demultiplexed µP interface mode selected.         |  |

| RxD3<br>RxD2<br>RxD1<br>RxD0 | 2<br>3<br>4<br>5   | 3<br>4<br>5<br>6    |                                                     | Receive PCM interface Data: Serial data is received at these lines at standard TTL or CMOS levels.                                                                                                                                              |  |

| A1                           |                    | 7                   | 1                                                   | Address Bus Bit 1: This input interfaces to the system's address bus to select an internal register for a read or write access. This pin is only provided in the PLCC package and only active if a demultiplexed µP interface mode is selected. |  |

| TSC0<br>TSC1<br>TSC2<br>TSC3 | 6<br>8<br>10<br>12 | 8<br>10<br>12<br>14 | 0                                                   | Tristate control for the PCM interface. These lines are low when the corresponding TxD outputs are valid.                                                                                                                                       |  |

| TxD0<br>TxD1<br>TxD2<br>TxD3 | 7<br>9<br>11<br>13 | 9<br>11<br>13<br>15 | 0                                                   | Transmit PCM interface Data: Serial data is sent by these lines at standard TTL or CMOS levels. These pins can be tristated.                                                                                                                    |  |

| PFS                          | 14                 | 16                  | ı                                                   | PCM interface frame synchronization pulse.                                                                                                                                                                                                      |  |

| PDC                          | 15                 | 17                  | ı                                                   | PCM interface data clock, single or double rate.                                                                                                                                                                                                |  |

|                                                      | T                                            | T                                            | . T | A44                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------|----------------------------------------------|----------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2                                                   | -                                            | 18                                           |     | Address Bus Bit 2: This input interfaces to the system's address bus to select an internal register for a read or write access. This pin is only provided in the PLCC package and only active if a demultiplexed $\mu P$ interface mode is selected.                                                                                                                      |

| AD0<br>AD1<br>AD2<br>AD3<br>AD4<br>AD5<br>AD6<br>AD7 | 16<br>17<br>18<br>19<br>20<br>21<br>22<br>23 | 19<br>20<br>21<br>22<br>23<br>24<br>25<br>26 | 1/0 | Address Data Bus. If the multiplexed address/data $\mu P$ interface bus mode is selected these pins transfer data and commands between the $\mu P$ and the EPIC.  If a demultiplexed mode is used, these bits interface with the system data bus.                                                                                                                         |

| vss                                                  | 24                                           | 27                                           | I   | Ground: 0V                                                                                                                                                                                                                                                                                                                                                                |

| RD                                                   | 25                                           | 28                                           | ı   | Read: The signal indicates a read operation, active low.                                                                                                                                                                                                                                                                                                                  |

| WR                                                   | 26                                           | 29                                           | l   | Write: This signal indicates a write operation, active low.                                                                                                                                                                                                                                                                                                               |

| <del>cs</del>                                        | 27                                           | 30                                           | l   | Chip select. A low on this line selects the EPIC for a read/write operation.                                                                                                                                                                                                                                                                                              |

| ALE                                                  | 28                                           | 31                                           | 1   | Address latch enable. In the Intel type multiplexed $\mu P$ interface mode a logical high on this line indicates an address of an EPIC internal register on the external address/data bus. In the Intel type demultiplexed $\mu P$ interface mode this line is hardwired to VSS, in the demultiplexed Motorola type $\mu P$ interface mode it should be connected to VDD. |

| INT                                                  | 29                                           | 32                                           | OD  | Interrupt line, active low                                                                                                                                                                                                                                                                                                                                                |

| DCL                                                  | 30                                           | <b>3</b> 3                                   | 10  | Data clock input or output in IOM/slave clock in SLD configuration.                                                                                                                                                                                                                                                                                                       |

| FSC                                                  | 31                                           | 34                                           | 10  | Frame synchronization input or output<br>in IOM configuration / Direction indica-<br>tion signal in SLD configuration.                                                                                                                                                                                                                                                    |

| DU3/SIP7<br>DU2/SIP6<br>DU1/SIP5<br>DU0/SIP4         | 32<br>33<br>34<br>35                         | 35<br>36<br>37<br>38                         | NO  | Data Upstream Input In 10M configuration. Serial Interface port 4, 5, 6 and 7 in bidirectional configuration.                                                                                                                                                                                                                                                             |

| A3                                           | •                      | 39                   | l   | Address Bus Bit 3: This input interfaces to the system's address bus to select an internal register for a read or write access. This pin is only provides in the PLCC package and only active if a demultiplexed $\mu P$ interface mode is selected. |

|----------------------------------------------|------------------------|----------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DD0/SiP0<br>DD1/SiP1<br>DD2/SiP2<br>DD3/SiP3 | SIP1 37 4<br>SIP2 38 4 | 40<br>41<br>42<br>43 | ONO | Data Downstream outputs in IOM configuration. Serial interface ports 0, 1, 2 and 3 in bidirectional configuration.                                                                                                                                   |

| RES                                          | 40                     | 44                   | 1   | Reset. A logical high on this input forces the EPIC into the reset state.                                                                                                                                                                            |

Tab. 1.1: Pin Listing

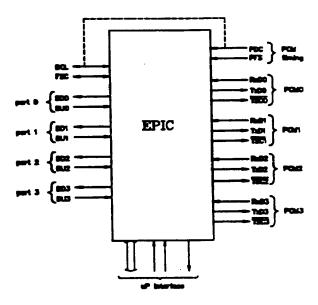

# 1.5. Logic Symbol

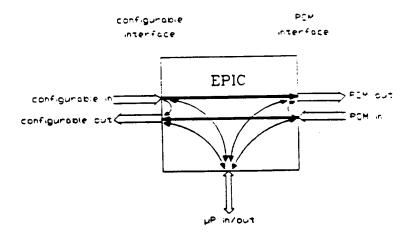

Fig. 1.2: Functional Symbol for the Duplex Configuration

Fig. 1.3: Functional Symbol for the Bidirectional Configuration

# 1.6. System Integration

### 1.6.1. Communication Multiplexers

The nonbiocking switching capability for various bandwidths implemented in the EPIC makes the circuit suitable for use in communication multiplexers. Due to the data rate programmability of the configurable and PCM interfaces data rate adaption (e.g. between 1544 and 2048 kbps systems) can be accomplished.

### 1.6.2. Concentrators

Due to the high data rates of up to 8192 kbps the EPIC can be used in concentrator applications.

### 1.6.3. Central Switches

The EPIC is a nonblocking switch for up to 128 channels per direction. The channel bandwidth can be programmed to 16, 32 or 64 kbps. The PCM and configurable interfaces are programmable for a wide variety of data rates from 8 to 8192 kbps. PCM and configurable interfaces can be operated with different clock frequences. Thus, the EPIC can be used in central switches and for data rate adaption.

### 1.6.4. Line Cards

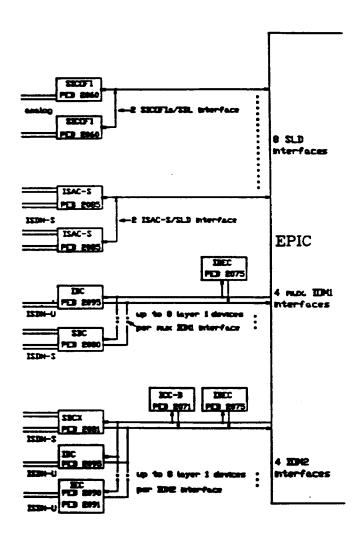

The EPIC is designed to operate in 3 different digital or analog line card architectures. For a schematic summary of these possible line card configurations refer to figure 1.4

With its <u>configurable interface</u> being programmed as a <u>SLD interface</u>, it can communicate with SLD compatible devices (e.g. Siemens Codec Filter, SICOFI<sup>3</sup>, PEB 2060 or ISDN Subscriber Access Controller ISAC<sup>3</sup>-S, PEB 2085). Connected to up to 16 SICOFIs, the EPIC can serve up to 16 analog lines. Used together with ISAC-Ss, the EPIC provides the signals for up to 16 ISAC-S, to support up to 16 S-interfaces.

Alternatively, the configurable interface may be selected as <u>IOM interface</u>, which is compatible to both the <u>multiplexed IOM1</u> and the <u>IOM2interface</u>.

If the <u>multiplexed IOM1 interface</u> is chosen, the EPIC supports up to 32 ISDN subscribers on the digital line card. The interface lines are then connected to the EPIC, an IOM1 compatible layer 1 device e.g. the S-bus controller (SBC, PEB 2080), the ISDN Burst Transceiver Circuit (IBC, PEB 2095) or the ISDN Echo Cancellation Circuit (IEC, PEB 2090) and, optionally, an IOM1 compatible layer 2 device e.g. the ISDN D Channel Exchange Controller (IDEC, PEB 2075).

//

In the case of an <u>IOM2 interface</u> the EPIC supports up to 32 ISDN or 64 voice subscribers. They are connected via the SBCX (PEB 2081), IBC-B (PEB 2096) or IEC (PEB 20901 and PEB 20902) and a digital loop. In both cases either the ICC-B (PEB 2070) or the IDEC (PEB 2075) may perform the D channel handling.

Fig. 1.4: Schematic Summary of the Line Card

#### 1.6.5. Analog Line Card

In analog line cards the EPIC controls the signaling, voice and data paths of 64 kbps channels

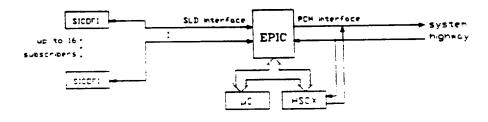

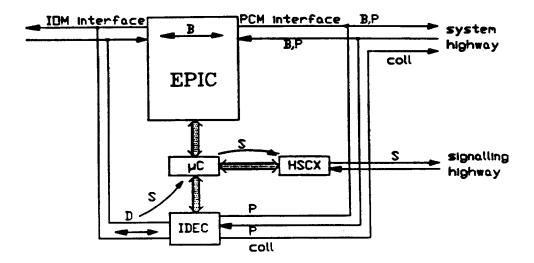

In combination with SLD compatible devices e.g. the highly flexible Siemens Codec Filter (PEB 2060), it forms an optimized analog subscriber line board architecture as shown in figure 1.5. The HSCX (High Level Serial Communication Controller, SAB 82525) handles the signaling information contained in a time slot of programmable bandwidth at the PCM interface or on a dedicated signaling highway.

Moreover, the EPIC controls the feature control and signaling channels and buffers these channels to the  $\mu\text{C}$ .

Fig. 1.5: Example of an Analog Line Card Architecture

## -1.6.6. Digital Line Cards

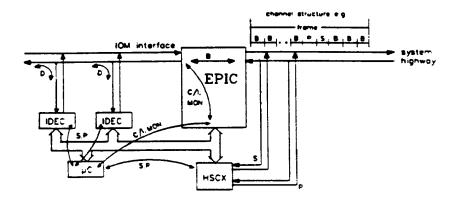

On digital line cards, the EPIC performs the switching function for up to 32 ISDN subscribers between the PCM system highways and the IOM interfaces. Moreover, it has the layer 1 controlling capability of buffering the C/I and monitor channels of the IOM interface.

The EPIC can be operated in tandem, i.e. one device is active, another one is a backup device. The backup device can instantaneously take over from the active device when the active device fails. Due to this tandem operation capability and the high number of ISDN subscribers which can be connected to one EPIC, the use of single line cards is feasable.

Several architectures are possible.

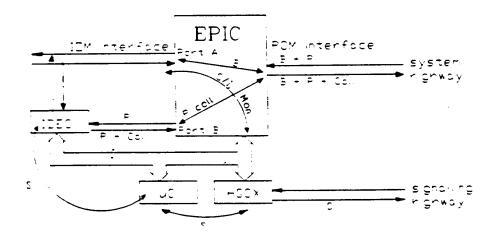

In completely decentral D channel processing architectures (Fig. 1.6), the processing capacity of a line card is usually dimensioned to avoid blocking situations even under maximum conceivable D channel traffic conditions. In such an architecture the EPIC switches the B channels and performs C/I and monitor channel control. The IDECs handle the layer 2 functions for signaling and data packets in the D channel and transfer the extracted data via the  $\mu P$  and an HDLC controller, e.g. the HSCX (Enhanced High Level Serial Communication Controller SAB

82525) to the system. One of the channels of the HSCX may be used for example for the signaling information, the other for data packets. The HSCX may access either a time slot of programmable bandwidth on one of the system highways (Fig. 1.6) or a separate signaling highway (Fig. 1.7). In both cases the highway capacity used for packet traffic can be shared among several line cards due to the statistical multiplexing capabilities of the HSCX.

Fig. 1.6: Completely Decentral Packet Switching Digital Line Card Architecture

In an architecture with <u>completely central D</u> channel handling (Fig. 1.7), the EPIC switches the B and D channels and performs the C/I and monitor channel control functions.

The line card microcontroller programs the EPIC and is connected to the group control via a signaling highway and an HSCX. Moreover the EPIC controls the layer 1 protocol on the IOM interface, buffering the C/I and monitor channels to the microprocessor.

Fig. 1.7: Digital Line Card Architecture with a Completely Central D Channel Handling

A third possibility is a <u>mixed architecture</u> with central packet data and decentral signal handling. This is a very flexible architecture which reduces the dynamic load of central processing units by evaluating the signaling information on the line card. For this case, any increase of packet data traffic does not necessitate any changes in the architecture since the line cards do not have to be modified. The central packet handling unit can simply be expanded.

For such an architecture, the EPIC performs B and D channel switching in addition to C/I and monitor channel control. The IDECs handle the signaling data of the D channel. These messages are transferred to the group controller via the microprocessor and an HDLC controller. The packet data of the D channel are switched to the system highways and processed by the central packet unit.

In this architecture, the EPIC switches the B channels from IOM port A (Fig. 1.8) to the PCM interface. The IDEC works in a master/slave configuration. Therefore, an additional collision resolution line is needed. The IDEC separates signaling from data packets. The signaling messages are transferred to the  $\mu$ C, which in turn hands them over to the group controller using the HSCX.

The packet data are processed differently. Together with the collision resolution line they are handled by the IDEC at another IOM port (port B). The EPIC switches the channels of these ports to the PCM interface as shown in figure 1.8.

Fig. 1.8: Line Card Architecture for Mixed Packet Handling two IOM Ports of the EPIC

In such a configuration, the p packets and the collision resolution signal occupy one of the IOM ports available at the configurable interface. This reduces the total switching capability of the EPIC to 24 ISDN subscribers.

Alternately, the packet data and the collision line can be directly exchanged between the IDEC and the PCM highway. The EPIC then simply switches the B channels (see figure 1.9). The

packet data are separated by the IDEC and placed on the PCM highway. Thus, the full 32 subscriber switching capability of the EPIC is retained.

Fig. 1.9: Digital Line Card Architecture for Mixed Packet Handling Using a Collision Highway

### 1.7. Packet Handlers

The EPIC is an important building block for networks based on either central, decentral or mixed signaling and packet data handling architectures. Its flexibility allows for the modification of the packet handling architecture according to the changing needs.

Thus, it may be useful to add central packet handling groups to a network originally based on decentral signaling packet handling. This may be the case if growing data packet traffic exceeds the initial capacity of the network. The result is a mixed architecture.

On the other hand, increasing packet handling demand on a few dedicated subscriber lines calls for solutions which back up the capacity at these few decentral line cards.

In both of these cases and several other applications, the EPIC is a powerful device for solving the problem of packet handling. In most applications it is used together with the IDEC (ISDN D Channel Exchange Controller).

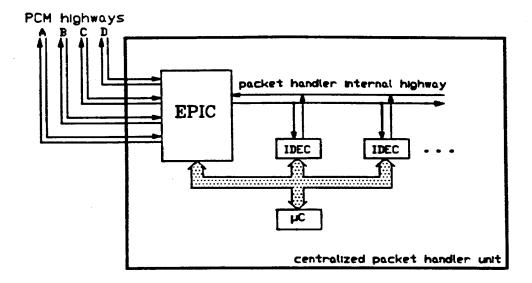

Decentralized and mixed packet handling has already been covered in the line card chapter. In the following, the centralized signaling/data packet handlers built up with the EPIC will be described.

Central packet handling is used if many subscribers with a generally low demand for packet switching are to be connected to a system. Concentrating the packet servers for multiple users eliminates the need to provide a packet server channel for every user. The overall number of packet server channels can thus be reduced.

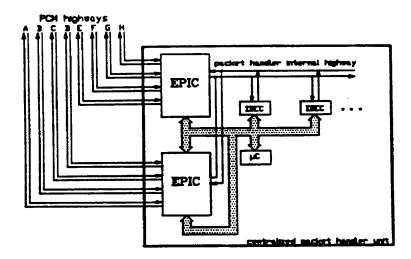

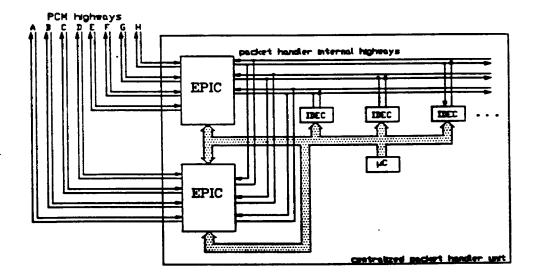

In such a central packet handling group, the EPIC performs the switching and concentrator function. It connects a variable number of PCM highways to the packet handler internal highway. HDLC controllers are also connected to this internal highway as illustrated in figure 1.10.

Fig. 1.10: Centralized Packet Handler with a single Internal Highway Connected to 4 PCM Highways

This figure shows one EPIC connecting four PCM highways to one packet handler internal highway. These highways are accessed by the IDECs (ISDN D channel Exchange Controller) which are 4 channel HDLC controllers and handle the packets. If more than four PCM highways shall be connected to the centralized packet handler, further EPICs are necessary. Such a situation is shown in figure 1.11, where 8 highways are switched to one packet handler internal highway. In this case the two EPICs are connected in parallel at the packet handler internal side.

Fig. 1.11: Centralized Packet Handler with One Internal Highway Connected to 8 PCM Highways

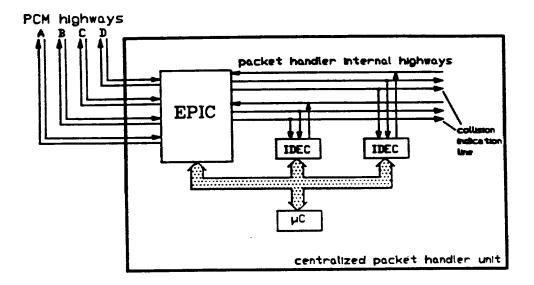

The data rate of the packet handler internal highway can be up to 4096 kbps. If this capacity is not sufficient, other packet handler internal highways may be added as shown in figure 1.12.

Fig. 1.12: Centralized Packet Handler with 3 Internal Highways

In some applications an additional collision resolution signal is required for the HDLC controllers. This Information can be demultiplexed from the PCM highways to a third line for each packet handler internal highway (see figure 1.13).

Fig. 1.13: Centralized Packet Handler with Internal Collision line

The applications illustrated apply equally to centralized signaling as well as to data packet handlers.

### 2. Functional Description

In the following chapters the functions of the PEB 2055 will be covered in more detail.

### 2.1. PCM Interface

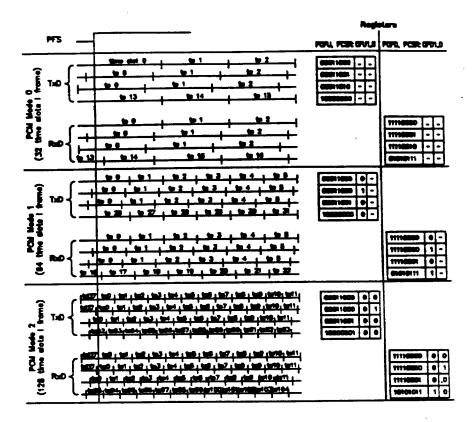

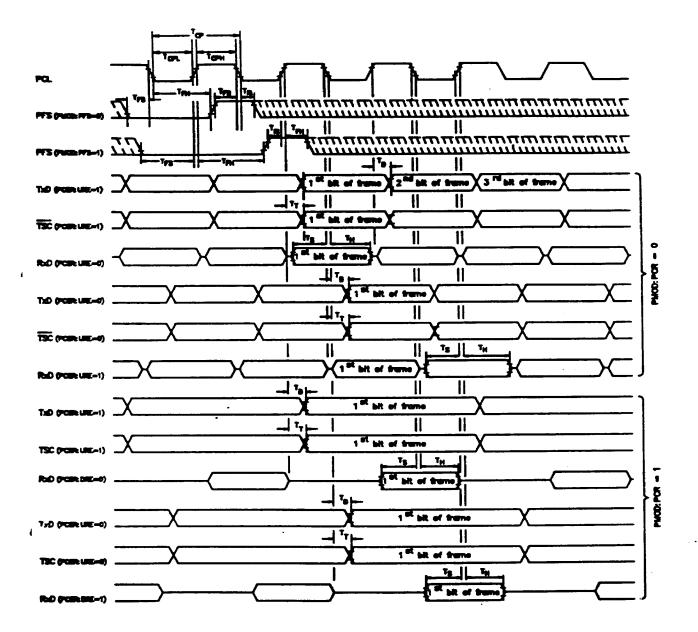

The PCM Interface formats the data transmitted or received at the PCM highways. Via PMOD: PMD1, PMD2 it can be configured to one, two or four PCM ports consisting each of a data receive (RxD#), a data transmit (TxD#) and an output tristate Indication line (TSC#).

As stated in table 4.2 the *maximum* data rate with four PCM ports is 2048 kbps (PCM mode 0), with two PCM ports 4096 kbps (PCM mode 1), for one PCM port it is 8192 kbps (PCM mode 2). However, the *actual* data rate may be varied in a wide range. It is programmed to PBNR. In PCM mode 0 this register contains the number of bits per frame minus 1 bit, in PCM mode 1 half the number of bits minus 2 bits and in CM mode 2 the fourth of the number of bits per frame minus 4 bits. Hence the data rate can be stepped in 8, 16 or 32 kbps increments in PCM mode 0, 1 and 2, respectively.

E.g., selecting the T1 data rate (1544 kbps) at the system interface PBNR = 11000000 has to be programmed (PCM mode 0). To initialize the EPIC for a 8192 kbps data rate in PCM mode 2 PBNR has to be written with FFH.

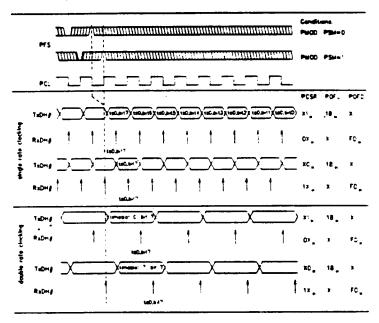

To properly clock the PCM interface a PDC signal with a frequency equal to or twice the data rate has to be applied to the EPIC as selected in PMOD: PCR.

For the synchronization of the time slot structure a framing signal needs to be connected to the EPIC's PFS pin. The rising edge of this signal is evaluated by the device.

Under the control of PMOD: PSM this occurs either with the rising or the falling PDC slope as shown in figure 4.1. The PFS pulse is of arbitrary length. However, it must be ensured that the framing signal is low for at least the last PDC clock period before the next framing pulse.

The PFS period is internally checked against the duration expected from the PBNR and PMOD: PCR entries. E.g. programming PBNR = 11000000 (1544 kbps) and PMOD:PCR = 1 a PFS period equal to 386 PCL clock periods is anticipated.

After reset, the EPIC reaches synchronism having received two consecutive correct PFS pulses. Synchronization is considered lost by the device if the PFS signal is not repeated with the correct repetition rate. The PCM synchronization status can be seen in STAR: PSS. For any change in the synchronization status a maskable interrupt (ISTA: PFI, MASK: PFI) is generated.

A logical 1 indicates the synchronous state, a logical 0 shows, that synchronism has been lost.

Without programming the bit shift function of the EPIC'S PCM interface, the rising edge of the PFS signal marks the following bits:

| upstream   | PCM mode 0: | blt7, time slot | 29  |

|------------|-------------|-----------------|-----|

| - (        | PCM mode 1: | bit7, time slot | 58  |

|            | PCM mode 2: | blt7, time slot | 116 |

| downstream | PCM mode 0: | blt7, time slot | 2   |

|            | PCM mode 1: | bit7, time slot | 4   |

|            | PCM mode 2: | bit7, time slot | 8   |

In upstream direction the maximum number of bits in the relevant PCM mode is assumed. In the case of a lower bit count per frame the PFS signal marks an according bit in the frame. E.g., in a 1536 kbps system (24 time slots numbered 0 through 23/frame in PCM mode 0), it marks bit 7 of the time slot 21.

The time slot structure may be shifted using the POFD, POFU and PCSR registers.

The correlation between the framing signal PFS and the bit stream is controlled by the content of these registers as shown in table 2.1.

| Register Bits            | Direction  | PCM Mode |  |

|--------------------------|------------|----------|--|

| POFD: OFD92, PCSR: OFD10 | downstream | 2        |  |

| POFD: OFD92, PCSR: OFD1  | downstream | 1        |  |

| POFD: OFD92              | downstream | 0        |  |

| POFU: OFU92, PCSR: OFU10 | upstream   | 2        |  |

| POFU: OFU92, PCSR: OFU1  | upstream   | 1        |  |

| POFU: OFU92              | upstream   | 0        |  |

Table 2.1: Register Bits Correlating PFS Signal and PCM Bit Stream

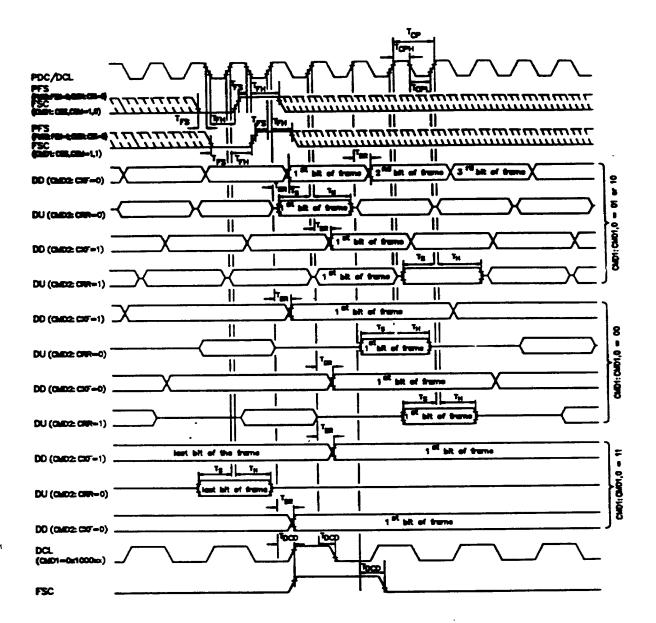

These register contents denote the number of bit periods, the PCM frame is shifted. A few examples are given in figure 2.1.

After reset, with single rate clocking, the downstream data is input and upstream data is output with the falling edge of the PDC signal. However, programming the PCSR: DRE and URE bits with a logical 0, these instants may be changed to the rising edge. Thus the frame structure can be shifted by a half bit period. For a picture of this behaviour - also with double rate clocking, please refer to figure 4.1.

Another feature of the EPIC's PCM Interface is its' alternative input function. In PCM mode 1 and 2, the unused input ports can be used for redundancy purposes. In these modes, for every active input port there exists a second input port, which can be connected to a redundant PCM input line. The EPIC checks the input from the two lines for mismatches. PMOD: AIC0, AIC1 control this comparison function of the EPIC. With AIC0 active (logical 1) the EPIC compares RxD 1 and RxD0 in PCM mode 1 and stores the timeslot, where a mis-

match occures in the PICM register. Similarily, an active PMOD: AIC1 enables the comparison function between RxD2 and RxD3 (in PCM modes 1 and 2). PMOD: AIS1, AIS0 associate the lines to the logical ports. For the active output lines the TSC# pins indicate the output driver impedance. TSC1 and TSC3 output the value programmed to AIS0 and AIS1, respectively.

For a tabularic summary of the PCM interface line functions please refer to table 4.3.

Finally all PCM outputs may be switched to high impedance. (OMDR: PSB). Thus redundand systems with one of two devices working in standby mode are feasible.

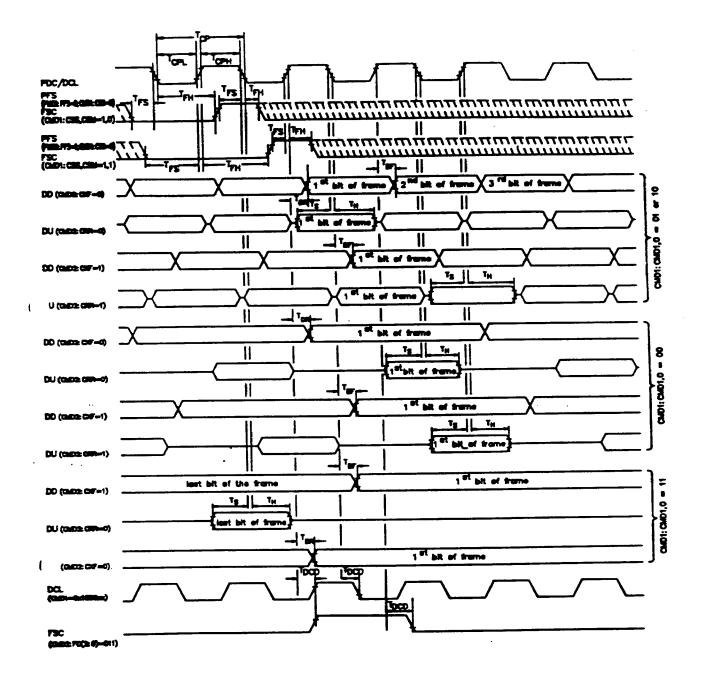

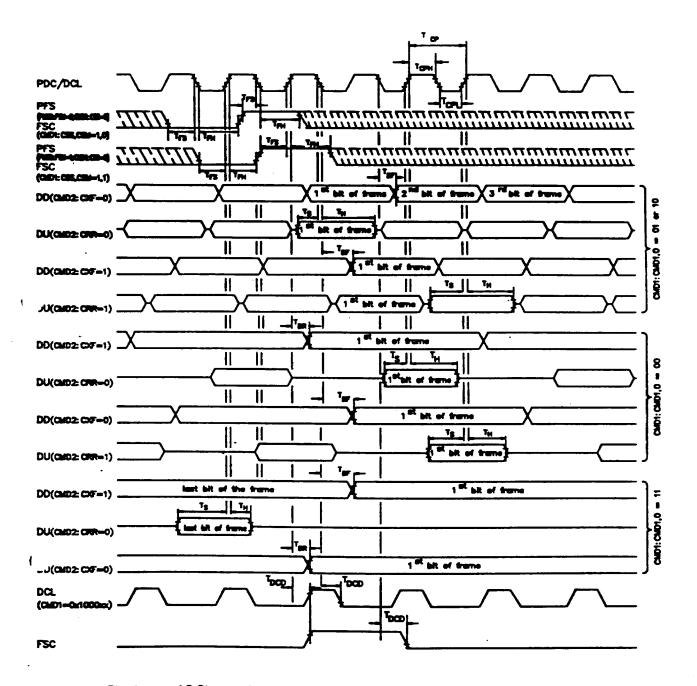

# 2.2. Configurable Interface

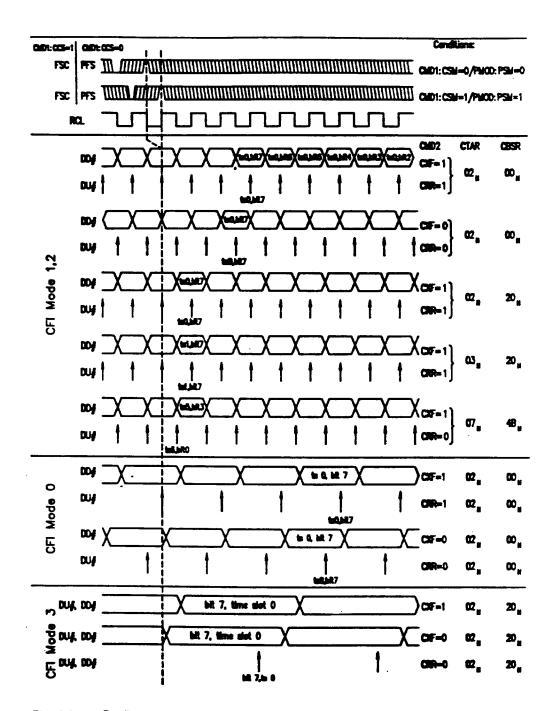

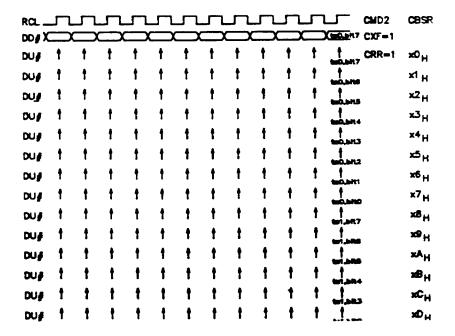

The CFI formats the data transmitted or received at the DD#, DU# or SIP# lines. Via CMD1: CMD1, 0 it can be configured to one, two or four duplex ports consisting each of a data downstream (DD#) and a data upstream line (DU#), or to eight bidirectional lines (SIP#).

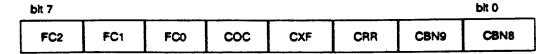

As stated in table 4.6 the maximum data rate with four duplex ports is 2048 kbps (CFI mode 0), with two duplex ports it is 4096 kbps (CFI mode 1), with one duplex port 8192 kbps (CF0 mode 2) and with eight bidirectional ports 1024 kbps (CFI mode 3). The actual data rate, however, is subject to the CMD2: CBN9, 8 and CBNR entries and may be varied in a wide range. In each CFI frame there are (CBN9..CBN0)8 bits plus one bit. Hence, the data rate can be stepped in 8 kbps increments in all CFI modes.

To properly clock the CFI a reference clock (RCL) of a specific frequency is required, as also stated in table 4.6.!

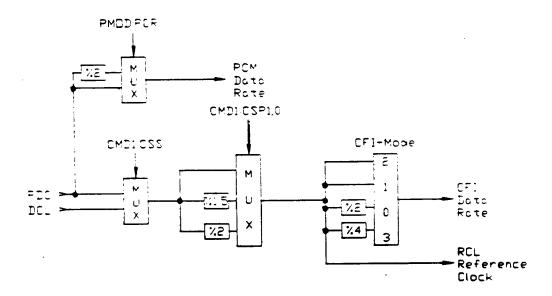

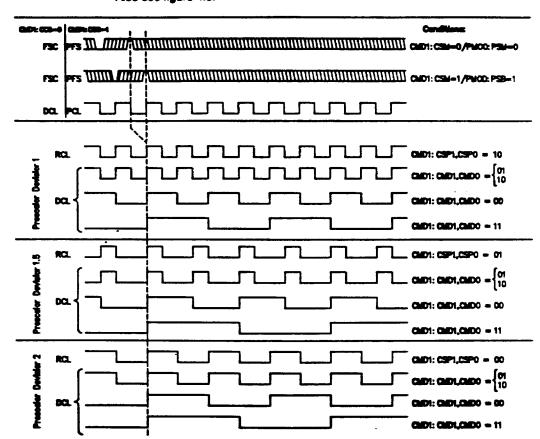

In CFI modes 1 and 2 this frequency is equal to the actual data rate, in CFI mode 0 it is twice the actual data rate and in CFI mode 3 four times the actual data rate. Thus, a 2048 kHz reference clock is needed for a bidirectional setup with a 512 kbps data rate or for a duplex setup with 2 ports and a 2048 kbps data rate. This reference clock may be obtained from the DCL pin (CMD1:CSS = 1) or the PDC pin (CMD1:CSS = 0) subject to the prescalor divisor selection (see figure 2.1).

Flaure 2.1: EPIC Clock Sources for the CFI and PCM Interface

Depending on the values CMD1: CSP1..CSP0 the external clock is divided by 2, 1.5 or 1. As a result, the reference clock is generated.

Thus, using the PDC as the source for the reference clock, the following data rate ratios between PCM Interface and CFI may be obtained.

| PCM/CFI data rate ratio | PCM clocking | Prescalor divisor | CFI mode |

|-------------------------|--------------|-------------------|----------|

| 1                       | single rate  | 1                 | 1,2      |

| 1.5                     | single rate  | 1.5               | 1,2      |

| 2                       | single rate  | 2                 | 1,2      |

| 2                       | single rate  | 1 1               | 0        |

| 3                       | single rate  | 1.5               | 0        |

| 4                       | single rate  | 2                 | 0        |

| 4                       | single rate  | 1 1               | 3        |

| 6                       | single rate  | 1.5               | 3        |

| 8                       | single rate  | 2                 | 3        |

| 0.5                     | double rate  | 1 1               | 1,2      |

| 0.75                    | double rate  | 1.5               | 1,2      |

| 1                       | double rate  | 2                 | 1,2      |

| 1                       | double rate  | 1                 | 0        |

| 1.5                     | double rate  | 1.5               | 0        |

| 2                       | double rate  | 2                 | 0        |

| 2                       | double rate  | 1                 | 3        |

| 3                       | double rate  | 1.5               | 3        |

| 4                       | double rate  | 2                 | 3        |

For other data rate ratios DCL has to be used as clock source.

CMD1: CSS also selects the synchronization source. With CMD1: CSS = 0 the synchronization signal is taken from PFS whereas with CMD1: CSS = 1 It is derived from FSC.

Again, the rising edge of the synchronization signal is evaluated by the device. Under the control of CMD1: CSM the signal is evaluated at every positive or negative source clock slope. The framing pulse is of arbitrary length. However, it must be ensured that the framing signal is low for at least the last clock period before the next framing pulse. This behaviour and the pulse shape of the generated reference clock is shown in figure 4.5.

If PDC and PFS are selected as clock and framing sources the EPIC outputs clock signals derived from these at DCL and FSC. As stated in table 4.6 a single rate clock signal with a frequency equal to the CFI data rate or a double rate clock signal (CFI modes 0 and 3) may be generated at DCL (CMD2: COC). Figure 4.5 shows the wave form and phase correlation of the generated output clocks.

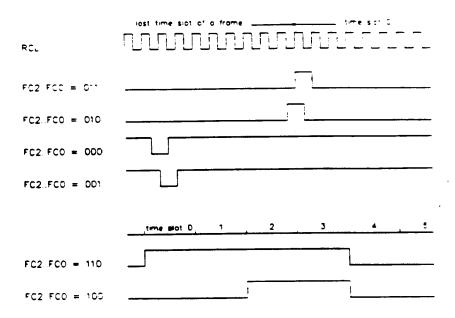

The generated output framing signal is controlled by CMD2: FC2..FC0. The different pulse forms are shown in the figures 4.3 and 4.4. Except in FC mode 7 (see table 4.8) they have a period of one frame.

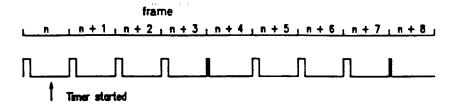

In the framing mode 7 the generation of the framing signal includes the use of two other registers, the timer register and the command register. The timer register defines a period in multiples of 250  $\mu$ sec (TIMR: TVAL6..TVAL0 = 0: 250  $\mu$ sec). E.g., setting TIMR: TVAL6..TVAL0 = 01H defines a period of 500  $\mu$ sec equalling 4 frames. Programming CMDR: ST = 1 starts the timer. At every but the last frame begin in the predefined period the EPIC then outputs the framing signal of FC mode 6, i.e. a logical 1 during the time slots 0, 1, 2 and 3. At the last frame begin the framing signal of FC mode 3 is sent, i.e. a logical 1 during the first bit period of the frame.

This function is repeated until the timer is stopped (see 2.6.1). For a repetition period of 500  $\mu$ s the frame signal is shown in figure 4.4.

The bit shift function of the EPIC's CFI is illustrated in figure 4.6. The time slot adjustment register (CTAR) and bit shift register (CBSR) control it. CTAR and CBSR: CDS2..CDS0 shift both upstream and downstream frame in exactly the same way. The CTAR content shifts the frame structure by whole time slots, CBSR: CDS2..CDS0 by single bits. CBSR: CUSR..CUS0 shift the upstream frame relative to the downstream frame by up to 15 bit periods covering the range of two time slots. Finally, the upstream and downstream frame may be shifted by half bit periods independently from each other programming the CMD2: CXF and CMD2: CRR bits accordingly.

Similar to the PCM Interface for CFI mode 1 and 2 the input of a logical port may be chosen from one of two physical lines. This feature is controlled by CMD1:CIS1 and CIS0. A complete list of the physical line allocation is shown in table 4.7. A line comparison and mismatch monitoring is not provided for the CFI.

For unassigned output channels the output driver may be selected to be open drain or tristate (OMDR: COS). OMDR: CSB switches all CFI outputs to high impedance, over ruling the output driver impedance selecting and thus allowing for standby operation in redundand systems.

Different from the PCM interface (see 2.4) the subchannel assignement of the CFI occurs on a per port basis. Two bits per port are provided in the CSCR for this function. Thus, a time slot on a CFI port can contain only one channel having a bandwith of 16, 32 or 64 kbps, and all subchannels on the port have the same position (e.g. bits 5 and 4 of a time slot for a 16 kbps channel).

# 2.3. Memory Structure and Switching

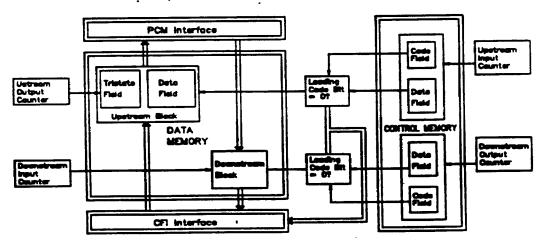

The EPIC contains two memories, the control memory (CM) and data memory (DM). Their structure and connection is shown in figure 2.2.

The data memory consists of two blocks. The downstream block buffers the data input from the PCM interface, the upstream block the data input from the CFI. The downstream block has a capacity of 128 timeslots to buffer a whole PCM frame. It is written from the PCM interface periodically once every frame controlled by the downstream input counter and read at random to perform the switching function.

The upstream block consists of the data and tristate fields. Similar to the downstream block the upstream data field has a capacity of 128 time slots and is capable to buffer a whole PCM frame to the PCM interface. This field is written at random and read cyclically for PCM interface output, under the control of the upstream output counter.

The upstream tristate field contents control the PCM output impedance. This field is written via the  $\mu P$  interface and read synchronously with the data field. Thus, the impedance information is read together with the data for output at the PCM interface. The tristate field contains 512 bits, structured as 128 x 4, so that one bit of the tristate field is attributed to each of the possible 2 bit/frame sub time slot positions.

The upstream and downstream data field are randomly accessed by either the CFI (for switching) or the  $\mu P$  interface (for information monitoring or idle code implementation).

The control memory is also composed of an upstream and a downstream block. Each block contains 128 locations of 8 bits of control memory data and 4 bits of control memory code. Both blocks are written at random via the  $\mu P$  interface and read cyclically under the control of a seperate counter for each block/upstream input counter, downstream output counter). These counters are synchronous with the CFI upstream and downstream frames.

Figure 2.2: EPIC Memory Structure

Ú

The code field entries determine, in which way the data field entries are handled. The codes are entered via MACR: CMC3..CMC0 setting MACR: MOC3..MOC1 to 111 (see chapter 4.3). A leading 0 in the code field entry identifies the data field entry as a pointer to a data memory position.

For downstream switching, the downstream block of the CM is read in sequence. If the leading bit of the code field is a logical 0 the corresponding data field entry points to a location in the data memory downstream block. The byte in this data memory location is read into the current downstream CFI frame.

For upstream switching the corresponding upstream blocks are involved.

For proper switching, the CM needs to be programmed for the desired connection. The control memory address corresponds to one particular CFI time slot and port number. The contents of this CM address point to a particular PCM time slot and line number correlated to a fixed location in the data memory.

The lower significant code field bits control the PCM subchannel bandwith and location, i.e. the number of bits and their position within the time slot (see 4.3.1). Thus up to four 16 kbps subchannels may be combined into one byte at the PCM interface. However, in switching operation only one channel or subchannel may be assigned to one CFI time slot, the position and bandwith of which is defined by CSCR.

A leading 1 in the control memory code field entry indicates a CFI data interaction. Thus either a CFI idle code may be programmed or a control channel (IOM applications)/signaling channel (SLD applications) is marked. The function of these channels will be covered in the Control/Signaling section.

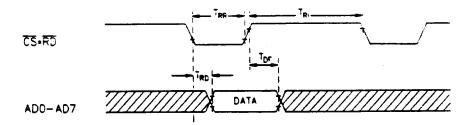

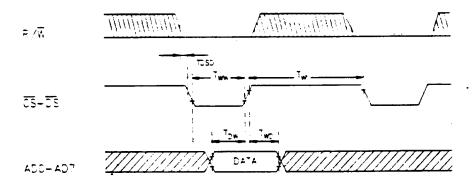

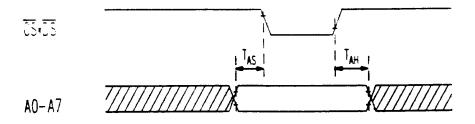

# 2.4. Microprocessor Interface

The EPIC provides interface signals for both, Motorola type and Intel type microprocessors. In the Intel type  $\mu P$  interface mode either a multiplexed or a demultiplexed bus structure may be chosen.

For a demultiplexed bus structure including the Motorola type  $_{\mu}P$  interface the PLCC 44 package of the EPIC needs to be used, since only this package provides the additional lines of a separate 4 line address bus.

The ALE line of the PEB 2055 is used to control the bus structure and interface type. ALE is fixed to + 5V for the Motorola type  $\mu$ P interface and it is switching to signal an address or data transfer in the multiplexed intel type  $\mu$ P interface mode. Pins 28 and 29 of the PLCC package are interpreted as RD and WR for a intel type interface or DS and R/W for a Motorola type interface. Tab. 2.2 summarizes these functions.

| ALE             | Type of<br>µP Interface | Bus Structure | PLCC<br>pin 28 | PLCC<br>pin 29 | package     |

|-----------------|-------------------------|---------------|----------------|----------------|-------------|

| fixed to VDD    | Motorola                | demultiplexed | DS             | R/W            | PLCC        |

| fixed to ground | Intel                   | demultiplexed | RD             | WR             | PLCC        |

| switching       | Intel                   | multiplexed   | RD             | WR             | DIP or PLCC |

### Table 2.2: uP interface Functions

In the multiplexed  $\mu P$  interface mode the addresses as outlined in the detailed register description are used, AD0 is always fixed to logical 0. This simplifies the use of a 16 bit Intel type processors.

For a demultiplexed  $\mu P$  interface, in addition to the A3 to A0 lines the OMDR: RBS bit is needed for addressing a register. With OMDR: RBS (register bank selection) one of two register banks is selected. RBS = 1 selects a set of registers used in the device initialization phase (e.g. CFI interface and CM initialization), RBS = 0 switches to a group of registers necessary during operation (e.g. connection programming, special channel programming).

The OMDR register containing the RBS bit can be accessed with either value of RBS.

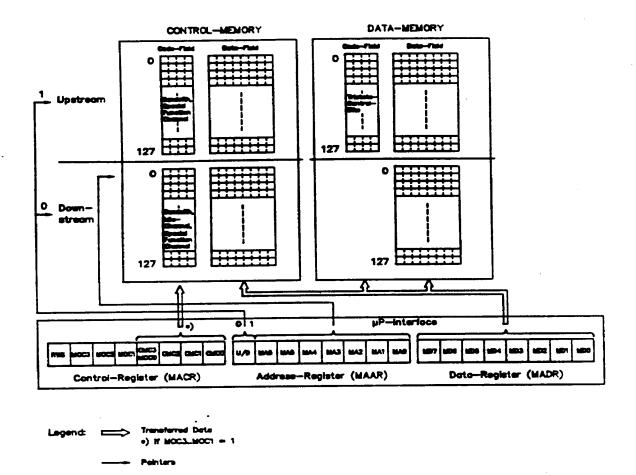

For memory accesses the memory access registers are provided. Fig. 2.3 visualizes the functions of these registers. The memory access adddress register contains the address of a specific location of the data or control memory, the memory access data registers the content to be read or written. The memory access control register content controls the memory access.

There are control codes to access the

- data memory upstream tristate field

- data memory data fields

- control memory data fields

- control memory data and code fields simultaneously.

A memory access using the actual MADR and MAAR contents is performed upon every MACR write access.

During the processing of the memory access, which takes at most 9.5 RCL periods. STAR: MAR is set.

For a detailed descriptions of the codes please refer to chapter 4.3.

Figure 2.3: Data Transfer between  $\mu P$ -Interface and the Memories

The following few examples illustrate the behaviour of the EPIC.

In PCM mode 0 the instruction sequence

MADR 01011000 MAAR 11000110 MACR 00001000

instructs the EPIC to output the idle code 58<sub>H</sub> in time slot 16 at the PCM port 3.

### Then programming

MADR 00001111 MAAR 11000110 MACR 01100000

will switch the output drivers at the PCM port 3 to low impedance in the selected time slot 16.

### Now programming

MADR 11000110 MAAR 10100010 MACR 01110001

will establish a connection from CFI time slot 8 port 1 (CFI mode 0) to PCM port 3 time slot 16 erasing the idle code.

### whereas the instruction sequence

MAAR 01000110 MADR 00100010 MACR 01110111

would set up a connection between bits 7..6 of time slot 18 of PCM port 0 (input) and the CFI time slot 70 (output). PCM mode 1 and CFI mode 2 are assumed, the CFI subchannel position is determined by the CSCR content.

### The code

| MADR | 10101001 |

|------|----------|

| MAAR | 10101011 |

| MACR | 01110010 |

| MAAR | 00110111 |

| MADR | 10101001 |

| MACR | 01110010 |

| MADR | 00000000 |

| MAAR | 10101001 |

| MACR | 01100000 |

loops back the bit 3..0 sub time slot of time slot 11 at the CFI port 1 to time slot 13 of CFI port 3. CSCR, = xxxx11xx, CFI mode 0 and PCM mode 1 are assumed. The output of PCM time slot 21 port 0 is hold at high impedance. By selecting the bits 7 of MAAR and MADR the switching mode is elected for MACR:MOC3..MOC1 = 111 according to table 2.3.

| bit 7 MAAR | bit 7 MADR | Switching Mode       |

|------------|------------|----------------------|

| 0          | 0          | Connection PCM → CFI |

| 1          | 1          | Connection CFI → PCM |

| Ď          | 1          | CFI → PCM → CFI      |

| 1          | 0          | PCM → CFI → PCM      |

Table 2.3: Switching Modes

# 2.5. Preprocessed Channels

# The EPIC supports the

- Monitor/Feature Control (MF) and

- Control/Signaling (CS)

### channels at the CFI.

The monitor handler takes care of the monitor/feature control channels, the signaling handler of the control/signaling channels. These channels are established by programming an appropriate code (as shown in figures 4.14 and 4.15) for two consecutive CFI time slots (starting with the even time slot number) to the control memory. The even address maps to the monitor/feature control channel, the consecutive odd to the control/signaling channel.

The possible code combinations for the different applications are listed in table 2.4.

| Application                       | Upstream Codes |                        | Downstream Codes |                         |

|-----------------------------------|----------------|------------------------|------------------|-------------------------|

| Decentral ISDN-D Channel Handling | 1000           | 0000                   | 1000             | 1011                    |

| Central ISDN-D Channel Handling   | 1000           | 16kbps<br>channel code | 1000             | 16 kbps<br>channel code |

| 6 Bit Signaling (e.g. analog IOM) | 1010           | 1010                   | 1010             | 1011                    |

| 8 Bit Signaling (e.g. SLD)        | 1011           | 1011                   | 1010             | 1011                    |

| CM-Address                        | even           | odd                    | even             | odd                     |

Table 2.4: Possible Preprocessed Channel Codes

### 2.5.1. Signaling Handler

In downstream direction the relevant content of the control memory data field location with the even address is transmitted in the odd time slot (signaling channel). In the central D channel handling scheme the two bits of the current control memory data field location, which are selected by the code residing in the code field, are added.

This is shown in figure 4.15.

In upstream direction the signaling handler monitors the received control/signaling channels. Upon a change

- an interrupt is generated (ISTA, MASK:SFI)

- the address of the specific channel is written into the C/I FIFO and

- the actual value is stored in the even control memory data field locations.

In the central D channel handling scheme the two D channel bits are written to the odd data field location at a position identified by the code residing in the code field of the same location (table 4.16).

In the 6 bit and 8 bit signaling schemes the odd data field location contains the stable value the even data field location the actual value. The actual value is subject to the double last look procedure (LL procedure). As shown in figure 2.7 the actual value is sampled when the last look period runs out the next time and again a double last look period later. The actual value is copied to the stable value, if it is identical to the two samples. This period is controlled by the timer register (TIMR). If TIMR: SSR is selected to logical 1, the double last look period is fixed to 125  $\mu$ sec, otherwise it is a multiple of 250  $\mu$ sec. Depending on TIMR: TVAL6..TVAL0 it may thus be varied from 250  $\mu$ sec (TIMR = 00H) to 32 ms (TIMR = 7FH).

The signaling FIFO is 9 bytes deep and can thus hold 9 channels, where the signaling information changed. Each entry in this FIFO includes the SBV bit indicating the validity of the entry. The polarity of SBV (SBV = 1: valid entry) has been chosen such that a valid C/I FIFO entry can instantaneously be used for control memory accesses without manipulations: A valid pointer selects the upstream block of the CM. Moreover SAD0 is set to logical 1 (odd address) if the 6 or 8 bit signaling scheme is used pointing to the stable value. In the ISDN D-channel handling schemes it is fixed to logical 0 for an access of the C/I information at the even address location.

The complete signaling FIFO is reset, i.e. all SBV bits are set to logical 0 by selecting OMDR: OMS0 = 0 or by instructing the EPIC to reset the C/I FIFO with CMDR: MFFR = 1.

#### 2.5.2. Monitor Handler

The monitor handler communicates with the subscriber circuits subject to the IOM or SLD protocols. It works either with active (only in IOM applications) or with not active handshake protocol as selected in OMDR: MFPS. With the handshake protocol active each byte exchanged between the EPIC and the subscriber in the monitor channel is internally autonomously acknowledged for a safe communication. When the handshake protocol is not active the bytes constituing the message are sent one per frame.

The monitor handler only works upon it has been instructed with a proper selection in the command register.

The time slot and port/line numbers coded in MFSAR/MFAIR: SAD5..SAD0 may be identified using table 4.17. In this case an additional least significant logical 0 and a most significant bit depending on the transmission direction has to be assumed.

#### HANDSHAKE PROTOCOL ACTIVE

With the handshake protocol active the following commands are provided by the EPIC.

By setting CMDR: MFSO to logical 1 the EPIC starts to look for active monitor channels.

As soon as an active channel is found the ISTA, MASK: MAC interrupt is generated and the address of this channel is stored in MFAIR: SAD5.:SAD0.

The search for an active monitor channel is stopped, when one such channel has been found or when a logical 0 is written to CMDR: MFSO.

The address of a found channel may be copied to MFSAR: SAD5..SAD0 for further processing.

By setting CMDR: MFT1, MFT0 to 01 the EPIC starts transmitting the content of MFFIFO.

When the message has been completely transferred, the ISTA, MASK: MFFI interrupt is generated. The group of recipient subscribers is defined by MFSAR: MFTC1, MFTC0. Programming these bits with

- 00 the message is sent to the subscriber with the address specified in MFSAR: SAD5..SAD0.

- 01 the message is broadcast in all monitor channels. The MF bytes are transmitted at maximum speed, i.e. one byte per three frames. The arriving acknowledgments are ignored.

- the MFFIFO content is not transmitted and may instantaneously be read again (test operation). The ISTA, MASK: MFFI interrupt is also generated instantaneously.

- For the transmission of messages longer than 16 bytes the selection CMDR: MFT1, MFT0 = 11 is provided. This choice transmits a block of 16 bytes and interrupts the microprocessor for the next bytes to be written to MFFIFO. (ISTA, MASK: MFFI; STAR:MFAE = 1, MFRW = 0). The last block of such a long message in transmitted programming CMDR: MFT1, MFT0 to 10.

Such a long message can only be transmitted to a single subscriber (MFSAR: MFTC1, MFTC0 = 00).

Setting CMDR: MFT1,0 to 10 an answer to the sent message is expected from the same subscriber (same port, same time slot). The MFTC1, MFTC0 bits need to be fixed to 00.

The message is stored in MFFIFO and as soon as it is complete the ISTA, MASK: MFFI interrupt is generated.

In all cases the transmitted message consists of the MFFIFO content prior to the command.

If a message shall be received without transmission (e.g. an active monitor channel has been found) the receive and transmission command is issued with an empty MFFIFO.

The STAR: MFAB bit is set, if the remote partner aborts the reception of an arriving message.

# HANDSHAKE PROTOCOL INACTIVE

With the handshake protocol not active a search for an active monitor channel is not possible. The EPIC always outputs transmitted messages at full speed, i.e. one byte per frame. Keeping that in mind the transmit (CMDR: MFT1, MFT0 = 01) and transmit + receive same timeslot (CMDR: MFT1, MFT0 = 10) commands are similar to the active handshake protocol case. Executing the CMDR: MFT1, MFT0 = 11 command, however (transmit + receiver same line), the EPIC expects the arriving bytes at the same line, but four time slots later than those it sent the transmitted bytes to. (SLD application)

In both transmit + receive cases the number of expected bytes is programmed to MFSAR: MFTC1,0 bits. Setting these bits to

00 1 byte

01 2 bytes

10 8 bytes

11 16 bytes

### of answer are expected.

Before every command and after each MFFI interrupt STAR should be read. The bits MFT0, MFAB, MFAE, MFRW and MFFE show the state of the monitor handler.

To reset the MFFIFO CMDR: MFFR has to be set.

### 2.5.3. Synchron Transfer

The synchron transfer utility allows the synchronous exchange of information between the PCM interface, the configurable interface and the  $\mu P$  interface for two independent channels (A and B).

The information is buffered in the  $\mu P$  transfer data register. It is copied to there from a data memory location ponted to by the content of the  $\mu P$  transfer receive register and copied from the data register to a data memory location programmed to the  $\mu P$  transfer transmit register.

The transmit and receive register contents identify the interface as well as the time slot and port numbers of the involved channels according to tables 4.16 and 4.17. Further bits  $\ln \mu P$  transfer control register allow to restrict the synchron transfer to one of he possible sub time slots and are enabling or disabling the facility.

Thus it is possible to read information from the PCM interface input to the Synchron Data Transfer Register (STD#) via the downstream data memory and to transmit it from STD# back to the PCM output via the upstream data register, routing a loop from the PCM interface to the PCM interface. Similarly the synchron transfer facility may be used to loop configurable interface channels or to establish connections. While the information is stored in the data register it may be read and or manipulated by the µP.

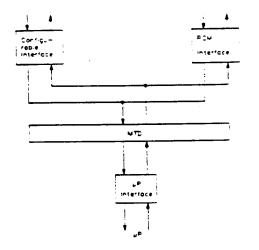

The data flow paths for the EPIC as a whole are shown in figure 2.4, for the synchron transfer facility they can be seen in figure 2.5.

Figure 2.4: Transmission and Access Possibilities of the EPIC

Figure 2.5: Synchron Transfer Paths between the  $\mu P_{\nu}$  PCM and Configurable Interfaces

In upstream transmit direction ist is necessary to ensure that no other data memory access writes to the same location in the upstream block. Hence an upstream connection involving the same PCM port and timeslot as the synchron transfer may not be programmed.

An idie code entered to the data or connection memory for the upstream or downstream directions is overwritten.

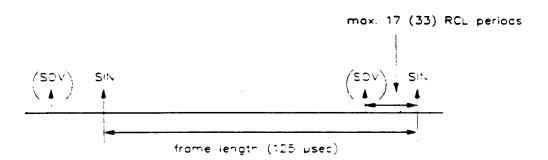

The EPIC generates interrupts guiding through the synchronous transfer. Upon the ISTA, MASK: SIN interrupt the data registers may be accessed for some time. If the data register of an active synchron transfer channel has not been accessed at the end of this time interval the ISTA, MASK: SOV interrupt is genrated, before the EPIC performs the transfer to the memory locations. After that it again issues the ISTA, MASK: SIN interrupt and the access window opens again. The repetition cycle of the synchronous transfer is identical to a frame length. The access window is closed for at most 16 RCL periods per active channel + 1 RCL period, leaving a very long data register access time. This behaviour is also shown in figure 2.6.

Figure 2.6: Synchron Transfer Flow Diagram

#### 2.6. Special Functions

#### 2.6.1. Hardware Timer

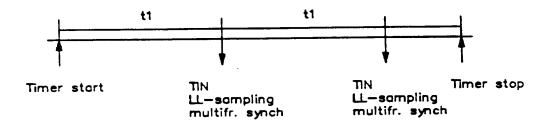

The EPIC provides an hardware timer continuously interrupting the  $\mu P$  after programmable time periods. The timer period is selected by programming TIMR: TVAL6..TVAL0. It's value is given there in multiples of 250  $\mu s$ . Programming e.g. TVAL6..TVAL0 with 07 $\mu$  gives a timer period of 2 ms. The timer is started by setting CMDR: ST to logical 1. Then STAR: TAC is set indicating the active timer. To activate the interrupt (MASK, 1STA: TIN) generation, CMDR: TIG must also be set. Now the EPIC generates a periodic interrupt whenever the timer runs out.

Besides this interrupt generation the timer is used for determining the double last look period or generating a proper CFI multiframe synchronization signal. For all three application the period is equal. The timer is stopped by accessing TIMR.

Fig. 2.7: Example of the Timer Function

## 3. Operational Description

### 3.1. Principles

Every time slot at the configurable interface is controlled by one control memory entry. Thus, the functionality of every time slot may be chosen from the choices of table 3.1.

|               | Functionality                                       | Application                    |  |  |  |  |

|---------------|-----------------------------------------------------|--------------------------------|--|--|--|--|

| Transparent   | 64 kbps to/from PCM interface<br>32 kbps<br>16 kbps | Switching                      |  |  |  |  |

| Transparent   | 64 kbps from μP Interface                           | Idle Code                      |  |  |  |  |

| Signaling Cha | annel bits 52                                       | IOM C/I channel                |  |  |  |  |

| Signaling Cha | annel bits 72                                       | e.g. analog IOM channel        |  |  |  |  |

| Signaling Cha | annel bits 70                                       | e.g. SLD signaling channel     |  |  |  |  |

| MFFIFO Cha    | nnel                                                | Monitor Channel in IOM         |  |  |  |  |

|               |                                                     | Feature Control Channel in SLD |  |  |  |  |

Tab. 3.1: CFI Time Stot Functionality Choices

Every channel may be selected in either upstream or downstream direction. The selections for the time slots are nearly independant of each other.

The only restriction is that MFFIFO and signaling channels must be programmed to adjacent time slots, starting with the MFFIFO channel at the even time slot.

The choices of table 3.1 may be programmed independantly of the selected mode.

By programming the time slots the configurable interface may be configured e.g. as a

- \* transparent PCM Interface (plain switching function)

- IOM interface

- \* SLD interface.

### 3.2. Initialization Procedure

For a proper initialization of the EPIC the following procedure is recommended.

#### 3.2.1. Reset

First a reset pulse of at least 4 PDC clock periods has to be applied.

#### 3.2.2. Register Initialization

After reset the register contents are their reset values. In the multiplexed  $\mu P$  access mode, the OMDR is left unchanged (PCM interface and CFI are in standby mode). In the demultiplexed  $\mu P$  access modes OMDR: RBS is switched to logical 1. Now the PCM interface and CFI registers can be initialized to the values necessary in the later application.

#### 3.2.3. CM Initialization

Having thus selected a proper RCL frequency, in the next step the CM is initialized. OMDR: OMS1, OMS0 are still at their reset value 00. Now programming

MACR = 70H

initalizes the complete control memory with 256 RCL periods.

It is recommended to select

MADR = FFH

for this operation.

After the control memory initialization all CFI channels are unassigned.

#### 3.2.4. CFI Configuration

As a next step CFI is configured. Using the configurable interface without preprocessed channels (as a plain PCM interface) nothing needs to be done at this step. For configuring CFI as

- SLD interface or

- IOM2 interface

the preprocessed channels need to be programmed. Selecting OMDR: OMS1, OMS0 = 10 this procedure is speeded up, since the memory access time is reduced to max. 2.5 RCL cycles from the standard max. 9.5 RCL cycles in normal operation mode (OMDR: OMS1, OMS0 = 11).

The tables 3.2 and 3.3 show the values to be programmed to MADR, MAAR and MACR for these applications.

|          | Funct     | tion |        | MACR            | MAAR                    | MADR |

|----------|-----------|------|--------|-----------------|-------------------------|------|

| Transmit | time slot | 2    | port 0 | 7Ан             | 10H                     | XVAL |

| Transmit | time slot | 3    | port 0 | 7BH             | 11 <sub>H</sub>         | FFH  |

| Transmit | time siot | 2    | port 1 | 7AH             | 12H                     | XVAL |

| Transmit | time slot | 3    | port 1 | 7BH             | 13 <sub>H</sub>         | FFH  |

| Transmit | time slot | 2    | port 2 | 7 <b>A</b> H    | 14 <sub>H</sub>         | XVAL |

| Transmit | time slot | 3    | port 2 | 7BH             | 15 <sub>H</sub>         | FFH  |

| Transmit | time slot | 2    | port 3 | 7Ан             | 16 <sub>H</sub>         | XVAL |

| Transmit | time slot | 3    | port 3 | 7BH             | 17 <sub>H</sub>         | FFH  |

| Transmit | time slot | 2    | port 4 | 7 <b>A</b> H    | 18 <sub>H</sub>         | XVAL |

| Transmit | time slot | 3    | port 4 | 7BH             | 19 <sub>H</sub>         | FFH  |

| Transmit | time siot | 2    | port 5 | 7Ан             | 1Ан                     | XVAL |

| Transmit | time slot | 3    | port 5 | 7BH             | 18 <sub>H</sub>         | FFH  |

| Transmit | time slot | 2    | port 6 | 7AH             | 1CH                     | XVAL |

| Transmit | time slot | 3    | port 6 | 7BH             | 1DH                     | FFH  |

| Transmit | time slot | 2    | port 7 | 7AH             | 1EH                     | XVAL |

| Transmit | time slot | 3    | port 7 | 7BH             | 1FH                     | FFH  |

| Receive  | time slot | 6    | port 0 | 7BH             | ВОн                     | RVAL |

| Receive  | time slot | 7    | port 0 | 7B <sub>H</sub> | B1 <sub>H</sub>         | FFH  |

| Receive  | time slot | 6    | port 1 | 78 <sub>H</sub> | <b>B</b> 2H             | RVAL |

| Receive  | time slot | 7    | port 1 | 7Вн             | <b>В</b> 3н             | FFH  |

| Receive  | time slot | 6    | port 2 | 7BH             | В4н                     | RVAL |

| Receive  | time slot | 7    | port 2 | 7B <sub>H</sub> | <b>B</b> 5H             | FFH  |

| Receive  | time slot | 6    | port 3 | 7BH             | В6н                     | RVAL |

| Receive  | time slot | 7    | port 3 | 7B <sub>H</sub> | B7H                     | FFH  |

| Receive  | time slot | 6    | port 4 | 78 <sub>H</sub> | В8н                     | RVAL |

| Receive  | time slot | 7    | port 4 | 7BH             | <b>B</b> 9H             | FFH  |

| Receive  | time slot | 6    | port 5 | 7BH             | BAH                     | RVAL |

| Receive  | time slot | 7    | port 5 | 7BH             | <b>B</b> B <sub>H</sub> | FFH  |

| Receive  | time slot | 6    | port 6 | 7BH             | ВСн                     | RVAL |

| Receive  | time slot | 7    | port 6 | 7BH             | BDH                     | FFH  |

| Receive  | time slot | 6    | port 7 | 7BH             | BEH                     | RVAL |

| Receive  | time slot | 7    | port 7 | 7BH             | BFH                     | FFH  |

Tab. 3.2: Initialization of the Preprocessed Channels in the CM in a 8 channel SLD Configuration

|          | Functi    | on       |        | MACR            | MAAR            | MADR            |

|----------|-----------|----------|--------|-----------------|-----------------|-----------------|

| Transmit | time slot | 2        | port 0 | 78/7AH          | 08н             | XVal            |

| Transmit | time slot | 3        | port 0 | 78H             | 09н             | FFH             |

| Transmit | time slot | 2        | port 1 | 78/7AH          | ОАн             | XVal            |

| Transmit | time slot | 3        | port 1 | 7BH             | ОВн             | FFH             |

| Transmit | time slot | 2        | port 2 | 78/7AH          | 0Сн             | XVal            |

| Transmit | time slot | 3        | port 2 | 7B <sub>H</sub> | 0DH             | FFH             |

| Transmit | time slot | 2        | port 3 | 78/7AH          | 0EH             | XVal            |

| Transmit | time slot | 3        | port 3 | 78 <sub>H</sub> | 0FH             | FF <sub>H</sub> |

| Transmit | time slot | 6        | port 0 | 78/7AH          | 18H             | XVa!            |

| Transmit | time slot | 7        | port 0 | 78 <sub>H</sub> | 19 <sub>H</sub> | FFH             |

| Transmit | time slot | 6        | port 1 | 78/7AH          | 1AH             | XVal            |

| Transmit | time slot | 7        | port 1 | 7 <b>8</b> H    | 1BH             | FFH             |

| Transmit | time slot | 6        | port 2 | 78/7AH          | 1CH             | XVai            |

| Transmit | time slot | 7        | port 2 | 7BH             | 1DH             | FFH             |

| Transmit | time slot | 6        | port 3 | 78H/7AH         | 1EH             | XVal            |

| Transmit | time slot | 7        | port 3 | 7 <b>B</b> H    | 1FH             | FFH             |

| Transmit | time slot | 10       | port 0 | 78/7AH          | 28H             | XVal            |

| Transmit | time siot | 11       | port 0 | 7BH             | 29н             | FFH             |

| Transmit | time slot | 10       | port 1 | 78/7AH          | 2Ан             | XVal            |

| Transmit | time slot | 11       | port 1 | 7Вн             | 2B <sub>H</sub> | FFH             |

| Transmit | time slot | 10       | port 2 | 78H/7AH         | 2CH             | XVal            |

|          | time slot | 11       | port 2 | 7Вн             | 2DH             | FFH             |

| Transmit | time slot | 10       | port 3 | 78/7AH          | 2EH             | X∀ai            |

| Transmit | time slot | 11       | port 3 | 7Вн             | 2FH             | FFH             |

| Transmit |           | 14       | port 0 | 78/7AH          | 38 <sub>H</sub> | XVal            |

| Transmit | time slot | 15       | port 0 | 7BH             | 39H             | FFH             |

| Transmit | time slot |          | port 1 | 78H/7AH         | ЗАн             | XVal            |

| Transmit | time slot | 14<br>15 | port 1 | 78 <sub>H</sub> | 3Вн             | FFH             |

| Transmit | time slot |          | •      | 78/7AH          | 3Сн             | XVal            |

| Transmit | time slot | 14       | port 2 | 78H             | 3DH             | FFH             |

| Transmit | time slot | 15       | port 2 | 78/7AH          | 3EH             | XVal            |

| Transmit | time slot | 14       | port 3 | 78 <sub>H</sub> | 3FH             | FFH             |

| Transmit | time slot | 15       | port 3 | / DH            | <del></del>     |                 |

| Transmit | time slot | 18       | port 0 | 78/7AH          | 48н             | XVal            |

| Transmit | time slot | 19       | port 0 | 7B <sub>H</sub> | 49н             | FFH             |

| Transmit | time slot | 18       | port 1 | 78/7AH          | 4Ан             | XVal            |

| Transmit | time slot | 19       | port 1 | 7Вн             | 4Вн             | FFH             |

| Transmit | time slot | 18       | port 2 | 78/7AH          | 4Сн             | XVai            |

| Transmit |           | 19       | port 2 | 78 <sub>H</sub> | 4DH             | FFH             |

| Transmit | time slot | 18       | port 3 | 78/7AH          | 4EH             | XVal            |

| Transmit | time slot | 19       | port 3 | 7 <b>8</b> H    | 4FH             | FFH             |

| Transmit |           | 22       | port 0 | 78/7AH          | 58н             | XVal            |

| Transmit |           | 23       | port 0 | 78 <sub>H</sub> | 59н             | FFH             |

| Transmit |           | 22       | port 1 | 78/7AH          | 5Ан             | XVal            |

| Transmit |           | 23       | port 1 | . <b>7В</b> н   | 5Вн             | FFH             |

| Transmit |           | 22       | port 2 | 78/7AH          | ' 5Сн           | XVai            |

| Transmit |           | 23       | port 2 | 7 <b>8</b> H    | 5DH             | FFH             |

| Transmit |           | 22       | port 3 | 78H/7AH         | 5EH             | XVal            |

| Transmit |           | 23       | port 3 | 7Вн             | 5FH             | FFH             |

|          | Func      | tion |        | MACR            | MAAR            | MADR |

|----------|-----------|------|--------|-----------------|-----------------|------|

| Transmit | time slot | 26   | port 0 | 78/7AH          | 68н             | XVal |

| Transmit | time slot | 27   | port 0 | 7BH             | 69н             | FFH  |

| Transmit | time slot | 26   | port 1 | 78/7AH          | 6Ан             | XVal |

| Transmit | time slot | 27   | port 1 | 7Вн             | 6Вн             | FFH  |

| Transmit | time slot | 26   | port 2 | 78/7AH          | 6Сн             | XVal |

| Transmit | time slot | 27   | port 2 | 7B <sub>H</sub> | 6DH             | FFH  |

| Transmit | time slot | 26   | port 3 | 78/7AH          | 6Ен             | XVai |

| Transmit | time slot | 27   | port 3 | 78 <sub>H</sub> | 6FH             | FFH  |

| Transmit | time slot | 30   | port 0 | 78/7AH          | 78 <sub>H</sub> | XVal |

| Transmit | time slot | 31   | port 0 | 78 <sub>H</sub> | 79H             | FFH  |

| Transmit | time slot | 30   | port 1 | 78/7AH          | 7 <b>A</b> H    | XVai |

| Transmit | time slot | 31   | port 1 | 7BH             | 78 <sub>H</sub> | FFH  |

| Transmit | time slot | 30   | port 2 | 78/7AH          | 7CH             | XVal |

| Transmit | time slot | 31   | port 2 | 7B <sub>H</sub> | 7DH             | FFH  |

| Transmit | time slot | 30   | port 3 | 78/7AH          | 7EH             | XVal |

| Transmit | time slot | 31   | port 3 | 7B <sub>H</sub> | 7F <sub>H</sub> | FFH  |

| Receive  | time slot | 2    | port 0 | 78H/7AH         | <b>88</b> H     | FFH  |

| Receive  | time slot | 3    | port 0 | 70H/7AH         | <b>89</b> H     | FFH  |

| Receive  | time slot | 2    | port 1 | 78h/7Ah         | 8Ан             | FFH  |

| Receive  | time slot | 3    | port 1 | 70H/7AH         | <b>8</b> BH     | FFH  |

| Receive  | time slot | 2    | port 2 | 78H/7AH         | 8CH             | FFH  |

| Receive  | time slot | 3    | port 2 | 70H/7AH         | 8DH             | FFH  |

| Receive  | time slot | 2    | port 3 | 78H/7AH         | 8EH -           | FFH  |

| Receive  | time slot | 3    | port 3 | 70H/7AH         | 8FH             | FFH  |

| Receive  | time slot | 6    | port 0 | 78H/7AH         | 98∺             | FFH  |

| Receive  | time slot | 7    | port 0 | 70h/7Ah         | <b>9</b> 9H     | FFH  |

| Receive  | time slot | 6    | port 1 | 78H/7AH         | 9AH             | FFH  |

| Receive  | time slot | 7    | port 1 | 70H/7AH         | 9BH             | FFH  |

| Receive  | time slot | 6    | port 2 | 78h/7Ah         | 9CH             | FFH  |

| Receive  | time slot | 7    | port 2 | 70H/7AH         | 9DH             | FFH  |

| Receive  | time slot | 6    | port 3 | 78h/7Ah         | 9EH             | FFH  |

| Receive  | time slot | 7    | port 3 | 70H/7AH         | 9F <sub>H</sub> | FFH  |

| Receive  | time slot | 10   | port 0 | 78H/7AH         | A8 <sub>H</sub> | FFH  |

| Receive  | time slot | 11   | port 0 | 70H/7AH         | <b>A9</b> H     | FFH  |

| Receive  | time slot | 10   | port 1 | 78H/7AH         | AAH             | FFH  |

| Receive  | time slot | 11   | port 1 | 70H/7AH         | ABH             | FFH  |

| Receive  | time slot | 10   | port 2 | 78h/7Ah         | ACH             | FFH  |

| Receive  | time slot | 11   | port 2 | 70H/7AH         | ADH             | FFH  |

|          | time slot |      | •      | 1               |                 |      |

| Receive  | rime sior | 10   | port 3 | i 78н/7Aн I     | <b>AE</b> H     | FFH  |