# 68HC05CC2

# SPECIFICATION (General Release)

© February 20, 1995

CSIC System Design Group Austin, Texas

GENERAL RELEASE SPECIFICATION

# **TABLE OF CONTENTS**

| Section                                                                                                             | on Title                                                                                                                                                               | Page                                                                                   |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|                                                                                                                     | SECTION 1 GENERAL DESCRIPTION                                                                                                                                          |                                                                                        |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.4.1<br>1.4.2<br>1.4.3<br>1.4.4<br>1.4.5<br>1.4.6<br>1.4.7<br>1.4.8<br>1.4.9<br>1.4.10 |                                                                                                                                                                        | . 1-3<br>. 1-3<br>. 1-4<br>. 1-5<br>. 1-6<br>. 1-6<br>. 1-7<br>. 1-7<br>. 1-7<br>. 1-7 |

|                                                                                                                     | SECTION 2 MEMORY                                                                                                                                                       |                                                                                        |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.5                                                                   | Memory Map Registers RAM ROM User ROM Internal ROM OSD ROM                                                                                                             | .2-2<br>.2-3<br>.2-4<br>.2-4                                                           |

|                                                                                                                     | SECTION 3 CENTRAL PROCESSING UNIT                                                                                                                                      |                                                                                        |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                         | Registers Accumulator (A) Index Register (X) Program Counter (PC) Stack Pointer (SP) Condition Code Register (CCR) Addressing Modes Immediate Direct Extended Relative | .3-2<br>.3-2<br>.3-2<br>.3-3<br>.3-4<br>.3-4<br>.3-4                                   |

| MC68H                                                                                                               | IC05CC2 MOTC                                                                                                                                                           | ROLA                                                                                   |

**TABLE OF CONTENTS**

GENERAL RELEASE SPECIFICATION

| Section                                                     | on Title                                                                                                                                                                                                                                       | Page                                               |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10         | Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset Bit Set/Clear Bit Test and Branch Inherent                                                                                                                                     | . 3-5<br>. 3-5<br>. 3-6<br>. 3-6                   |

|                                                             | SECTION 4 INTERRUPTS                                                                                                                                                                                                                           |                                                    |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9 | CPU Interrupt Processing Reset Software Interrupt (SWI) External Interrupt Pulse Accumulator Interrupts On-Screen Display Interrupt Closed-Caption Data Slicer Interrupt Synchronous Serial Interface Interrupt Multifunction Timer Interrupts | . 4-2<br>. 4-3<br>. 4-3<br>. 4-3<br>. 4-3<br>. 4-4 |

|                                                             | SECTION 5 RESETS                                                                                                                                                                                                                               |                                                    |

| 5.1<br>5.2<br>5.3<br>5.4                                    | Power-On Reset (POR) Computer Operating Properly (COP) Reset Illegal Address (ILADR) Reset RESET Pin                                                                                                                                           | . 5-1<br>. 5-2                                     |

|                                                             | SECTION 6<br>LOW POWER MODES                                                                                                                                                                                                                   |                                                    |

| 6.1<br>6.2                                                  | STOPWAIT                                                                                                                                                                                                                                       |                                                    |

|                                                             | SECTION 7 INPUT/OUTPUT PORTS                                                                                                                                                                                                                   |                                                    |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5                             | Port A Port B Port C Port D Input/Output Programming                                                                                                                                                                                           | . 7-1<br>. 7-1<br>. 7-1                            |

GENERAL RELEASE SPECIFICATION

# **TABLE OF CONTENTS**

| Section                                                                                                                          | ction Title                                                                                                                                                                                                                                                                                                               |                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                                                                                                  | SECTION 8 PULSE ACCUMULATOR                                                                                                                                                                                                                                                                                               |                                                                                  |

| 8.1<br>8.2<br>8.2.1<br>8.2.2<br>8.3<br>8.3.1<br>8.3.2<br>8.4<br>8.4.1<br>8.5<br>8.5.1<br>8.5.2<br>8.5.3<br>8.6.1<br>8.6.2<br>8.7 | Features Overview Pulse Measurement Mode Pulse Counting Mode Programming Guidelines Setup Interrupt Servicing Input/Output PAMIN Registers PAM Control Register (PAMCR) PAM Status Register (PAMSR) PAM Data Register (PAMDR) Low Power Modes Operation During WAIT Mode Operation During STOP Mode Interrupts and Resets | 8-1<br>8-1<br>8-2<br>8-2<br>8-2<br>8-3<br>8-3<br>8-3<br>8-5<br>8-6<br>8-6<br>8-6 |

|                                                                                                                                  | SECTION 9 SYNCHRONOUS SERIAL INTERFACE                                                                                                                                                                                                                                                                                    |                                                                                  |

| 9.1<br>9.2<br>9.2.1<br>9.2.2<br>9.3                                                                                              | Features Overview Master Mode Slave Mode Programming Guidelines                                                                                                                                                                                                                                                           | 9-1<br>9-1<br>9-2                                                                |

| 9.3.1<br>9.3.2<br>9.4<br>9.4.1<br>9.4.2                                                                                          | Setup Interrupt Servicing Input/Output SCK SDIO                                                                                                                                                                                                                                                                           | 9-2<br>9-3<br>9-3<br>9-3                                                         |

| 9.5<br>9.5.1<br>9.5.2<br>9.5.3                                                                                                   | Registers SSI Control Register (SSICR) SSI Status Register (SSISR) SSI Data Register (SSIDR)                                                                                                                                                                                                                              | 9-4<br>9-4<br>9-7                                                                |

| 9.6<br>9.6.1<br>9.6.2<br>9.7                                                                                                     | Low Power Modes Operation During WAIT Mode Operation During STOP Mode Interrupts and Resets                                                                                                                                                                                                                               | 9-9<br>9-9                                                                       |

# GENERAL RELEASE SPECIFICATION

# **TABLE OF CONTENTS**

| Section Title F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SECTION 10 MULTIFUNCTION TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                            |

| 10.1       Features       1         10.2       Overview       1         10.3       Programming Guidelines       1         10.3.1       Setup       1         10.3.2       Interrupt Servicing       1         10.4       Input/Output       1         10.5       Registers       1         10.5.1       MFT Control and Status Register (MFTCSR)       1         10.6       Low Power Modes       1         10.6.1       Operation During WAIT Mode       1         10.6.2       Operation During STOP Mode       1         10.7       Interrupts and Resets       1         10.7.1       Computer Operating Properly (COP) Watchdog Reset       1         10.7.2       MFT Interrupts       1                                                                                                                                                                                                                                                                 | 10-1<br>10-2<br>10-2<br>10-3<br>10-3<br>10-3<br>10-4<br>10-4<br>10-5<br>10-5                                                                               |

| SECTION 11 ON-SCREEN DISPLAY  11.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11-1                                                                                                                                                       |

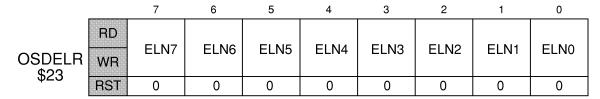

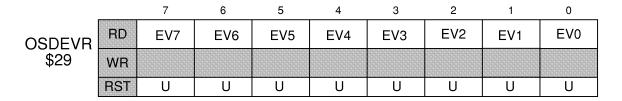

| 11.2 Overview       1         11.2.1 Synchronization       1         11.2.2 Registers and ROM       1         11.2.3 OSD Output Logic       1         11.2.4 Display Characteristics       1         11.3 Programming Guidelines       1         11.3.1 Setup       1         11.3.2 Interrupt Servicing       11         11.3.3 Software Controlled Features       11         11.4 Input/Output       11         11.4.1 HSYNC and VSYNC       11         11.4.2 PLLGND and VCO       11         11.4.3 R, G, and B Outputs       11         11.5 Registers       11         11.5.1 OSD Character Registers (OSDCH1-OSDCH34)       11         11.5.2 OSD Video Control Registers (OSDVCR1-OSDVCR2)       11         11.5.3 OSD Enable Control Register (OSDECR)       11         11.5.4 OSD Event Line Number Register (OSDELR)       11         11.5.5 OSD Event Count Register (OSDEVR)       11         11.5.6 OSD Output Control Register (OSDCR)       11 | 11-2<br>  11-3<br>  11-4<br>  11-9<br>  1-10<br>  1-11<br>  1-11<br>  1-11<br>  1-12<br>  1-13<br>  1-13<br>  1-13<br>  1-14<br>  1-17<br>  1-19<br>  1-19 |

# **TABLE OF CONTENTS**

| Section                                          | Title                                                                                                                                                                                           | Page                             |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

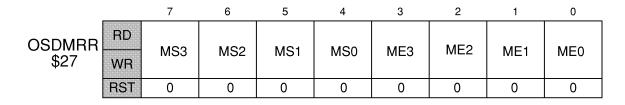

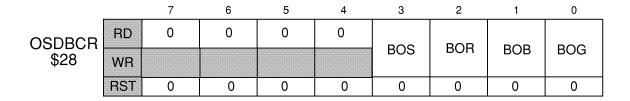

| 11.5.7<br>11.5.8<br>11.5.9<br>11.5.10<br>11.6 Lo | OSD Horizontal Delay and Character Size Register (OSDHDR) OSD Status Register OSD Matrix Range Register (OSDMRR) OSD Border Control Register (OSDBCR) ow Power Modes Operation During WAIT Mode | 11-23<br>11-23<br>11-24<br>11-25 |

| 11.6.2                                           | Operation During STOP Modeterrupts and Resets                                                                                                                                                   | 11-25                            |

|                                                  | SECTION 12 CLOSED-CAPTION DATA SLICER                                                                                                                                                           |                                  |

|                                                  |                                                                                                                                                                                                 |                                  |

|                                                  | eatures                                                                                                                                                                                         |                                  |

|                                                  | verview                                                                                                                                                                                         |                                  |

| 12.2.1                                           | Slicer                                                                                                                                                                                          |                                  |

| 12.2.2                                           | Line and Field Detection                                                                                                                                                                        |                                  |

| 12.2.3                                           | Data Sampling                                                                                                                                                                                   |                                  |

| 12.3 Pr                                          | ogramming Guidelines                                                                                                                                                                            | . 12-3                           |

| 12.3.1                                           | Setup                                                                                                                                                                                           |                                  |

| 12.3.2                                           | Interrupt Servicing                                                                                                                                                                             | . 12-3                           |

| 12.3.3                                           | Debugging                                                                                                                                                                                       | . 12-4                           |

| 12.4 In                                          | put/Output                                                                                                                                                                                      | . 12-5                           |

| 12.4.1                                           | Video                                                                                                                                                                                           | . 12-5                           |

| 12.4.2                                           | VSYNC, HSYNC, and Composite Video Input Requirements                                                                                                                                            | . 12-5                           |

| 12.5 Re                                          | egisters                                                                                                                                                                                        |                                  |

| 12.5.1                                           | DSL Character Registers (DSLCH1-DSLCH2)                                                                                                                                                         | . 12-7                           |

| 12.5.2                                           | DSL Control Register 1 (DSLCR1)                                                                                                                                                                 |                                  |

| 12.5.3                                           | DSL Control Register 2 (DSLCR2)                                                                                                                                                                 |                                  |

| 12.5.4                                           | DSL Status Register (DSLSR)                                                                                                                                                                     |                                  |

| 12.6 Lc                                          | ow Power Modes                                                                                                                                                                                  |                                  |

| 12.6.1                                           | Operation During WAIT Mode                                                                                                                                                                      |                                  |

| 12.6.2                                           | Operation During STOP Mode                                                                                                                                                                      |                                  |

|                                                  | terrupts and Resets                                                                                                                                                                             |                                  |

|                                                  |                                                                                                                                                                                                 |                                  |

|                                                  | SECTION 13 PULSE WIDTH MODULATOR                                                                                                                                                                |                                  |

|                                                  |                                                                                                                                                                                                 |                                  |

|                                                  | eatures                                                                                                                                                                                         |                                  |

|                                                  | verview                                                                                                                                                                                         |                                  |

|                                                  | ogramming Guidelines                                                                                                                                                                            |                                  |

| 13.3.1                                           | Setup                                                                                                                                                                                           | . 13-3                           |

MC68HC05CC2 Rev. 1.2

# **TABLE OF CONTENTS**

GENERAL RELEASE SPECIFICATION

| Section                                                                                                                                                                                                                                           | on Title                                                                                                                                                                | Page                                                                 |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|

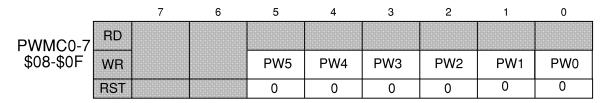

| 13.4 Input/Output 13.4.1 DA0-DA7 13.5 Registers 13.5.1 PWM Channel Registers (PWMC0-PWMC7) 13.5.2 PWM Enable Register (PWMEN) 13.6 Low Power Modes 13.6.1 Operation During WAIT Mode 13.6.2 Operation During STOP Mode 13.7 Interrupts and Resets |                                                                                                                                                                         |                                                                      |  |  |  |

|                                                                                                                                                                                                                                                   | SECTION 14 A/D CONVERTER                                                                                                                                                |                                                                      |  |  |  |

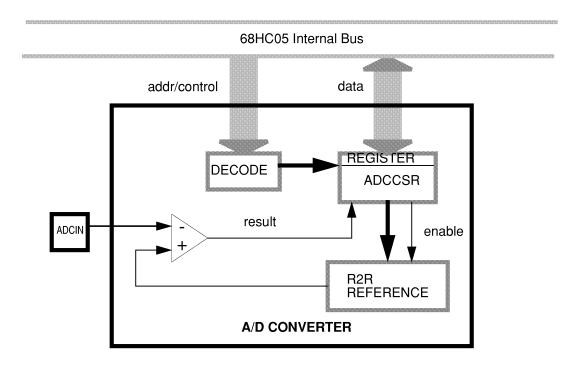

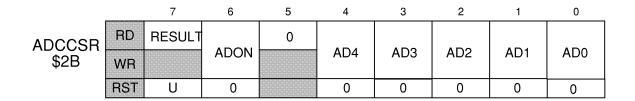

| 14.1<br>14.2<br>14.3<br>14.3.1<br>14.3.2<br>14.4<br>14.4.1<br>14.5<br>14.5.1<br>14.6<br>14.6.1<br>14.6.2                                                                                                                                          | Features Overview Programming Guidelines Setup Conversions Input/Output ADCIN Registers ADC Control/Status Register (ADCCSR) Low Power Modes Operation During WAIT Mode | 14-1<br>14-2<br>14-2<br>14-2<br>14-2<br>14-3<br>14-3<br>14-4<br>14-4 |  |  |  |

|                                                                                                                                                                                                                                                   | SECTION 15 ELECTRICAL SPECIFICATIONS                                                                                                                                    |                                                                      |  |  |  |

| 15.1<br>15.2<br>15.3<br>15.4<br>15.5                                                                                                                                                                                                              | Maximum Ratings Thermal Characteristics DC Electrical Characteristics Control Timing On-Screen Display Timing                                                           | 15-1<br>15-2<br>15-3                                                 |  |  |  |

|                                                                                                                                                                                                                                                   | SECTION 16                                                                                                                                                              |                                                                      |  |  |  |

| 16.1<br>16.2                                                                                                                                                                                                                                      | MECHANICAL SPECIFICATIONS  42-Pin SDIP Package (Case 858-01)                                                                                                            |                                                                      |  |  |  |

MOTOROLA viii

GENERAL RELEASE SPECIFICATION

# **TABLE OF CONTENTS**

| Sectio | on Title                        | Page |

|--------|---------------------------------|------|

|        | SECTION 17 ORDERING INFORMATION |      |

| 17.1   | MCU Ordering Forms              | 17-1 |

|        | Application Program Media       |      |

| 17.3   | ROM Program Verification        | 17-3 |

| 17.4   | ROM Verification Units (RVUs)   | 17-3 |

| 17.5   | MC Order Numbers                | 17-4 |

MOTOROLA MC68HC05CC2 Rev. 1.2

# **LIST OF FIGURES**

| Title                                                                                                                                         | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Assignments                                                                                                                               | 1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Register Organization Registers \$0000-\$000F Registers \$0010-\$001F Registers \$0020-\$002F Registers \$0100-\$010F Registers \$0110-\$011F | 2-3<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

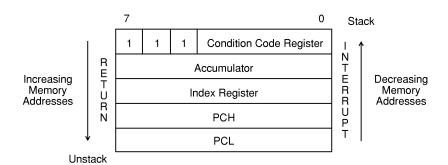

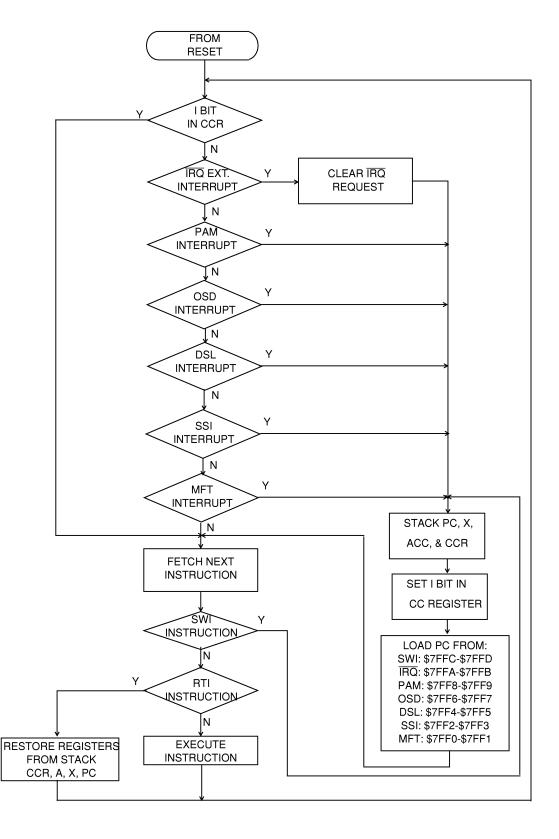

| Interrupt Flowchart                                                                                                                           | 4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

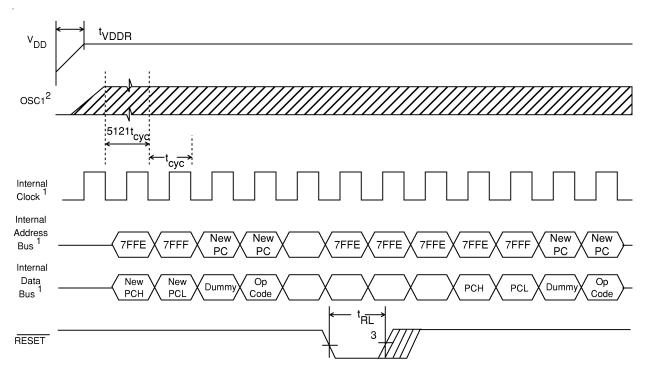

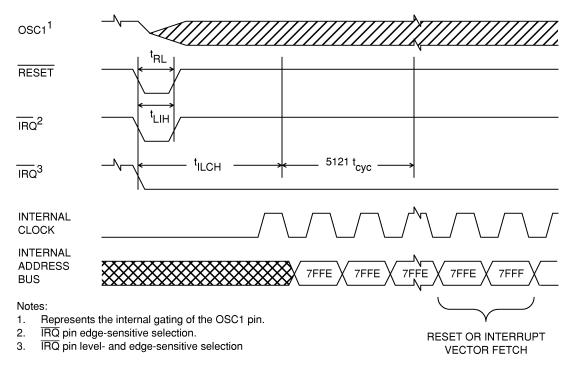

| Power-On Reset and RESET                                                                                                                      | 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

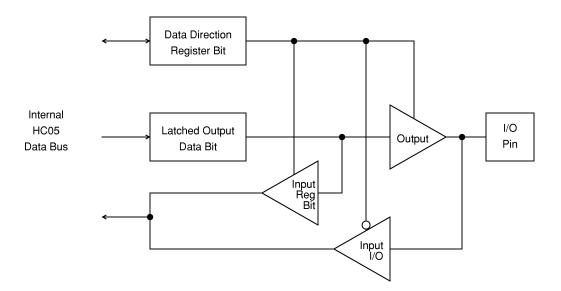

| Port I/O Circuitry                                                                                                                            | 7-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PAM Control Register (PAMCR)PAM Status Register (PAMSR)                                                                                       | 8-3<br>8-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

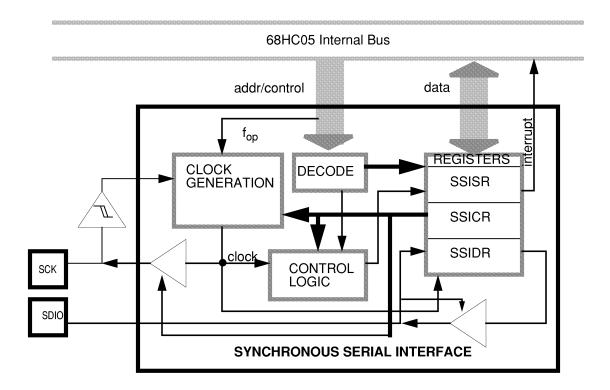

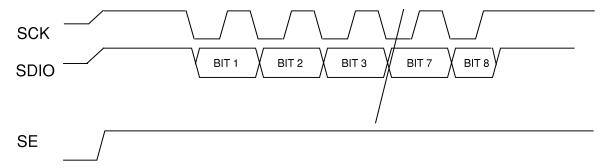

| Serial I/O Port Timing (CPOL=1) Serial I/O Port Timing (CPOL=0) SSI Control Register (SSICR) SSI Status Register (SSISR)                      | 9-4<br>9-4<br>9-5<br>9-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

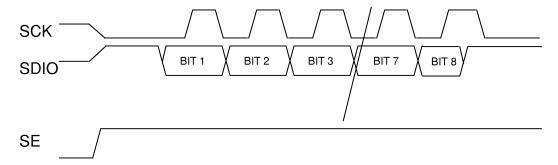

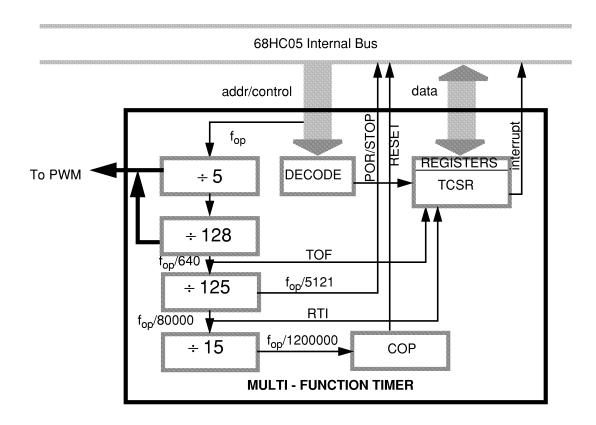

| Multifunction Timer Block Diagram                                                                                                             | 10-2<br>10-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

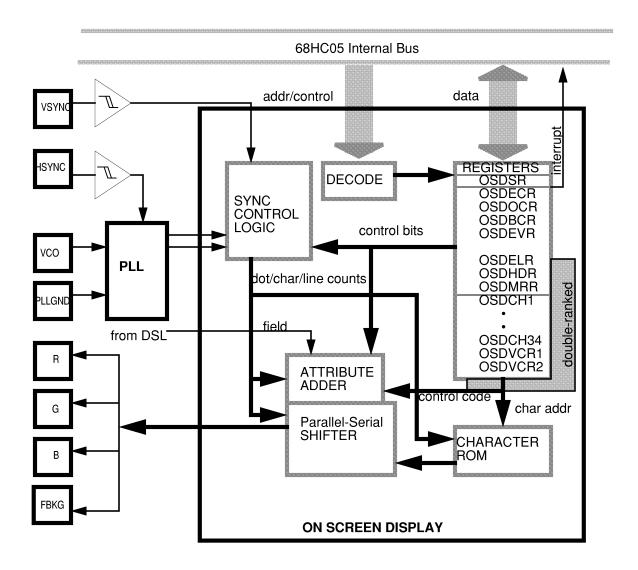

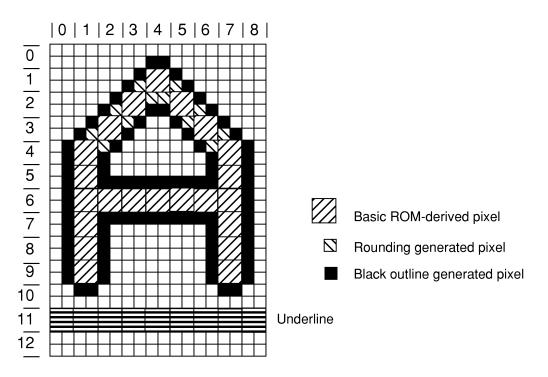

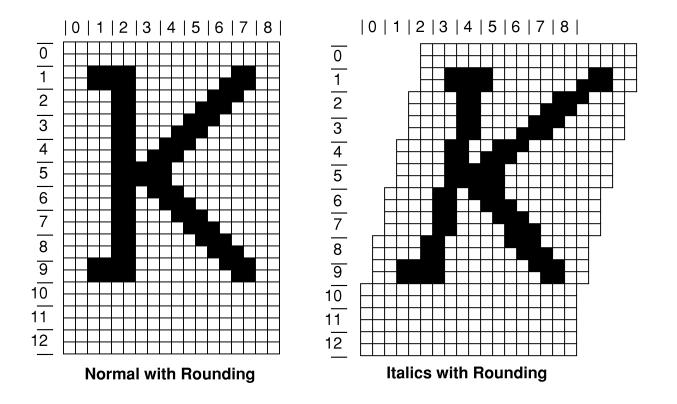

| Character Display Styles                                                                                                                      | 11-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

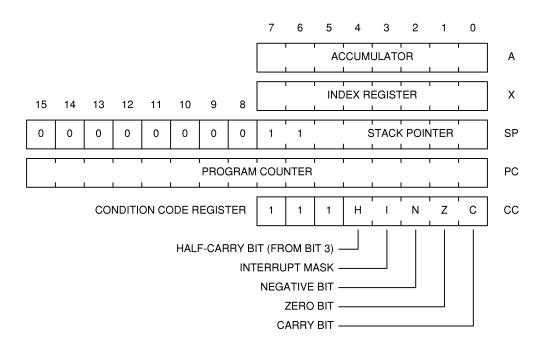

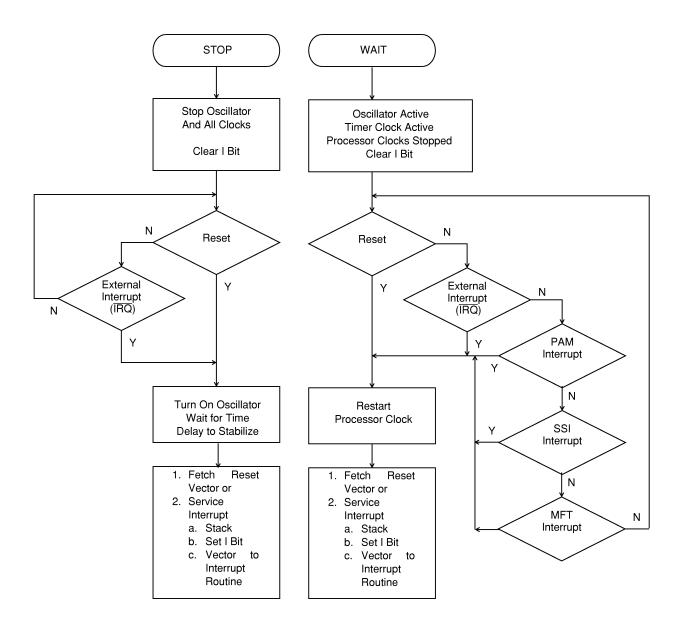

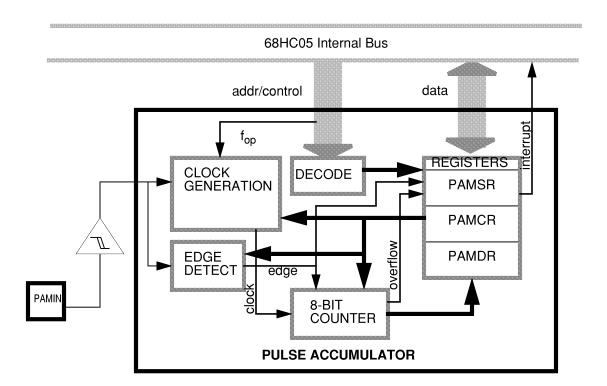

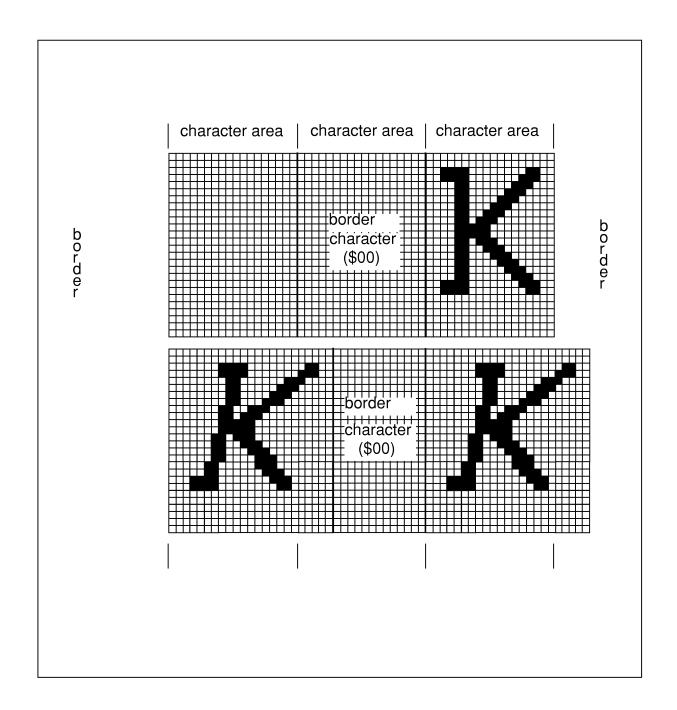

|                                                                                                                                               | Block Diagram Pin Assignments Oscillator Connections  Memory Map Register Organization Registers \$0000-\$000F Registers \$0010-\$001F Registers \$0020-\$002F Registers \$01100-\$011F Registers \$0120-\$12F  MC68HC05 Programming Model Stacking Order  Interrupt Flowchart  Power-On Reset and RESET  Stop Recovery Timing Diagram STOP/WAIT Flowchart  Port I/O Circuitry  Pulse Accumulator Block Diagram PAM Control Register (PAMCR) PAM Status Register (PAMCR) PAM Data Register (PAMDR)  SSI Block Diagram Serial I/O Port Timing (CPOL=1) Serial I/O Port Timing (CPOL=0) SSI Control Register (SSICR) SSI Status Register (SSICR) SSI Status Register (SSICR) SSI Data Register (SSICR) Multifunction Timer Block Diagram MFT Control and Status Register (MFTCSR)  OSD Block Diagram Character Display Styles Display Boundary Conditions |

MC68HC05CC2 Rev. 1.2

# **LIST OF FIGURES**

GENERAL RELEASE SPECIFICATION

| Figure                                                                                             | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                         |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

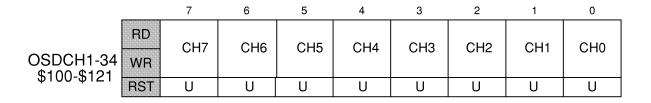

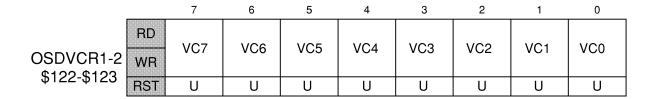

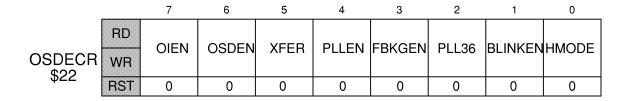

| 11-4<br>11-5<br>11-6<br>11-7<br>11-8<br>11-9<br>11-10<br>11-11<br>11-12<br>11-13<br>11-14<br>11-15 | PLL Filter Circuit  OSD Character Registers (OSDCH1-34)  OSD Video Control Registers (OSDVCR1-OSDVCR2)  Video Control Code Formats  OSD Enable Control Register (OSDECR)  OSD Event Line Number Register (OSDELR)  OSD Event Count Register (OSDEVR)  OSD Output Control Register (OSDOCR)  OSD Horizontal Delay and Character Size Register (OSDHDR)  OSD Status Register (OSDSR)  OSD Matrix Range Register (OSDMRR)  OSD Border Control Register (OSDBCR) | 1-13<br> 1-14<br> 1-15<br> 1-17<br> 1-19<br> 1-20<br> 1-21<br> 1-23<br> 1-23 |

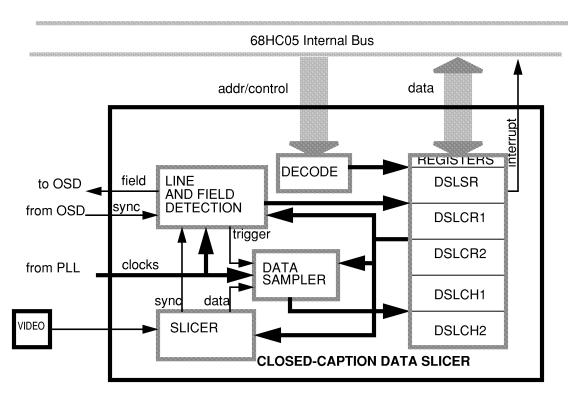

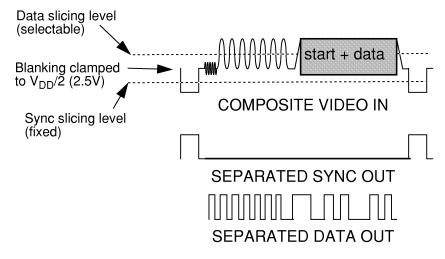

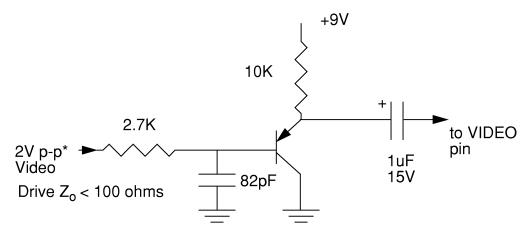

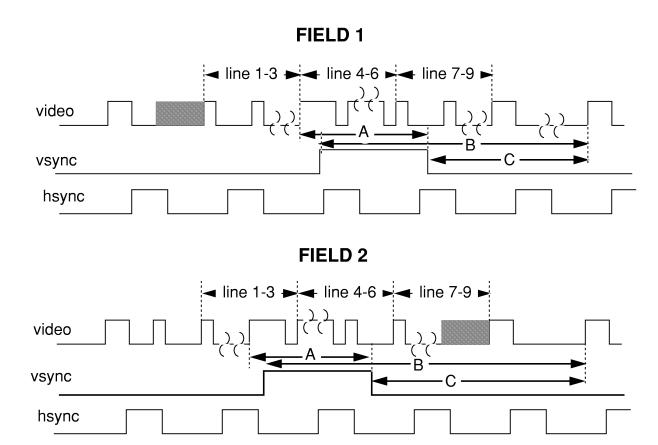

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10                      | Data Slicer Block Diagram SLICER Input and Output Video Input Circuit DSL Input Timing DSL Character Registers (DSLCH1-DSLCH2) DSL Control Register 1 (DSLCR1) DSL Control Register 2 (DSLCR2) Data/Sync Slicing Conditions for setting VPD DSL Status Register (DSLSR)                                                                                                                                                                                      | 12-2<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>2-10                         |

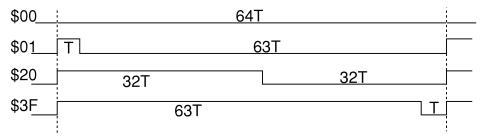

| 13-1<br>13-2<br>13-3<br>13-4                                                                       | PWM Block Diagram PWM Output Waveform Examples PWM Channel Registers (PWMC0-PWMC7) PWM Enable Register (PWMEN)                                                                                                                                                                                                                                                                                                                                               | 13-3<br>13-4                                                                 |

| 14-1<br>14-2                                                                                       | ADC Block DiagramADC Control/Status Register (ADCCSR)                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                              |

GENERAL RELEASE SPECIFICATION

# **LIST OF TABLES**

| Table        | Title                                   | Page         |

|--------------|-----------------------------------------|--------------|

| 4-1          | Vector Address for Interrupts and Reset | . 4-2        |

| 7-1          | I/O Pin Functions                       | .7-2         |

| 8-1          | Pulse Accumulator Prescaler Rates       | . 8-5        |

| 9-1          | SSI SCK Rates                           | . 9-7        |

| 10-1         | RTI and minimum COP Reset Times         | 10-5         |

| 11-1<br>11-2 | RBG Color Map                           | 1-16<br>1-22 |

| 12-2<br>12-3 | •                                       | 2-10<br>2-11 |

| 12-4         | Phase Delay Selection                   | 2-12         |

MOTOROLA MC68HC05CC2 xiv Rev. 1.2

# SECTION 1 GENERAL DESCRIPTION

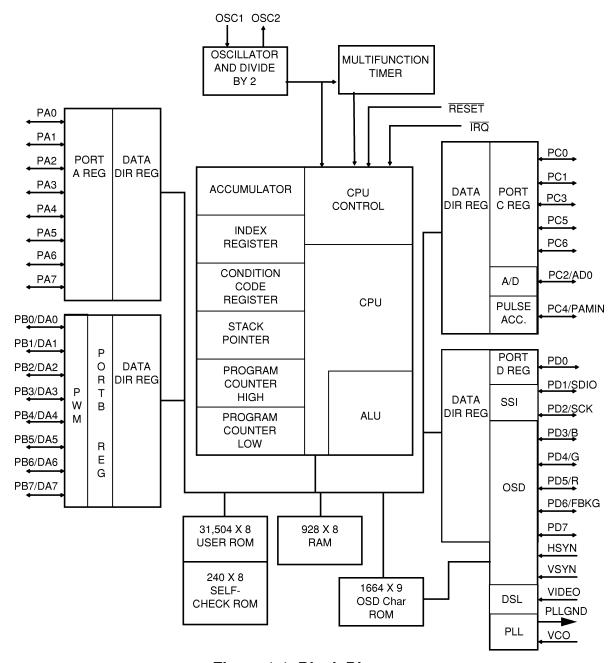

The MC68HC05CC2 HCMOS microcomputer is a member of the M68HC05 Family. This part is suitable for applications which require closed-caption decoding and TV or VCR control. This 8-bit microcomputer unit (MCU) contains an on-chip oscillator, central processing unit (CPU), RAM, ROM, serial and parallel input/output (I/O), multifunction timer, analog-to-digital (A/D) converter, pulse-width modulation (PWM) digital-to-analog (D/A) converter, closed-caption data slicer and an on-screen display video controller. A functional block diagram of the MC68HC05CC2 is shown in Figure 1-1.

#### 1.1 Features

- HC05 Core

- 4 MHz CPU Bus Operation

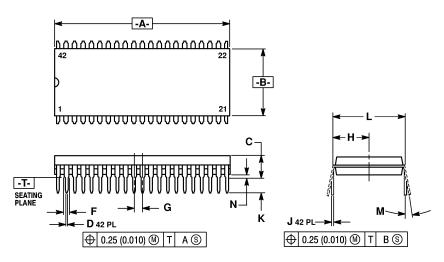

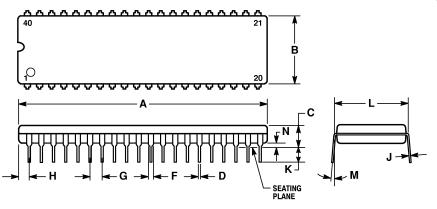

- 42-Pin Shrink Dual-in-Line (SDIP) Package

- 40-Pin Dual-in-Line (DIP) Package (pin-compatible with MC68HC05T2)

- 31 Bidirectional I/O Lines (eight open drain)

- 31,504 Bytes of User ROM

- 928 Bytes of RAM

- On-Screen Display (OSD) Controller with Closed-Caption Capability

- NTSC Closed-Caption Data Slicer (DSL) with Internal Sync Separator

- 28.2/36.3-MHz Phase-Locked Loop (PLL)

- 8-Bit Pulse Accumulator (PAM) for Infrared (IR) Decoding

- Synchronous Serial Interface (SSI) with I<sup>2</sup>C Master Capability

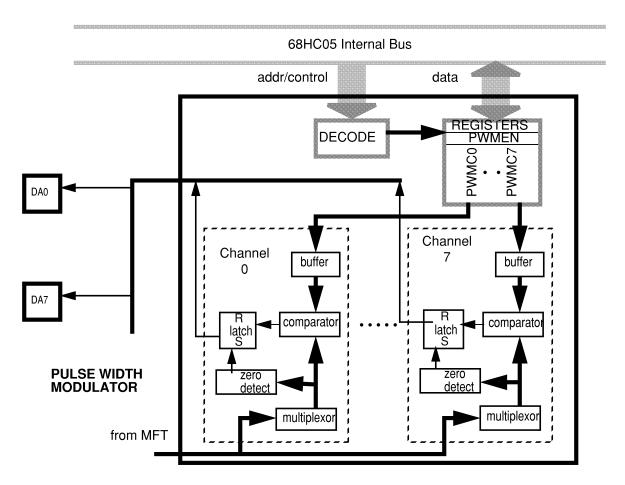

- Eight Channels of 6-Bit Pulse Width Modulated (PWM) D/A Converter

- One Channel Resistive Ladder A/D Converter (ADC)

- Multifunction Timer (MFT) with 20 ms Periodic Interrupt

- Power Saving STOP and WAIT Modes

- STOP Instruction Disable Mask Option

- COP Watchdog Timer Disable Mask Option

- Edge-Sensitive or Edge-and-Level-Sensitive Interrupt Trigger Mask Option

Figure 1-1. Block Diagram

MOTOROLA 1-2 **GENERAL DESCRIPTION**

MC68HC05CC2

#### NOTE

A line over a signal name indicates an active low signal. For example, RESET is active high and RESET is active low. Any reference to voltage, current, or frequency specified in the following sections will refer to the nominal values. The exact values and their tolerance or limits are specified in **SECTION 15 ELECTRICAL SPECIFICATIONS**.

# 1.2 Mask Options

The following mask options are available:

IRQ Interrupt Sensitivity (edge-sensitive only or edge-and-level-sensitive)

Selectable COP Watchdog

Selectable STOP Instruction

# 1.3 Pin Assignments

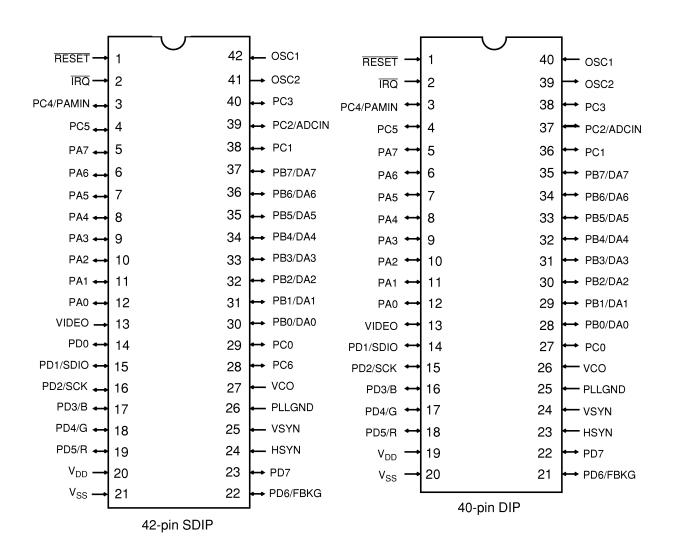

The MC68HC05CC2 is available in the 42-pin SDIP and 40-pin DIP packages. The pin assignments for these packages are shown in Figure 1-2.

Figure 1-2. Pin Assignments

# 1.4 Functional Pin Description

The following paragraphs give a description of the general function of each pin.

# 1.4.1 $V_{DD}$ and $V_{SS}$

Power is supplied to the microcontroller using these two pins.  $V_{DD}$  is the positive supply and  $V_{SS}$  is ground. The MCU operates from a single power supply.

Very fast signal transitions occur on the MCU pins. The short rise and fall times place very high short-duration current demands on the power supply. To prevent

noise problems, special care should be taken to provide good power supply bypassing at the MCU by using bypass capacitors with good high-frequency characteristics that are positioned as close to the MCU as possible.

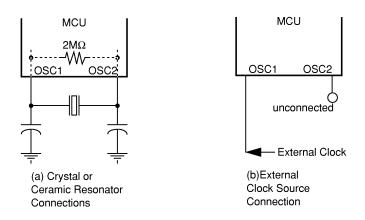

#### 1.4.2 OSC1 and OSC2

The OSC1 and OSC2 pins are the connections for the on-chip oscillator. The OSC1 and OSC2 pins can accept the following sets of components:

- 1. A crystal as shown in Figure 1-3.(a)

- 2. A ceramic resonator as shown in Figure 1-3.(a)

- 3. An external clock signal as shown in Figure 1-3.(b)

The frequency, f<sub>OSC</sub>, of the oscillator or external clock source is divided by two to produce the internal operating frequency, f<sub>OP</sub>

# 1.4.2.1 Crystal Oscillator

The circuit in Figure 1-3.(a) shows a typical oscillator circuit for an AT-cut, parallel resonant crystal. The crystal manufacturer's recommendations should be followed, since the crystal parameters determine the external component values required to provide maximum stability and reliable start-up. The load capacitance values used in the oscillator circuit design should include all stray capacitances. The crystal and components should be mounted as close as possible to the pins for start-up stabilization and to minimize output distortion. An internal start-up resistor of approximately 2  $M\Omega$  is provided between OSC1 and OSC2 for the crystal-type oscillator.

#### 1.4.2.2 Ceramic Resonator Oscillator

In cost-sensitive applications, a ceramic resonator can be used in place of the crystal. The circuit in Figure 1-3.(a) is also applicable for a ceramic resonator. The resonator manufacturer's recommendations should be followed, as the resonator parameters determine the external component values required for maximum stability and reliable starting. The load capacitance values used in the oscillator circuit design should include all stray capacitances. The ceramic resonator and components should be mounted as close as possible to the pins for start-up stabilization and to minimize output distortion. An internal start-up resistor of approximately 2  $M\Omega$  is provided between OSC1 and OSC2 for the ceramic resonator type oscillator.

## 1.4.2.3 External Clock

An external clock from another complementary metal-oxide semiconductor (CMOS) compatible device can be connected to the OSC1 input, with the OSC2 input not connected, as shown in Figure 1-3.(b).

Figure 1-3. Oscillator Connections

### 1.4.3 **RESET**

This active low input-only pin is used to reset the MCU to a known start-up state. The RESET pin contains an internal Schmitt trigger as part of its input to improve noise immunity. See **SECTION 5 RESETS** for more information.

#### 1.4.4 **IRQ**

This input pin drives the asynchronous IRQ interrupt function of the CPU. The IRQ interrupt function has a mask option to select either negative edge-sensitive triggering or both negative edge-sensitive and low level-sensitive triggering. When the former method is used, the interrupt will be cleared internally; when the latter option is selected, the interrupt will not be cleared until the rising edge of the  $\overline{IRQ}$  pin. If  $\overline{IRQ}$  is not used, it must be tied to the  $V_{DD}$  supply. The  $\overline{IRQ}$  pin contains an internal Schmitt trigger as part of its input to improve noise immunity. See **SECTION 4 INTERRUPTS** for more information.

# 1.4.5 PA0-PA7

These eight I/O lines comprise port A. The state of any pin is software programmable and all port A lines are configured as inputs during power-on or reset. See **SECTION 7 INPUT/OUTPUT PORTS** for more information.

#### 1.4.6 PB0-PB7 / DA0-DA7

These eight I/O lines comprise port B. The state of any pin is software programmable and all port B lines are configured as inputs during power-on or reset. See **SECTION 7 INPUT/OUTPUT PORTS** for more information. All of the port B pins are shared with the PWM D/A subsystem. See **SECTION 13 PULSE WIDTH MODULATOR** for a detailed description of the PWM. These eight pins have open-drain outputs.

### 1.4.7 PC0-PC6/AD0 and PAMIN

These seven I/O lines comprise port C. The state of any pin is software programmable and all port C lines are configured as inputs during power-on or reset. See **SECTION 7 INPUT/OUTPUT PORTS** for more information. PC2 is shared with the ADC subsystem. See **SECTION 14 A/D CONVERTER** for a detailed description of the ADC. PC4 is shared with the PAM subsystem. See **SECTION 8 PULSE ACCUMULATOR** for a detailed description of the PAM. PC0, PC1, PC3, PC5, and PC6 are general-purpose I/O pins. PC6 is not externally available on the 40-pin package.

## 1.4.8 PD0-PD7/SDIO, SCK, B, G, R, and FBKG

These eight I/O lines comprise port D. The state of any pin is software programmable and all port D lines are configured as inputs during power-on or reset. See **SECTION 7 INPUT/OUTPUT PORTS** for a detailed description of I/O programming. PD1 and PD2 are shared with the SSI subsystem. See **SECTION 9 SYNCHRONOUS SERIAL INTERFACE** for a detailed description of the SSI. PD3, PD4, PD5, and PD6 are shared with the OSD subsystem. See **SECTION 11 ON-SCREEN DISPLAY** for a detailed description of the OSD. PD0 and PD7 are general-purpose I/O pins. PD0 is not externally available on the 40-pin package.

### 1.4.9 VSYN and HSYN

These two input-only pins are used by the OSD subsystem to synchronize to the television. See **SECTION 11 ON-SCREEN DISPLAY** for a detailed description of the OSD. These two pins contain internal Schmitt triggers as part of their inputs to improve noise immunity.

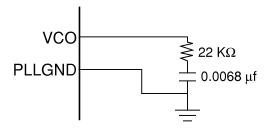

#### 1.4.10 VCO and PLLGND

These two pins are used by the PLL in the OSD subsystem. An external filter should be tied to these pins for proper operation of the PLL. See **SECTION 11 ON-SCREEN DISPLAY** for a detailed description of the OSD and PLL.

GENERAL RELEASE SPECIFICATION

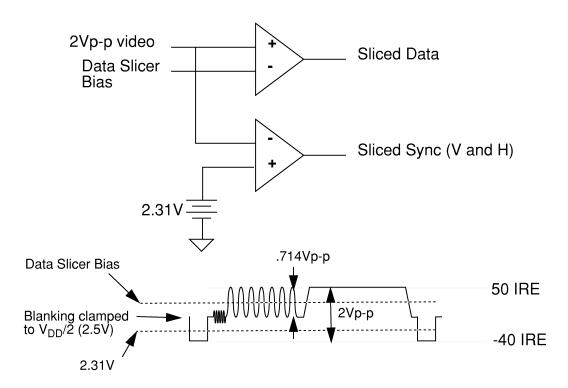

# 1.4.11 VIDEO

This input-only pin is the National Television System Committee (NTSC) composite base-band video input signal for the DSL subsystem. See **SECTION 12 CLOSED-CAPTION DATA SLICER** for a detailed description of the DSL.

# SECTION 2 MEMORY

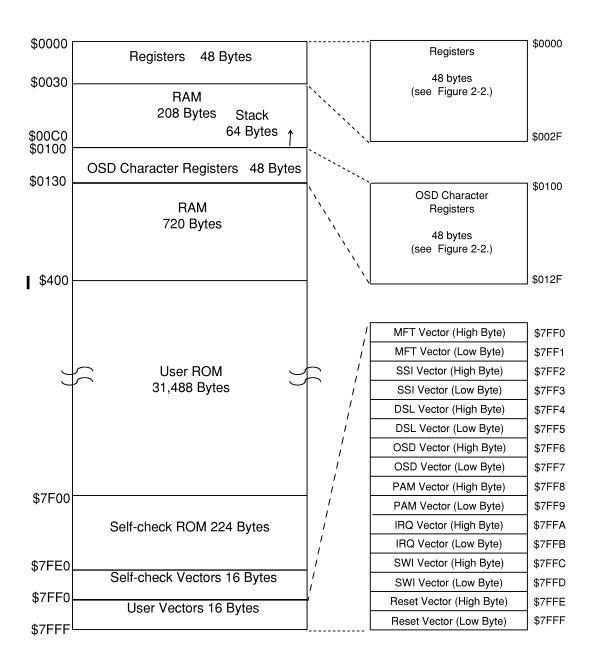

The MC68HC05CC2 has a 32-Kbyte memory map.

# 2.1 Memory Map

The memory map consists of 96 bytes of registers, 928 bytes of RAM, 31,504 bytes of user ROM and 240 bytes of self-check ROM. The OSD ROM is not available to the CPU. See Figure 2-1.

GENERAL RELEASE SPECIFICATION

Figure 2-1. Memory Map

# 2.2 Registers

The registers reside in locations \$0000-\$002F and \$0100-\$012F. The overall organization of these registers is shown in Figure 2-1. The bit assignments for each register are shown in Figure 2-3 through Figure 2-7. Reading from unimplemented bits will return unknown states, and writing to unimplemented bits will be ignored. Reserved spaces should not be read or modified.

GENERAL RELEASE SPECIFICATION

| Port A Data                 | \$0000                                 | OSD Character 1     | \$010         |

|-----------------------------|----------------------------------------|---------------------|---------------|

| Port B Data                 | \$0001                                 | OSD Character 2     | \$010         |

| Port C Data                 | \$0002                                 | OSD Character 3     | \$010         |

| Port D Data                 | \$0003                                 | OSD Character 4     | \$010         |

| Port A Data Direction       | \$0004                                 | OSD Character 5     | \$010         |

| Port B Data Direction       | \$0005                                 | OSD Character 6     | \$010         |

| Port C Data Direction       | \$0006                                 | OSD Character 7     | \$010         |

| Port D Data Direction       | \$0007                                 | OSD Character 8     | \$010         |

| PWM Channel 0               | \$0008                                 | OSD Character 9     | \$010         |

| PWM Channel 1               | \$0009                                 | OSD Character 10    | \$010         |

| PWM Channel 2               | \$000A                                 | OSD Character 11    | \$010         |

| PWM Channel 3               | \$000A E                               | OSD Character 12    | \$010         |

| PWM Channel 4               | ====================================== | OSD Character 13    | \$010         |

| PWM Channel 5               | ====================================== | OSD Character 14    | \$010         |

| PWM Channel 6               | \$000E                                 | OSD Character 15    | \$010         |

| PWM Channel 7               | \$000F                                 | OSD Character 16    | \$010         |

| PWM Enable                  | \$000P                                 | OSD Character 17    | \$010         |

| unimplemented               | 30010 E                                | OSD Character 18    | \$011         |

| RESERVED                    | \$0011                                 | OSD Character 19    | \$011         |

| DSL Control 1               | \$0012                                 | OSD Character 19    | \$011         |

| DSL Control 2               |                                        | OSD Character 21    |               |

| DSL Control 2  DSL Status   | \$0014                                 |                     | \$011         |

| DSL Status  DSL Character 1 | \$0015                                 | OSD Character 22    | \$011         |

|                             | \$0016                                 | OSD Character 23    | \$011         |

| DSL Character 2             | \$0017                                 | OSD Character 24    | \$011         |

| PAM Control                 | \$0018                                 | OSD Character 25    | \$011         |

| PAM Status                  | \$0019                                 | OSD Character 26    | \$011         |

| PAM Data                    | \$001A                                 | OSD Character 27    | \$011         |

| SSI Control                 | \$001B                                 | OSD Character 28    | \$011         |

| SSI Status                  | \$001C                                 | OSD Character 29    | \$011         |

| SSI Data                    | \$001D                                 | OSD Character 30    | \$011         |

| unimplemented               | \$001E                                 | OSD Character 31    | \$011         |

| unimplemented               | \$001F                                 | OSD Character 32    | \$011         |

| unimplemented               | \$0020                                 | OSD Character 33    | \$012         |

| unimplemented               | \$0021                                 | OSD Character 34    | \$012         |

| OSD Enable Control          | \$0022                                 | OSD Video Control 1 | \$012         |

| OSD Event Line              | \$0023                                 | OSD Video Control 2 | \$012         |

| OSD Output Control          | \$0024                                 | unimplemented       | \$012         |

| OSD Horizontal Delay        | \$0025                                 | unimplemented       | \$012         |

| OSD Status                  | \$0026                                 | unimplemented       | \$012         |

| OSD Matrix Range            | \$0027                                 | unimplemented       | \$012         |

| OSD Border Control          | \$0028                                 | unimplemented       | \$012         |

| OSD Event Count             | \$0029                                 | unimplemented       | \$012         |

| RESERVED                    | \$002A                                 | unimplemented       | <b></b> \$012 |

| ADC Control/Status          | \$002B                                 | unimplemented       | \$012         |

| unimplemented               | \$002C                                 | unimplemented       | \$012         |

| MFT Control/Status          | \$002D                                 | unimplemented       | \$012         |

| unimplemented               | \$002E                                 | unimplemented       | \$012         |

| RESĖRVED                    | \$002F                                 | unimplemented       | \$012         |

\$0010 - \$002F

Figure 2-2. Register Organization

\$0100-\$012F

#### 2.3 RAM

The RAM consists of 928 bytes divided into two segments. The first RAM segment, including the stack area, is from \$0030 through \$00FF. The second RAM segment is from \$0130 through \$03FF. The stack begins at address \$00FF. The stack pointer can access 64 bytes of RAM in the range \$00FF to \$00C0. See **3.1.4 Stack Pointer (SP)**.

### **NOTE**

Using the stack area for data storage or temporary work locations requires care to prevent it from being overwritten due to stacking from an interrupt or subroutine call.

GENERAL RELEASE SPECIFICATION

#### 2.4 ROM

The MC68HC05CC2 contains 31-Kbytes of CPU-accessible ROM, which is divided into user ROM and internal ROM.

#### 2.4.1 User ROM

The user ROM consists of 31,504 bytes of ROM: 31,488 bytes of program space from \$400 through \$7EFF and 16 bytes of user vectors from \$7FF0 through \$7FFF.

All of the user vectors, from \$7FF0 through \$7FFF, are dedicated to reset and interrupt vectors.

#### 2.4.2 Internal ROM

The internal, or fixed data, section of the ROM is used for factory testing. The self-check ROM consists of 224 bytes of code from \$7F00 through \$7FDF and 16 bytes of vectors from \$7FE0 through \$7FEF.

# 2.5 OSD ROM

The OSD ROM consists of 128 9  $\times$  13 bit matrices, or 14,976 bits. This ROM is used by the OSD to define the characters which can be displayed on the television screen. The OSD ROM is not accessible by the CPU.

GENERAL RELEASE SPECIFICATION

| ADDR   | REGISTER                      | READ<br>WRITE | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------------------------------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$0000 | PORT A DATA<br>PORTA          | R<br>W        | PA7   | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

| \$0001 | PORT B DATA<br>PORTB          | R<br>W        | PB7   | PB6   | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   |

| \$0002 | PORT C DATA<br>PORTC          | R<br>W        | 0     | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| \$0003 | PORT D DATA<br>PORTD          | R<br>W        | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| \$0004 | PORT A DATA DIRECTION<br>DDRA | R<br>W        | DDRA7 | DDRA6 | DDRA5 | DDRA4 | DDRA3 | DDRA2 | DDRA1 | DDRA0 |

| \$0005 | PORT B DATA DIRECTION<br>DDRB | R<br>W        | DDRB7 | DDRB6 | DDRB5 | DDRB4 | DDRB3 | DDRB2 | DDRB1 | DDRB0 |

| \$0006 | PORT C DATA DIRECTION<br>DDRC | R<br>W        | 0     | DDRC6 | DDRC5 | DDRC4 | DDRC3 | DDRC2 | DDRC1 | DDRC0 |

| \$0007 | PORT D DATA DIRECTION<br>DDRD | R<br>W        | DDRD7 | DDRD6 | DDRD5 | DDRD4 | DDRD3 | DDRD2 | DDRD1 | DDRD0 |

| \$0008 | PWM CHANNEL 0<br>PWMC0        | R<br>W        |       |       | PW5   | PW4   | PW3   | PW2   | PW1   | PW0   |

| \$0009 | PWM CHANNEL 1<br>PWMC1        | R<br>W        |       |       | PW5   | PW4   | PW3   | PW2   | PW1   | PW0   |

| \$000A | PWM CHANNEL 2<br>PWMC2        | R<br>W        |       |       | PW5   | PW4   | PW3   | PW2   | PW1   | PW0   |

| \$000B | PWM CHANNEL 3<br>PWMC3        | R<br>W        |       |       | PW5   | PW4   | PW3   | PW2   | PW1   | PW0   |

| \$000C | PWM CHANNEL 4<br>PWMC4        | R<br>W        |       |       | PW5   | PW4   | PW3   | PW2   | PW1   | PW0   |

| \$000D | PWM CHANNEL 5<br>PWMC5        | R<br>W        |       |       | PW5   | PW4   | PW3   | PW2   | PW1   | PW0   |

| \$000E | PWM CHANNEL 6<br>PWMC6        | R<br>W        |       |       | PW5   | PW4   | PW3   | PW2   | PW1   | PW0   |

| \$000F | PWM CHANNEL 7<br>PWMC7        | R<br>W        |       |       | PW5   | PW4   | PW3   | PW2   | PW1   | PW0   |

UNIMPLEMENTED RESERVED

Figure 2-3. Registers \$0000-\$000F

### GENERAL RELEASE SPECIFICATION

| ADDR   | REGISTER                  | READ<br>WRITE | 7     | 6      | 5      | 4     | 3      | 2          | 1     | 0     |

|--------|---------------------------|---------------|-------|--------|--------|-------|--------|------------|-------|-------|

| \$0010 | PWM ENABLE<br>PWMEN       | R W           | CHEN7 | CHEN6  | CHEN5  | CHEN4 | CHEN3  | CHEN2      | CHEN1 | CHEN0 |

| \$0011 | unimplemented             | R<br>W        |       |        |        |       |        |            |       |       |

| \$0012 | RESERVED                  | R<br>W        |       |        |        |       |        |            |       |       |

| \$0013 | DSL CONTROL 1<br>DSLCR1   | R<br>W        | DSIEN | DSEN   | LINE5  | LINE4 | LINE3  | LINE2      | LINE1 | 0     |

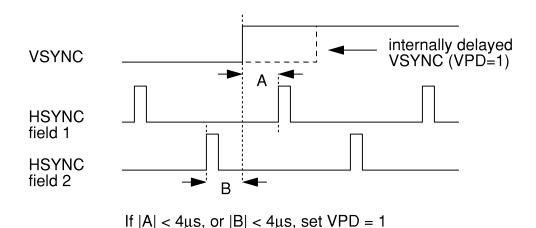

| \$0014 | DSL CONTROL 2<br>DSLCR2   | R<br>W        | VR1   | VR0    | PW1    | PW0   | VPD    | PD2        | PD1   | PD0   |

| \$0015 | DSL STATUS<br>DSLSR       | R<br>W        | DSFL  | OVFL   | FIELD1 | INTLC | CSYNC  | VPDET      | RIC1  | RIC0  |

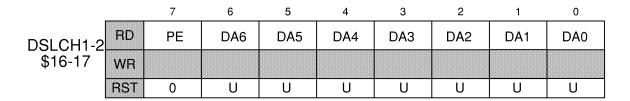

| \$0016 | DSL CHARACTER 1<br>DSLCH1 | R             | PE    | DA6    | DA5    | DA4   | DA3    | DA2        | DA1   | DA0   |

|        | DSL CHARACTER 2           | W             | PE    | DA6    | DA5    | DA4   | DA3    | DA2        | DA1   | DA0   |

| \$0017 | DSLCH2                    | w             |       |        |        |       |        |            |       |       |

| \$0018 | PAM CONTROL<br>PAMCR      | R<br>W        | PAFIE | PAOVIE | PAPOL  | PAEN  | PAMODE | 0<br>PARST | PAPR1 | PAPR0 |

| \$0019 | PAM STATUS<br>PAMSR       | R<br>W        | PAF   | PAOVF  | PAPIN  | 0     | 0      | 0          | 0     | 0     |

| \$001A | PAM DATA                  | R             | DA7   | DA6    | DA5    | DA4   | DA3    | DA2        | DA1   | DA0   |

| \$001B | PAMDR SSI CONTROL SSICR   | R<br>W        | SIE   | SE     | LSBF   | MSTR  | CPOL   | T/R        | SR1   | SR0   |

| \$001C | SSI STATUS<br>SSISR       | R<br>W        | SF    | DCOL   | 0      | 0     | 0      | 0          | 0     | 0     |

| \$001D | SSI DATA<br>SSIDR         | R<br>W        | DA7   | DA6    | DA5    | DA4   | DA3    | DA2        | DA1   | DA0   |

| \$001E | unimplemented             | R<br>W        |       |        |        |       |        |            |       |       |

| \$001F | unimplemented             | R<br>W        |       |        |        |       |        |            |       |       |

UNIMPLEMENTED RESERVED

Figure 2-4. Registers \$0010-\$001F

GENERAL RELEASE SPECIFICATION

| ADDR   | REGISTER                       | READ<br>WRITE | 7      | 6     | 5    | 4     | 3         | 2          | 1      | 0     |

|--------|--------------------------------|---------------|--------|-------|------|-------|-----------|------------|--------|-------|

| \$0020 | unimplemented                  | R<br>W        |        |       |      |       |           |            |        |       |

| \$0021 | unimplemented                  | R<br>W        |        |       |      |       |           |            |        |       |

| \$0022 | OSD ENABLE CONTROL<br>OSDECR   | R<br>W        | OIEN   | OSDEN | XFER | PLLEN | FBKGEN    | PLL36      | BLNKEN | HMODE |

| \$0023 | OSD EVENT LINE<br>OSDELR       | R<br>W        | ELN7   | ELN6  | ELN5 | ELN4  | ELN3      | ELN2       | ELN1   | ELN0  |

| \$0024 | OSD OUTPUT CONTROL OSDOCR      | R<br>W        | HINV   | VINV  | CINV | FBINV | FDINV     | REN        | BEN    | GEN   |

| \$0025 | OSD HORIZONTAL DELAY<br>OSDHDR | R<br>W        | CHHS   | CHWS  | HD5  | HD4   | HD3       | HD2        | HD1    | HD0   |

| \$0026 | OSD STATUS<br>OSDSR            | R<br>W        | OSDFL  | HSYN  | VSYN | 0     | 0         | 0          | 0      | 0     |

| \$0027 | OSD MATRIX RANGE<br>OSDMRR     | R<br>W        | MS3    | MS2   | MS1  | MS0   | ME3       | ME2        | ME1    | ME0   |

| \$0028 | OSD BORDER CONTROL<br>OSDBCR   | R<br>W        | 0      | 0     | 0    | 0     | BOS       | BOR        | вов    | BOG   |

| \$0029 | OSD EVENT COUNT<br>OSDEVR      | R<br>W        | EV7    | EV6   | EV5  | EV4   | EV3       | EV2        | EV1    | EV0   |

| \$002A | RESERVED                       | R<br>W        |        |       |      |       |           |            |        |       |

| \$002B | ADC CONTROL/STATUS<br>ADCCSR   | R<br>W        | RESULT | ADON  | 0    | AD4   | AD3       | AD2        | AD1    | AD0   |

| \$002C | unimplemented                  | R<br>W        |        |       |      |       |           |            |        |       |

| \$002D | MFT CONTROL/STATUS<br>MFTCSR   | R<br>W        | TOF    | RTIF  | TOFE | RTIE  | 0<br>TOFC | 0<br>RTIFC | 0      | 0     |

| \$002E | unimplemented                  | R<br>W        |        |       |      |       |           |            |        |       |

| \$002F | RESERVED                       | R<br>W        |        |       |      |       |           |            |        |       |

UNIMPLEMENTED RESERVED RESERVED

Figure 2-5. Registers \$0020-\$002F

### GENERAL RELEASE SPECIFICATION

| ADDR   | REGISTER                    | READ<br>WRITE | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----------------------------|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| \$0100 | OSD CHARACTER 1<br>OSDCH1   | R<br>W        | CH7 | CH6 | CH5 | CH4 | СНЗ | CH2 | CH1 | CH0 |

| \$0101 | OSD CHARACTER 2<br>OSDCH2   | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$0102 | OSD CHARACTER 3<br>OSDCH3   | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$0103 | OSD CHARACTER 4<br>OSDCH4   | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$0104 | OSD CHARACTER 5<br>OSDCH5   | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$0105 | OSD CHARACTER 6<br>OSDCH6   | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$0106 | OSD CHARACTER 7<br>OSDCH7   | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$0107 | OSD CHARACTER 8<br>OSDCH8   | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$0108 | OSD CHARACTER 9<br>OSDCH9   | R<br>W        | CH7 | CH6 | CH5 | CH4 | СНЗ | CH2 | CH1 | CH0 |

| \$0109 | OSD CHARACTER 10<br>OSDCH10 | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$010A | OSD CHARACTER 11<br>OSDCH11 | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$010B | OSD CHARACTER 12<br>OSDCH12 | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$010C | OSD CHARACTER 13<br>OSDCH13 | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$010D | OSD CHARACTER 14<br>OSDCH14 | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$010E | OSD CHARACTER 15<br>OSDCH15 | R<br>W        | CH7 | CH6 | CH5 | CH4 | CH3 | CH2 | CH1 | CH0 |

| \$010F | OSD CHARACTER 16<br>OSDCH16 | R<br>W        | CH7 | CH6 | CH5 | CH4 | СНЗ | CH2 | CH1 | СНО |