## CMOS 8-BIT MICROCONTROLLERS

# TMP90C802AP/TMP90C802AM TMP90C803AP/TMP90C803AP

#### 1. OUTLINE AND CHARACTERISTICS

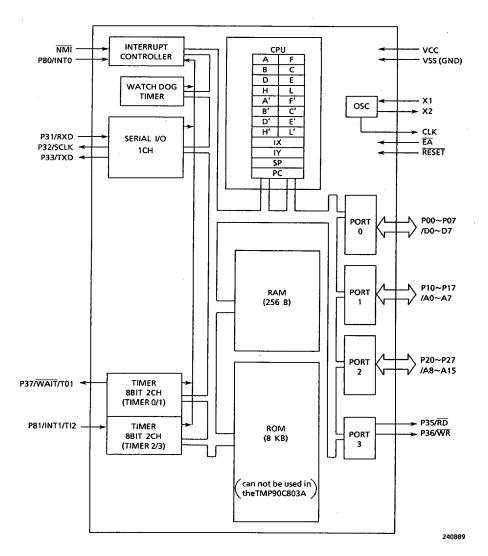

The TMP90C802A is a high-speed advanced 8-bit micro controller applicable to a variety of equipment.

With its 8-bit CPU, ROM, RAM, timer/event counter and general-purpose serial interface integrated into a single CMOS chip, the TMP90C802A allows the expansion of external memories (up to 56K byte). The TMP90C803A is the same as the TMP90C802A but without the ROM.

The TMP90C802AP/803AP is in a DIP package.

The TMP90C802AM/803AM is in a SOP (Small Outline Package).

The characteristics of the TMP90C802A include:

- Powerful instructions: 163 basic instructions, including Multiplication, division, 16-bit arithmetic operations, bit manipulation instructions

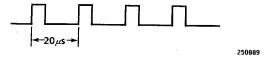

- (2) Minimum instruction executing time: 320 ns (at 12.5 MHz oscillation frequency)

- (3) Internal ROM: 8K byte (The TMP90C803A does not have a built-in ROM.)

- (4) Internal RAM: 256 byte

- (5) Memory expansion

External memory: 56K byte

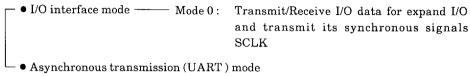

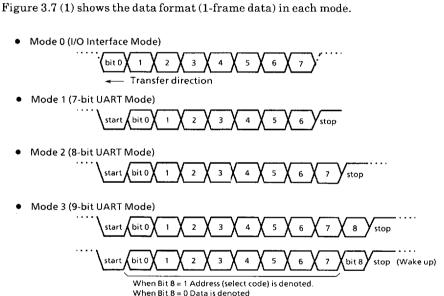

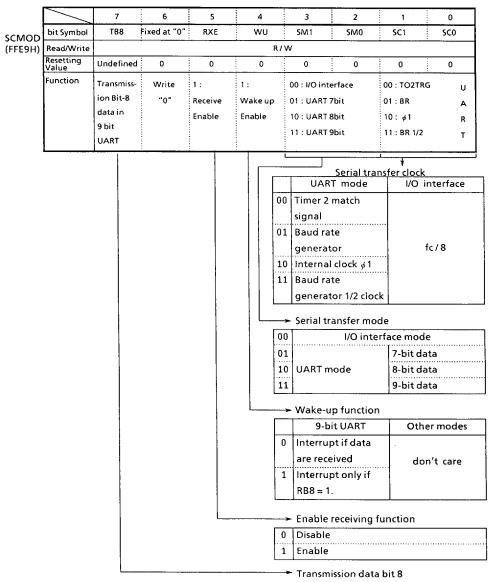

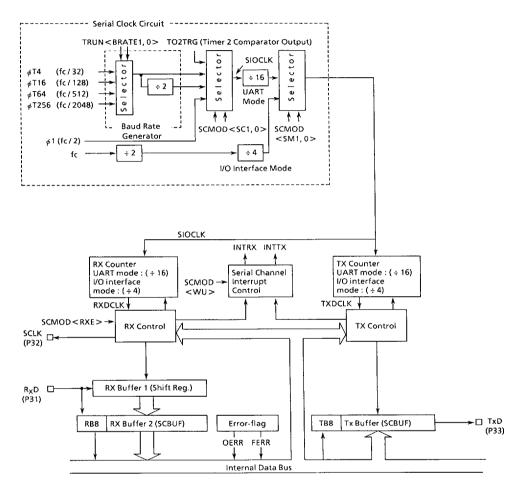

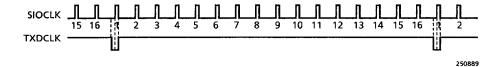

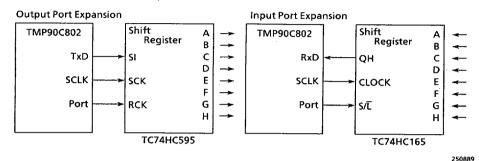

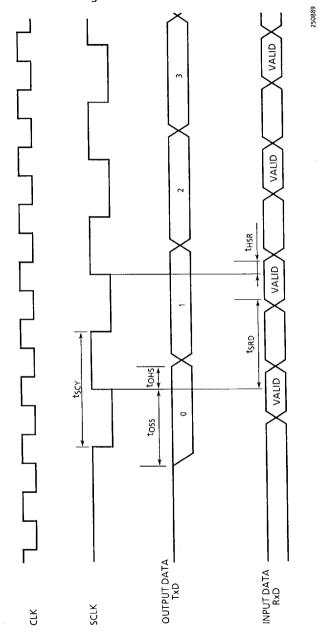

- (6) General-purpose serial interface (1 channel) Asynchronous mode, I/O interface mode

- (7) 8-bit timers (4 channels): (1 external clock input)

- (8) Port with zero cross detection circuit (1 input)

- (9) Input/Output ports (TMP90C802A: 32pins, TMP90C803A: 6pins)

- (10) Interrupt function: 8 internal interrupts and 3 external interrupts

- (11) Micro Direct Memory Access (DMA) function (4 channels)

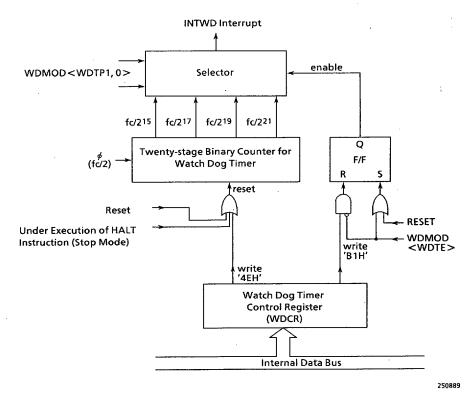

- (12) Watchdog timer

- (13) Standby function (4 HALT modes)

MCU90-259

🖿 9097249 0040715 963 **=**

Powered by ICminer.com Electronic-Library Service CopyRight 2003

Figure 1 TMP90C802A Block Diagram

#### MCU90-260

📟 9097249 0040716 8TT 📟

## 2. PIN ASSIGNMENT AND FUNCTIONS

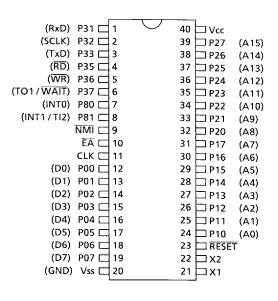

The assignment of input/output pins, their names and functions are described below.

#### 2.1 Pin Assignment

Figure 2.1 shows pin assignment of the TMP90C802A/803A.

Figure 2.1 Pin Assignment

240889

**9**997249 0040717 736 **=**

#### 2.2 Pin Names and Functions

The names of input/output pins and their functions are summarized in Table 2.2.

Table 2.2 Pin Names and Functions (1/2)

| Pin Name | No. of pins | I/O 3 states | Function                                                                                                  |

|----------|-------------|--------------|-----------------------------------------------------------------------------------------------------------|

| P00~P07  | 8           | I/O          | Port 0: 8-bit I/O port that allows selection of input/output on byte basis                                |

| /D0~D7   |             | 3 states     | Data bus: Also functions as 8-bit bidirectional data bus for external memory (For 803A, fixed to databus) |

| P10~P17  | 8           | I/O          | Port 1: 8-bit I/O port that allows selection on byte basis                                                |

| /A0~A7   |             | Output       | Address bus: The lower 8 bits address bus for external memory (For 803A, fixed to address bus)            |

| P20~P27  | 8           | 1/0          | Port 2: 8-bit I/O port that allows selection on bit basis                                                 |

| /A8~A15  |             | Output       | Address bus: The upper 8 bits address bus for external memory (For 803A, fixed to address bus)            |

| P31      | 1           | Input        | Port 31: 1-bit input port                                                                                 |

| /RxD     |             |              | Receives Serial Data                                                                                      |

| P32      | 1           | Output       | Port 32: 1-bit output port                                                                                |

| /SCLK    |             |              | Serial clock output                                                                                       |

| P33      | 1           | Output       | Port 33: 1-bit output port                                                                                |

| /TxD     |             |              | Transmittes Serial Data                                                                                   |

| P35      | 1           | Output       | Port 35: 1-bit output port                                                                                |

| /RD      |             |              | Read: Generates strobe signal for reading external memory                                                 |

| P36      | 1           | Output       | Port 36: 1-bit output port                                                                                |

| /WR      |             |              | Write: Generates strobe signal for writing into external memory                                           |

| P37      | 1           | Input        | Port 37: 1-bit input port                                                                                 |

| /WAIT    |             |              | Wait: Input pin for connecting slow speed memory or peripheral LSI                                        |

| /TO1     |             | Output       | Timer output 1: Output of Timer 0 or 1                                                                    |

| P80      | 1           | Input        | Port 80: 1-bit input port                                                                                 |

| /INTO    |             |              | Interrupt request pin 0: interrupt request pin (Level/rising edge is programmable)                        |

| P81      | 1           | Input        | Port 81: 1-bit input port                                                                                 |

| /INT1    |             |              | Interrupt request pin 1: interrupt request pin (Rising edge)                                              |

| /TI2     |             |              | Timer input 2: Counter input signal for Timer 2                                                           |

| NMI      | 1           | Input        | Non-maskable interrupt request pin: Falling edge interrupt request pin                                    |

#### MCU90-262

9097249 0040718 672

Table 2.2 Pin Names and Functions (2/2)

| Pin Name  | No. of pins | I/O 3 states     | Function                                                                                                                              |

|-----------|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| CLK       | 1           | Output           | Clock output: Generates clock pulse at 1/4 frequency of clock oscillation. It is pulled up internally during resetting.               |

| ĒĀ        | 1           | Input            | External access: Connects with Vcc pin in the TMP90C802A using internal ROM, and with GND pin in the TMP90C803A with no internal ROM. |

| RESET     | 1           | Input            | Reset: Initializes the TMP90C802A/803A (Built in pull-up resister)                                                                    |

| X1/X2     | 2           | Input/<br>Output | Pin for quartz crystal or ceramic resonator (1~12.5MHz)                                                                               |

| Vcc       | 1           |                  | Power supply ( + 5V)                                                                                                                  |

| Vss (GND) | 1           |                  | Ground (0V)                                                                                                                           |

120889

MCU90-263

9097249 0040719 509

#### OPERATION

This chapter describes the functions and the basic operations of the TMP90C802A in every block.

#### 3.1 CPU

TMP90C802A includes a high performance 8-bit CPU. For the function of CPU, see the previous chapter "TLCS-90 CPU." This chapter explains exclusively the functions of the CPU of TMP90C802A which are not described in the "TLCS-90 CPU."

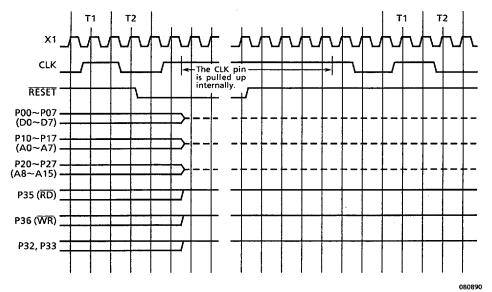

#### 3.1.1 Reset

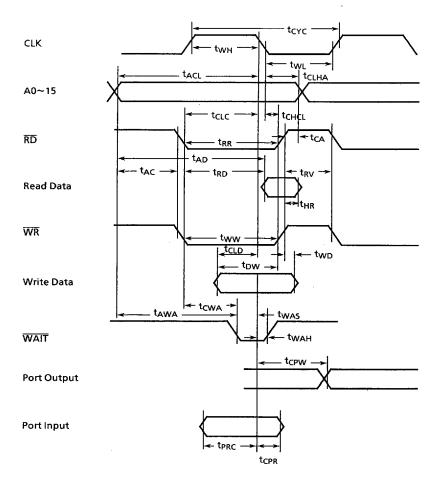

The basic timing of the reset operation is indicated in Figure 3.1. In order to reset the TMP90C802A, the RESET input must be maintained at the "0" level for at least ten system clock cycles (10 states :  $2\mu s$  at 10MHz) within an operating voltage band and with as table oscillation. When a reset request is accepted, all I/O ports (Port 0 /data bus D0~D7, Port 1/address bus A0~A7, Port 2/address bus A8~A15) function as input ports (high impedance state). Output ports (P32, P33, P35 ( $\overline{\text{RD}}$ ) and P36 ( $\overline{\text{WR}}$ )) and CLK turn to "1." Input ports remain unchanged.

The registers of the CPU also remain unchanged. Note, however, that the program counter "PC" and the interrupt enable flag IFF are cleared to "0". Register A shows an undefined status.

When the reset is cleared, the CPU starts executing instructions from the address 0000H.

Figure 3.1 Reset Timing

MCU90-264

**-** 9097249 0040720 220 **-**

#### 3.1.2 EXF (Exchange Flag)

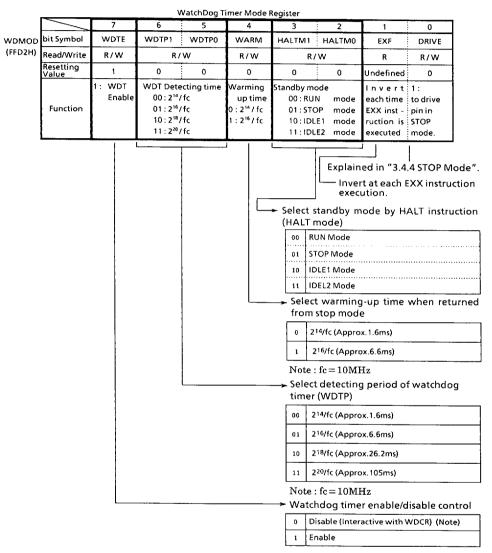

For TMP90C802A, "EXF", which is inverted when the command "EXX" is executed to transfer data between the main register and the auxiliary register, is allocated to the first bit of memory address FFD2H.

|         |                    | 7                 | 6                                                                                                            | 5        | 4                                                                        | 3                                                      | 2                            | 1                                                          | 0                                       |

|---------|--------------------|-------------------|--------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------|--------------------------------------------------------|------------------------------|------------------------------------------------------------|-----------------------------------------|

| (EED2H) | bit Symbol         | WDTE              | WDTP1                                                                                                        | WDTP0    | WARM                                                                     | HALTM1                                                 | HALTM0                       | EXF                                                        | DRIVE                                   |

|         | Read/Write         | R/W               | R/                                                                                                           | w        | R/W                                                                      | R/W                                                    |                              | R                                                          | R/W                                     |

|         | Resetting<br>Value | 1                 | 0                                                                                                            | 0        | 0                                                                        | 0                                                      | 0                            | Undefined                                                  | 0                                       |

|         | Function           | 1 : WDT<br>Enable | WDT Dete<br>00: 2 <sup>14</sup> /<br>01: 2 <sup>16</sup> /<br>10: 2 <sup>18</sup> /<br>11: 2 <sup>20</sup> / | fc<br>fc | Warming<br>up time<br>0: 2 <sup>14</sup> / fc<br>1: 2 <sup>16</sup> / fc | Standby me<br>00: RU/<br>01: STC<br>10: IDL<br>11: IDL | N mode<br>DP mode<br>E1 mode | Invert<br>each time<br>EXX inst-<br>ruction is<br>executed | 1:drive<br>pins even<br>in STOP<br>mode |

010491

#### 3.1.3 Wait Control

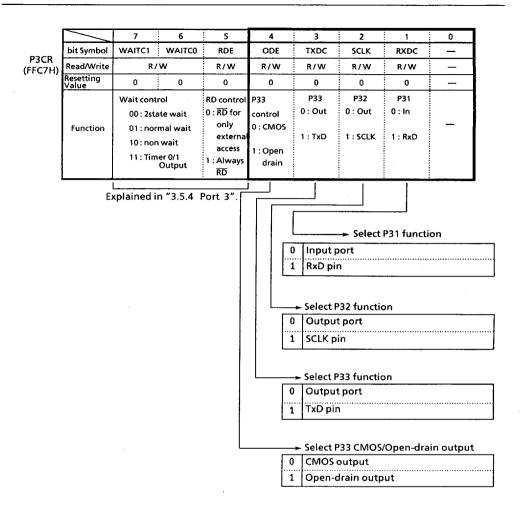

For TMP90C802A, a wait control register (WAITC) is allocated to the  $6 \mathrm{th}$  and  $7 \mathrm{th}$  bits of memory address FFC7H.

|                |                    | 7                               | 6                              | 5   | 4                                           | 3                         | 2                          | 1                        | 0 |

|----------------|--------------------|---------------------------------|--------------------------------|-----|---------------------------------------------|---------------------------|----------------------------|--------------------------|---|

| P3CR<br>FFC7H) | bit Symbol         | WAITC1                          | WAITC0                         | RDE | ODE                                         | TXDC                      | SCLK                       | RXDC                     | - |

|                | Read/Write         | R/W                             |                                | R/W | R/W                                         | R/W                       | R/W                        | R/W                      | _ |

|                | Resetting<br>Value | 0                               | 0                              | 0   | 0                                           | 0                         | 0                          | 0                        | _ |

|                | Function           | 01 : noi<br>10 : noi<br>11 :Tim | ate wait<br>mal wait<br>n wait | 1   | P33control<br>0 : CMOS<br>1 : Open<br>drain | P33<br>0 : Out<br>1 : TxD | P32<br>0 : Out<br>1 : SCLK | P31<br>0 : In<br>1 : RxD | - |

240890

MCU90-265

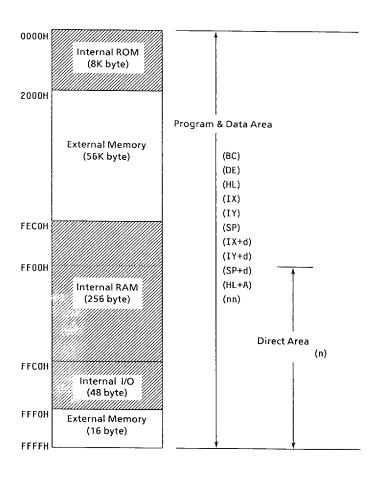

#### 3.2 Memory Map

The TMP90C802A supports a program or data memory of up to 64K bytes.

The program/data memory may be assigned to the address space from 0000H to FFFFH.

#### (1) Internal ROM

The TMP90C802A internally contains an 8Kbyte ROM. The address space 0000H~1FFFH is provided to the ROM. The CPU starts executing a program from 0000H by resetting.

The addresses 0010H~007FH in this internal ROM area are used for the entry area for the interrupt processing. The TMP90C803A dose not have a built-in ROM; there fore, the address space 0000H~1FFFH is used as external memory space.

#### (2) Internal RAM

The TMP90C802A also contains a 256byte RAM, which is allocated to the address space FEC0H~FFBFH. The CPU allows the access to whole RAM area (FF00H~FFBFH, 192 bytes) by a short operation code (opcode) in a "direct addressing mode".

The addresses from FF30H~FF7FH in this RAM area can be used as parameter area for micro DMA processing (and for any other purposes when the micro DMA function is not used).

#### (3) Internal I/O

The TMP90C802A provides a 48byte address space as an internal I/O area, whose addresses range from FFC0H~FFEFH. This I/O area can be accessed by the CPU using a short opcode in the "direct addressing mode".

Figure 3.2 is a memory map indicating the areas accessible by the CPU in the respective addressing mode.

#### MCU90-266

■ 9097249 0040722 OT3 ■

Figure 3.2 Memory Map

240889

#### MCU90-267

■ 7097249 0040723 T3T ■

#### 3.3 Interrupt Functions

The TMP90C802A supports a general purpose interrupt processing mode and a micro DMA processing mode that enables automatic data transferred by the CPU for internal and external interrupt requests.

After the reset state is released, all interrupt requests are processed in the general purpose interrupt processing mode. However, they can be processed in the micro DMA processing mode by using a DMA enable register to be described later.

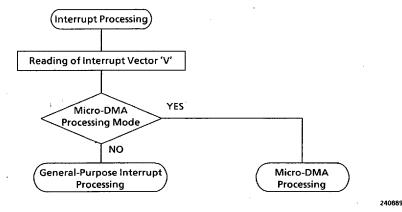

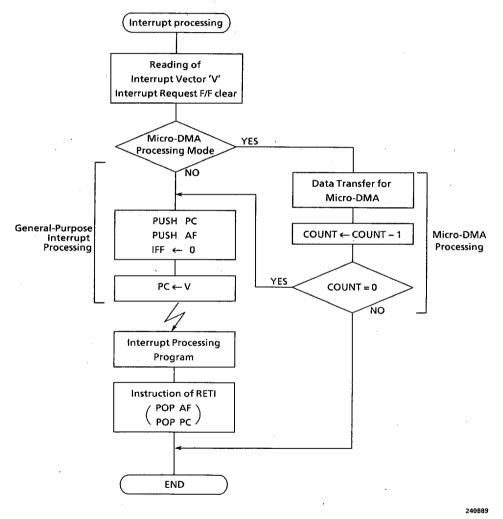

Figure 3.3 (1) is a flowchart of the interrupt response sequence.

Figure 3.3 (1) Interrupt Response Flowchart

When an interrupt is requested, the source of the interrupt transmits the request to the CPU via an internal interrupt controller. The CPU starts the interrupt processing if it is a non-maskable or maskable interrupt requested in the EI state. However, a maskable interrupt requested in the DI state (IFF= $^{\circ}$ 0') is ignored.

Having acknowledged an interrupt, the CPU reads out the interrupt vector from the internal interrupt controller to find out the interrupt source.

Then, the CPU checks if the interrupt requests the general purpose interrupt processing or the micro DMA processing, and proceeds to each processing.

As the reading of an interrupt vectors is performed in the internal operating cycles, the bus cycle results in dummy cycles.

MCU90-268 ■ 9097249 0040724 976 **■**

#### 3.3.1 General Purpose Interrupt Processing

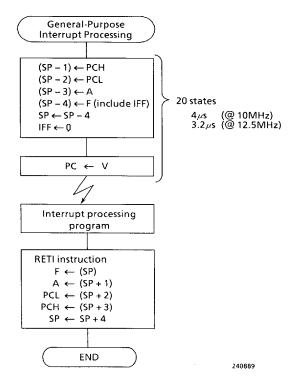

A general purpose interrupt is processed as shown in Figure 3.3 (2).

The CPU stores the contents of the program counter PC and the register pair AF into the stack, and resets the interrupt enable flag IFF to "0" (disable interrupts). Then transfers the value of the interrupt vector "V" to the program counter, and the processing jumps to an interrupt processing program.

The overhead for the entire process from accepting an interrupt to jumping to an interrupt processing program is 20 states.

Figure 3.3 (2) General Purpose Interrupt Processing Flowchart

An interrupt (Maskable and Nonmaskable) processing program ends with a RETI instruction.

When this instruction is executed, the data previously stacked from the program counter PC and the register pair AF are restored.

After the CPU reads out the interrupt vector, the interrupt source acknowledges that the CPU accepts the request, and clears the request.

#### MCU90-269

#### **9**097249 0040725 802 **1**

A non-maskable interrupt cannot be disabled by programming. A maskable interrupt, on the other hand, can be enabled or disabled by programming. An interrupt enable flip flop (IFF) is provided on the bit 5 of Register F in the CPU. The interrupt is enabled or disabled by setting IFF to "1" by the EI instruction or to "0" by the DI instruction, respectively. IFF is reset to "0" by the reset operation or the acceptance of any interrupt (including non-maskable interrupt). The EI instruction is executed after the subsequent instruction is executed.

Table 3.3 (1) lists the possible interrupt sources.

Start Start address of Vector address of Priority Vector general Type Interrupt source value Micro DMA order value purpose ÷8 processing interrupt parameter processing SWI instruction 1 02H 10H 0010H Non NMI (Input from NMI pin) 2 03H 18H 0018H maskable 3 INTWD (watchdog) 04H 20H 0020H 4 INTO (External input 0) 05H 28H 0028H 5 INTTO (Timer 0) 06H 30H 0030H FF30H 6 INTT1 (Timer 1) 07H 38H 0038H FF38H 7 Maskable INTT2 (Timer 2) 08H 40H 0040H 8 INTT3 (Timer 3) 09H 48H 0048H 9 INT1 (External input 1) OBH 58H 0058H 10 INTRX (End of serial receiving) 0EH 70H 0070H FF70H 11 INTTX (End of serial transmission) 0FH 78H 0078H FF78H

Table 3.3 (1) Interrupt Sources

240889

The "priority order" in the table shows the order of the interrupt source to be acknowledged by the CPU when more than interrupt are requested at one time.

If interrupt of fourth and fifth orders are requested simultaneously, for example, an interrupt of the "5th" priority is acknowledged after a "4th" priority interrupt processing has been completed by a RETI instruction. However, a lower priority interrupt can be acknowledged immediately by executing an EI instruction in a program that processes a higher priority interrupt.

The internal interrupt controller merely determines the priority of the sources of interrupts to be acknowledged by the CPU when more than one interrupt are requested at a time. It is, therefore, unable to compare the priority of interrupt being executed with the one being requested.

#### MCU90-270

9097249 0040726 749 📟

## 3.3.2 Micro DMA Processing

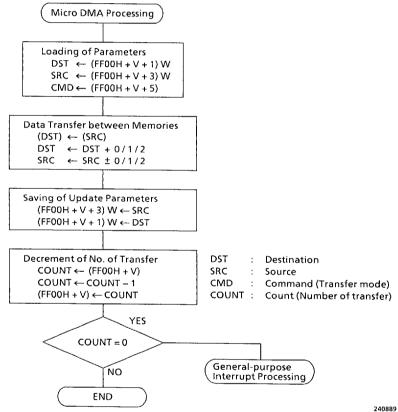

Figure 3.3 (3) is a flowchart of the micro DMA processing. Parameters (addresses of source and destination, and transfer mode) for the data transfer between memories are loaded by the CPU from an address modified by an interrupt vector value. After the data transfer between memories according to these parameter, these parameters are updated and saved into the original locations. The CPU then decrements the number of transfers, and completes the micro DMA processing unless the result is "0".

If the number of transfer becomes "0", the CPU proceeds to the general purpose interrupt handling described in the previous chapter.

Figure 3.3 (3) Micro DMA Processing Flowchart

MCU90-271

**=** 9097249 0040727 685 **=**

The micro DMA processing is performed by using only hardware to process interrupts mostly completed by simple data transfer. The use of hardware allows the micro DMA processing to handle the interrupt in a higher speed than the conventional methods using software. The CPU registers are not affected by the micro DMA processing.

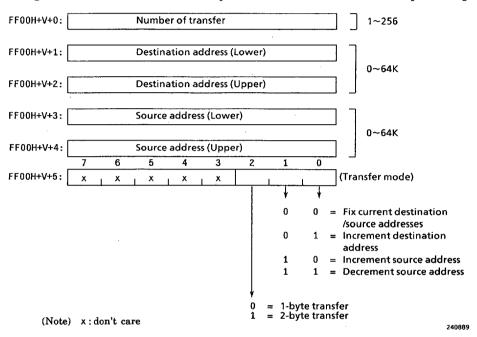

Figure 3.3 (4) shows the functions of parameters used in the micro DMA processing.

Figure 3.3 (4) Parameters for Micro DMA Processing

Parameters for the micro DMA processing are located in the internal RAM area (See Table 3.3 (1) Interrupt Sources). The start address of each parameter is "FF00H + interrupt vector value", from which a six bytes' space is used for the parameter. This space can be used for any other memory purposes if the micro DMA processing is not used.

The parameters normally consist of the number of transfer, addresses of destination and source, and transfer mode. The number of transfer indicates the number of data transfer accepted in the micro DMA processing.

The amount of data transferred by a single micro DMA processing is limited to one or two bytes. Both the destination and source addresses are specified by 2-byte data. The address space available for the micro DMA processing ranges from 0000H to FFFFH.

Bits 0 and 1 of the transfer mode indicate the mode updating the source and/or destination, and the bit 2 indicates the data length (one byte or two bytes).

#### MCU90-272

9097249 0040728 511 📟

Table 3.3 (2) shows the relation between the transfer mode and the result of updating the destination/source addresses.

Table 3.3 (2) Addresses Updated by Micro DMA Processing

| Transfer<br>mode |                   | Function                                         | Destination address | Source<br>address |

|------------------|-------------------|--------------------------------------------------|---------------------|-------------------|

| 000              | 1-byte transfer : | Fix the current source/<br>destination addresses | 0                   | 0                 |

| 001              | 1-byte transfer : | Increment the destination address                | +1                  | 0                 |

| 010              | 1-byte transfer : | Increment the source address                     | 0                   | +1                |

| 011              | 1-byte transfer : | Decrement the source address                     | 0                   | -1                |

| 100              | 2-byte transfer : | Fix the current source/<br>destination addresses | 0                   | 0                 |

| 101              | 2-byte transfer : | Increment the destination address                | +2                  | 0                 |

| 110              | 2-byte transfer : | Increment the source address                     | 0                   | +2                |

| 111              | 2-byte transfer : | Decrement the source address                     | 0                   | -2                |

240889

240889

In the 2-byte transfer mode, data are transferred as follows:

```

(Destination address) ← (Source address)

(Destination address + 1) ← (Source address + 1)

```

Similar data transfers are made in the modes that "decrement the source address", but the updated results are different as shown in the table 3.3 (2).

Figure 3.3 (5) shows an example of the micro DMA processing that handles data receiving of internal serial I/O.

This is an example of executing "an interrupt processing program after serial data receiving" after receiving 7-frame data (Assume 1 frame = 1 byte for this example) and saving them into the memory addresses from FF00H to FF06H.

```

; Initial setting for serial receiving.

CALL SIOINIT

SET 1,(OFFE6H)

; Enable an interrupt for serial data receiving.

SET 1, (OFFE8H)

; Set the micro DMA processing mode for the interrupt.

(OFF70H),7

; Set the number of transfer = 7

LD

LDW (OFF71H),OFF00H

; Set FF00H for the destination address.

LDW

(OFF73H),OFFEBH

; Set FFEBH for the source (serial receiving buffer) address.

LD

(OFF75H),1

; Set the transfer mode (1-byte transfer: Increment destination

address).

ΕI

ORG

0070H

Interrupt processing program

after serial data receiving

RETI

```

Figure 3.3 (5) Example of Micro DMA Processing

MCU90-273

9097249 0040729 458

The bus operation in the general purpose interrupt processing and the micro DMA processing is included in "Table 1.4 (2) Bus Operation for Executing Instructions" in the previous section."

The micro DMA processing time (when the number of transfer is not decremented to 0) is 46 states (9.2 $\mu$ s at 10MHz oscillation frequency) without regard to the 1-byte/2-byte transfer mode.

Figure 3.3 (6) shows the interrupt processing flowchart.

Figure 3.3 (6) Interrupt Processing Flowchart

MCU90-274

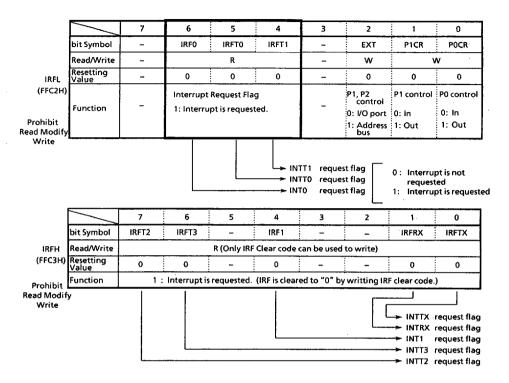

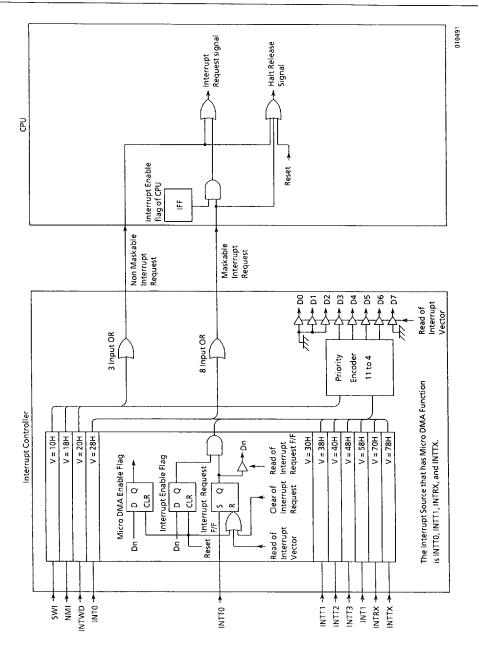

#### 3.3.3 Interrupt Controller

Figure 3.3 (8) outlines the interrupt circuit. The left side of this figure represents an interrupt controller, and the right side comprises the CPU's interrupt request signal circuit and HALT release signal circuit.

The interrupt controller has Interrupt Request Flip-flops, interrupt enable flags, and micro DMA enable flags (4 channels) for each interrupt channel (11 channels). The Interrupt Request Flip-flops serve to latch interrupt requests from peripherals. Each flip-flop is reset to "0" when a reset or interrupt is acknowledged by the CPU and the vector of the interrupt channel is read into the CPU, or when the CPU executes an instruction that clears a request to interrupt that channel (write "vector divided by 8" into the memory address FFC3H). For example, by executing.

LD (0FFC3H), 38H/8,

The Interrupt Request Flip-flops for the interrupt channel "INTT1" whose vector is 38H is reset to "0".

The status of an Interrupt Request Flip-flops is found out by reading the memory address FFC2H or FFC3H. "0" denotes there is no interrupt request, and "1" denotes that an interrupt is requested. Figure 3.3 (7) illustrates the bit configuration indicating the status of Interrupt Request Flip-flops.

MCU90-275

**■** 9097249 0040731 006 **■**

(Caution) Writing "vector divided by 8" into the memory address FFC3H clears the Flip-Flop for the specified interrupt request.

Figure 3.3 (7) Configration of Interrupt Request Flip-flops

MCU90-276

**9**097249 0040732 T42

Figure 3.3 (8) Block Diagram of Interrupt Controller

#### MCU90-277

## **9097249 0040733 989**

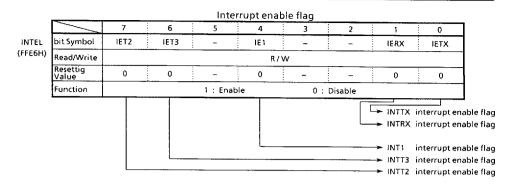

The interrupt enable flags provided for all interrupt request channels are assigned to the memory address FFE6H or FFE7H. Setting any of these flags to "1" enables an interrupt of the respective channel. These flags are initialized to "0" by resetting.

#### Clear the interrupt enable flag in the DI status.

The micro DMA enable flag also provided for each interrupt request channel is assigned to the memory address FFE7H or FFE8H. The interrupt processing for each channel is placed in the micro DMA processing mode by setting this flag to "1". This flag is initialized to "0" (general purpose interrupt processing mode) by resetting.

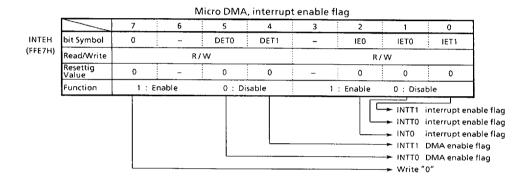

Figure 3.3 (9) shows the bit configuration of the interrupt enable flags and micro DMA enable flags.

The external interrupt functions are shown below.

| Interrupt | Common<br>terminal | Mode        |              | setting           |

|-----------|--------------------|-------------|--------------|-------------------|

| NMI       | _                  | _           | Falling edge |                   |

| INTO      | P80                | <b>□</b> *□ | Level        | P8CR < EDGE > = 0 |

| 11470     | INTO PRO           |             | Rising edge  | P8CR < EDGE > = 1 |

| INT1      | P81                |             | Rising edge  | ·                 |

FOR the pulse width for the external interrupts, see selection 4.7 "Interrupt Operation".

Attention should be paid to the following two modes having special circuits:

| INTO Level mode | IF INTO is not an edge-based interrupt, the function of Interrupt Request Flip-flop is canceled. Therefore the interrupt request signal must be held until the interrupt request is acknowledged by the CPU. A change in the mode (edge to level) automatically clears the interrupt request flag. When the CPU has been put in the interrupt response sequence by changing INTO from "0" to "1", it is necessary to leave INTO at "1" until the second bus cycle of the interrupt response sequence is completed. Also, "1" must always be held until HALT is cleared when using the INTO level mode to clear HALT. (Use care to prevent noise changing "1" back to "0".) When switching from the level mode to the edge mode, the interrupt request flag set in the level mode is not cleared; therefore, use the following sequence to clear the interrupt request flag.  DI  LD (OFFD1H), 01H: switch from level to edge LD (OFFC3H), 05H: clear interrupt request flag. El |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRX           | The Interrupt Request Flip-flop is cleared only by resetting or reading the serial channel receiving buffer, and not by an instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

240889

#### MCU90-278

**9** 9097249 0040734 815

|        |                  |   |  |   |  | Micr  | o DN | /IA ena | able flag | S     |      |      |      |

|--------|------------------|---|--|---|--|-------|------|---------|-----------|-------|------|------|------|

|        |                  | 7 |  | 6 |  | 5     | :    | 4       | 3         |       | 2    | 1    | 0    |

|        | it Symbol        | - |  | - |  | -     |      | -       | -         |       | -    | DERX | DETX |

| E8H) R | ead/Write        | - |  |   |  |       |      |         |           |       | R/W  |      |      |

| R<br>V | esettig<br>'alue | _ |  |   |  | -     |      | -       | -         |       |      | 0    | 0    |

| F      | unction          |   |  |   |  | 1 : E | nabl | e       | C         | : Dis | able |      |      |

|        |                  |   |  |   |  |       |      |         |           |       |      |      |      |

INTTX DMA enable flag

Figure 3.3 (9) Interrupt/Micro DMA Enable Flags

MCU90-279

🖿 9097249 0040735 751 🖿

## 3.4 Standby Function

When a HALT instruction is executed, the TMP90C802 selects one of the following modes as determined by the halt mode set register:

- (1)RUN: Suspends only the CPU operation. The power consumption remains unchanged.

- (2)IDLE1: Suspends all internal circuits except the internal oscillator. In this mode, the power consumption is less than 1/10 of that in the normal operation.

- (3)IDLE2: Operate only the internal oscillator and specific internal I/O devices. The power consumption is less than 1/3 of that in the normal operation.

- (4)STOP: Suspends all internal circuits including the internal oscillator. In this mode, the power consumption is considerably reduced.

The HALT mode set register WDMOD <HALTM1, 0> is assigned to the bits 2 and 3 of the memory address FFD2H in the internal I/O register area (other bits are used to control other functions). The register is reset to "00" (RUN mode) by resetting.

These HALT state can be released by resetting or requesting an interrupt. The methods for releasing the HALT status are shown in Table 3.4 (2).

Either a non-maskable or maskable interrupt with EI (enable interrupt) condition is acknowledged and interrupt processing is processed. A maskable interrupt with DI (disable interrupt) condition is also acknowledged and CPU starts executing an instruction that follows the HALT instruction, but the interrupt request flag is held at "1".

But if interrupt request occur before MPU practices "HALT" command in the state of DI and it latches interrupt request flag, it causes to release HALT state and to state will be released as soon after MPU practices "HALT" command. (MPU doesn't HALT state.)

Therefore clear interrupt request flag or disable interrupt enable flag before MPU practices "HALT" command.

ex) MPU becomes "STOP" mode in the state of DI and release it by INT0 interupt. But "built-in I/O" used only "Timer 0".

$\begin{array}{lll} DI & & ; \\ SET & 2, (INTEH) & ; INT0 \ interrupt \ enable \\ RES & 1, (INTEH) & ; INTT0 \ interrupt \ disable \\ \end{array}$

LD (WDMOD), 04H ; STOP mode

HALT

After release "HALT", Practice Program

When the halt status is released by a reset, the status in effect before entering the halt status (including built-in RAM) is held. The RAM contents may not be held, however, if the HALT instruction is executed within the built-in RAM.

#### MCU90-280

## **■ 9097249 0040736 698 ■**

|                 |       | 7                 | 6                 | 5                                                                                                       | 4                                                                        | 3                                                          | 2                                    | 1                                                          | 0                                         |

|-----------------|-------|-------------------|-------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------|------------------------------------------------------------|-------------------------------------------|

| OD bit Syr      | nbol  | WDTE              | WDTP1             | WDTP0                                                                                                   | WARM                                                                     | HALTM1                                                     | HALTM0                               | EXF                                                        | DRIVE                                     |

| !H) Read∧       | Write | R/W               | R,                | R/W                                                                                                     |                                                                          | R/W                                                        |                                      | R                                                          | R/W                                       |

| Resett<br>Value | ing   | 1                 | 0                 | 0                                                                                                       | 0                                                                        | 0                                                          | 0                                    | Undefined                                                  | 0                                         |

| Functi          | ion   | 1 : WDT<br>Enable | 00:<br>01:<br>10: | ecting time<br>2 <sup>14</sup> /fc<br>2 <sup>16</sup> /fc<br>2 <sup>18</sup> /fc<br>2 <sup>20</sup> /fc | Warming<br>up time<br>0: 2 <sup>14</sup> / fc<br>1: 2 <sup>16</sup> / fc | Standby m<br>00: RUN<br>01: STOP<br>10: IDLE1<br>11: IDLE2 | mode<br>mode<br>mode<br>mode<br>mode | Invert<br>each time<br>EXX inst-<br>ruction is<br>executed | 1:<br>to drive<br>pin in<br>STOP<br>mode. |

|                 | L     | Explair           | ned in "3.8       | Watchdog T                                                                                              | imer"                                                                    |                                                            | Exchang<br>Explaine                  |                                                            | plained in<br>4.4.4 STOP<br>Registers"    |

Figure 3.4 (1) HALT Mode Set Register

#### 3.4.1 RUN Mode

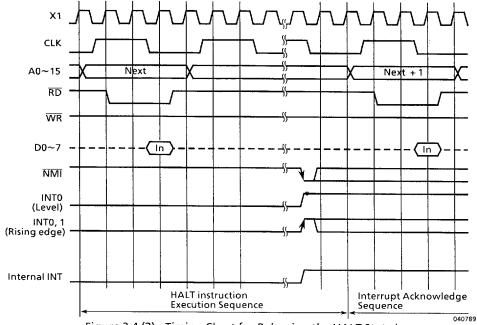

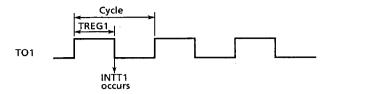

Figure 3.4 (2) shows the timing for releasing the HALT state by interrupts in the RUN/IDLE 2 mode.

In the RUN mode, the system clock in the MCU continues to operate even after a HALT instruction is executed. Only the CPU stops executing the instruction. Until the HALT state is released, the CPU repeats dummy cycles. In the HALT state, an interrupt request is sampled with the rising edge of the "CLK" signal.

Figure 3.4 (2) Timing Chart for Releasing the HALT State by Interrupts in RUN/IDLE 2 Modes

MCU90-281

**--** 9097249 0040737 524 **--**

#### 3.4.2 IDLE 1 Mode

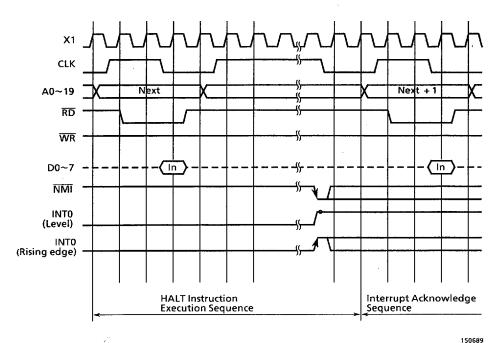

Figure 3.4 (3) illustrates the timing for releasing the HALT state by interrupts in the IDLE 1 mode.

In the IDLE 1 mode, only the internal oscillator and the watchdog timer operate. The system clock in the MCU stops, and the CLK signal is fixed at the "1" level.

In the HALT state, an interrupt request is sampled asynchronously with the system clock, however the HALT release (restart of operation) is performed synchronously with it.

Note: An interrupt requested by the watchdog timer is prohibited through the HALT period in this mode.

Figure 3.4 (3) Timing Chart of HALT Released by Interrupts in IDLE1 Mode

MCU90-282

**-** 9097249 0040738 460 **-**

#### 3.4.3 IDLE 2 Mode

Figure 3.4 (2) shows the timing of HALT release caused by interrupts in the RUN/IDLE 2 mode.

In the IDLE 2 mode, the HALT state is released by an interrupt with the same timing as in the RUN mode, except the internal operation of the MCU. In the RUN mode, only the CPU stops executing the current instruction, and the system clock is supplied to all internal devices. In the IDLE 2 mode, however, the system clock is supplied to only specific internal I/O devices. As a result, the HALT state in the IDLE 2 mode requires only a 1/3 of the power consumed in the RUN mode. In the IDLE 2 mode, the system clock is supplied to the following I/O devices:

- 8-bit timer

- Serial interface

- Watchdog timer

MCU90-283

📰 9097249 0040739 3T7 🖿

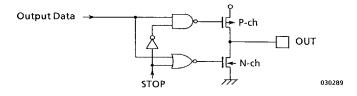

#### 3.4.4 STOP Mode

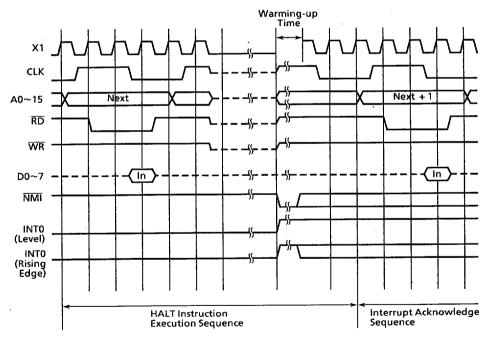

Figure 3.4 (4) is a timing chart for releasing the HALT state by interrupts in the STOP mode.

The STOP mode is selected to stop all internal circuits including the internal oscillator. In this mode, all pins except special ones are put in the high-impedance state, independent of the internal operation of the MCU. Table 3.4 (1) summarizes the state of these pins in the STOP mode. Note, however, that the pre-halt state (The status prior to execution of HALT instruction) of all output pins can be retained by setting the internal I/O register WDMOD <DRIVE> (Drive enable: Bit 0 of memory address FFD2H) to "1". The content of this register is initialized to "0" by resetting.

When the CPU accepts an interrupt request, the internal oscillator is restarted immediately. However, to get the stabilized oscillation, the system clock starts its output after the time set by the warming up counter WDMOD <WARM> (Warming up: Bit 4 of memory address FFD2H). A warming-up time of either the clock oscillation time  $\times$  2<sup>14</sup> or  $\times$  2<sup>16</sup> can be set by setting this bit to either "0" or "1". This bit is initialized to "0" by resetting.

Figure 3.4 (4) Timing Chart of HALT Released by Interrupt in STOP Mode

200689

MCU90-284

9097249 0040740 019 🖿

The internal oscillator can be also restarted by the input of the  $\overline{\text{RESET}}$  signal at "0" to the CPU. In the Reset restart mode, however, the warming-up counter remains inactive in order to get the quick response of MCU when the power is turned on (Power on Reset). As a result, the normal clock operation may not be performed due to the unstable clock supplied immediately after restarting the internal oscillator. To avoid this, it is necessary to keep the  $\overline{\text{RESET}}$  signal at "0" long enough to release the HALT state in the STOP mode.

|                                 | IN/OUT                                              | DRVE = 0 | DRVE = 1       |

|---------------------------------|-----------------------------------------------------|----------|----------------|

| Р0                              | Input mode<br>Output mode                           | OUT      | ——<br>ОUТ      |

| P1                              | Input mode<br>Output mode                           |          | IN<br>OUT      |

| P2                              | Input mode<br>Output mode                           | _        | IN<br>OUT      |

| Р3                              | Input pin<br>Output pin                             |          | IN<br>OUT      |

| P80 (INT0)<br>P81 (INT1)        | Input pin<br>Input pin                              | IN       | IN.<br>IN*     |

| NMI<br>CLK<br>RESET<br>X1<br>X2 | Input pin Output pin Input pin Input pin Output pin | IN       | IN "1" IN: "1" |

Table 3.4 (1) State of Pins in STOP Mode

240889

---: Indicates that input mode/input pin cannot be used for input and that the output mode/output pin have been set to high impedance.

IN: The input enable status.

IN: The input gate is operating. Fix the input voltage at either "0" or "1" to prevent the pin floating.

OUT: The output status.

It is necessary to leave INTO at "1" until the second bus cycle of the interrupt response sequence is completed, when the STOP mode is released by the level mode of INTO.

MCU90-285

■ 9097249 0040741 T55 ■

<sup>\*:</sup> Intermediate bias is still applied to this pin in the zero cross detect mode.

Table 3.4 (2) I/O Operation During Halt and How to Release the Halt Command

|           | Hal                  | t mode                | RUN                           | IDLE2         | IDLE1   | STOP                 |   |   |      |   |   |   |

|-----------|----------------------|-----------------------|-------------------------------|---------------|---------|----------------------|---|---|------|---|---|---|

| W         | MOD .                | <haltm1,0></haltm1,0> | 00                            | 11            | 10 .    | 01                   |   |   |      |   |   |   |

|           | СРИ                  |                       | Halt                          |               |         |                      |   |   |      |   |   |   |

| block     | I/O po               | ort                   | Keeps the state was executed. | when the half | command | See<br>Table 3.4 (1) |   |   |      |   |   |   |

| d g       | 8 bit 1              | timer                 |                               |               |         |                      |   |   |      |   |   |   |

| Operating | Serial<br>interf     |                       | Opera                         | ation         | н       | alt                  |   |   |      |   |   |   |

| å         | Watchdog timer       |                       |                               |               |         |                      |   |   |      |   |   |   |

|           | Interrupt controller |                       |                               |               |         |                      |   |   |      |   |   |   |

|           |                      | NMI                   | 0                             | 0             | 0       | 0                    |   |   |      |   |   |   |

|           | ţ                    |                       |                               |               | INTWD   | 0                    | 0 | _ | _    |   |   |   |

| o C       |                      |                       |                               |               |         |                      |   |   | INTO | 0 | 0 | 0 |

| source    |                      |                       |                               | INTTO         | 0       | 0                    | _ |   |      |   |   |   |

| 1         | g.                   | INTT1                 | 0                             | 0             | _       | _                    |   |   |      |   |   |   |

| asi       | Interrupt            | INTT2                 | 0                             | 0             | _       | _                    |   |   |      |   |   |   |

| releasing | <u> </u>             | INTT3                 | 0                             | 0             | _       |                      |   |   |      |   |   |   |

| Halt      |                      | INT1                  | 0                             | 0             | _       | -                    |   |   |      |   |   |   |

| E E       |                      | INTRX                 | 0                             | 0             | _       |                      |   |   |      |   |   |   |

|           |                      | INTTX                 | 0                             | 0             | -       | _                    |   |   |      |   |   |   |

|           | Rese                 | t                     | 0                             | 0             | 0       | 0                    |   |   |      |   |   |   |

$\bigcirc$ : Can be used to release the halt commnad.

-: Cannot be used to release the halt command.

010491

## MCU90-286

**9097249 0040742 991**

#### 3.5 Function of Ports

The TMP90C802A contains total 32 pins (TMP90C803A: 6pins) input/output ports. These ports function not only for the general-purpose I/O but also for the input/output of the internal CPU and I/O. Table 3.5 describes the functions of these ports.

| Port<br>name | Pin name | No. of pins | Direction | Direction set<br>unit | Resetting value | Pin name for internal function |

|--------------|----------|-------------|-----------|-----------------------|-----------------|--------------------------------|

| Port 0       | P00~P07  | 8           | 1/0       | Byte                  | Input           | D0~D7                          |

| Port 1       | P10~P17  | 8           | 1/0       | Byte                  | Input           | A0~A7                          |

| Port 2       | P20~P27  | 8           | 1/0       | Bit                   | Input           | A8~A15                         |

| Port 3       | P31      | 1           | Input     | _                     | Input           | RxD                            |

|              | P32      | 1           | Output    | _                     | Output          | SCLK                           |

|              | P33      | 1           | Output    | _                     | Output          | TxD                            |

|              | P35      | 1           | Output    | _                     | Output          | RD                             |

|              | P36      | 1           | Output    | _                     | Output          | WR                             |

|              | P37      | 1           | Input     | -                     | Input           | WAIT/TO1                       |

| Port 8       | P80      | 1           | Input     | _                     | Input           | INT0                           |

|              | P81      | 1           | Input     | _                     | Input           | INT1/TI2                       |

Table 3.5 Functions of Ports

230890

These port pins function as the general-purpose input/output ports by resetting. The port pins, for which input or output is programmably selectable, function as input ports by resetting. A separate program is required to use them for an internal function.

The TMP90C803A functions in the same way as the TMP90C802A except:

- Port 0 always functions as data bus (D0 to D7)

- Port 1 always functions as address bus (A0 to A7)

- Port 2 always functions as address bus (A8to A15)

- P35 and P36 of always function as RD and WR pins, respectively

MCU90-287

9097249 0040743 828 🖿

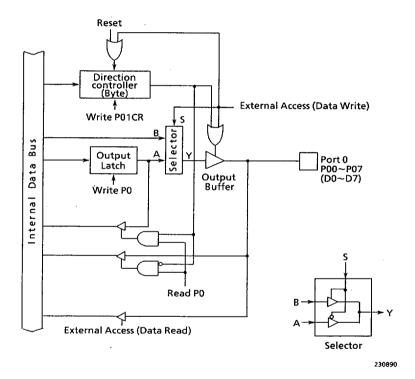

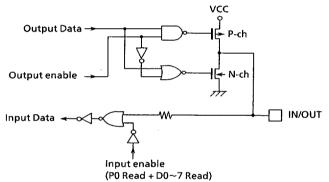

#### 3.5.1 Port 0 (P00~P07)

Port 0 is an 8-bit general-purpose I/O port P0 whose I/O function is specified by the control register P01CR < P0C > in byte. By resetting all bits of the control register are initialized to "0", whereby Port 0 turns to the input mode, and the contents of the output latch register are undefined.

In addition to the general-purpose I/O port function, it functions as a data hus (D0~D7). Access of an external memory makes it automatically function as a data bus and <P0C> are cleared to "0".

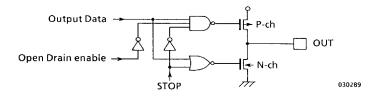

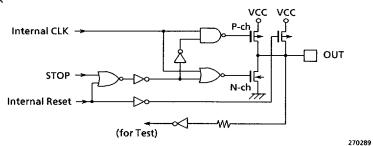

Figure 3.5 (1) Port 0

MCU90-288 ■ 9097249 0040744 764 **■**

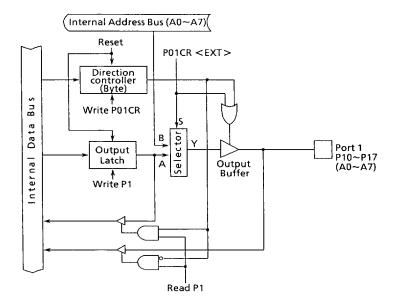

#### 3.5.2 Port 1 (P10~P17)

Port 1 is an 8-bit general-purpose I/O port P1 whose I/O function is specified by the control register P01CR <P1C> in byte. All bits of the output latch and the control register are initialized to "0" by resetting, whereby Port 1 is put in the input mode.

In addition to the general-purpose I/O port function, it functions as an address bus (A0 $\sim$ A7). The address bus function can be selected by setting only the external extension control register P01CR <EXT> to "1" regardless of the status of the above control register <P1C>. The <EXT> register is reset to "0" whereby Port 1 and Port 2 turn to the general-purpose I/O mode.

190990

Figure 3.5 (2) Port 1

#### MCU90-289

■ 9097249 0040745 6TO **■**

|                    | 7            | 6                         | 5             | 4,            | 3            | 2                 | 1                           | 0             |  |

|--------------------|--------------|---------------------------|---------------|---------------|--------------|-------------------|-----------------------------|---------------|--|

| bit Symbol         | P07          | P06                       | P05           | P04           | P03          | P02               | P01                         | P00           |  |

| Read/Write         | R/W          |                           |               |               |              |                   |                             |               |  |

| Resetting<br>Value | Input Mode   |                           |               |               |              |                   |                             |               |  |

|                    |              |                           |               |               |              |                   |                             |               |  |

|                    |              |                           |               | Port 1 Regi   |              |                   |                             |               |  |

|                    | 7            | . 6                       | 5             | 4             | 3 3          | 2                 | 1                           | 0             |  |

| bit Symbol         | P17          | P16                       | P15           | P14           | P13          | P12               | P11                         | P10           |  |

| Read/Write         |              | R/W                       |               |               |              |                   |                             |               |  |

| Resetting<br>Value |              |                           |               |               | Mode         |                   |                             |               |  |

| varue              |              |                           |               |               |              |                   |                             |               |  |

|                    |              |                           |               |               |              |                   |                             |               |  |

|                    | 7            | 6                         | - Poi         | rt 0,1 Contro | Register 3   | 2                 |                             | . 0           |  |

| bit Symbol         |              | IRFO                      | IRFTO         | IRFT1         | _            | EXT               | 1<br>P1C                    | POC           |  |

| Read/Write         | _            |                           | R             | : "           |              | w                 |                             | w FOC         |  |

| Resetting<br>Value |              | 0                         | 0             | 0             |              | 0                 | 0                           |               |  |

| Value              | <del>-</del> | <del></del>               | :             | •             | <u> </u>     | <del>-</del>      | <del></del>                 | 0             |  |

| Function           |              |                           | : Request Fla | -             |              | P1, P2<br>control | P1 control                  | P0 control    |  |

| Function           | -            | 1: Interrupt is requested |               |               | -            | 0: I/O port       | 0: In                       | 0: In         |  |

| 1                  |              |                           |               |               |              | 1: Address<br>bus | 1: Out                      | 1: Out        |  |

|                    |              | <u> </u>                  |               |               |              | Dus               |                             |               |  |

| odify              |              | Evolained                 | in "3 3 3 In  | nterrupt cont | ;<br>rollor" | 1 =               |                             |               |  |

|                    |              | cxpramed                  | 3.3.3 11      | iterrupt com  | JOHEI        | ر<br>ا            | et I/O of Po                | ort 0         |  |

|                    |              |                           |               |               |              | ПГ                | 0 Input                     |               |  |

|                    |              |                           |               |               |              |                   | 1 Outpu                     | t             |  |

|                    |              |                           |               |               |              |                   | <u> </u>                    |               |  |

|                    |              |                           |               |               |              | L_s               | et I/O of Po                | ort 1         |  |

|                    |              |                           |               |               |              |                   | Input                       |               |  |

|                    |              |                           |               |               |              |                   | Outpu                       | t             |  |

|                    |              |                           |               |               |              | -                 | —- <del></del>              |               |  |

|                    |              |                           |               |               |              |                   | t general-p<br>s of Ports 1 | ourpose port/ |  |

|                    |              |                           |               |               |              | υu                | つい ていじらし                    |               |  |

|                    |              |                           |               |               |              | Г                 |                             |               |  |

|                    |              |                           |               |               |              |                   | Genera                      | l-purpose po  |  |

Figure 3.5 (3) Registers for Port 0 and 1

MCU90-290

**9**097249 0040746 537 **5**

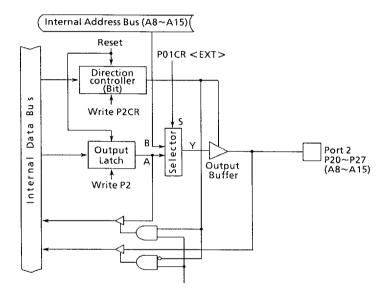

#### 3.5.3 Port 2 (P20~P27)

Port 2 is an 8-bit general-purpose I/O port P2 whose I/O functions are specified by the control register P2CR for each bit. All bits of the output latch and the control register are initialized to "0" by resetting, where by Port 2 turns to the input mode.

In addition to the general-purpose I/O port function, it functions as an address bus (A8 $\sim$ A15). The address bus function can be selected by setting the register P01CR <EXT> (shared with port 1) to "1" and setting the Port 2 control register P2CR to the output mode. When the Port 2 control register P2CR is set to "0", Port 2 functions as an input port, regardless of the status of the <EXT> register.

190990

Figure 3.5 (4) Port 2

MCU90-291

**9**097249 0040747 473 **9**

|                  |                    |            |      | F       | Port 2 Regist                                                                            | ter                  |              |       |           |  |

|------------------|--------------------|------------|------|---------|------------------------------------------------------------------------------------------|----------------------|--------------|-------|-----------|--|

|                  |                    | 7          | 6    | 5       | 4                                                                                        | 3                    | 2            | 1     | . 0       |  |

|                  | bit Symbol         | P27        | P26  | P25     | P24                                                                                      | P23                  | P22          | P21   | P20       |  |

| H)               | Read/Write         | R/W        |      |         |                                                                                          |                      |              |       |           |  |

| İ                | Resetting<br>Value | Input Mode |      |         |                                                                                          |                      |              |       |           |  |

|                  |                    |            |      | Port    | 2 Control Re                                                                             | egister              |              |       |           |  |

|                  |                    | 7          | 6    | 5       | 4                                                                                        | 3                    | 2            | 1     | 0         |  |

|                  | bit Symbol         | P27C       | P26C | P25C    | P24C                                                                                     | P23C                 | P22C         | P21C  | P200      |  |

| ' <sup>1</sup> [ | Read/Write         | W          |      |         |                                                                                          |                      |              |       |           |  |

|                  | Resetting<br>Value | 0          | 0    | 0       | 0                                                                                        | 0                    | 0            | 0     | 0         |  |

| . [              | Function           |            |      | 0: In 1 | : Out (                                                                                  | I/O selected         | bit by bit)  |       |           |  |

| odi              | fy L               |            |      |         | → Set I/O                                                                                |                      | d Address Bu | s     |           |  |

|                  |                    |            |      |         | P2CR<br><p2xc< td=""><td>PO1CR<br/><ext></ext></td><td>0</td><td></td><td>1</td></p2xc<> | PO1CR<br><ext></ext> | 0            |       | 1         |  |

|                  |                    |            |      |         |                                                                                          | 0                    | Input Por    | t ir  | put Port  |  |

|                  |                    |            |      |         |                                                                                          | 1                    | Output Po    | rt Ad | idress Bu |  |

Note: Settings can be in units of bits. Here, P2CR < P2XC > is the Xth bit of P2CR.

010491

Figure 3.5 (5) Registers for Port 2

# MCU90-292 ■ 9097249 0040748 30T ■

190990

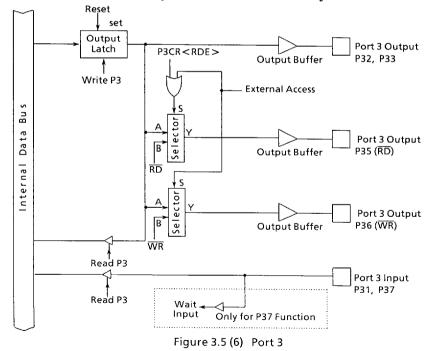

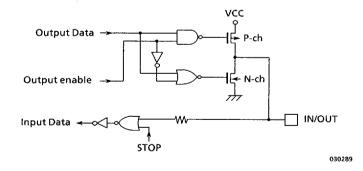

#### 3.5.4 Port 3 (P31~P33, P35~P37)

Port 3 is a 6-bit general-purpose I/O port P3 with fixed I/O function. All bits of the output latch are initialized to "1" by resetting, and "High level" is generated to the output port.

In addition to the I/O port function, P31~P33 have the I/O function for the internal serial interface, while P35~P37 have the external memory control function. The additional functions can be selected by the control register P3CR. All bits of the control register are initialized to "0" by resetting, and the port turns to the general-purpose I/O Ports mode.

However, P37 is placed in the input mode after resetting, and turns to the TO1 output port mode after writing P3CR < WAITC1, 0 > = 1, 1.

Further, access of an external memory makes P35 and P36 automatically function as the memory control pins ( $\overline{RD}$  and  $\overline{WR}$ ), and access of an internal memory makes them function as general-purpose I/O ports.

When an external memory is accessed, therefore, the output latch registers P35  $(\overline{RD})$  and P36  $(\overline{WR})$  should be kept at "1" which is the initial value after the reset.

The P3CR <RDE > of the control register is intended for a pseudostatic RAM. When set to "1", it always functions as an  $\overline{RD}$  pin. Therefore the  $\overline{RD}$  pin outputs "0" (Enable) when it is an internal memory read and internal I/O read cycle.

MCU90-293

9097249 0040749 246

|       |                    | 7         | . 6      | 5          | 4                | 3                                                                      | 2                                                                                                  | 1                             | 0        |

|-------|--------------------|-----------|----------|------------|------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------|----------|

| Р3    | bit Symbol         | P37       | P36      | P35        | -                | P33                                                                    | P32                                                                                                | P31                           | -        |

| FC6H) | Read/Write         | R         | R/W      | ,R/W       | -                | R/W                                                                    | R/W                                                                                                | R                             | -        |

|       | Resetting<br>Value | Input     | 1        | 1          | -                | 1                                                                      | 1                                                                                                  | Input                         | -        |

|       |                    |           |          | Port       | 3 Control R      | egister                                                                |                                                                                                    |                               |          |

|       |                    | 7         | 6        | 5          | 4                | 3                                                                      | 2                                                                                                  | 1                             | 0        |

| P3CR  | bit Symbol         | WAITC1    | WAITC0   | RDE        | ODE              | TXDC1                                                                  | TXDC0                                                                                              | RXDC1                         | - :      |

| FC7H) | Read/Write         | R/        | w        | R/W        | R/W              | R/W                                                                    | R/W                                                                                                | R/W                           | -        |

|       | Resetting<br>Value | 0         | 0        | 0          | 0                | 0                                                                      | 0                                                                                                  | 0                             |          |

|       |                    | Wait cont | rol      | RD control | P33control       | P33                                                                    | P32                                                                                                | P31                           |          |

|       |                    | 00: 2sta  | ate wait | 0: RD for  | 0: CMOS          | 00: Out                                                                | 0: Out                                                                                             | 0: In                         |          |

|       | Function           | 01: nor   | mal wait | only       | Output           | 01: Out                                                                |                                                                                                    |                               |          |

|       |                    | 10: nor   | wait     | access     | 1: Open<br>Drain | 10: TxD                                                                | 1: SCLK                                                                                            | 1: RxD                        |          |

|       |                    | 11: Tim   | ner 0/1  | 1: Always  | Output           | 11: TxD                                                                |                                                                                                    |                               |          |

|       | 1 1                | _         |          |            |                  |                                                                        |                                                                                                    |                               |          |

|       |                    | L         | tput .   | RD<br>I    |                  | <u> </u>                                                               | Explained in                                                                                       | "3 8 Serial                   | Channel" |

|       |                    | 00        | tput     | I I        |                  | 5et port  0 CM 1 Ope  Set port  0 Ger 1 Fixe                           | P33 to open OS output en drain out P35 to fixed neral-purpos ed as RD Pin                          | RD mode                       |          |

|       |                    |           | tput     | I I        |                  | Set port  O CM  1 Ope  Set port  O Ger  1 Fixe  WAIT co                | P33 to open OS output en drain out P35 to fixed neral-purpos ed as RD Pin                          | drain outpu<br>put<br>RD mode |          |

|       |                    |           | tput     | I I        |                  | > Set port  0 CM 1 Ope  1 Ope  Set port  0 Ger 1 Fixe  WAIT co  00 2st | P33 to open OS output en drain out P35 to fixed neral-purpos ed as RD Pin                          | drain outpu<br>put<br>RD mode |          |

|       |                    |           | tput     | I I        |                  | > Set port                                                             | P33 to open OS output en drain out P35 to fixed neral-purpos ed as RD Pin ntrol ate wait           | drain outpu                   |          |

|       |                    |           | tput     | , RD       |                  | > Set port  0 CM 1 Ope  Set port  0 Ger 1 Fixe  WAIT co  00 Zst 01 No. | P33 to open OS output en drain out P35 to fixed neral-purpos ed as RD Pin ntrol ate wait rmal wait | put  RD mode e I/O port       |          |

Figure 3.5 (7) Register for Ports 3

## MCU90-294

9097249 0040750 T68

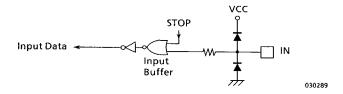

### 3.5.5 Port 8 (P80~P81)

Port 8 is a 2-bit general-purpose INPUT port P8.

Port 8 also has the functions of interrupt request input, and clock input for a timer/event counter.

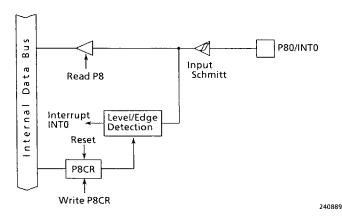

## (1) P80/INTO

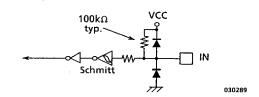

P80 is a general-purpose input port, also used as the external interrupt request input pin INTO. INTO allows the selection of either an "H" level interrupt or rising edge interrupt by using the control register P8CR < EDGE >.

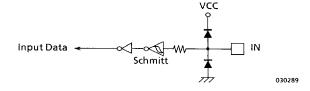

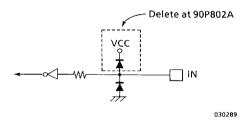

Figure 3.5 (8) Port P80/INT0

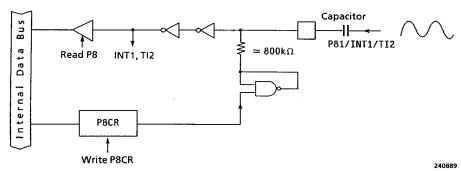

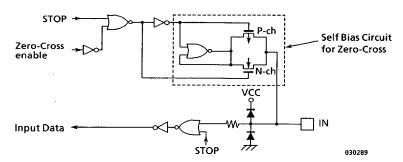

### (2) P81/INT1/TI2

P81 is a general-purpose input port, also used as the external interrupt request input pin INT1 and the clock input pin T12 for the timer/event counter.

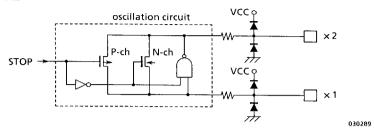

This port incorporates a zero-cross detection circuit, and enables zero-cross detection by connecting an external capacitor. The zero-cross detection can be disabled/enabled by using the control register P8CR <ZCE1>. This control register is reset to "0", making the zero-cross detection disabled by resetting.

MCU90-295

9097249 0040751 914

Figure 3.5 (9) Port P81/INT1/TI2

|        |                    |   |   | F | ort 8 Regis | ter |   |       |      |

|--------|--------------------|---|---|---|-------------|-----|---|-------|------|

|        |                    | 7 | 6 | 5 | 4           | 3   | 2 | 1     | 0    |

|        | bit Symbol         | - | - | - | -           | -   | - | P81   | P80  |

| FFD0H) | Read/Write         |   |   |   |             |     |   | R     | R    |

|        | Resetting<br>Value |   |   |   |             | :   |   | Input | Mode |

|                    |   |   | Por | t 8 Control F | Register |           |                                         |                                         |

|--------------------|---|---|-----|---------------|----------|-----------|-----------------------------------------|-----------------------------------------|

|                    | 7 | 6 | 5   | 4             | 3        | 2         | 1                                       | 0                                       |

| CR bit Symbol      | - | - | -   | -             |          | -         | ZCE1                                    | EDGE                                    |

| (1H) Read/Write    |   |   |     |               |          |           | w                                       | w                                       |

| Resetting<br>Value |   |   |     |               |          |           | 0                                       | 0                                       |

| Function           |   |   |     |               | -        |           | INT1/TI4<br>control<br>1: ZCD<br>enable | INT0<br>control<br>0: level<br>1: ↑edge |

| bit <br>Modify     | • |   |     |               |          | Control   | INTO                                    | -1" level                               |

|                    |   |   |     |               |          | 1 In      | terrupt by "I<br>etection               | H" rising ed                            |

|                    |   |   |     |               | L        | → P81/INT | 1/TI2 zero-cr                           | oss enable                              |

|                    |   |   |     |               |          | 0 Di      | sable                                   |                                         |

|                    |   |   |     |               |          | 1 En      | able                                    | ••••••                                  |

Figure 3.5 (10) Registers for Port 8

9097249 0040752 830

### 3.6 Timers

The TMP90C802A incorporates four 8-bit timers.

The four 8-bit timers can be operated independently, and can also be functioned as two 16-bit timer by mode setting: Timer 2 has an event counter function, so that it can also be used as an 8-bit counter. Furthermore, it can be used as a 16-bit counter cascaded with Timer 3.

- 8-bit interval timer mode (4 timers)

- 16-bit interval timer mode (2 timers)

- 8-bit programmable pulse generation (PPG) output mode (Timer 0 and Timer 1)

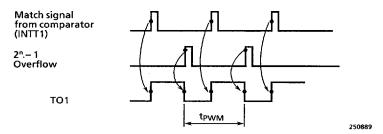

- 8-bit PWM output mode (Timer 1) Possible arrangements: 8-bit × 2 and 16-bit × 1

- 8-bit event counter mode (Timer 2)

- 16-bit event counter mode (Timer 2 and Timer 3)

- Software counter latch function (Timer 2 and Timer 3)

### 3.6.1 8-bit Timers

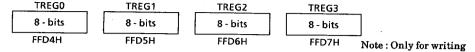

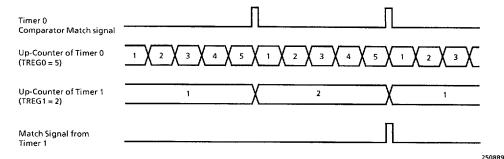

The TMP90C802A incorporates four 8-bit interval timers (Timers 0, 1, 2 and 3), each of which can be operated independently. The cascade connection of Timer 0 and 1, or Timer 2 and 3 allows these timers used as 16-bit internal timers.

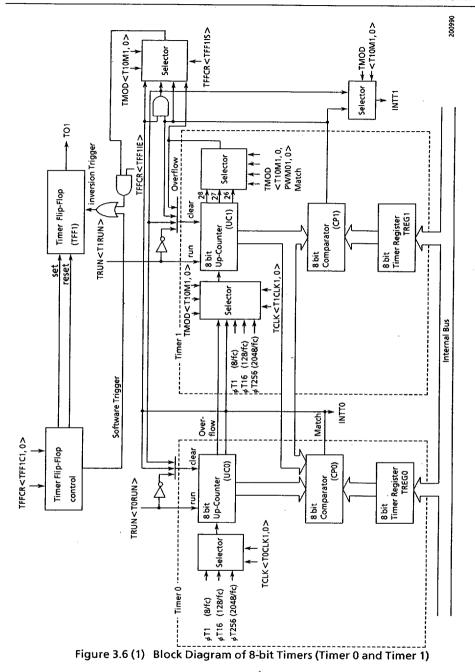

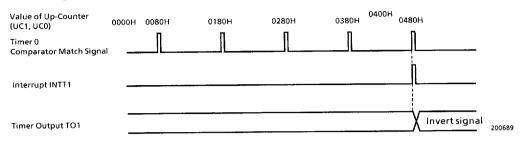

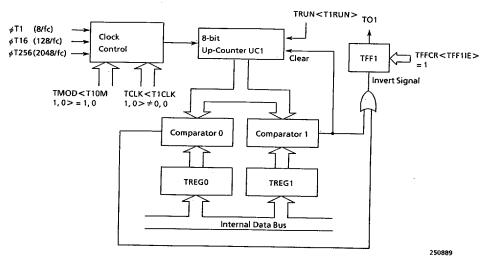

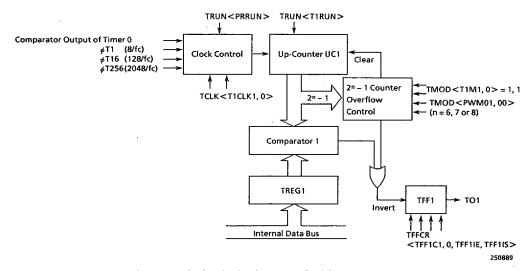

Figure 3.6 (1) is a block diagram of the 8-bit timers (Timer 0 and Timer 1).

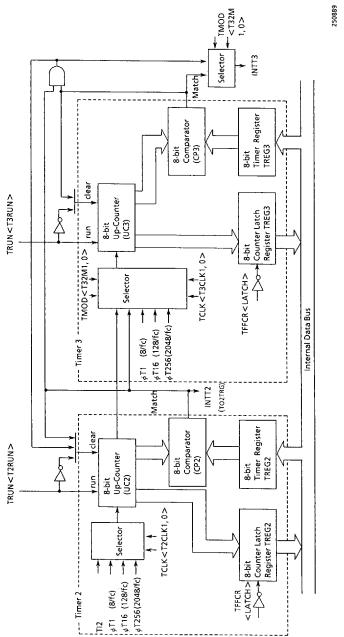

Figure 3.6 (2) is a block diagram of the 8-bit timer/event counters (Timer 2 and Timer 3).

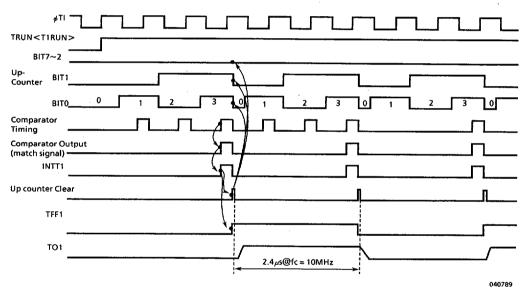

Each interval timer is composed of an 8-bit up-counter, an 8-bit comparator and an 8-bit timer register, with a Timer Flip-flop (TFF1) provided to pair of Timer 0/1.

Internal clocks ( $\phi$ T1,  $\phi$ T16 and  $\phi$ T256), some of the input clock sources for the interval timers, are generated by the 9-bit prescaler shown in Figure 3.6 (3).

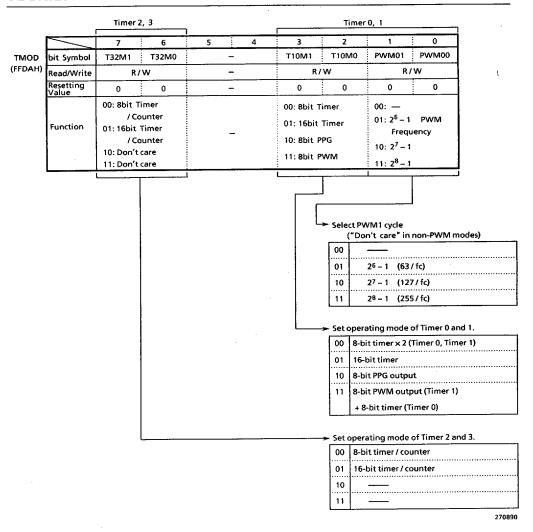

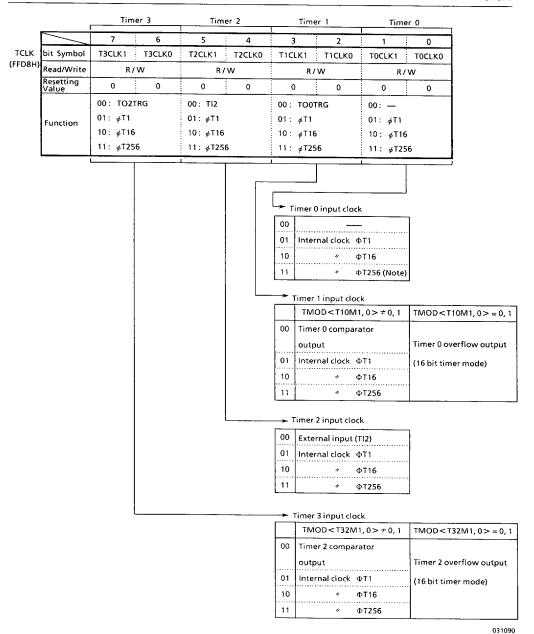

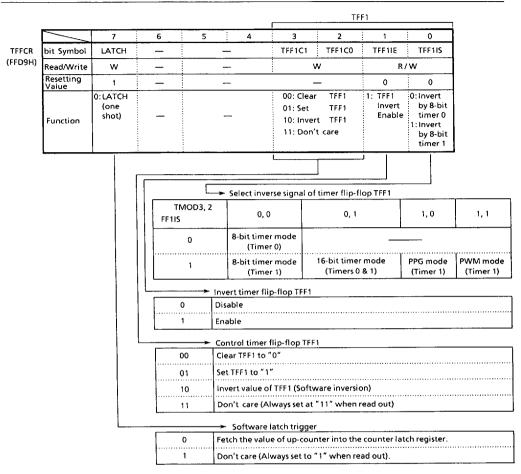

Their operating modes of the 8-bit timers and flip-flops are controlled by four control registers (TCLK, TFFCR, TMOD and TRUN).

MCU90-297

9097249 0040753 777

# 9097249 0040754 603 🖿

Figure 3.6 (2) Block Diagram of 8-bit Timer/Counter (Timer 2 and Timer 3)

# ■ 9097249 0040755 54T ■

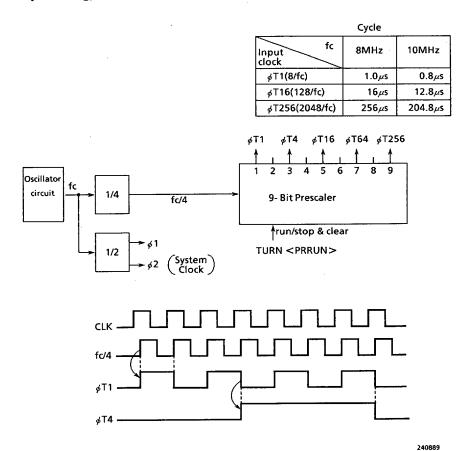

### 1 Prescaler

An 9-bit prescaler is provided to further devide the clock frequency already divided to a 1/4 of the frequency of the source clock (fc).

It generates an input clock pulse for the 8-bit timers, the baud-rate generator, etc. For the 8-bit timers, three types of clock are generated ( $\phi$ T1,  $\phi$ T16 and  $\phi$ T256).

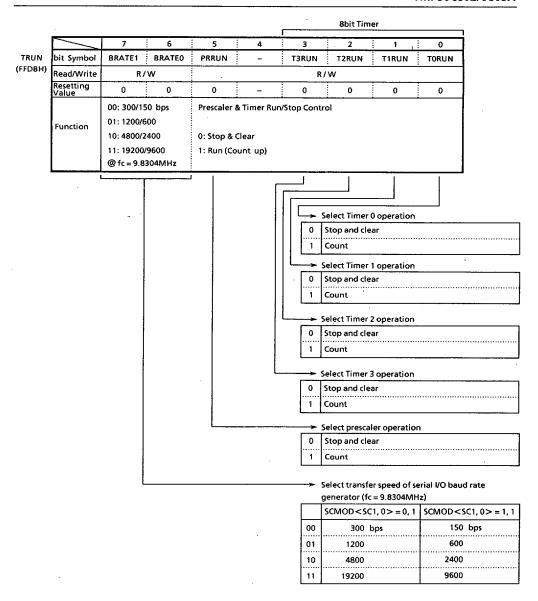

The prescaler can be run or stopped by using the 5th bit TRUN < PRRUN > of the timer control register TRUN. Setting < TRUN > to "1" makes the prescaler count, and setting it to "0" clears the prescaler to stop.

By resetting, <PRRUN> is initialized to "0", making the prescaler clear and stop.

Figure 3.6 (3) Prescaler

MCU90-300

9097249 0040756 486

## 2 Up-counter

This is an 8-bit binary counter that counts up by an input clock pulse specified by an 8-bit timer clock control register TCLK and an 8-bit timer mode register (TMOD).

The input clock pulse for Timer 0 and 2 is selected from  $\phi T1$ ,  $\phi T16$  and  $\phi T256$  according to the setting of the TCLK register. When using Timer 2 as the counter, set bit 4 and bit 5 of TCLK to "0".

Example: When setting TCLK < T0CLK1,  $0 > = 0, 1, \, _{\phi}T1$  is selected as the input clock pulse for Timer 0.

The input clock pulse to Timer 1 and 3 is selected according to the operating mode. In the 16-bit timer/counter mode, the overflow output of Timer 0 and 2 is automatically selected as the input clock pulse, regardless of the setting of the TCLK register.

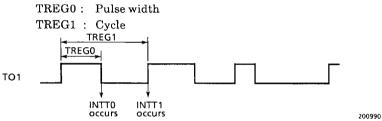

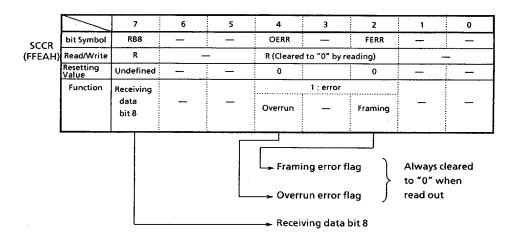

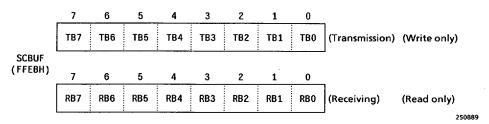

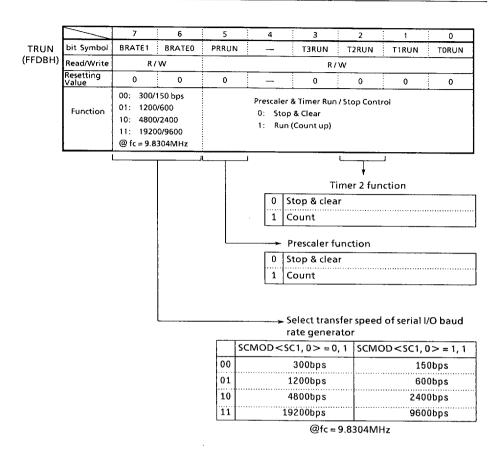

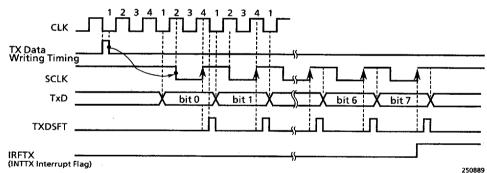

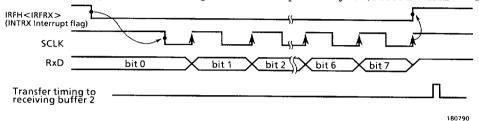

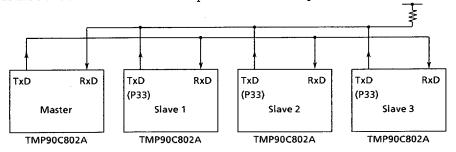

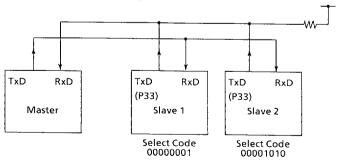

In the other operating modes, the clock pulse is selected among the internal clocks  $\phi$ T1,  $\phi$ T16 and  $\phi$ T256, and the output of the Timer 0 and 2 comparator (match signal).