# CMOS SINGLE 8-BIT PaletteDAC™ FOR TRUE COLOR APPLICATIONS

PRELIMINARY IDT75C457

#### **FEATURES**

- · 165/135/125/110/80 MHz operating speeds

- · Pin- and function-compatible with Brooktree Bt 457

- · Fixed pipeline delay: No external circuitry required

- · 50ns read access time

- Integral and differential linearity < 1/2 LSB</li>

- Single 8-bit DAC

- 256 x 8 Dual-Ported Color Palette RAM

- 4 x 8 Dual-Ported Overlay Palette RAM

- · Multiplexed TTL pixel and overlay inputs

- RS-343A compatible output

- Single 5 volt power supply

- 84-pin PGA and PLCC packages

- Typical power dissipation: 1000mW

- CEMOS™ Monolithic construction

- Military product is compliant with MIL-STD-883, Class B

## DESCRIPTION

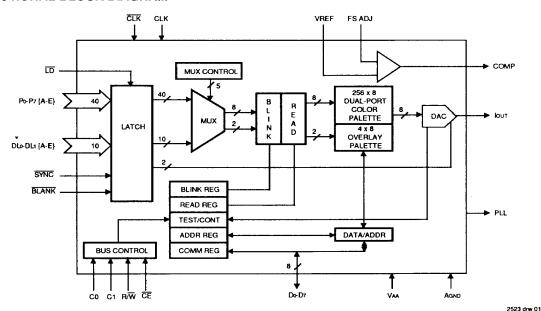

The IDT75C457 is a single channel 8-bit video DAC with on-chip, dual-ported color palette memory. This chip is specifically designed for the display of true-color, high resolution graphics. The architecture eliminates the ECL pixel interface by providing multiple TTL-compatible pixel ports and by multiplexing the pixel data on-chip.

Features included on-chip are programmable blink rates, bit plane masking and blinking, as well as color overlay capability. The IDT75C457 generates an RS-343A compatible video output that is capable of driving a doubly terminated 75 ohm coaxial cable directly. A PLL current output enables synchronization of three IDT75C457s, thus allowing display of true-color images.

The IDT75C457 military PaletteDACs are manufactured in compliance with the latest revision of MIL-STD-883, Class B, making them ideally suited to military temperature applications demanding the highest levels of performance and reliability.

## **FUNCTIONAL BLOCK DIAGRAM**

CEMOS and PaletteDAC are trademarks of Integrated Device Technology, Inc.

**MILITARY AND COMMERCIAL TEMPERATURE RANGES**

**JANUARY 1990**

@ 1990 Integrated Device Technology, Inc.

5.14 - 1

USC-5009/-

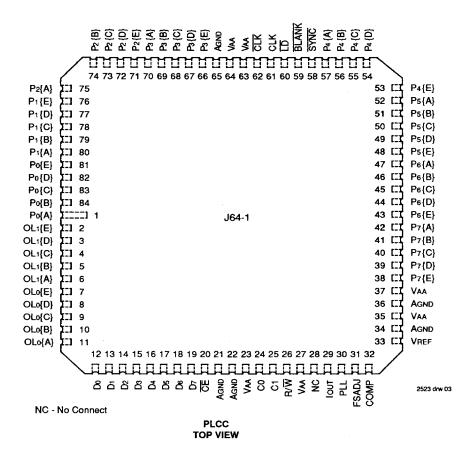

# **PIN CONFIGURATIONS**

|    | _ A                 | В              | С                   | D                   | E                   | F                   | G                  | Н                  | J                  | K                  | L                  | М                  |

|----|---------------------|----------------|---------------------|---------------------|---------------------|---------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| 12 | СОМЕ                | AGNE           | VAA                 | P <sub>7</sub> (D)  | P7(B)               | P <sub>6</sub> {E}  | P <sub>6</sub> {C} | P <sub>6</sub> {B} | P5{E}              | P5{C}              | P5(B)              | P <sub>4</sub> {E} |

| 11 | PLL                 | AGNO           | VAA                 | P <sub>7</sub> {E}  | P <sub>7</sub> {C}  | P <sub>7</sub> {A}  | P <sub>6</sub> (D) | P6(A)              | P <sub>5</sub> {D} | P <sub>5</sub> {A} | P4{C}              | P <sub>4</sub> {A} |

| 10 | ЮП                  | FSAD.          | VREF                |                     |                     | P4{D}               | P4{B}              | SYNC               |                    |                    |                    |                    |

| 9  | · VAA               | NC             |                     |                     |                     |                     | BLANK              | Īΰ                 |                    |                    |                    |                    |

| 8  | C1                  | R/W            |                     |                     |                     |                     | CLK                | CLK                |                    |                    |                    |                    |

| 7  | VAA                 | co             |                     |                     |                     |                     |                    | VAA                | VAA                |                    |                    |                    |

| 6  | AGND                | AGND           |                     |                     |                     | G                   | 84-2               |                    |                    |                    | P3{E}              | AGND               |

| 5  | ĈĒ                  | D <sub>7</sub> |                     |                     |                     |                     |                    |                    |                    |                    | P3{C}              | P3{D}              |

| 4  | D <sub>6</sub>      | D <sub>5</sub> |                     |                     |                     |                     |                    |                    |                    |                    | P <sub>3</sub> {A} | P <sub>3</sub> (B) |

| 3  | D <sub>4</sub>      | D <sub>2</sub> | D <sub>0</sub>      | ΔAL                 | JGNME               | NT MAF              | RK                 |                    |                    | P <sub>2</sub> {A} | P <sub>2</sub> {C} | P <sub>2</sub> (E) |

| 2  | D3                  | ы              | OL <sub>0</sub> (B) | OL <sub>0</sub> (E) | OL <sub>1</sub> {B} | OL <sub>1</sub> {E} | P <sub>0</sub> (B) | P <sub>0</sub> {D} | P <sub>1</sub> {A} | P <sub>1</sub> {D} | P <sub>1</sub> {E} | P <sub>2</sub> {D} |

| 1  | OL <sub>0</sub> (A) | OL0(C)         | Or <sup>0</sup> (D) | OL <sub>1</sub> {A} | OL <sub>1</sub> (C) | OL <sub>1</sub> {D} | P <sub>0</sub> {A} | P <sub>0</sub> (C) | P <sub>0</sub> (E) | P <sub>1</sub> {B} | P <sub>1</sub> {C} | P <sub>2</sub> (B) |

PGA TOP VIEW

2523 drw 02

## **GENERAL INFORMATION**

The IDT75C457 triple 8-bit PaletteDAC is a highly integrated building block which interfaces a relatively low bandwidth frame buffer memory to analog RS-343A high bandwidth output.

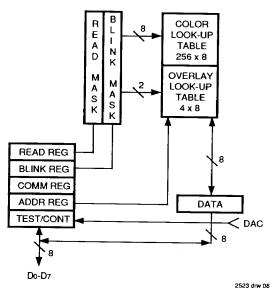

The IDT75C457 includes a look-up table for updating color information and other graphics applications. The basic functional blocks are the microprocessor bus interface, the frame buffer memory interface and multiplexer, a dual-port RAM with one R/W port, one high-speed R/O port and one 8-bit video speed DAC.

# MICROPROCESSOR BUS INTERFACE

The IDT75C457 supports a standard microprocessor bus interface, allowing the MPU direct access to the internal control registers and color/overlay palettes. The dual-port color palette RAM and overlay registers allow color updating without contention with the display refresh process.

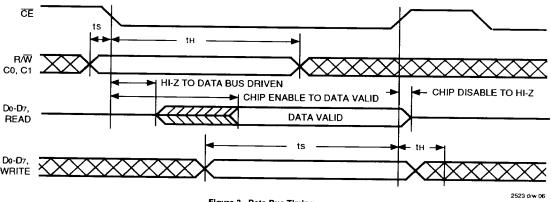

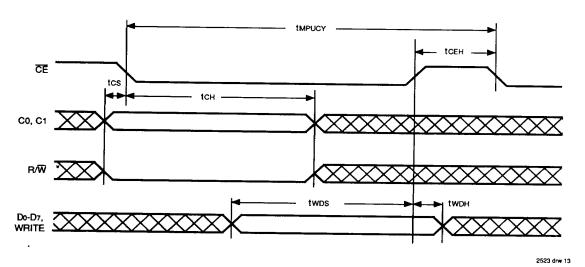

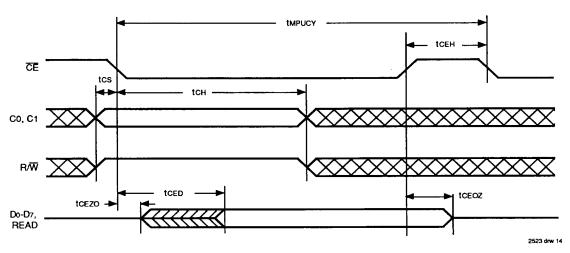

The bus interface consists of eight bidirectional data pins, Do-Dr, with two control inputs, C0 and C1, a read/write direction input, R/ $\overline{W}$ , and a clock input,  $\overline{CE}$ . All data and control information are latched on the falling edge of  $\overline{CE}$ , as shown in Figure 3. All accesses to the chip are controlled by the data in the address register combined with the control inputs C0, C1 and R/ $\overline{W}$ , depicted in the Truth Table (Table 1).

An access to a control register requires writing a 4 through 7 into the address register (C0 = C1 = 0) and then writing or reading data to the selected register (C0 = 0, C1 = 1). When accessing the control registers, the address register is not changed, facilitating read-modify-write operations. If an invalid address is loaded into the address register, data written is ignored or invalid data is read out.

It is also possible to access the color palette information. The palette is organized as 256 address with 8 bits of red, blue or green information. Additionally, there are two extra addresses assigned to overlay information, yielding a total memory size of 260 x 8.

There are two modes of accessing palette entries on the IDT75C457, "Normal", and "RGB".

In Normal mode, writing color data entails the MPU loading the address register with the address of the color palette location or the overlay palette location to be modified. The MPU performs a color write cycle, using C0 and C1 to select either the color palette or the overlay palette. The address register then increments to the next address location which the MPU may modify simply by writing another color. Reading color data is similar to writing, except the MPU executes read cycles.

Normal mode is useful if a 24-bit data bus is available, as 24 bits of color information (eight bits each of red, green, and blue) may be read or written to three IDT75C457s in a single MPU cycle. In this application the  $\overline{CE}$  inputs of all three IDT75C457s are connected together. If only an eight-bit data bus is available, the  $\overline{CE}$  inputs must be individually selected during the appropriate color read or write cycle (red  $\overline{CE}$  during red write cycle, blue during blue write cycle, etc.). When accessing the color palette the address register resets to \$00

after a read or write cycle to location \$FF. When accessing the overlay palette, the address register increments to \$04 following a read or write cycle to overlay color three.

In RGB mode, writing color data entails the MPU loading the address register with the address of the color palette location or overlay palette location to be modified. The MPU performs three successive write cycles (eight bits each of red, green or blue), using C0 or C1 to select either the color palette or the overlay palette. After the blue write cycle, the address register then increments to the next location which the MPU may modify by simply writing another sequence of red, green or blue data. Reading color data is similar to writing except the MPU executes the read cycles.

RGB mode is useful if only an eight-bit data bus is available. Each IDT75C457 is programmed to be red, green or blue PaletteDAC, and will respond only to the assigned read or write cycle. In this application, the IDT75C457s share a common eight-bit data bus. The  $\overline{\text{CE}}$  inputs of all three IDT75C457s must be asserted simultaneously only during color read/write cycles and address register write cycles.

| Address Register<br>Data | C1  | CO | Access              |

|--------------------------|-----|----|---------------------|

| Х                        | 0   | 0  | Address Register    |

| \$00-\$FF                | 0   | 1  | Color Palette       |

| \$00                     | 1   | 1  | Overlay Color 0     |

| \$01                     | 1   | 1  | Overlay Color 1     |

| \$02                     | 1   | 1  | Overlay Color 2     |

| \$03                     | 1   | 1  | Overlay Color 3     |

| \$04                     | 1   | 0  | Read Mask Register  |

| \$05                     | 1 1 | 0  | Blink Mask Register |

| \$06                     | 1   | 0  | Command Register    |

| \$07                     | 1 1 | 0  | Test Register       |

2523 tbi 01

Table 1. Truth Table for MPU Operations

When accessing the color palette, the address register resets to \$00 after a blue read or write cycle to location \$FF. When accessing the overlay palette, the address register increments to location \$04 following a blue read or write cycle to overlay color three. To keep track of the red, green and blue read/write cycles, the address register has two additional bits (ADDRa, ADDRb) that count module three. They are reset to 0 when the MPU reads or writes to the address register. The MPU does not have access to these bits. The other eight bits of the address register (ADDR 0-7) are accessible to the MPU.

## FRAME BUFFER INTERFACE

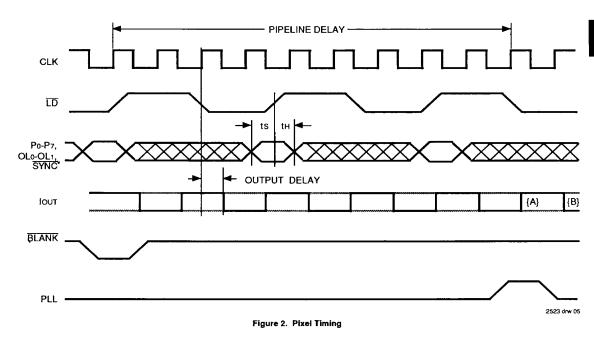

The frame buffer interface consists of five 8-bit input ports which correspond to five consecutive pixels. In addition, there are two extra bits per port which may be used for overlay information. To reduce the bandwidth requirements for the pixel data, the IDT75C457 latches 4 or 5 pixels (the multiplex factor is programmable to 4 or 5 by bit 7 of the command register) on each rising edge of  $\overline{\text{LD}}$ . The color and overlay information is internally multiplexed at the pixel clock frequency,

5.14~4

CLK, and sequentially output. This arrangement allows pixel data to be transferred at a rate 4 or 5 times slower than the pixel clock. Typically,  $\overline{LD}$  is the pixel clock divided by 4 or 5 and is used to clock data out of the frame buffer memory.

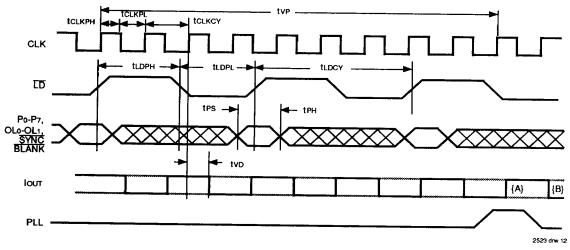

As shown in Figure 2, sync, blank, color and overlay information are latched on the rising edge of  $\overline{LD}$ . Up to 40 bits of color information are input through Po-P7 {A-E} and up to 10 bits of overlay information are input through OLo-OL1 {A-E}. Both sync and blank have separate inputs,  $\overline{SYNC}$  and  $\overline{BLANK}$ , respectively. The IDT75C457 outputs color information on each clock cycle. Four or five pixels are output sequentially, beginning with the {A} information, then the {B} information, until the cycle is completed with the {D} or {E} information. In this configuration, sync and blank are limited to multiples of four or five clock cycles.

The multiplexing factor, 4:1 or 5:1, is programmable from the command register, bit 7. In the 4:1 mode, the  $\{E\}$  color and overlay inputs are not used and the  $\overline{LD}$  clock should be CLOCK divided by 4. The  $\{E\}$  color and overlay inputs must be connected to a valid logic level.

The overlay inputs (OLo-OL1) have the same timing as the pixel inputs (Po-P7). It is possible to use additional bit planes or external logic to control the overlay selection for cursor generation.

5.14~5

#### INTERNAL MULTIPLEXING

$\overline{LD}$  is typically CLK divided by four or five and it latches color and overlay information on every rising edge, independent of CLK. A digital PLL allows  $\overline{LD}$  to be phase independent of CLK. The only restriction is that only one rising edge of  $\overline{LD}$  is allowed to occur per four (4:1 multiplexing) or five (5:1 multiplexing) CLK cycles.

#### **Color Palette**

On the rising edge of each CLK cycle, eight bits of color information (Po-P7) and two bits of overlay information (OLo-OL1) for each pixel are processed by the read mask, blink mask and command registers. This information provides the address to the dual-port color palette RAM. Note that Po is the LSB when addressing the color palette RAM. The value stored at a selected address determines the displayed color. Through the use of the control register, individual bit planes may be enabled or disabled for display and/or blinked at one of four blink rates and duty cycles.

The blink timing is based on vertical retrace intervals which are defined by at least 256  $\overline{\text{LD}}$  cycles since the last falling edge of  $\overline{\text{BLANK}}$ . The color changes during this normally blanked time.

The processed pixel data is then used to select which color palette entry or overlay register is used to provide color information. Table 2 illustrates the truth table used for color selection.

| CR6 <sup>(1)</sup> | OL <sub>1</sub> | OLo | P7-P0 | Palette Entry            |

|--------------------|-----------------|-----|-------|--------------------------|

| 1                  | 0               | 0   | \$00  | Color Palette Entry \$00 |

| 1                  | 0               | 0   | \$01  | Color Palette Entry \$01 |

|                    |                 |     | l     |                          |

|                    |                 |     |       | ,                        |

|                    |                 |     | i     |                          |

| 1                  | 0               | 0   | \$FF  | Color Palette Entry \$FF |

| 0                  | 0               | 0   | \$xx  | Overlay Color 0          |

| x                  | 0               | 1   | \$xx  | Overlay Color 1          |

| ×                  | 1               | 0   | \$xx  | Overlay Color 2          |

| X                  | 1               | 1   | \$xx  | Overlay Color 3          |

#### NOTE:

1. CRs is bit 6 of the Command Register.

Table 2. Palette and Overlay Select

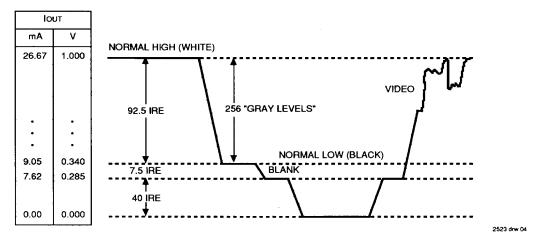

#### Video Generation, DACs

On every CLK cycle, the selected 8 bits of color information from the Color Palette RAM are presented to the 8-bit D/A converters. The IDT75C457 uses a 5 x 3 segmented approach where the five MSBs of the input data are decoded into a parallel "Thermometer" code which produces thirty two "coarse" output levels. The remaining three LSBs of input data drive three binary weighted current switches with a total contribution of one-thirty second of full scale. The MSB and LSB currents are summed at the output to produce 256 levels.

The SYNC and BLANK inputs are pipelined to maintain synchronization with the pixel data. Both inputs drive appropriately weighted current switches which are summed at the output of the DACs to produce the specific output levels required by RS-343, as shown in Figure 3. Table 3 details the output levels associated with SYNC, BLANK and data.

#### Monitor Interface

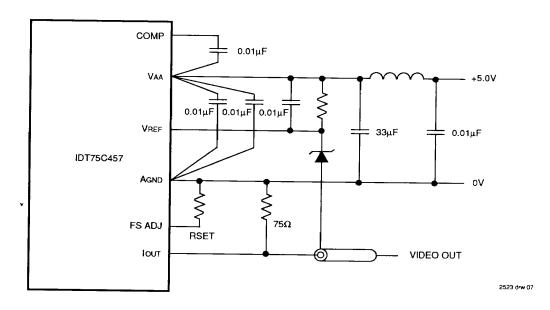

The analog outputs of the IDT75C457 are high-impedance current sources which are capable of directly driving a doubly terminated 75 $\Omega$  coaxial cable to standard video levels. A typical output circuit is shown in Figure 4.

| Description    | S | В   | DAC Data | lout (mA)   |

|----------------|---|-----|----------|-------------|

| WHITE          | 1 | 1   | \$FF     | 26.67       |

| DATA           | 1 | 1 1 | Data     | Data + 9.05 |

| DATA and SYNC  | 0 | 1   | Data     | Data + 1.44 |

| BLACK          | 1 | 1   | \$0      | 9.05        |

| BLACK and SYNC | 0 | 1   | \$0      | 1.44        |

| BLANK          | 1 | 0   | X        | 7.62        |

| SYNC           | 0 | 0   | X        | l n         |

## NOTE:

2523 tbl 02

1. Typical values with full scale lout = 26.67mA, Rset = 523 $\Omega_{\rm c}$  VREF = 1.235V, S is SYNC, B is BLANK.

Table 3. Video Output Truth Table

5.14-6

2523 tbl 03

Figure 1. Composite Video Output Waveform

5.14-7

Figure 3. Data Bus Timing

Figure 4. Typical Application

## **PIN DESCRIPTIONS**

| Pin Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Bus            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Do-D7               | 8-bit, bidirectional data bus. Data is input and output over this bus and the flow is controlled by R/W and CE. D7 is the most significant bit.                                                                                                                                                                                                                                                                                                                                            |

| CE                  | Chip Enable Input. The chip is enabled when this control pin is LOW. During a write cycle (RW LOW), the data present on Do-D7 is internally latched on the LOW-to-HIGH transition of this pin.                                                                                                                                                                                                                                                                                             |

| R/₩                 | Read/Write Control input. The Read/Write input is latched on the HIGH-to-LOW transition of $\overline{CE}$ and determines the direction of the bidirectional data bus, Do-D7. If $\overline{R/W}$ is HIGH during the falling edge of $\overline{CE}$ , a read cycle occurs. If $\overline{R/W}$ is LOW during the falling edge of $\overline{CE}$ , a write cycle occurs and, additionally, Do-D7 are latched on the rising edge of $\overline{CE}$ .                                      |

| C0, C1              | Register Control inputs. C0 and C1 determine which register or palette entry is accessed during a read or write cycle. These inputs are latched on the HIGH-to-LOW transition of CE.                                                                                                                                                                                                                                                                                                       |

| Pixel               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CLK, CLK            | Pixel Clock Inputs. These inputs are differential and may be driven by ECL operating from a +5V supply. The clock frequency is normally the system pixel clock rate.                                                                                                                                                                                                                                                                                                                       |

| LD                  | Load Clock input. The Load Clock is normally CLK divided by 4 or 5 (determined by the Control Register bit 7). The pixel data, Po-P7 {A-E} and OLo-OL1 {A-E}, BLANK and SYNC are internally latched on the LOW-to-HIGH transition of LD.                                                                                                                                                                                                                                                   |

| Po-P7 <b>{A</b> -E} | Pixel Input Data. These inputs provide the address input to the color palette RAM. The data stored at a particular address is the color output by the DAC. Four or five consecutive pixels, as determined by bit 7 in the Command Register, are internally latched on the LOW-to-HIGH transition of LD. The pixels are output sequentially, first {A} then {B}. After all four or five pixels have been output, the cycle repeats. Unused inputs must be connected to a valid logic level. |

| OLo-OL1{A-E}        | Pixel Overlay Inputs. The Overlay inputs have the same timing as Po-P7 and select between either the color palette or the overlay palette. When the overlay palette is selected, the pixel information Po-P7 {A-E} is ignored. Bit 6 of the command register determines if Overlay = 0 displays overlay color 0 or the color palette entry. See Table 2 for details.                                                                                                                       |

| BLANK               | Composite Blank Input. A LOW on this input forces the analog outputs (IOUT) to the blanking level. The BLANK input is internally latched on the LOW-to-HIGH transition of LD. This input overrides all other pixel information.                                                                                                                                                                                                                                                            |

| SYNC                | Composite Sync Input. A LOW on this input subtracts approximately 7mA from the IOs analog output and overrides no other pixel information. For the correct SYNC level, this input should be LOW only when BLANK is also LOW. The SYNC input is internally latched on the LOW-to-HIGH transition of LD.                                                                                                                                                                                     |

| Analog              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AGND                | Analog Ground Power Supply, 0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Vaa                 | Analog Power Supply, 5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VREF *              | Voltage Reference Input, 1.235V. This input supplies a reference voltage for the DAC circuitry. Care must be taken to correctly decouple this voltage because noise on this pin will couple directly to the DAC outputs.                                                                                                                                                                                                                                                                   |

| FS ADJ              | Full-Scale Adjust Input. The current flowing from this pin to AGND is directly proportional to the full-scale analog output current. Normally, a resistor is connected between this pin and AGND. The voltage on this pin is approximately equal to VREF. The relationship lour (mA) = 11.294 x VREF (V)/RSET (KΩ).                                                                                                                                                                        |

| lout                | DAC current output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| СОМР                | Compensation Input. This pin provides the ability to compensate the internal reference operational amplifier.                                                                                                                                                                                                                                                                                                                                                                              |

| PLL                 | Phase Lock Loop Current Output. This high impedance current source is used to enable multiple IDT75C457s to be synchronized with sub-pixel resolution when used with an external PLL. A logic one on the BLANK input results in no current being output onto this pin, while a logic zero results in the following current being output:                                                                                                                                                   |

|                     | PLL (mA) = 3227 * VREF (V)/RSET (ohm).                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| •                   | If sub-pixel synchronization of multiple devices is not required, this output should be connected to GND (either directly or through a register up to 150 ohms).                                                                                                                                                                                                                                                                                                                           |

2523 tbl 04

Figure 5. IDT75C457 Register Block Diagram

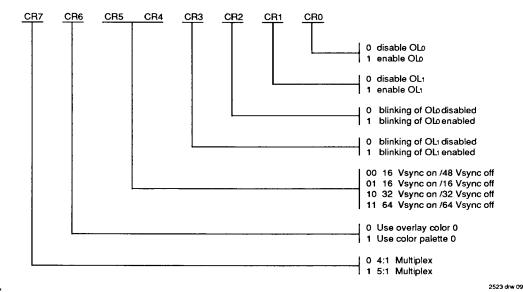

## **Command Register**

CR1

CR<sub>2</sub>

CR3

The Command Register is accessed by reading or writing with the Address Register = \$06, C0 = 0 and C1 = 1 (see Table 1). It internally ANDs the pixel information with a bit from the register before the color palette selection, effectively enabling (HIGH) or disabling (LOW) the entire pixel plane. The Read Mask Register may be read or written at any time. RMR7 (Read Mask Register bit 7) corresponds to D7 (Data Bus bit 7).

CR0 OLo Display Enable. This bit is ANDed internally with the data from OLo prior to the palette selection. If CR0 is LOW, the internal OLo bits are set LOW, allowing only overlay colors 0 and 2 to be selected.

1 to be selected.

OL1 Display Enable. This bit is ANDed internally with the data from OL1 prior to the palette selection. If CR1 is LOW, the internal OL1 bits are set LOW, allowing only overlay colors 0 and

OLo Blink Enable. If this bit is set HIGH, the OLo bit is internally switched between the value input and 0 at the rate specified by the CR4 and CR5 bits. CR0 must be set HIGH for this function.

OL1 Blink Enable. If this bit is set HIGH, the OL1 bit is internally switched between the value input and 0 at the rate specified by the CR4 and CR5 bits. CR1 must be set HIGH for this function.

CR4, CR5

Blink Rate Select. These bits select blink rates based on Vertical Sync cycles, defined as more than 256 \overline{LD} cycles during BLANK.

CR6

Color Palette RAM Enable. This bit specifies whether to use the Color Palette or the Overlay Palette when OLo = OL1 = LOW.

CR7

Multiplex Select. This bit selects between 4:1

(CR7 = 0) or 5:1 (CR7 = 1) multiplexing. When using 4:1 multiplexing the {E} inputs are never used and must be connected to a valid logic level.

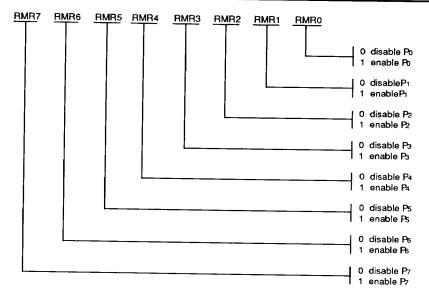

## Read Mask Register

The Read Mask Register is accessed by reading or writing with the Address Register = \$04, C0 = 0 and C1 = 1 (see Table 1). It internally ANDs the pixel information with a bit from the register before the color palette selection, effectively enabling (HIGH) or disabling (LOW) the entire pixel plane. The Read Mask Register may be read or written at any time. RMR7 (Read Mask Register bit 7) corresponds to D7 (Data Bus bit 7).

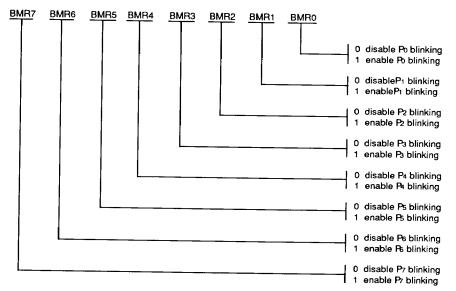

## Blink Mask Register

The Blink Mask Register is accessed by reading or writing with the Address Register = \$05, C0 = 0 and C1 = 1 (see Table 1). Each register bit causes the corresponding pixel bit (Po-P7) to internally switch between the input value and 0 at the blink rate specified in the Command Register. For this function to work, the corresponding enable bit in the Read Mask Register must be set HIGH. The Blink Mask Register may be read or written at any time. BMR7 (Blink Mask Register bit 7) corresponds to D7 (Data Bus bit 7).

#### **Test/Control Register**

The Test/Control Register is accessed by reading or writing with the Address Register = \$07, C0 = 0 and C1 = 1 (see Table 1). This register allows the MPU to read the 8 input bits of the DAC. It may be written to or read by the MPU at any time, and is not initialized. The register bits are defined as follows:

| D7-D4          | DAC input data (one nibble)               |

|----------------|-------------------------------------------|

| Dз             | Upper (LOW) or Lower (HIGH) nibble select |

| D <sub>2</sub> | Blue enable                               |

| D <sub>1</sub> | Green enable                              |

| D <sub>0</sub> | Red enable                                |

2523 tbl 05

When writing to the register, upper four bits (D4-D7) are ignored.

To use the test/control register, the MPU writes to it, specifying the upper or lower nibble of the 8-bit input information to the DAC. When the MPU reads the register, the four bits of color information from the DAC inputs are contained in the upper four bits of the register, and the lower four bits contain whatever was previously written to the register. Note that either the CLOCK must be slowed down to the MPU cycle time, or the same pixel and overlay data must be presented to the device during the entire MPU read cycle.

The red, green and blue enable bits are also used to specify the mode of writing color data to, and reading color data from, the IDT75C457. If all three enable bits are a logic zero, each write cycle to the color palette or the overlay palette loads eight bits of color data. During each read cycle of the color palette or the overlay palette, eight bits of color data are output onto the data bus. If a 24-bit data bus is available, this enables three IDT75C457 to be accessed simultaneously.

If any of the red, green, blue bits are a logic one, the IDT75C457 assumes the MPU is reading or writing color information using red, green, blue cycles, such as are used on the IDT75C458. Setting the appropriate enable bit configures

the IDT75C457 to output or input color data only for the color read/write cycle corresponding to the enabled color. Thus, if the green enable bit is a logic one, and a red, green, blue write cycle occurred, the IDT75C457 would input data only during the green write cycle. If a red, green, blue read cycle occurred, the IDT75C457 would output data only during the green read cycle. Note that CEmust be a logic zero during each of the red, green, blue cycles. One, and only one, of the enable bits must be a logic one. This mode of operation is useful where only an 8-bit data bus is available and the software drivers are written for RGB operation.

Figure 6. Command Register Designations

5.14-{}

Figure 7. Read Mask Register Designations

2523 drw 010

Figure 8. Blink Mask Register Designations

2523 drw 11

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol                                  | Rating                                | Value            | Unit |

|-----------------------------------------|---------------------------------------|------------------|------|

| Power Supplies                          | 1                                     | ·                |      |

| VAA                                     | Measured to AGND                      | -0.5 to +7.0     | ٧    |

| Input Voltage                           | · · · · · · · · · · · · · · · · · · · |                  |      |

| Applied Voltage (2)                     | Measured to AGND                      | -0.5 to VAA +0.5 | ٧    |

| Output                                  |                                       |                  |      |

| Applied Voltage (2)                     | Measured to AGND                      | -0.5 to VAA +0.5 | ٧    |

| Applied Current (2, 3, 4)               | Externally forced                     | -1.0 to +6.0     | mA   |

| Analog Output Short<br>Circuit Duration | Analog output High to AGND            | Indef            | s    |

| Temperature                             |                                       |                  |      |

| Operating                               | Military                              | 55 to +125       | °C   |

| Ambient                                 | Commercial                            | 0 to +70         | °C   |

| Storage                                 | Military                              | -65 to +150      | °C   |

|                                         | Commercial                            | -55 to +125      | °C   |

## NOTES:

- 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect reliability. Absolute Maximum Ratings are limiting values applied individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied.

- 2. Applied voltage must be current limited to specified range.

- 3. Forcing voltage must be limited to specified range

- 4. Current is specified as conventional current when flowing into the device.

# DC ELECTRICAL CHARACTERISTICS

| Symbol              | Parameter                | Test Conditions          | Min.       | Тур. | Max.      | Unit |

|---------------------|--------------------------|--------------------------|------------|------|-----------|------|

| VAA                 | Power Supply             | Measured to AGND         | 4.75       | 5.0  | 5.25      | V    |

| IAA                 | Power Supply Current     | VAA = Typ., Static       |            | 120  | _         | mÁ   |

| VIH (1)             | Input Voltage HIGH       |                          | 2.0        |      | VAA + 0.5 | V    |

| V <sub>IL</sub> (1) | Input Voltage LOW        |                          | AGND - 0.5 | _    | 0.8       | V    |

| Vсін                | Clock Input Voltage HIGH |                          | VAA - 1.0  |      | VAA + 0.5 | v    |

| VCIL                | Clock Input Voltage LOW  |                          | AGND - 0.5 |      | VAA - 0.6 | V    |

| l ін                | Input Current HIGH       | VIN = 2.4V               | _          |      | 1         | μА   |

| l IL                | Input Current LOW        | VIN = 0.4V               | _          | _    | -1        | μА   |

| Vон                 | Output Voltage HIGH      | VAA = Min., IOH = -800μA | 2.4        |      | _         | V    |

| Vol                 | Output Voltage LOW       | VAA = Min., IOL = 6.4mA  |            |      | 0.4       | V    |

| loz                 | Output 3-State Current   |                          | _          |      | 10        | μА   |

1. All digital inputs except CLK and CLK.

2523 tbl 07

# **AC ELECTRICAL CHARACTERISTICS**

Following conditions apply unless otherwise specified: TA = 0°C to +70°C (Commercial Temperature Range)

TA = -55°C to +125°C (Military Temperature Range)

$VAA = 5.0V \pm 5\%$

TTL Inputs, VIL = 0V, VIH = 3V, rise/fall time <5ns

CLK Inputs, VIH = VAA - 1.0V, VIL = VAA - 1.6V, rise/fall time <2ns

Timing reference points at 50% of signal swing

|        |                                            | '75C457-165 <sup>(1)</sup> |      | '75C457-135 <sup>(1)</sup> |      | '75C457-125 |      | 75C457-110 |      | 75C457-80 |             | 1    |  |

|--------|--------------------------------------------|----------------------------|------|----------------------------|------|-------------|------|------------|------|-----------|-------------|------|--|

| Symbol | Parameter                                  | Min.                       | Max. | Min.                       | Max. | Min.        | Max. | Min.       | Max. | Min.      | Max.        | Unit |  |

| FCLK   | Clock Frequency                            | -                          | 165  | _                          | 135  | _           | 125  | -          | 110  | _         | 80          | MHz  |  |

| FCLD   | LD Clock Frequency                         | _                          | 41   | _                          | 34   | -           | 32   |            | 28   |           | 20          | MHz  |  |

| tcs    | Control Set-up Time, C0, C1, R/W           | 0                          |      | 0                          | _    | 0           | _    | 0          |      | 0         |             | ns   |  |

| tcH    | Control Hold Time, C0, C1, R/W             | 15                         | -    | 15                         | _    | 15          |      | 15         |      | 15        |             | ns   |  |

| tCEH   | CE HIGH Time                               | 20                         |      | 20                         |      | 25          |      | 25         | -    | 25        |             | ns   |  |

| tCEL   | CE LOW Time                                | 30                         |      | 30                         | _    | 50          |      | 50         |      | 50        |             | ns   |  |

| tcezo  | CE to Data Bus Driven                      | 10                         | -    | 10                         |      | 10          | _    | 10         |      | 10        | <del></del> | ns   |  |

| tCED   | CE to Data Valid                           |                            | 30   |                            | 30   |             | 50   | _          | 50   |           | 75          | ns   |  |

| tceoz  | CE to Data Bus Hi-Z                        |                            | 15   |                            | 15   | _           | 15   | -          | 15   | _         | 15          | ns   |  |

| twds   | Write Data Set-Up Time                     | 30                         | -    | 30                         | _    | 35          | _    | 35         | _    | 50        |             | ns   |  |

| twoH   | Write Data Hold Time                       | 0                          | _    | 0                          |      | 0           |      | 0          | _    | 0         | _           | ns   |  |

| tclkcy | Clock Cycle Time                           | 6                          | _    | 7.4                        |      | 8           | _    | 9          | _    | 12        |             | ns   |  |

| tclkpl | Clock Pulse Width LOW                      | 2.8                        | -    | 3.0                        | _    | 3.2         | _    | 4          |      | 5         |             | ns   |  |

| tclkph | Clock Pulse Width HIGH                     | 2.8                        | _    | 3.0                        | _    | 3.2         | _    | 4          | _    | 5         |             | ns   |  |

| LDCÝ   | LD Cycle Time                              | 24                         | _    | 29                         | _    | 31          |      | 35         |      | 50        |             | ns   |  |

| LDPH   | LD Pulse Width HIGH                        | 10                         | _    | 12                         | _    | 13          |      | 15         | _    | 20        |             | ns   |  |

| LDPL   | LD Pulse Width LOW                         | 10                         | -    | 12                         | _    | 13          |      | 15         | _    | 20        |             | ns   |  |

| PS .   | Pixel Data Set-up Time                     | 2                          |      | 3                          | _    | 3           |      | 3          |      | 4         |             | ns   |  |

| PH     | Pixel Data Hold Time                       | 1                          |      | 2                          | _    | 2           |      | 2          | _    | 2         |             | ns   |  |

| AAD    | Dynamic Supply Current<br>Commercial Temp. | -                          | 270  | -                          | 250  | -           | 230  |            | 210  |           | 190         | mA   |  |

| DAAD   | Dynamic Supply Current Military Temp.      | -                          | -    | -                          | -    | -           | 260  | -          | 240  | -         | 220         | mA   |  |

1. 165 and 135 specification over commercial temperature only.

5.14 - 14 14

Powered by ICminer.com Electronic-Library Service CopyRight 2003

2523 tol 09

# ANALOG OUTPUT DC ELECTRICAL CHARACTERISTICS

| Symbol     | Parameter                       | Test Cond            | litions         | Min.  | Тур.  | Max.  | Unit |

|------------|---------------------------------|----------------------|-----------------|-------|-------|-------|------|

| Res        | Resolution                      |                      |                 | _     | 8     | 1     | bits |

| ILSB       | LSB Current Size                |                      |                 | -     | 69.1  | 1     | μА   |

| Li         |                                 |                      | I LSB Version   | _     | 1/2   | ±1    | LSB  |

|            |                                 |                      | 1/2 LSB Version | _     | 1/4   | ±1/2  | LSB  |

| LD         |                                 |                      | I LSB Version   | -     | 1/2   | ±1    | LSB  |

|            |                                 |                      | 1/2 LSB Version | -     | 1/4   | ±1/2  | LSB  |

| Voc        | Output Compliance Voltage       |                      |                 | -1.0  | _     | 1.2   | ٧    |

| RAOUT (2)  | Output Impedance                |                      |                 |       | 50    |       | kΩ   |

| CAOUT (2)  | Output Capacitance              | f = 1MHz, lout = 0mA |                 |       | 8     | 12    | pF   |

| IREF       | VREF Input Current              |                      |                 |       | 10    |       | μА   |

| Ем         | Matching Error (DAC to DAC)     |                      |                 | -     | 2     | 5     | %    |

| PSRR       | Power Supply Rejection<br>Ratio |                      |                 | =     | 50    | -     | dB   |

| [w (1)     | White Current                   | Measured to Blank    |                 | 17.69 | 19.05 | 20.40 | mA   |

| IB (1)     | Black Current                   | Measured to Blank    |                 | 0.95  | 1.44  | 1.90  | mA   |

| IBLANK     | Blank Current IOR, IOB          |                      |                 | 0     | 5     | 50    | μA   |

| IBLANK (1) | Blank Current IOG               |                      |                 | 6.29  | 7.62  | 8.96  | mA   |

| ISYNC      | Sync Current IOG                |                      |                 | 0     | 5     | 50    | μА   |

#### NOTES:

1. RSET =  $523\Omega$ . VREF = 1.235V

## 2. This parameter is guaranteed but not tested in production.

**ANALOG OUTPUT AC ELECTRICAL CHARACTERISTICS**

Following conditions apply unless otherwise specified: TA = 0°C to +70°C (Commercial Temperature Range)

TA = -55°C to +125°C (Military Temperature Range)

$VAA = 5.0V \pm 5\%$

TTL Inputs, VIL = 0.8V, VIH = 2.0V, rise/fall time <5ns

CLK Inputs, VIH = VAA - 1.0V, VIL = VAA - 1.6V, rise/fall time <2ns

Timing reference points at 50% of signal swing

|        | •                            |      |      | 75C457-165 <sup>(3)</sup> |      |      | 75C457-135 <sup>(3)</sup> |      | '75C457-125 |      | 75C457-110 |      | 110  | '75C457-80 |      |      |       |

|--------|------------------------------|------|------|---------------------------|------|------|---------------------------|------|-------------|------|------------|------|------|------------|------|------|-------|

| Symbol | Parameter                    | Min. | Тур. | Max.                      | Min. | Тур. | Max.                      | Min. | Тур.        | Max. | Min.       | Тур. | Max. | Min.       | Тур. | Max. | Unit  |

| FCLK   | Clock Frequency              | _    | -    | 165                       | _    | -    | 135                       | -    | -           | 125  | l -        | -    | 110  | -          | _    | 80   | MHz   |

| tvo    | Video Output Delay Time      | -    | 15   | -                         | -    | 15   | -                         | _    | 15          | -    | -          | 15   | -    | -          | 15   |      | ns    |

| tvT    | Video Output Transition Time |      | 1.5  | -                         | -    | 1.7  | _                         | -    | 1.8         | -    | -          | 2    |      | -          | 2    | -    | ns    |

| ts     | Video Output Skew            | _    | 0    | <2                        | -    | 0    | <2                        | -    | 0           | <2   | -          | 0    | <2   | -          | 0    | <2   | ns    |

| ts     | Video Ouput Setting Time     | -    | 6    | -                         | -    | 7    | -                         | -    | 8           | -    | -          | 8    | _    |            | 12   | · -  | ns    |

| FT     | Clock and Data Feedthrough   | _    | 50   | -                         | -    | 50   | -                         | -    | 50          | -    |            | 50   | -    |            | 50   | -    | pV-s  |

| GE     | Glitch Energy                | -    | 50   | -                         | -    | 50   | -                         | -    | 50          | _    | -          | 50   | _    | -          | 50   |      | pV-s  |

| СТ     | Crosstalk, DAC to DAC        | -    | 100  | -                         | -    | 100  | _                         | -    | 100         | -    | -          | 100  | -    |            | 100  |      | pV-s  |

| tvp    | Pipeline Delay               | 9    | -    | 9                         | 9    | -    | 9                         | 9    | -           | 9    | 9          | -    | 9    | 9          |      | 9    | clock |

| tpul   | PLL Delay Time               | -    | 15   | -                         | -    | 15   | -                         | - T  | 15          | _    |            | 15   | -    | l –        | 15   | _    | ns    |

#### NOTES:

1. CL = 10pF, 10%-90% points.

2. This parameter is guaranteed but not tested in production. 3. 165 and 135 MHz over commercial temperature range only. 2523 tol 10

Figure 9. Video I/O Timing Diagram

Figure 10. MPU WRITE Timing Diagram

5.14-16

16

Figure 11. MPU READ Timing Diagram

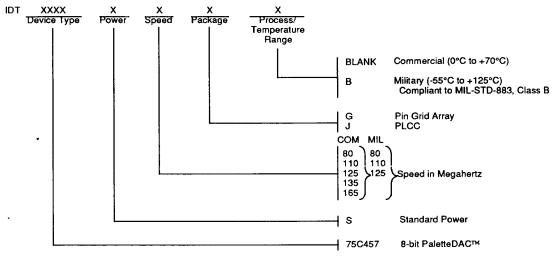

## **ORDERING INFORMATION**

2523 drw 15