# HT2823 Triple Tone Generator

## **Features**

- Single power supply: 2.4V~5.1V

- Low standby current: 1µA (typically at VDD=3V)

- Single, dual or triple tone output

- 128-step D/A output

- Auto power off function

- System clock of 65.5kHz

- Minimal external components

- Built-in envelop control circuitTone frequency programmable

## **General Description**

The HT2823 is a CMOS LSI specially designed for single, dual and triple tone generators. It

provides three built-in D/A converters to generate tones.

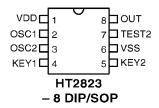

#### Pin Assignment

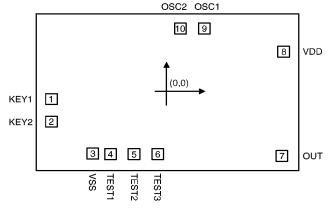

## **Pad Coordinates**

Unit: mil

| Pad No. | X      | Y      |

|---------|--------|--------|

| 1       | -48.32 | -3.4   |

| 2       | -48.32 | -13.34 |

| 3       | -30.94 | -27.37 |

| 4       | -23.55 | -27.67 |

| 5       | -13.64 | -27.67 |

| 6       | -3.66  | -27.67 |

| 7       | 48.41  | -28.47 |

| 8       | 49.13  | 17.38  |

| 9       | 15.85  | 27.58  |

| 10      | 5.91   | 27.58  |

Chip size:  $109 \times 69 \text{ (mil)}^2$

<sup>\*</sup> The IC substrate should be connected to VDD in the PCB layout artwork.

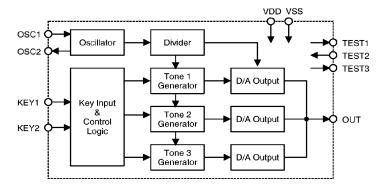

## **Block Diagram**

## **Pad Description**

| Pad  |                 |     | Internal           |                                                                                                                                                                                                     |

|------|-----------------|-----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.  | Pad Name        | I/O | Connection         | Description                                                                                                                                                                                         |

| 1, 2 | KEY1, KEY2      | I   | CMOS<br>Pull-Low   | Key tone trigger input, high active<br>A single tone/dual tone is generated by connecting<br>KEY1 or KEY2 to VDD. If KEY2 and KEY2 are both<br>connected to VDD, a triple tone output is generated. |

| 3    | vss             | I   |                    | Power supply (negative)                                                                                                                                                                             |

| 4~6  | TEST1~<br>TEST3 | I,O | _                  | For IC test only                                                                                                                                                                                    |

| 7    | OUT             | О   | PMOS<br>Open Drain | Tone signal output to drive a speaker via an NPN transistor for applications                                                                                                                        |

| 8    | VDD             | I   | _                  | Power supply (positive)                                                                                                                                                                             |

| 9    | OSC1            | I   | CMOS               | Oscillator input                                                                                                                                                                                    |

| 10   | OSC2            | 0   | CMOS               | Oscillator output                                                                                                                                                                                   |

## **Absolute Maximum Ratings\***

| Supply Voltage0.3V to 5.2V       | Input VoltageV <sub>SS</sub> $-0.3$ to V <sub>DD</sub> $+0.3$ V |

|----------------------------------|-----------------------------------------------------------------|

| Storage Temperature50°C to 125°C | Operating Temperature20°C to 75°C                               |

\*Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damageto the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2

## **Electrical Characteristics**

(Ta=25°C)

| Symbol             | Parameter                                           | Test Conditions   |                                                            | Min.                         | Tym  | Max.                 | Unit |

|--------------------|-----------------------------------------------------|-------------------|------------------------------------------------------------|------------------------------|------|----------------------|------|

| Symbol             |                                                     | $\mathbf{V_{DD}}$ | Conditions                                                 | WIIII.                       | Тур. | wax.                 |      |

| $ m V_{DD}$        | Operating Voltage                                   | _                 | _                                                          | 2.4                          | 3    | 5.1                  | v    |

| $I_{\mathrm{STB}}$ | Standby Current                                     | 3V                | R <sub>OSC</sub> =430kΩ<br>KEY1 and KEY2<br>are both open. | _                            | 1    | 5                    | μА   |

| $I_{ m DD}$        | Operating Current                                   | 3V                | F <sub>OSC</sub> =65.5kHz<br>No load                       | _                            | 80   | 200                  | μА   |

| $I_{\mathrm{IH}}$  | KEY1, KEY2 Input High<br>Current                    | 3V                | V <sub>IH</sub> =3V                                        | 3                            | 10   | 24                   | μА   |

| I <sub>OUT</sub>   | Max. OUT Output Current<br>(One Channel D/A Output) | 3V                | V <sub>OH</sub> =0.6V                                      | -0.9                         | -1.8 | -2.6                 | mA   |

| $V_{\mathrm{IH}}$  | "H" Input Voltage                                   | _                 | _                                                          | $0.8 \mathrm{V}_\mathrm{DD}$ | _    | _                    | v    |

| $ m V_{IL}$        | "L" Input Voltage                                   | _                 |                                                            | 0                            | _    | $0.2 { m V}_{ m DD}$ | v    |

| Fosc               | System Frequency                                    | 3V                | $R_{OSC}$ =430 $k\Omega$                                   | _                            | 65.5 | _                    | kHz  |

# **Functional Description**

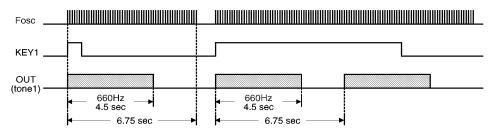

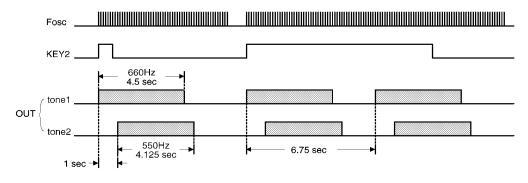

#### Single tone and dual tone outputs

The single tone (tone1) is generated by connecting KEY1 to VDD. As for the dual tone (tone1 and tone2), it is produced by connecting KEY2 to high. The following table shows the tone frequency as well as the tone duration of HT2823A.

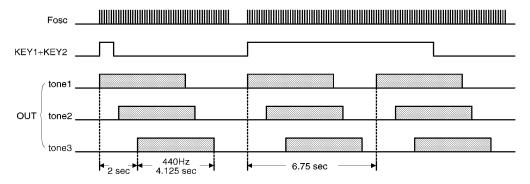

| Key Tone | Frequency | Duration<br>(F <sub>OSC</sub> =65.5kHz) |

|----------|-----------|-----------------------------------------|

| Tone1    | 660Hz     | 4.5 secs                                |

| Tone2    | 550Hz     | 4.125 secs                              |

| Tone3    | 440Hz     | 4.125 secs                              |

Notice the system frequency is  $65.5 \mathrm{kHz}$ .

# Triple tone output

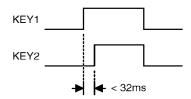

The triple tone (tone1, tone2 and tone3) is generated by connecting both KEY1 and KEY2 to VDD. The frequency of tone3 is 440Hz, and its duration is around 4.125 secs. The time difference for connecting KEY1 and KEY2 to VDD must be less than 32ms.

# Timing Diagram (HT2823A)

## Single tone

#### **Dual tone**

# Triple tone

4

\* Note: The time of key pressing must be greater than 8ms.

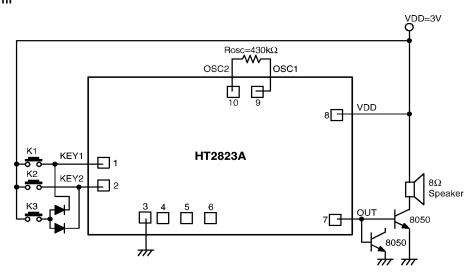

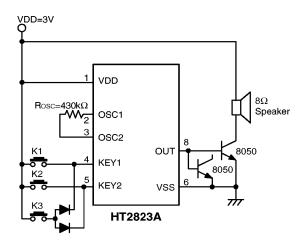

# **Application Circuits**

## Chip form

$\ensuremath{^{*}}$  The IC substrate should be connected to VDD in the PCB layout artwork.

## Package form

$<sup>\</sup>ensuremath{^*}$  The output of the HT2823A is a "door bell" sound.

5