# HM62A932 Series

## 32k x 9 Data Cache RAM

#### **■ DESCRIPTION**

The Hitachi HM62A932 is a high speed 288-kbit synchronous static cache RAM optimized for use in secondary caches for 32-bit microprocessor system. This RAM has a 32-kword x 9-bit organization for building a 32k x 32-bit cache data array, with byte parity by using four of these chips. The HM62A932 is available in a 44-pin PLCC for high density mounting.

#### **■ FEATURES**

- 32-kword x 9-bit organization

- · Synchronous read and write

- Internal burst read/write address counter

- Self-timed write

- Matches timing of 50 MHz 32-bit micro processor

- Additional address strobe input for implementing extended burst

### **■ ORDERING INFORMATION**

| Type No.                                                         | Access Time                      | CPU Clock Rate                       | Package        |

|------------------------------------------------------------------|----------------------------------|--------------------------------------|----------------|

| HM62A932CP-14<br>HM62A932CP-19<br>HM62A932CP-24<br>HM62A932CP-34 | 14 ns<br>19 ns<br>24 ns<br>34 ns | 50 MHz<br>40 MHz<br>33 MHz<br>25 MHz | 44-pin<br>PLCC |

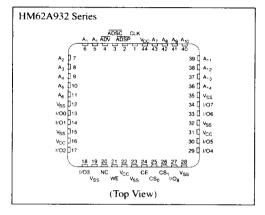

### ■ PIN ARRANGEMENT

### ■ PIN DESCRIPTION

| Pin Name                                              | Function                                       |

|-------------------------------------------------------|------------------------------------------------|

| CLK                                                   | Clock Input                                    |

| ADSP                                                  | Address Status Input from MPU                  |

| ADSC                                                  | Address Status Input from the Cache Controller |

| $CS_0, \overline{CS}_1$                               | Complementary Chip Select Input                |

| A0-A14                                                | Base Address Input                             |

| ADV                                                   | Synchronous Address Advance Input              |

| WE                                                    | Synchronous Write Enable Input                 |

| ŌE                                                    | Asynchronous Data Output Enable Input          |

| I/O <sub>0</sub> -I/O <sub>7</sub> , I/O <sub>8</sub> | Input/Output Data Pin                          |

| NC                                                    | No Connection                                  |

|                                                       |                                                |

## **(1)** HITACHI

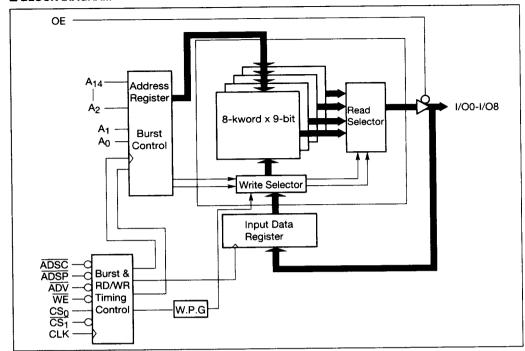

## **■ BLOCK DIAGRAM**

#### FUNCTION TABLE

Table 1. Synchronous Operation

| CS <sub>0</sub> | CS <sub>1</sub> | ADSP | ADSC | ĀĎV | WE | CLK | I/O Pin | Function                                                          |

|-----------------|-----------------|------|------|-----|----|-----|---------|-------------------------------------------------------------------|

| X               | Н               | X    | X    | X   | X  |     | High-Z  | Disable                                                           |

| L               | X               | X    | X    | X   | X  |     | High-Z  | Disable                                                           |

| <u>H</u>        | L               | L    | X    | X   | X  |     | Output  | Latch Base Address Read Address                                   |

| Н               | L               | Н    | L    | x   | L  |     | Input   | Latch Base Address Sample Write Data<br>Start a Self-Timed Write  |

| Н               | L               | Н    | L    | X   | Н  |     | Output  | Latch Base Address Read Access                                    |

| Н               | L               | Н    | Н    | L   | L  |     | Input   | Sample Write Data Advance Burst Count<br>Start a Self-Timed Write |

| Н               | L               | Н    | Н    | L   | Н  |     | Output  | Advance Burst Count Read Access                                   |

| н               | L               | Н    | Н    | Н   | L  |     | Input   | Start a Self-Timed Write                                          |

| Н               | L               | Н    | Н    | Н   | Н  |     | Output  | Read Access                                                       |

X = Don't care, H = High, L = Low, High-Z = High Impedance

Table 2. Asynchronous Output Control (See Notes 2 and 3 Below)

| OE | I/O Pin |

|----|---------|

| L  | Output  |

| Н  | High-Z  |

Notari I Tirr

- Notes: 1. Two separate address strobe inputs are provided and both will load a new base address. ADSP, from the MPU will override all other functions and cause a read access to the base address. ADSC, from the controller, is affected by WE if ADSP is inactive, and ADSC will start either a read or write cycle to the base address.

- The CS<sub>0</sub> and CS<sub>1</sub> inputs are sampled with the addresses when ADSP or ADSC is sampled active. Only if CS<sub>0</sub> and CS<sub>1</sub> are sampled active will WE or OE affect the chip.

- 3. Any time  $\overline{WE}$  is active when  $\overline{ADSP}$  is inactive, a self-timed write will start.

- 4. During data read cycles, data is always presented asynchronously with clock after  $\overline{OE}$  becomes low.

- 5. If the asynchrous  $\overline{OE}$  signal is activated during a self-timed write cycle, I/O pins will be in High-Z state.

- 6. OE must not be driven by any controller when setting up for a write cycle, since the data collision would corrupt the write data.

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 325

| Pin Descrip                         | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK                                 | Clock input signal. It samples all of the input signals except $\overline{OE}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ADSP                                | Address status input signal from MPU. When activated, a new "base" address is latched and an internal read access is performed. All other synchronous inputs are ignored when it is sampled active.                                                                                                                                                                                                                                                                                                                                   |

| ADSC                                | Address status input signal from the cache controller. When activated, a new "base" address is latched. Used during extended burst, and write-back cases when the cache controller must tell the device what addresses to access.                                                                                                                                                                                                                                                                                                     |

| $CS_0, \overline{CS}_1$             | Complementary chip select input signals. These are sampled along with the addresses when $\overline{ADSP}$ or $\overline{ADSC}$ is sampled. For any read/write or data bus activity to occur, CS <sub>0</sub> must be sampled high and $\overline{CS}_1$ must be sampled low.                                                                                                                                                                                                                                                         |

| A <sub>0</sub> , A <sub>14</sub>    | Base address input signals. They are sampled when $\overline{ADSP}$ or $\overline{ADSC}$ is active. A0-A14 may change after $\overline{ADSP}$ or $\overline{ADSC}$ samples them. A1 and A0 are latched and modified by the internal burst counter which XORs the bits in a certain burst order.                                                                                                                                                                                                                                       |

| ĀDV                                 | Address advance input signal. When $\overline{ADV}$ is sampled active, and $\overline{ADSP}$ and $\overline{ADSC}$ are both sampled inactive, $\overline{ADV}$ will increment the burst counter prior to a read or write access. If $\overline{ADV}$ and $\overline{WE}$ are sampled active, the address will be incremented before a self-timed write starts. If $\overline{ADV}$ is sampled active with $\overline{WE}$ inactive, the address will be incremented before a read access starts.                                      |

| WE                                  | Write enable input signal. When $\overline{WE}$ is sampled active and $\overline{ADSP}$ is sampled inactive, a self-timed write will start. When $\overline{WE}$ is sampled inactive, a self-timed write will start. When $\overline{WE}$ is sampled inactive, a read access will start. Active $\overline{WE}$ with $\overline{ADSC}$ active will cause a write to occur.                                                                                                                                                            |

| ŌĒ                                  | Asynchronous data output enable signal input. When active, the I/O pins will be driven will be driven with the read data available inside chip. $\overline{OE}$ activated while an internal self-timed write is in progress will cause the I/O pins to be High-Z. $\overline{OE}$ must be activated while an internal self-timed write is in progress will cause the I/O pins to be High-Z. $\overline{OE}$ must be inactive with enough margin before a self-timed write is started to guarantee that no data bus contention occurs. |

| I/O <sub>0</sub> , I/O <sub>8</sub> | Input/Output data pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### ■ FUNCTIONAL DESCRIPTION

HM62A932 Series

This cache RAM contains both data and address edge triggered latches to perform high speed synchronous accesses. These latches, combined with internal self-timed write logic, allow the write decision to be postponed until it is known that a write must be done.

An internal burst address counter is provided to support burst read and burst write cycles. The counter sequences through the four internal bytes on the rising edge of the clock when input is sampled active. If the device reaches end of the normal burst sequence, the counter will wrap-around to the initial base address.

The rules for handling the low order address bits during a burst sequence is shown here (the low order address bits):

Use base address provided with ADSC or ADSP Initial access:

Next burst access: Invert only base address Ao

Invert only base address A<sub>1</sub> Next burst access:

Invert only base address A1-A0 Next burst access:

Wrap-around, use initial base address Next burst access:

## ■ ABSOLUTE MAXIMUM RATINGS

| Item                                 | Symbol           | Value                 | Unit |

|--------------------------------------|------------------|-----------------------|------|

| Voltage on any pin relative to VSS   | VT               | $-0.5^{*1}$ to $+7.0$ | v    |

| Power Dissipation                    | PT               | 1.2                   | W    |

| Operating Temperature Range          | Topr             | 0 to +70              | °C   |

| Storage Temperature Range            | T <sub>stg</sub> | -55 to +125           | °C   |

| Storage Temperature Range Under Bias | Thias            | -10 to +85            | °C   |

Note: 1. V<sub>T</sub> min = -2.5 V for pulse width  $\le 10$  ns.

## ■ RECOMMENDED DC OPERATING CONDITIONS $(T_a = 0 \text{ to } 70^{\circ}\text{C})$

| Parameter                    | Symbol | Min.   | Тур | Max. | Unit |  |

|------------------------------|--------|--------|-----|------|------|--|

| Supply Voltage               | VCC    | 4.5    | 5.0 | 5.5  | V    |  |

|                              | Vss    | 0      | 0   | 0    | V    |  |

| Input High (Logic 1) Voltage | ViH    | 2.2    | _   | 6.0  | v    |  |

| Input Low (Logic 0) Voltage  | VIL    | -0.5*1 |     | 0.8  | V    |  |

Note: 1. VIL min = -2.0V for pulse width  $\le 10$  ns.

## **DC CHARACTERISTICS** ( $T_a = 0$ to $70^{\circ}$ C, $V_{CC} = 5V \pm 10\%$ , $V_{SS} = 0V$ )

| Parameter                                | Symbol          | Min. | Typ*1 | Max. | Unit | Test Conditions                     |

|------------------------------------------|-----------------|------|-------|------|------|-------------------------------------|

| Input Leakage Current                    | l <sub>LI</sub> |      | _     | 2    | μΑ   | VCC = Max., Vin = VSS to VCC        |

| Output Leakage Current                   | ILO             | _    | _     | 10   | μА   | Output Disable<br>VI/O = VSS to VCC |

| Active Operating Power<br>Supply Current | ICC             | _    |       | TBD  | mA   | TBD                                 |

| Output Low Voltage                       | Vol             | _    | _     | 0.4  | V    | IOL =3.2 mA                         |

| Output High Voltage                      | Voh             | 2.4  |       | _    | V    | IOH = -2.0  mA                      |

Note: 1. Typical limits are at  $V_{CC} = 5.0V$ ,  $T_a = +25^{\circ}C$  and specified loading

## **EXECUTANCE** $(T_a = 25^{\circ}C, f = 1 \text{ MHz})^{*1}$

| Parameter                | Symbol | Min | Max | Unit | Test Conditions       |

|--------------------------|--------|-----|-----|------|-----------------------|

| Input Capacitance        | Cin    | _   | 5   | pF   | $V_{in} = 0V$         |

| Input/Output Capacitance | CI/O   |     | 10  | pF   | V <sub>1/O</sub> = 0V |

Note: 1. This parameter is sampled and not 100% tested.

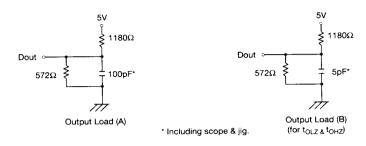

## **E AC CHARACTERISTICS** ( $V_{CC}$ = $5V \pm 10\%$ , $T_a$ = 0 to $70^{\circ}C$ )

## **Test Conditions**

Input and Output timing reference levels: 1.5V

Input pulse levels: Vss to 3V

Input rise and fall times: 3ns

Output load: See figures

|                                     |             | HM62A | 932-14   | HM62/    | 4932-19 | HM62/    | 932-24 | HM62A932-34 |            | Unit |

|-------------------------------------|-------------|-------|----------|----------|---------|----------|--------|-------------|------------|------|

| Parameter                           | Symbol      | Min   | Max      | Min      | Max     | Min      | Max    | Min         | Max        | Ont  |

| Read Cycle Time                     | tCYC        | 20    |          | 25       |         | 30       |        | 40          |            | ns   |

| Clock Pulse High                    | tCH         | 8     |          | 9.5      |         | 11       |        | 14          |            | ns   |

| Clock Pulse Low                     | tCL         | 8     |          | 9.5      |         | - 11_    |        | 14          |            | ns   |

| Address Setup Time                  | tAS         | 3     |          | 3        |         | . 5      |        | 5           |            | ns   |

| ADS Setup Time                      | tADSS       | 3     | _        | 3        |         | 5        |        | 5           | <b>↓</b> = | ns   |

| Output Select Setup Time            | tCSS        | 3     |          | 3        |         | 5        |        | 5           |            | ns   |

| Address Hold Time                   | tAH         | 2     | <u> </u> | 2        |         | 3        |        | 3_          | <u> </u>   | ns   |

| ADS Hold Time                       | tADSH       | 2     | <u> </u> | 2        |         | 3        |        | 3           |            | ns   |

| Chip Select Hold Time               | <b>ICSH</b> | 2     | _        | 2        |         | 3        |        | 3           | ļ          | ns   |

| Input Data Setup Time               | tDS         | 3     |          | 3        |         | 5        |        | 5           |            | ns   |

| ADV Setup Time                      | tADVS       | 3     |          | 3        |         | 5        |        | 5           | <u> </u>   | ns   |

| Write Enable Setup Time             | twes        | 3     |          | 3        |         | 5        |        | 5           |            | ns   |

| Input Data Hold Time                | tDH         | 2     |          | 2        |         | 3        |        | 3           | <u>↓</u>   | ns   |

| ADV Hold Time                       | tADVH       | 2     | <u> </u> | 2        |         | 3        |        | 3_          |            | ns   |

| Write Enable Hold Time              | tWEH        | 2     |          | 2        |         | 3        |        | 3           |            | ns   |

| Clock to Output Valid               | tCD         |       | 14       | <u> </u> | 19      |          | 24     |             | 34         | ns_  |

| Output Enable Low to Output Valid   | tOE         |       | 7        |          | 8       |          | 9      |             | 10         | ns   |

| Output Enable Low to Output Low-Z   | tOLZ*1,*2   | 0     |          | 0        |         | 0        |        | 0           |            | ns   |

| Read Data Hold After New Clock      | tDC         | 3     |          | 3        |         | 3        |        | 3           | <u> </u>   | ns   |

| Output Enable High to Output High-Z | toHZ*1,*2   |       | 7        | <u> </u> | 8       |          | 9      |             | 10         | ns   |

| System Clock Skew                   | tSKEW       |       | 1        | _        | 1       |          | 1      | 1 -         | 1          | ns   |

| Frequency                           |             |       | 50       |          | 40      | <u> </u> | 33     | 12          | 25         | MHz  |

Notes: 1. Transition is measured ± 200 mV from steady state voltage with Load (B).

2. This parameter is sampled and not 100% tested.

328 Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

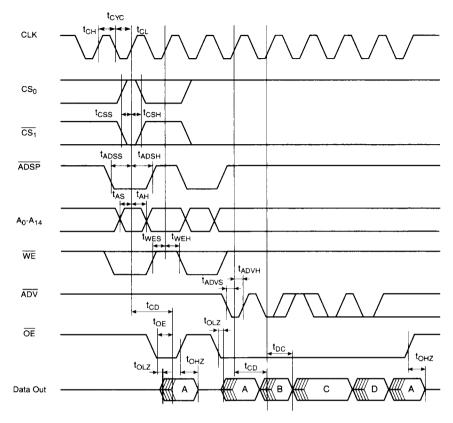

## **III** TIMING WAVEFORMS

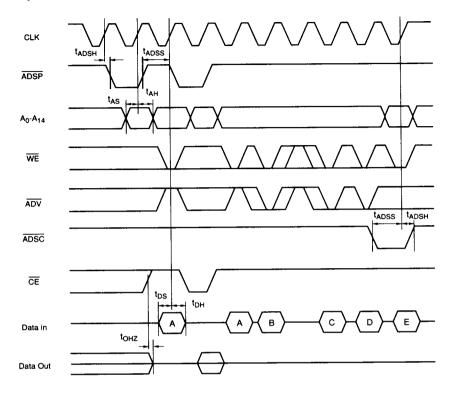

## (1) Read Cycle Followed by Burst with Wait State Added to Data C

- A-Data from Base ADDR

- B-Data from Base ADDR except A<sub>0</sub> is now  $\overline{A}_0$

- C-Data from Base ADDR except A<sub>1</sub> is now A<sub>1</sub>

- D-Data from Base ADDR except A<sub>0</sub> and  $\overline{A}_1$  are now  $\overline{A}_0$  and  $\overline{A}_1$

Note: 1. If ADSP or ADSC goes low during a burst cycle, a new address will be loaded, and another burst cycle will be started.

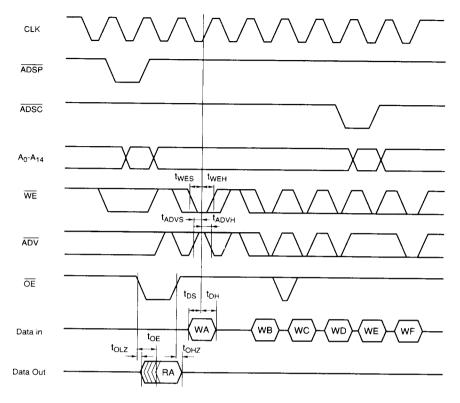

# (2) Write Cycle Followed by Burst Write with Wait State Added to Data C

A-Data to be written to Base ADDR

B-Data to be written to Base ADDR except A<sub>0</sub> is now A<sub>0</sub>

C-Data to be written to Base ADDR except A1 is now A1

D-Data to be written to Base ADDR except A<sub>0</sub> and A<sub>1</sub> are now  $\overline{A}_0$  and  $\overline{A}_1$

E-Data to be written to new Base ADDR loaded by  $\overline{ADSC}$

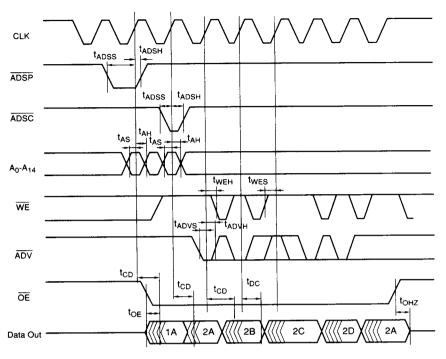

## (3) Burst Mixed Read/Write Cycles

RA-Data from Base ADDR

WA-Data to be written to Base ADDR

WB-Data to be written to Base ADDR except  $A_0$  is now  $\overline{A}_0$

WC-Data to be written to Base ADDR except  $A_1$  is now  $\overline{A}_1$

WD-Data to be written to Base ADDR except  $A_0$  and  $A_1$  are now  $\overline{A}_0$  and  $\overline{A}_1$

WE-Data to be written to new Base ADDR

WF-Data to be written to new Base ADDR except  $A_0$  is now  $\overline{A}_0$

## (4) Sequencial ADSP/ADSC Cycles

1A-Data from Base ADDR1

2A-Data from Base ADDR2

2B-Data from Base ADDR2 except A0 is now  $\overline{A}0$

2C-Data from Base ADDR2 except  $A_1$  is now  $\overline{A}_1$

2D-Data from Base ADDR2 except  $A_0$  and  $A_1$  are now  $\overline{A}_0$  and  $\overline{A}_1$

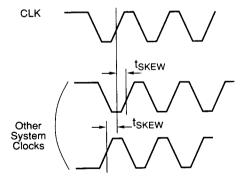

## (5) System Clock Skew Requirements

For this synchronous memory to meet its system timing requirements, the system clock skew must not exceed the specified range. Larger clock skews will require smaller clock-to-access times (tCD).

# **(1)** HITACHI

332 Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300