June 1995 (1 of 4)

# CELERITEK

# Amplifier-Switch 1.7 to 2.2 GHz 200mW (+23 dBm)

T/R modes switched by control signal

#### **Features**

200mW (+23 dBm) output power

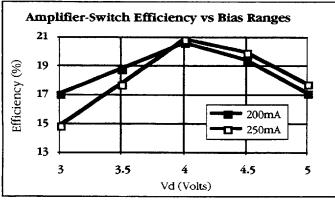

20% power added efficiency (including output switch loss)

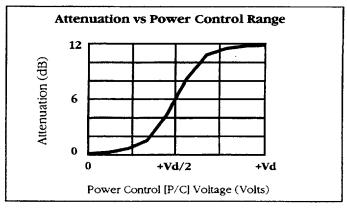

12 dB power control range

Surface mount SOIC-16 narrow plastic package

PCMCIA compatible

#### **Applications**

☐ Portable wireless communication (PCS/PCN, cordless phones)☐ Wireless local area networks (WLANs)

# Description

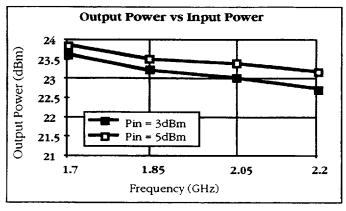

The CAS1402 is a power amplifier-switch designed for PCS/PCN and WLAN applications in the 1.7 to 2.2 GHz frequency range. The CAS1402 provides a +23dBm output signal from a +5dBm input signal with a typical power added efficiency of 20 %. An output switch is used to switch the RF path between Receive and Transmit modes. The CAS1402 requires both a positive and a negative supply to operate. Switching between the two modes is accomplished through switching a control signal (T/R Control) to the switch. The main supply voltage to the amplifier (+Vd) remains on in both Transmit and Receive modes. The negative supply voltage can be increased to cause the amplifier to "pinch off" to draw low current from the positive supply in Receive mode. The output power can be externally attenuated over a 12dB range via a positive control voltage applied to the power control (P/C) pin. When in Receive mode, the loss from the antenna pin (ANT) to the low noise amplifier pin (LNA) is typically less than 1dB.

#### **Absolute Maximum Ratings**

| Parameter           | Rating  |  |  |

|---------------------|---------|--|--|

| Drain voltage (+Vd) | +8V     |  |  |

| Drain current (Id)  | 350mA   |  |  |

| Power dissipation   | 1.5 W   |  |  |

| Thermal resistance  | 55 °C/W |  |  |

| Parameter           | Rating |

|---------------------|--------|

| Gate voltage (-Vg)  | -6V    |

| Power control (P/C) | +8V    |

| T/R control signal  | +8V    |

| RF input power      | 13dBm  |

| 5 °C to 150 °C  |

|-----------------|

| ,,              |

| 60 °C for 5 sec |

| 75 °C           |

|                 |

#### **Recommended Operating Conditions**

| Parameter                                 | Typ       | Units |

|-------------------------------------------|-----------|-------|

| Drain voltage (+Vd), Switch supply (+Vs)  | 3.0 - 5.0 | V     |

| Drain current (Id), set by -Vg adjustment | 250       | mA    |

| Parameter                        | Min | Max | Units |

|----------------------------------|-----|-----|-------|

| Operating temperature (PC board) | -20 | 70  | °C    |

|                                  |     |     |       |

#### **Electrical Characteristics**

The following specifications are guaranteed at room temperature with drain voltage (+Vd) = 4.0V +/-5%, drain current (Id) = 250mA +/- 10% (-Vg set to approximately -1.5V), T/R control signal (T/R Control) = 4.0V +/-5%, RF input power = +5 dBm, and power control (P/C) = 0V.

| Parameter                                                     | Condition                             | Min  | Typ     | Max   | Units    |

|---------------------------------------------------------------|---------------------------------------|------|---------|-------|----------|

| Frequency Range                                               |                                       | 1.7  |         | 2.2   | GHz      |

| Pout                                                          | · · · · · · · · · · · · · · · · · · · | 22   | 23      |       | dBm      |

| Power added efficiency (1)                                    |                                       |      | 20 %    |       | GDIII    |

| Gate voltage (-Vg)                                            | Id = 250 mA                           | -1.0 | -1.5    | -3.0  | V        |

| Gate current (Ig)                                             | Id = 250 mA                           |      | 1.0     | 3.0   | mA       |

| T/R control current                                           |                                       |      | 1.0     | - 3.0 | mA       |

| Small signal gain                                             | Pin = -5dBm                           |      | 18.0    |       | dB       |

| Input/Output VSWR                                             |                                       |      | 2.2 : 1 |       | <u>u</u> |

| Power control range                                           | P/C = 0V  to  +Vd                     | 10.0 | 12.0    |       | dB       |

| Low noise amplifier (LNA) pin leakage                         | Transmit mode                         | 1    | 14.0    | 16.0  | dBm      |

| Antenna (ANT) to low noise amplifier (LNA) pin insertion loss | Receive mode                          |      | 1.0     | 1.3   | dB       |

| Switching speed                                               |                                       | i    | 100     |       | nS       |

(1) Efficiency includes output switch loss. Typical efficiency of amplifier alone is 25%. Specifications subject to change without notice.

3236 Scott Boulevard

Santa Clara, California 95054

Phone: (408) 986-5060

Fax: (408) 986-5095

**■** 1974503 0000191 499 ■

64

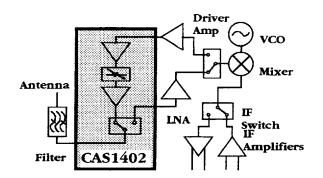

# **Typical Transceiver Application**

The CAS1402 Amplifier-Switch is an ideal choice for wireless transceivers. The block diagram to the right shows an implementation of the chip. The integrated switch simplifies the overall architecture of the transceiver as well as adding reliability through integration. Power control adds flexibility for varying transmit power environments.

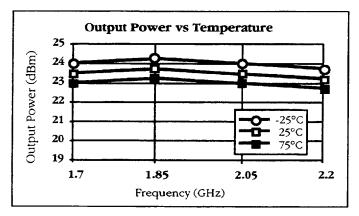

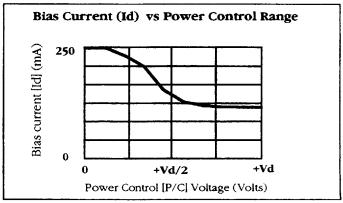

#### Typical performance curves

The following typical performance was tested at room temperature with drain voltage (+Vd) = 4.0V +/-5%, drain current (Id) = 250mA +/- 10% (-Vg set to approximately -1.5V), T/R control signal (T/R Control) = 4.0V +/-5%, RF input power = +5 dBm, Frequency = 2.2 GHz, and power control (P/C) = 0\ unless otherwise specified.

CELERITEK

1974503 0000192 325

3236 Scott Boulevard, Santa Clara, California 95054 Phone: (408) 986-5060 Fax: (408) 986-5095

65

June 1995 (3 of 4)

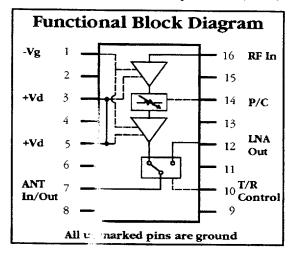

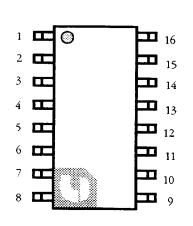

# Connection Diagram and Pin Description

| Pin # | Name        | I/O | Description                                                         |

|-------|-------------|-----|---------------------------------------------------------------------|

| 1     | -Vg         | I   | Negative voltage input for amplifier gate control.                  |

| 2     | GND         |     | Ground connection.                                                  |

| 3     | +Vd         | I   | Drain voltage internally connected to pin 5. (1)                    |

| 4     | GND         |     | Ground connection.                                                  |

| 5     | +Vd         | 1   | Drain voltage internally connected to pin 3. (1)                    |

| 6     | GND         |     | Ground connection.                                                  |

| 7     | ANT         | 1/0 | Antenna connection. Input in Receive mode, Output in Transmit.      |

| 8     | GND         |     | Ground connection.                                                  |

| 9     | GND         |     | Ground connection.                                                  |

| 10    | T/R Control | Į   | T/R Control Signal. (2)                                             |

| 11    | GND         |     | Ground connection.                                                  |

| 12    | LNA         | 0   | External LNA output ( Receive mode).                                |

| 13    | GND         |     | Ground connection.                                                  |

| 14    | P/C         | I   | Power Control connection. 0V to +Vd at: _nuates output power level. |

| 15    | GND         |     | Ground connection.                                                  |

| 16    | RF In       | I   | RF input to switch amplifier for Transmit mode.                     |

- (1) As Pins 3 and 5 are internally connected, only one pin requires applied voltage.

- (2) Transmit mode selected when +Vd is applied. Receive mode selected when 0V is applied.

#### **Application Information**

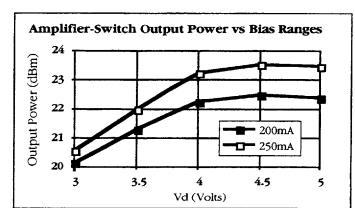

The CAS1402 is specified at +4.0V, 250mA. The typical relationship of output power (and overall efficiency) to bias is shown in the performance curves. Care should be taken to keep the maximum dissipated power below 1.5W and PC board temperature below 70°C in order to keep the active device junction well below the maximum rated temperature. For optimum performance, good thermal design is necessary.

The CAS1402 is a microwave device. By nature, its performance is affected by the circuit environment within which it operates. Celeritek has found that shunt capacitance (typically less than 1pF) at the RF pins optimizes performance. Because circuit board layout will affect the impedance presented to the device, Celeritek recommends a prototype phase for board design to realize best results.

**Power up/power down sequence** In order to prevent damage to the CAS1402 due to excessive power dissipation (greater then the 1.5W specified), the negative supply (-V) must be powered on prior to the positive supply (+V). When powering down, the positive supply must be powered off prior to the negative supply.

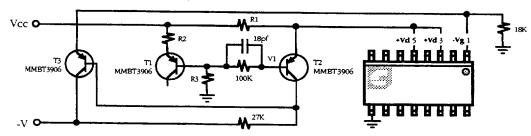

Biasing the CAS1402 The CAS1402 was designed for optimum efficiency and maximum output power when operated at a drain voltage (Vd) of 4 Volts and a drain current (Id) of 250 mA. The drain current of the CAS1402 is set by adjusting the gate voltage (-Vg) to the device. Designs need to incorporte a means of setting this voltage within the -1.0 to -3.0 Volt range specified to obtain Id = 250 mA. The exact relationship of gate voltage (-Vg) to drain current (Id) will vary. For this reason an active bias circuit similar to the one shown below is recommended. This active bias circuit has been designed to hold the drain current (and the output power) constant from device to device in high volume manufacturing by automatically adjusting the gate voltage.

#### Active Bias Circuit Diagram

Circuit Operation A temperature compensated reference is formed by R2, R3, and T1 at node V1. As variations from device to device occur on the CAS1402 due to normal processing tolerances, the drain current will change with a constant voltage applied to the -Vg pin (pin 1). As the drain current changes transistor T2 is either turned on harder or turned off more, which changes the voltage on the base of transistor T3, turning it off or on. This negative feedback adjusts the pin 1 gate voltage to cause a relatively constant drain current condition.

Component Selection RI is used to set the drain current. It is a small value resistor that sets the relationship between the drain current and the drain voltage that is applied to the device. It is specified by the equation:  $RI = \frac{V_{CC} - Vd}{V}$

Since the best operating point for this device is Vd = 4 Volts and Id = 250 mA, in a nominal 5 Volt system, R1 should be 4 ohms. It is important to make sure that R1 is sized to be able to handle the current that will flow through it. The ratio of the resistive divider formed by R2 and R3 is determined by the ratio of the voltage Vd and Vcc as shown: Vd/Vcc = R3

R2 and R3 should be sufficiently large to minimze power dissipation in those applications that are power sensitive. A value of R3 of about 50K ohms is suggested.

3236 Scott Boulevard

Santa Clara, California 95054

Phone: (408) 986-5060

R2 + R3

Fax: (408) 986-5095

📰 1974503 0000193 261 **=**

660

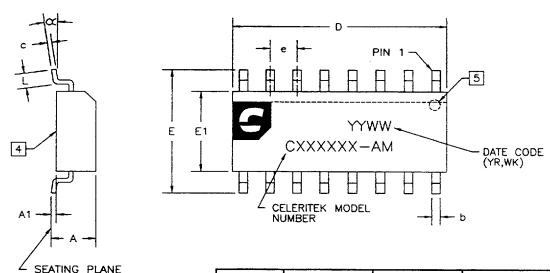

#### **Physical Dimensions**

NOTES: (UNLESS OTHERWISE SPECIFIED)

- 1. DIMENSIONS ARE IN MILLIMETERS[INCHES].

- 2. LEAD MATERIAL: COPPER

- 3. BODY MATERIAL: PLASTIC (EPOXY).

- 4. COUNTRY OF ORIGIN, IF OTHER THAN U.S., SHALL BE MARKED ON THIS SURFACE.

- 5. PIN 1 IDENTIFICATION IS A DOT OR BEVELED EDGE.

| DIMENSION | MINIMUM      | NOMINAL     | MAXIMUM      |

|-----------|--------------|-------------|--------------|

| Α         | 1.35[0.053]  | 1.63[0.064] | 1.75[0.069]  |

| A1        | 0.10[0.004]  | 0.15[0.006] | 0.20[0.008]  |

| b         | 0.35[0.014]  |             | 0.45[0.018]  |

| С         | 0.19[0.007]  |             | 0.22[0.009]  |

| D         | 9.80[0.385]  | 9.90[0.390] | 10.00[0.394] |

| Е         | 5.80[0.228]  | 5.99[0.236] | 6.20[0.244]  |

| E1        | 3.80[0.150]  | 3.91[0.154] | 4.00[0.158]  |

| e         |              | 1.27[0.050] |              |

| Ĺ         | 0.508[0.020] | 0.64[0.025] | 1.143[0.045] |

| α         | 0*           |             | 8.           |

# Test Configuration and Evaluation

Celeritek tests the CAS2402 on an FR4 PC test board. FR4 was chosen for its low loss characteristics at 2.2 GHz. Plated through hole connections from the top of the board to the backside ground plane minimizes inductance in the ground connections. These through hole connections are as close as possible to each ground pin. More details are available in a separate application note (AP-0001) for this product.

For evaluation purposes Celeritek offers a prototype evaluation board (PB-CAS1402-AM) for the CAS1402. Please call the factory or a local representative for more information.

# **Handling Precaution**

Microwave devices are sensitive to electrostatic discharge. Proper precautions should be taken to avoid ESD damage.

#### Ordering Information

The CAS1402 is available in a surface mount SOIC-16 narrow plastic package (physical dimensions shown above). Part Number for ordering Package

CAS1402-AM-000T

SOIC-16 surface mount narrow plastic package Same as above in Tape and Reel

Please consult the factory or local representative for delivery information. Standard shipping containers 508mm [20 inch] long antistatic gravity feed tubes. Please consult the factory for military versions, and or special screening requirements.

Celeritek reserves the right to make changes without further notice to any products herein. Celeritek makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Celeritek assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Celeritek does not convey any license under its patent rights nor the rights of others. Celeritek products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Celeritek product could create a situation where personal injury or death may occur. Should Buyer purchase or use Celeritek products for any such unintended or unauthorized application, Buyer shall indemnify and hold Celeritek and is officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Celeritek was negligent regarding the design or manufacture of the part. Celeritek is a registered trademark of Celeritek, Inc. Celeritek, Inc. is an Equal Opportunity/Affirmative Action Employer.

3236 Scott Boulevard, Santa Clara, California 95054 Phone: (408) 986-5060 Fax: (408) 986-5095