## ADVANCE INFORMATION

## INTEL StrataFlash™ MEMORY TECHNOLOGY 32 AND 64 MBIT

28F320J5 and 28F640J5

- High-Density Symmetrically-Blocked Architecture

- 64 128-Kbyte Erase Blocks (64 M)

- 32 128-Kbyte Erase Blocks (32 M)

- 5 V V<sub>CC</sub> Operation

- 2.7 V I/O Capable

- Configurable x8 or x16 I/O

- 120 ns Read Access Time (32 M) 150 ns Read Access Time (64 M)

- Enhanced Data Protection Features

- Absolute Protection with V<sub>PEN</sub> = GND

- Flexible Block Locking

- Block Erase/Program Lockout during Power Transitions

- Industry-Standard Packaging

- μBGA\* Package, SSOP and TSOP Packages (32 M)

- **■** Cross-Compatible Command Support

- Intel Basic Command Set

- Common Flash Interface

- Scaleable Command Set

- 32-Byte Write Buffer

- 6 μs per Byte Effective Programming Time

- 640,000 Total Erase Cycles (64 M)

320,000 Total Erase Cycles (32 M)

10,000 Erase Cycles per Block

- Automation Suspend Options

- Block Erase Suspend to Read

- Block Erase Suspend to Program

- System Performance Enhancements

STS Status Output

- Intel StrataFlash™ Memory Flash Technology

Capitalizing on two-bit-per-cell technology, Intel StrataFlash™ memory products provide 2X the bits in 1X the space. Offered in 64-Mbit (8-Mbyte) and 32-Mbit (4-Mbyte) densities, Intel StrataFlash memory devices are the first to bring reliable, two-bit-per-cell storage technology to the flash market.

Intel StrataFlash memory benefits include: more density in less space, lowest cost-per-bit NOR devices, support for code and data storage, and easy migration to future devices.

Using the same NOR-based ETOX<sup>™</sup> technology as Intel's one-bit-per-cell products, Intel StrataFlash memory devices take advantage of 400 million units of manufacturing experience since 1988. As a result, Intel StrataFlash components are ideal for code or data applications where high density and low cost are required. Examples include networking, telecommunications, audio recording, and digital imaging.

By applying FlashFile™ memory family pinouts, Intel StrataFlash memory components allow easy design migrations from existing 28F016SA/SV, 28F032SA, and Word-Wide FlashFile memory devices (28F160S5 and 28F320S5).

Intel StrataFlash memory components deliver a new generation of forward-compatible software support. By using the Common Flash Interface (CFI) and the Scaleable Command Set (SCS), customers can take advantage of density upgrades and optimized write capabilities of future Intel StrataFlash memory devices.

Manufactured on Intel's 0.4 micron ETOX™ V process technology, Intel StrataFlash memory provides the highest levels of quality and reliability.

January 1998 Order Number: 290606-004

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The 28F320J5 and 28F640J4 may contain design defects or errors known as errata. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937 Denver, CO 80217-9808 or call 1-800-548-4725 or visit Intel's website at http://www.intel.com

COPYRIGHT © INTEL CORPORATION 1997, 1998

CG-041493

\*Third-party brands and names are the property of their respective owners.

## **CONTENTS**

| PAC                                                 | èΕ |

|-----------------------------------------------------|----|

| 1.0 PRODUCT OVERVIEW                                | 5  |

| 2.0 PRINCIPLES OF OPERATION                         |    |

| 2.1 Data Protection                                 | 12 |

| 3.0 BUS OPERATION                                   | 12 |

| 3.1 Read                                            | 13 |

| 3.2 Output Disable                                  | 13 |

| 3.3 Standby                                         |    |

| 3.4 Reset/Power-Down                                | 13 |

| 3.5 Read Query                                      |    |

| 3.6 Read Identifier Codes                           | 14 |

| 3.7 Write                                           | 14 |

| 4.0 COMMAND DEFINITIONS                             | 14 |

| 4.1 Read Array Command                              | 18 |

| 4.2 Read Query Mode Command                         |    |

| 4.2.1 Query Structure Output                        | 18 |

| 4.2.2 Query Structure Overview                      | 20 |

| 4.2.3 Block Status Register                         | 21 |

| 4.2.4 CFI Query Identification String               | 22 |

| 4.2.5 System Interface Information                  | 23 |

| 4.2.6 Device Geometry Definition                    | 24 |

| 4.2.7 Primary-Vendor Specific Extended  Query Table | 25 |

| 4.3 Read Identifier Codes Command                   |    |

| 4.4 Read Status Register Command                    |    |

| 4.5 Clear Status Register Command                   |    |

| 4.6 Block Erase Command                             |    |

| 4.7 Block Erase Suspend Command                     | 27 |

| 4.8 Write to Buffer Command                         |    |

| 4.9 Byte/Word Program Commands                      | 28 |

| 4.10 Configuration Command                          |    |

| 4.11 Set Block and Master Lock-Bit Commands         | 29 |

| 5.0 DESIGN CONSIDERATIONS40                                |

|------------------------------------------------------------|

| 5.1 Three-Line Output Control40                            |

| 5.2 STS and Block Erase, Program, and Lock-                |

| Bit Configuration Polling40                                |

| 5.3 Power Supply Decoupling40                              |

| 5.4 V <sub>CC</sub> , V <sub>PEN</sub> , RP# Transitions40 |

| 5.5 Power-Up/Down Protection41                             |

| 5.6 Power Dissipation41                                    |

|                                                            |

| 6.0 ELECTRICAL SPECIFICATIONS42                            |

| 6.1 Absolute Maximum Ratings42                             |

| 6.2 Operating Conditions42                                 |

| 6.3 Capacitance42                                          |

| 6.4 DC Characteristics43                                   |

| 6.5 AC Characteristics— Read-Only                          |

| Operations45                                               |

| 6.6 AC Characteristics— Write Operations48                 |

| 6.7 Block Erase, Program, and Lock-Bit                     |

| Configuration Performance51                                |

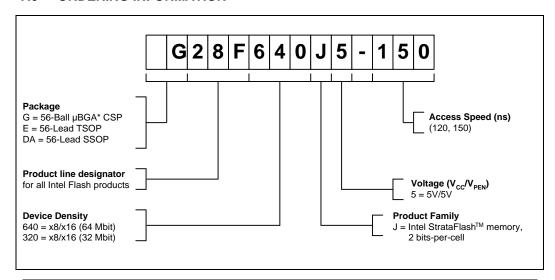

| 7.0 ORDERING INFORMATION52                                 |

| 8.0 ADDITIONAL INFORMATION53                               |

PAGE

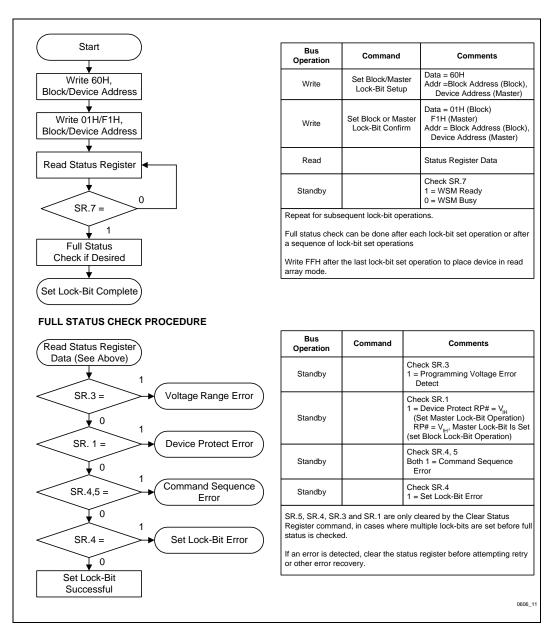

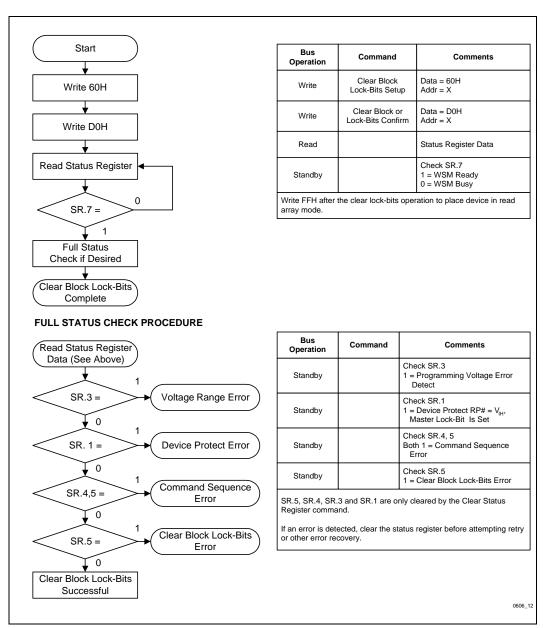

4.12 Clear Block Lock-Bits Command......30

| IGURES                                                                                                                                                                                                                                                                     | TABLES                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Figure 1. Intel StrataFlash™ Memory Block Diagram6                                                                                                                                                                                                                         | Table 1. Lead Descriptions7  Table 2. Chip Enable Truth Table13 |

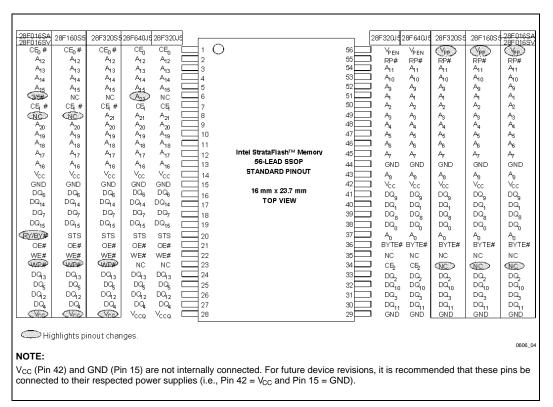

| Figure 2. µBGA* Package (64-Mbit and 32-Mbit)9 Figure 3. TSOP Lead Configuration (32-Mbit)10 Figure 4. SSOP Lead Configuration (64-Mbit and 32-Mbit)                                                                                                                       | Table 3. Bus Operations                                         |

| Figure 8. Byte/Word Program Flowchart                                                                                                                                                                                                                                      | Table 7. Query Structure                                        |

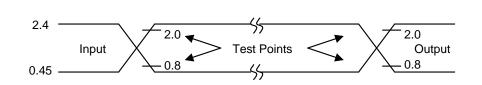

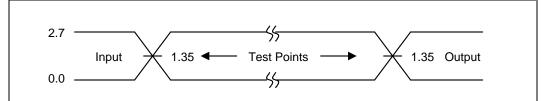

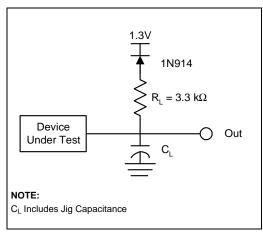

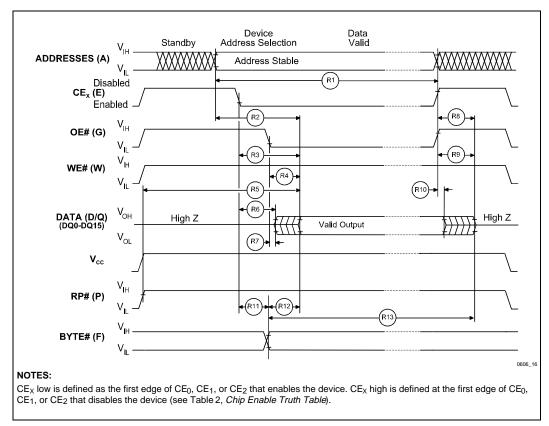

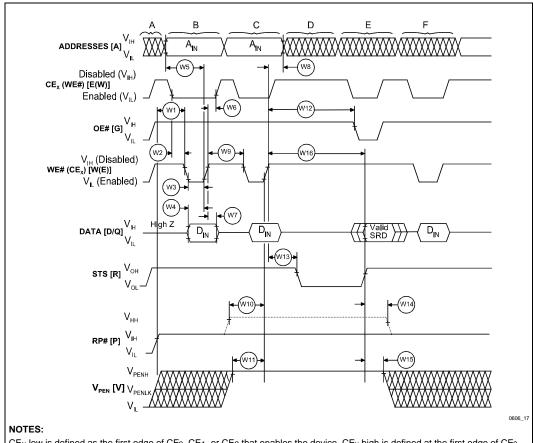

| Figure 13. Transient Input/Output Reference Waveform for V <sub>CCQ</sub> = 5.0 V ± 10% (Standard Testing Configuration)45  Figure 14. Transient Input/Output Reference Waveform for V <sub>CCQ</sub> = 2.7 V-3.6V45  Figure 15. Transient Equivalent Testing Load Circuit | Table 13. Identifier Codes                                      |

## **REVISION HISTORY**

| Date of<br>Revision | Version | Description                                                                                                                                                                                                                   |

|---------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09/01/97            | -001    | Original Version                                                                                                                                                                                                              |

| 09/17/97            | -002    | Modifications made to cover sheet                                                                                                                                                                                             |

| 12/01/97            | -003    | V <sub>CC</sub> /GND Pins Converted to No Connects specification change added I <sub>CCS</sub> , I <sub>CCD</sub> , I <sub>CCW</sub> , and I <sub>CCE</sub> specification change added Order Codes specification change added |

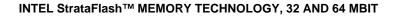

| 1/31/98             | -004    | The μBGA* chip-scale package in Figure 2 was changed to a 52-ball package and appropriate documentation added. The 64-Mb μBGA package dimensions were changed in Figure 2. Changed Figure 4 to read SSOP instead of TSOP.     |

### 1.0 PRODUCT OVERVIEW

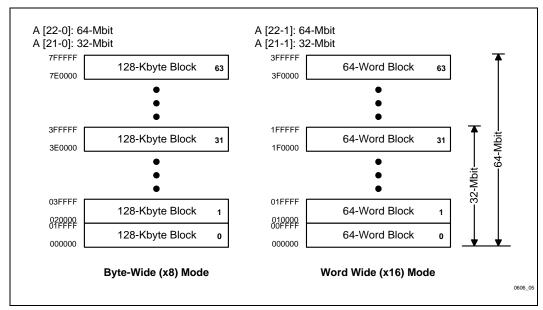

The Intel StrataFlash™ memory family contains high-density memories organized as 8 Mbytes or 4 Mwords (64-Mbit) and 4 Mbytes or 2 Mwords (32-Mbit). These devices can be accessed as 8- or 16-bit words. The 64-Mbit device is organized as sixty-four 128-Kbyte (131,072 bytes) erase blocks while the 32-Mbits device contains thirty-two 128-Kbyte erase blocks. Blocks are selectively and individually lockable and unlockable in-system. See the memory map in Figure 5.

A Common Flash Interface (CFI) permits software algorithms to be used for entire families of devices. This allows device-independent, JEDEC ID-independent, and forward- and backward-compatible software support for the specified flash device families. Flash vendors can standardize their existing interfaces for long-term compatibility.

Scaleable Command Set (SCS) allows a single, simple software driver in all host systems to work with all SCS-compliant flash memory devices, independent of system-level packaging (e.g., memory card, SIMM, or direct-to-board placement). Additionally, SCS provides the highest system/device data transfer rates and minimizes device and system-level implementation costs.

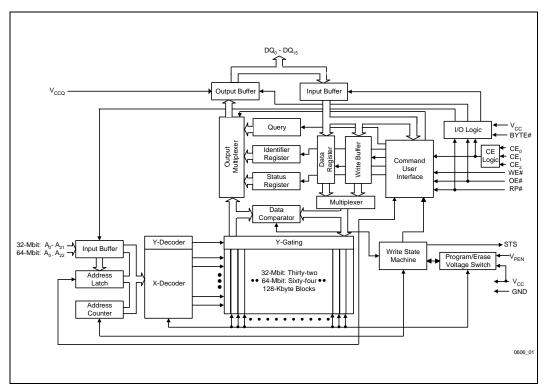

A Command User Interface (CUI) serves as the interface between the system processor and internal operation of the device. A valid command sequence written to the CUI initiates device automation. An internal Write State Machine (WSM) automatically executes the algorithms and timings necessary for block erase, program, and lock-bit configuration operations.

A block erase operation erases one of the device's 128-Kbyte blocks typically within one second—independent of other blocks. Each block can be independently erased 10,000 times. Block erase suspend mode allows system software to suspend block erase to read or program data from any other block.

Each device incorporates a Write Buffer of 32 bytes (16 words) to allow optimum programming performance. By using the Write Buffer, data is programmed in buffer increments. This feature can improve system program performance by up to 20 times over non Write Buffer writes.

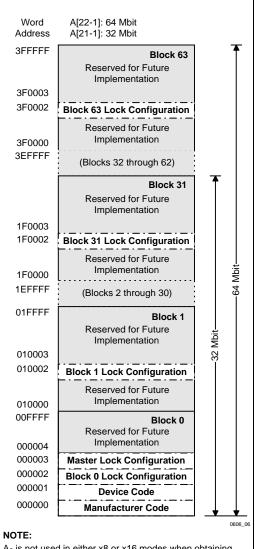

Individual block locking uses a combination of bits, block lock-bits and a master lock-bit, to lock and unlock blocks. Block lock-bits gate block erase and program operations while the master lock-bit gates block lock-bit modification. Three lock-bit configuration operations set and clear lock-bits (Set Block Lock-Bit, Set Master Lock-Bit, and Clear Block Lock-Bits commands).

The status register indicates when the WSM's block erase, program, or lock-bit configuration operation is finished.

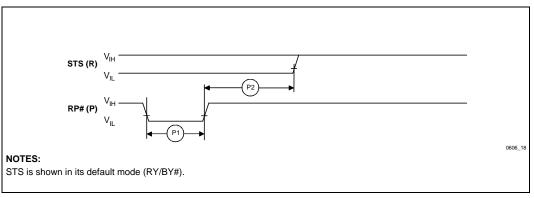

The STS (STATUS) output gives an additional indicator of WSM activity by providing both a hardware signal of status (versus software polling) and status masking (interrupt masking for background block erase, for example). Status indication using STS minimizes both CPU overhead and system power consumption. When configured in level mode (default mode), it acts as a RY/BY# pin. When low, STS indicates that the WSM is performing a block erase, program, or lock-bit configuration. STS-high indicates that the WSM is ready for a new command, block erase is suspended (and programming is inactive), or the device is in reset/power-down mode. Additionally, the configuration command allows the STS pin to be configured to pulse on completion of programming and/or block erases.

Three CE pins are used to enable and disable the device. A unique CE logic design (see Table 2, *Chip Enable Truth Table*) reduces decoder logic typically required for multi-chip designs. External logic is not required when designing a single chip, a dual chip, or a 4-chip miniature card or SIMM module.

The BYTE# pin allows either x8 or x16 read/writes to the device. BYTE# at logic low selects 8-bit mode; address A<sub>0</sub> selects between the low byte and high byte. BYTE# at logic high enables 16-bit operation; address A<sub>1</sub> becomes the lowest order address and address A<sub>0</sub> is not used (don't care). A device block diagram is shown in Figure 1.

When the device is disabled (see Table 2, *Chip Enable Truth Table*) and the RP# pin is at  $V_{CC}$ , the standby mode is enabled. When the RP# pin is at GND, a further power-down mode is enabled which minimizes power consumption and provides write protection during reset. A reset time ( $t_{PHQV}$ ) is required from RP# switching high until outputs

are valid. Likewise, the device has a wake time  $(t_{PHWL})$  from RP#-high until writes to the CUI are recognized. With RP# at GND, the WSM is reset and the status register is cleared.

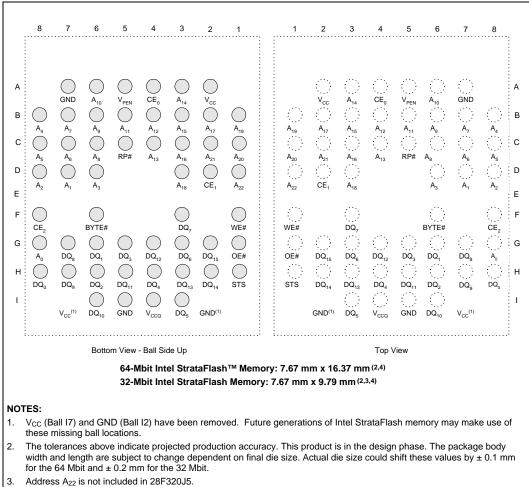

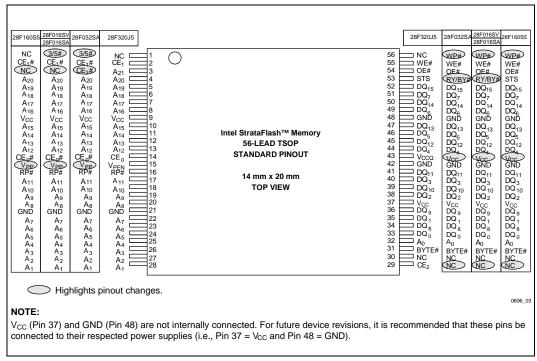

The Intel StrataFlash memory devices are available in several package types. The 64-Mbit is

available in 56-lead SSOP (Shrink Small Outline Package) and  $\mu BGA^*$  package (micro Ball Grid Array). The 32-Mbit is available in 56-lead TSOP (Thin Small Outline Package), 56-lead SSOP, and 56-bump  $\mu BGA$  packages. Figures 2, 3, and 4 show the pinouts.

Figure 1. Intel StrataFlash™ Memory Block Diagram

**Table 1. Lead Descriptions**

| Symbol                                                    | Type                    | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|-----------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A <sub>0</sub>                                            | INPUT                   | <b>BYTE-SELECT ADDRESS:</b> Selects between high and low byte when the device is in x8 mode. This address is latched during a x8 program cycle. Not used in x16 mode (i.e., the $A_0$ input buffer is turned off when BYTE# is high).                                                                                                                                                                                          |  |  |  |  |  |

| A <sub>1</sub> -A <sub>22</sub>                           | INPUT                   | ADDRESS INPUTS: Inputs for addresses during read and program operations addresses are internally latched during a program cycle.   32-Mbit: $A_0$ - $A_{21}$ 64-Mbit: $A_0$ - $A_{22}$                                                                                                                                                                                                                                         |  |  |  |  |  |

| DQ <sub>0</sub> –DQ <sub>7</sub>                          | INPUT/<br>OUTPUT        | LOW-BYTE DATA BUS: Inputs data during buffer writes and programming, and inputs commands during Command User Interface (CUI) writes. Outputs array, query, identifier, or status data in the appropriate read mode. Floated when the chip is de-selected or the outputs are disabled. Outputs DQ6-DQ0 are also floated when the Write State Machine (WSM) is busy. Check SR.7 (Status Register bit 7) to determine WSM status. |  |  |  |  |  |

| DQ <sub>8</sub> –DQ <sub>15</sub>                         | INPUT/<br>OUTPUT        | <b>HIGH-BYTE DATA BUS:</b> Inputs data during x16 buffer writes and programming operations. Outputs array, query, or identifier data in the appropriate read mode; not used for Status Register reads. Floated when the chip is de-selected, the outputs are disabled, or the WSM is busy.                                                                                                                                     |  |  |  |  |  |

| CE <sub>0</sub> ,<br>CE <sub>1</sub> ,<br>CE <sub>2</sub> | INPUT                   | <b>CHIP ENABLES:</b> Activates the device's control logic, input buffers, decoders, and sense amplifiers. When the device is de-selected (see Table 2, <i>Chip Enable Truth Table</i> ), power reduces to standby levels.                                                                                                                                                                                                      |  |  |  |  |  |

|                                                           |                         | All timing specifications are the same for these three signals. Device selection occurs with the first edge of $CE_0$ , $CE_1$ , or $CE_2$ that enables the device. Device deselection occurs with the first edge of $CE_0$ , $CE_1$ , or $CE_2$ that disables the device (see Table 2, <i>Chip Enable Truth Table</i> ).                                                                                                      |  |  |  |  |  |

| RP#                                                       | INPUT                   | RESET/ POWER-DOWN: Resets internal automation and puts the device in power-down mode. RP#-high enables normal operation. Exit from reset sets the device to read array mode. When driven low, RP# inhibits write operations which provides data protection during power transitions.                                                                                                                                           |  |  |  |  |  |

|                                                           |                         | RP# at V <sub>HH</sub> enables master lock-bit setting and block lock-bits configuration when the master lock-bit is set. RP# = V <sub>HH</sub> overrides block lock-bits thereby enabling block erase and programming operations to locked memory blocks. Do not permanently connect RP# to V <sub>HH</sub> .                                                                                                                 |  |  |  |  |  |

| OE#                                                       | INPUT                   | <b>OUTPUT ENABLE:</b> Activates the device's outputs through the data buffers during a read cycle. OE# is active low.                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| WE#                                                       | INPUT                   | WRITE ENABLE: Controls writes to the Command User Interface, the Write Buffer, and array blocks. WE# is active low. Addresses and data are latched on the rising edge of the WE# pulse.                                                                                                                                                                                                                                        |  |  |  |  |  |

| STS                                                       | OPEN<br>DRAIN<br>OUTPUT | <b>STATUS:</b> Indicates the status of the internal state machine. When configured in level mode (default mode), it acts as a RY/BY# pin. When configured in one of its pulse modes, it can pulse to indicate program and/or erase completion. For alternate configurations of the STATUS pin, see the Configurations command. Tie STS to V <sub>CCQ</sub> with a pull-up resistor.                                            |  |  |  |  |  |

Table 1. Lead Descriptions (Continued)

| Symbol           | Туре                       | Name and Function                                                                                                                                                                                                                                                                                                                                |

|------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BYTE#            | INPUT                      | <b>BYTE ENABLE:</b> BYTE# low places the device in x8 mode. All data is then input or output on DQ $_0$ –DQ $_7$ , while DQ $_8$ –DQ $_{15}$ float. Address A $_0$ selects between the high and low byte. BYTE# high places the device in x16 mode, and turns off the A $_0$ input buffer. Address A $_1$ then becomes the lowest order address. |

| V <sub>PEN</sub> | INPUT                      | <b>ERASE / PROGRAM / BLOCK LOCK ENABLE:</b> For erasing array blocks, programming data, or configuring lock-bits.                                                                                                                                                                                                                                |

|                  |                            | With $V_{PEN} \le V_{PENLK}$ , memory contents cannot be altered.                                                                                                                                                                                                                                                                                |

| V <sub>CC</sub>  | SUPPLY                     | <b>DEVICE POWER SUPPLY:</b> With $V_{CC} \le V_{LKO}$ , all write attempts to the flash memory are inhibited.                                                                                                                                                                                                                                    |

| Vccq             | OUTPUT<br>BUFFER<br>SUPPLY | <b>OUTPUT BUFFER POWER SUPPLY:</b> This voltage controls the device's output voltages. To obtain output voltages compatible with system data bus voltages, connect V <sub>CCQ</sub> to the system supply voltage.                                                                                                                                |

| GND              | SUPPLY                     | GROUND: Do not float any ground pins.                                                                                                                                                                                                                                                                                                            |

| NC               |                            | NO CONNECT: Lead is not internally connected; it may be driven or floated.                                                                                                                                                                                                                                                                       |

- Figures are not drawn to scale.

Figure 2. µBGA\* Package (64 Mbit and 32 Mbit)

Figure 3. TSOP Lead Configuration (32 Mbit)

Figure 4. SSOP Lead Configuration (64 Mbit and 32 Mbit)

#### 2.0 PRINCIPLES OF OPERATION

The Intel StrataFlash memory devices include an on-chip WSM to manage block erase, program, and lock-bit configuration functions. It allows for 100% TTL-level control inputs, fixed power supplies during block erasure, program, lock-bit configuration, and minimal processor overhead with RAM-like interface timings.

After initial device power-up or return from reset/power-down mode (see Bus Operations), the device defaults to read array mode. Manipulation of external memory control pins allows array read, standby, and output disable operations.

Read array, status register, query, and identifier codes can be accessed through the CUI (Command User Interface) independent of the  $V_{\text{PEN}}$  voltage.

V<sub>PENH</sub> on V<sub>PEN</sub> enables successful block erasure, programming, and lock-bit configuration. All functions associated with altering memory contents—block erase, program, lock-bit configuration—are accessed via the CUI and verified through the status register.

Commands are written using standard microprocessor write timings. The CUI contents serve as input to the WSM, which controls the block erase, program, and lock-bit configuration. The internal algorithms are regulated by the WSM, including pulse repetition, internal verification, and margining of data. Addresses and data are internally latched during program cycles.

Interface software that initiates and polls progress of block erase, program, and lock-bit configuration can be stored in any block. This code is copied to and executed from system RAM during flash memory updates. After successful completion, reads are again possible via the Read Array command. Block erase suspend allows system software to suspend a block erase to read or program data from/to any other block.

### 2.1 Data Protection

Depending on the application, the system designer may choose to make the  $V_{PEN}$  switchable (available only when memory block erases, programs, or lockbit configurations are required) or hardwired to  $V_{PENH}$ . The device accommodates either design practice and encourages optimization of the processor-memory interface.

When  $V_{PEN} \leq V_{PENLK}$ , memory contents cannot be altered. The CUI's two-step block erase, byte/word program, and lock-bit configuration command sequences provide protection from unwanted operations even when  $V_{PENH}$  is applied to  $V_{PEN}$ . All program functions are disabled when  $V_{CC}$  is below the write lockout voltage  $V_{LKO}$  or when RP# is  $V_{IL}$ . The device's block locking capability provides additional protection from inadvertent code or data alteration by gating erase and program operations.

#### 3.0 BUS OPERATION

The local CPU reads and writes flash memory in-system. All bus cycles to or from the flash memory conform to standard microprocessor bus cycles.

Figure 5. Memory Map

| Tahle 2 | Chin | Fnable | Truth | Table(1,2) |

|---------|------|--------|-------|------------|

| CE <sub>2</sub> | CE <sub>1</sub> | CE <sub>0</sub> | DEVICE   |

|-----------------|-----------------|-----------------|----------|

| V <sub>IL</sub> | $V_{IL}$        | $V_{IL}$        | Enabled  |

| V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Disabled |

| V <sub>IL</sub> | V <sub>IH</sub> | $V_{IL}$        | Disabled |

| V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Disabled |

| V <sub>IH</sub> | V <sub>IL</sub> | $V_{IL}$        | Enabled  |

| V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Enabled  |

| V <sub>IH</sub> | V <sub>IH</sub> | $V_{IL}$        | Enabled  |

| VIH             | VIH             | ViH             | Disabled |

#### NOTE:

- See Application Note AP-647 Intel StrataFlash™

Memory Design Guide for typical CE configurations.

- For single-chip applications CE<sub>2</sub> and CE<sub>1</sub> can be strapped to GND.

#### 3.1 Read

Information can be read from any block, query, identifier codes, or status register independent of the V<sub>PEN</sub> voltage. RP# can be at either V<sub>IH</sub> or V<sub>HH</sub>.

Upon initial device power-up or after exit from reset/power-down mode, the device automatically resets to read array mode. Otherwise, write the appropriate read mode command (Read Array, Read Query, Read Identifier Codes, or Read Status Register) to the CUI. Six control pins dictate the data flow in and out of the component: CE0, CE1, CE2, OE#, WE#, and RP#. The device must be enabled (see Table 2, Chip Enable Truth Table), and OE# must be driven active to obtain data at the outputs. CE<sub>0</sub>, CE<sub>1</sub>, and CE<sub>2</sub> are the device selection controls and, when enabled (see Table 2, Chip Enable Truth Table), select the memory device. OE# is the data output (DQ0-DQ15) control and, when active, drives the selected memory data onto the I/O bus. WE# must be at VIH.

## 3.2 Output Disable

With OE# at a logic-high level ( $V_{IH}$ ), the device outputs are disabled. Output pins DQ<sub>0</sub>–DQ<sub>15</sub> are placed in a high-impedance state.

## 3.3 Standby

CE<sub>0</sub>, CE<sub>1</sub>, and CE<sub>2</sub> can disable the device (see Table 2, *Chip Enable Truth Table*) and place it in standby mode which substantially reduces device power consumption.  $DQ_0$ – $DQ_{15}$  outputs are placed in a high-impedance state independent of OE#. If deselected during block erase, program, or lock-bit configuration, the WSM continues functioning, and consuming active power until the operation completes.

#### 3.4 Reset/Power-Down

RP# at V<sub>IL</sub> initiates the reset/power-down mode.

In read modes, RP#-low deselects the memory, places output drivers in a high-impedance state, and turns off numerous internal circuits. RP# must be held low for a minimum of  $t_{PLPH}$ . Time  $t_{PHQV}$  is required after return from reset mode until initial memory access outputs are valid. After this wake-up interval, normal operation is restored. The CUI is reset to read array mode and status register is set to 80H.

During block erase, program, or lock-bit configuration modes, RP#-low will abort the operation. In default mode, STS transitions low and remains low for a maximum time of  $t_{\rm PLPH}$  +  $t_{\rm PHRH}$  until the reset operation is complete. Memory contents being altered are no longer valid; the data may be partially corrupted after a program or partially altered after an erase or lock-bit configuration. Time  $t_{\rm PHWL}$  is required after RP# goes to logic-high (V\_IH) before another command can be written.

As with any automated device, it is important to assert RP# during system reset. When the system comes out of reset, it expects to read from the flash memory. Automated flash memories provide status information when accessed during block erase, program, or lock-bit configuration modes. If a CPU reset occurs with no flash memory reset, proper initialization may not occur because the flash memory may be providing status information instead of array data. Intel's flash memories allow proper initialization following a system reset through the use of the RP# input. In this application, RP# is controlled by the same RESET# signal that resets the system CPU.

## 3.5 Read Query

The read query operation outputs block status information, CFI (Common Flash Interface) ID string, system interface information, device geometry information, and Intel-specific extended query information.

#### 3.6 Read Identifier Codes

The read identifier codes operation outputs the manufacturer code, device code, block lock configuration codes for each block, and the master lock configuration code (see Figure 6). Using the manufacturer and device codes, the system CPU can automatically match the device with its proper algorithms. The block lock and master lock configuration codes identify locked and unlocked blocks and master lock-bit setting.

## 3.7 Write

Writing commands to the CUI enables reading of device data, query, identifier codes, inspection and clearing of the status register, and, when  $V_{\text{PEN}} = V_{\text{PENH}}$ , block erasure, program, and lock-bit configuration.

The Block Erase command requires appropriate command data and an address within the block to be erased. The Byte/Word Program command requires the command and address of the location to be written. Set Master and Block Lock-Bit commands require the command and address within the device (Master Lock) or block within the device (Block Lock) to be locked. The Clear Block Lock-Bits command requires the command and address within the device.

The CUI does not occupy an addressable memory location. It is written when the device is enabled and WE# is active. The address and data needed to execute a command are latched on the rising edge of WE# or the first edge of CE0, CE1, or CE2 that disables the device (see Table 2, Chip Enable Truth Table). Standard microprocessor write timings are used.

#### 4.0 COMMAND DEFINITIONS

When the  $V_{PEN}$  voltage  $\leq V_{PENLK}$ , only read operations from the status register, query, identifier codes, or blocks are enabled. Placing  $V_{PENH}$  on

V<sub>PEN</sub> additionally enables block erase, program, and lock-bit configuration operations.

Device operations are selected by writing specific commands into the CUI. Table 4 defines these commands.

$A_0$  is not used in either x8 or x16 modes when obtaining these identifier codes. Data is always given on the low byte in x16 mode (upper byte contains 00h).

Figure 6. Device Identifier Code Memory Map

**Table 3. Bus Operations**

| Mode                        | Notes | RP#                                   | CE <sub>0,1,2</sub> (10) | OE#(11)         | WE#(11)         | Address         | V <sub>PEN</sub>  | DQ(8)                                                     | STS<br>(default<br>mode) |

|-----------------------------|-------|---------------------------------------|--------------------------|-----------------|-----------------|-----------------|-------------------|-----------------------------------------------------------|--------------------------|

| Read Array                  | 1,2,3 | V <sub>IH</sub> or<br>V <sub>HH</sub> | Enabled                  | V <sub>IL</sub> | V <sub>IH</sub> | X               | Х                 | D <sub>OUT</sub>                                          | High Z <sup>(9)</sup>    |

| Output<br>Disable           |       | V <sub>IH</sub> or<br>V <sub>HH</sub> | Enabled                  | V <sub>IH</sub> | V <sub>IH</sub> | X               | X                 | High Z                                                    | X                        |

| Standby                     |       | V <sub>IH</sub> or<br>V <sub>HH</sub> | Disabled                 | Х               | Х               | Х               | Х                 | High Z                                                    | Х                        |

| Reset/Power-<br>Down Mode   |       | V <sub>IL</sub>                       | Х                        | Х               | Х               | Х               | Х                 | High Z                                                    | High Z <sup>(9)</sup>    |

| Read<br>Identifier<br>Codes |       | V <sub>IH</sub> or<br>V <sub>HH</sub> | Enabled                  | V <sub>IL</sub> | V <sub>IH</sub> | See<br>Figure 6 | Х                 | Note 4                                                    | High Z <sup>(9)</sup>    |

| Read Query                  |       | V <sub>IH</sub> or<br>V <sub>HH</sub> | Enabled                  | V <sub>IL</sub> | V <sub>IH</sub> | See<br>Table 7  | Х                 | Note 5                                                    | High Z <sup>(9)</sup>    |

| Read Status<br>(WSM off)    |       | V <sub>IH</sub> or<br>V <sub>HH</sub> | Enabled                  | V <sub>IL</sub> | V <sub>IH</sub> | Х               | Х                 | D <sub>OUT</sub>                                          |                          |

| Read Status<br>(WSM on)     |       | V <sub>IH</sub> or<br>V <sub>HH</sub> | Enabled                  | V <sub>IL</sub> | V <sub>IH</sub> | Х               | V <sub>PENH</sub> | $DQ_7 = D_{OUT}$ $DQ_{15-8} = High Z$ $DQ_{6-0} = High Z$ |                          |

| Write                       | 3,6,7 | V <sub>IH</sub> or<br>V <sub>HH</sub> | Enabled                  | V <sub>IH</sub> | V <sub>IL</sub> | X               | Х                 | D <sub>IN</sub>                                           | X                        |

### NOTES:

- 1. Refer to *DC Characteristics*. When  $V_{PEN} \le V_{PENLK}$ , memory contents can be read, but not altered.

- X can be V<sub>IL</sub> or V<sub>IH</sub> for control and address pins, and V<sub>PENLK</sub> or V<sub>PENH</sub> for V<sub>PEN</sub>. See *DC Characteristics* for V<sub>PENLK</sub> and V<sub>PENH</sub> voltages.

- In default mode, STS is V<sub>OL</sub> when the WSM is executing internal block erase, program, or lock-bit configuration algorithms.

It is V<sub>OH</sub> when the WSM is not busy, in block erase suspend mode (with programming inactive), or reset/power-down mode.

- 4. See Read Identifier Codes Command section for read identifier code data.

- 5. See Read Query Mode Command section for read query data.

- 6. Command writes involving block erase, program, or lock-bit configuration are reliably executed when V<sub>EN</sub> = V<sub>PENH</sub> and V<sub>CC</sub> is within specification. Block erase, program, or lock-bit configuration with V<sub>IH</sub> < RP# < V<sub>HH</sub> produce spurious results and should not be attempted.

- 7. Refer to Table 4 for valid D<sub>IN</sub> during a write operation.

- 8. DQ refers to DQ0–DQ7 if BYTE# is low and DQ0–DQ15 if BYTE# is high.

- 9. High Z will be  $V_{OH}$  with an external pull-up resistor.

- 10. See Table 2 for valid CE configurations.

- 11. OE# and WE# should never be enabled simultaneously.

Table 4. Intel StrataFlash™ Memory Command Set Definitions(14)

| Command                   | Scaleable<br>or Basic<br>Command<br>Set <sup>(15)</sup> | Bus<br>Cycles<br>Req'd. | Notes | First Bus Cycle |         |                  | Seco    | ond Bus ( | Cycle     |

|---------------------------|---------------------------------------------------------|-------------------------|-------|-----------------|---------|------------------|---------|-----------|-----------|

|                           |                                                         |                         |       | Oper(1)         | Addr(2) | Data(3,4)        | Oper(1) | Addr(2)   | Data(3,4) |

| Read Array                | SCS/BCS                                                 | 1                       |       | Write           | Х       | FFH              |         |           |           |

| Read Identifier<br>Codes  | SCS/BCS                                                 | ≥2                      | 5     | Write           | X       | 90H              | Read    | IA        | ID        |

| Read Query                | SCS                                                     | ≥ 2                     |       | Write           | X       | 98H              | Read    | QA        | QD        |

| Read Status<br>Register   | SCS/BCS                                                 | 2                       | 6     | Write           | Х       | 70H              | Read    | Х         | SRD       |

| Clear Status<br>Register  | SCS/BCS                                                 | 1                       |       | Write           | Х       | 50H              |         |           |           |

| Write to Buffer           | SCS/BCS                                                 | > 2                     | 7,8,9 | Write           | ВА      | E8H              | Write   | ВА        | Ν         |

| Word/Byte<br>Program      | SCS/BCS                                                 | 2                       | 10,11 | Write           | Х       | 40H<br>or<br>10H | Write   | PA        | PD        |

| Block Erase               | SCS/BCS                                                 | 2                       | 9,10  | Write           | Χ       | 20H              | Write   | ВА        | D0H       |

| Block Erase<br>Suspend    | SCS/BCS                                                 | 1                       | 9,10  | Write           | Х       | ВОН              |         |           |           |

| Block Erase<br>Resume     | SCS/BCS                                                 | 1                       | 10    | Write           | Х       | D0H              |         |           |           |

| Configuration             | SCS                                                     | 2                       |       | Write           | Х       | B8H              | Write   | Х         | CC        |

| Set Block Lock-Bit        | SCS                                                     | 2                       | 12    | Write           | Х       | 60H              | Write   | ВА        | 01H       |

| Clear Block Lock-<br>Bits | SCS                                                     | 2                       | 13    | Write           | Х       | 60H              | Write   | Х         | D0H       |

| Set Master Lock-<br>Bit   |                                                         | 2                       | 12,13 | Write           | X       | 60H              | Write   | Х         | F1H       |

# intط ا

## INTEL StrataFlash™ MEMORY TECHNOLOGY, 32 AND 64 MBIT

#### NOTES:

- 1. Bus operations are defined in Table 3.

- 2. X = Any valid address within the device.

- BA = Address within the block.

- IA = Identifier Code Address: see Figure 6 and Table 13.

- QA = Query database Address.

- PA = Address of memory location to be programmed.

- 3. ID = Data read from Identifier Codes.

- QD = Data read from Query database.

- SRD = Data read from status register. See Table 16 for a description of the status register bits.

- PD = Data to be programmed at location PA. Data is latched on the rising edge of WE#.

- CC = Configuration Code.

- 4. The upper byte of the data bus (DQ<sub>8</sub>-DQ<sub>15</sub>) during command writes is a "Don't Care" in x16 operation.

- Following the Read Identifier Codes command, read operations access manufacturer, device, block lock, and master lock codes. See Read Identifier Codes Command section for read identifier code data.

- 6. If the WSM is running, only DQ<sub>7</sub> is valid; DQ<sub>15</sub>–DQ<sub>8</sub> and DQ<sub>6</sub>–DQ<sub>0</sub> float, which places them in a high-impedance state.

- 7. After the Write to Buffer command is issued check the XSR to make sure a buffer is available for writing.

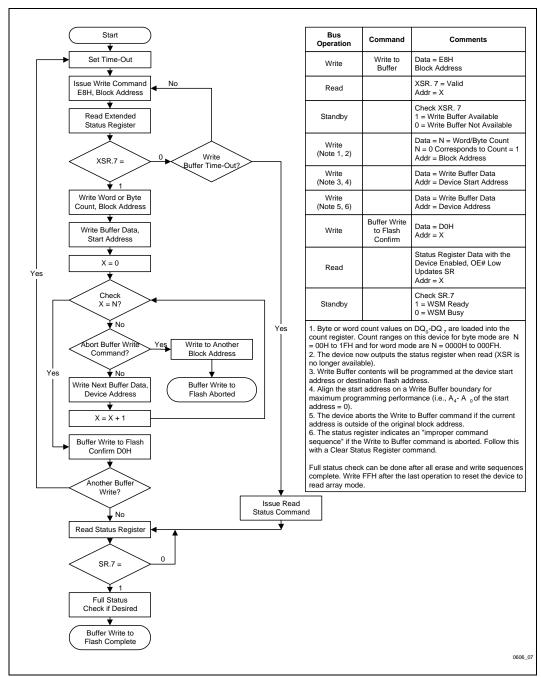

- 8. The number of bytes/words to be written to the Write Buffer = N + 1, where N = byte/word count argument. Count ranges on this device for byte mode are N = 00H to N = 1FH and for word mode are N = 0000FH. The third and consecutive bus cycles, as determined by N, are for writing data into the Write Buffer. The Confirm command (D0H) is expected after exactly N + 1 write cycles; any other command at that point in the sequence aborts the write to buffer operation. Please see Figure 7, Write to Buffer Flowchart, for additional information.

- 9. The write buffer or erase operation does not begin until a Confirm command (D0h) is issued.

- 10. If the block is locked, RP# must be at V<sub>HH</sub> to enable block erase or program operations. Attempts to issue a block erase or program to a locked block while RP# is V<sub>IH</sub> will fail.

- 11. Either 40H or 10H are recognized by the WSM as the byte/word program setup.

- 12. If the master lock-bit is set, RP# must be at V<sub>HH</sub> to set a block lock-bit. RP# must be at V<sub>HH</sub> to set the master lock-bit. If the master lock-bit is not set, a block lock-bit can be set while RP# is V<sub>IH</sub>.

- 13. If the master lock-bit is set, RP# must be at V<sub>HH</sub> to clear block lock-bits. The clear block lock-bits operation simultaneously clears all block lock-bits. If the master lock-bit is not set, the Clear Block Lock-Bits command can be done while RP# is V<sub>H</sub>.

- 14. Commands other than those shown above are reserved by Intel for future device implementations and should not be used.

- 15. The Basic Command Set (BCS) is the same as the 28F008SA Command Set or Intel Standard Command Set. The Scaleable Command Set (SCS) is also referred to as the Intel Extended Command Set.

## 4.1 Read Array Command

Upon initial device power-up and after exit from reset/power-down mode, the device defaults to read array mode. This operation is also initiated by writing the Read Array command. The device remains enabled for reads until another command is written. Once the internal WSM has started a block erase, program, or lock-bit configuration, the device will not recognize the Read Array command until the WSM completes its operation unless the WSM is suspended via an Erase Suspend command. The Read Array command functions independently of the  $V_{\mbox{\scriptsize PEN}}$  voltage and RP# can be  $V_{\mbox{\scriptsize IH}}$  or  $V_{\mbox{\scriptsize HH}}$ .

## 4.2 Read Query Mode Command

This section defines the data structure or "database" returned by the SCS (Scaleable Command Set) Query command. System software should parse this structure to gain critical information to enable programming, block erases, and otherwise control the flash component. The SCS Query is part of an overall specification for multiple command set and control interface descriptions called Common Flash Interface, or CFI. The Query can only be accessed when the WSM is off or the device is suspended.

#### 4.2.1 QUERY STRUCTURE OUTPUT

The Query "database," described later, allows system software to gain critical information for controlling the flash component. This section describes the device's CFI-compliant interface that allows the host system to access Query data.

Query data are always presented on the lowestorder data outputs DQ<sub>0</sub>–DQ<sub>7</sub> only. The Query table device starting address is a 10h word address.

The first two bytes of the Query structure, "Q" and "R" in ASCII, appear on the low byte at word addresses 10h and 11h. This CFI-compliant device outputs 00H data on upper bytes. Thus, the device outputs ASCII "Q" in the low byte DQ0-DQ7 and 00h in the high byte DQ8-DQ15.

Since the device is x8/x16 capable, the x8 data is still presented in word-relative (16-bit) addresses. However, the "fill data" (00h) is not the same as driven by the upper bytes in the x16 mode. As in x16 mode, the byte address ( $A_0$  or  $A_1$  depending on pinout) is ignored for Query output so that the "odd byte address" ( $A_0$  or  $A_1$  high) repeats the "even byte address" data ( $A_0$  or  $A_1$  low). Therefore, in x8 mode using byte addressing, the device will output the sequence "Q," "Q," "R," "R," "Y," "Y," and so on, beginning at byte-relative address 20h (which is equivalent to word offset 10h in x16 mode).

In Query addresses where two or more bytes of information are located, the least significant data byte is presented on the lower address, and the most significant data byte is presented on the higher address.

Table 5. Summary of Query Structure Output as a Function of Device and Mode

| Device<br>type/<br>mode | Query start<br>location<br>in maximum<br>device<br>bus width<br>addresses | Query data with<br>maximum device<br>bus width addressing<br>"x" = ASCII equivalent | Query<br>start<br>address<br>in bytes | Query data with<br>byte addressing            |

|-------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------|

| x16 device/<br>x16 mode | 10h                                                                       | 10h: 0051h "Q"<br>11h: 0052h "R"<br>12h: 0059h "Y"                                  | 20h                                   | 20h: 51h "Q"<br>21h: 00h null<br>22h: 52h "R" |

| x16 device/<br>x8 mode  | N/A <sup>(1)</sup>                                                        | N/A <sup>(1)</sup>                                                                  | 20h                                   | 20h: 51h "Q"<br>21h: 51h "Q"<br>22h: 52h "R"  |

## NOTE:

Table 6. Example of Query Structure Output of a x16- and x8-Capable Device

| Device<br>Address               | Word Addressing:<br>Query Data  | Byte<br>Address                | Byte Addressing:<br>Query Data |

|---------------------------------|---------------------------------|--------------------------------|--------------------------------|

| A <sub>16</sub> -A <sub>1</sub> | D <sub>15</sub> -D <sub>0</sub> | A <sub>7</sub> -A <sub>0</sub> | D <sub>7</sub> –D <sub>0</sub> |

| 0010h                           | 0051h "Q"                       | 20h                            | 51h "Q"                        |

| 0011h                           | 0052h "R"                       | 21h                            | 51h "Q"                        |

| 0012h                           | 0059h "Y"                       | 22h                            | 52h "R"                        |

| 0013h                           | P_ID <sub>LO</sub> PrVendor     | 23h                            | 52h "R"                        |

| 0014h                           | P_ID <sub>HI</sub> ID #         | 24h                            | 59h "Y"                        |

| 0015h                           | P <sub>LO</sub> PrVendor        | 25h                            | 59h "Y"                        |

| 0016h                           | P <sub>HI</sub> TblAdr          | 26h                            | P_ID <sub>LO</sub> PrVendor    |

| 0017h                           | A_ID <sub>LO</sub> AltVendor    | 27h                            | P_ID <sub>LO</sub> ID #        |

| 0018h                           | A_ID <sub>HI</sub> ID #         | 28h                            | P_ID <sub>HI</sub> "           |

|                                 |                                 |                                |                                |

The system must drive the lowest order addresses to access all the device's array data when the device is configured in x8

mode. Therefore, word addressing where these lower addresses not toggled by the system is "Not Applicable" for x8configured devices.

#### 4.2.2 QUERY STRUCTURE OVERVIEW

The Query command causes the flash component to display the Common Flash Interface (CFI) Query structure or "database." The structure sub-sections and address locations are summarized below. See *AP-646 Common Flash Interface (CFI) and Command Sets* (order number 292204) for a full description of CFI.

The following sections describe the Query structure sub-sections in detail.

**Table 7. Query Structure**

| Offset       | Sub-Section Name                                                        | Description                                                                       |

|--------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 00h          |                                                                         | Manufacturer Code                                                                 |

| 01h          |                                                                         | Device Code                                                                       |

| (BA+2)h(2)   | (BA+2)h <sup>(2)</sup> Block Status Register Block-Specific Information |                                                                                   |

| 04–0Fh       | Reserved                                                                | Reserved for Vendor-Specific Information                                          |

| 10h          | CFI Query Identification String                                         | Command Set ID and Vendor Data Offset                                             |

| 1Bh          | System Interface Information                                            | Device Timing and Voltage Information                                             |

| 27h          | Device Geometry Definition                                              | Flash Device Layout                                                               |

| <b>P</b> (3) | Primary Vendor-Specific Extended Query table                            | Vendor-Defined Additional Information<br>Specific to the Primary Vendor Algorithm |

#### NOTES:

- Refer to Query Data Output section of Device Hardware interface for the detailed definition of offset address as a function of device word width and mode.

- 2. BA = The beginning location of a Block Address (i.e., 2000h is the beginning location of block 2 when the block size is 128 KB).

- 3. The Primary Vendor-Specific Extended Query table (P) address may change among SCS-compliant devices. Software should retrieve this address from address 15 to guarantee compatibility with future SCS-compliant devices.

## 4.2.3 BLOCK STATUS REGISTER

The Block Status Register indicates whether a given block is locked and can be accessed for program/erase operations. On SCS devices that do not implement block locking, BSR.0 will indicate functional block status on partially functional devices. The Block Status Register is accessed from word address 02h within each block.

**Table 8. Block Status Register**

| Offset    | Length<br>(bytes) | Description                                                                                                                                         | Intel StrataFlash™<br>Memory<br>x16 device/mode          |

|-----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| (BA +2)h1 | 01h               | Block Status Register                                                                                                                               | BA+2: 0000h or<br>0001h                                  |

|           |                   | BSR.0 = Block Lock or Non-Functional Status                                                                                                         | BA+2 (bit 0): 0 or 1                                     |

|           |                   | (Optional) 1 = Locked or Non-Functional<br>0 = Unlocked                                                                                             |                                                          |

|           |                   | BSR.1 = Block Erase or Non-Functional Status <sup>(2)</sup> (Optional)                                                                              | BA+2 (bit 1): 0<br>(The device does<br>not support Block |

|           |                   | 1 = Last erase operation did     not complete successfully or Non- Functional     0 = Last erase operation     completed successfully or Functional | Erase Status)                                            |

|           |                   | BSR 2–7 Reserved for future use                                                                                                                     | BA+2 (bits 2-7): 0                                       |

## NOTES:

- 1. BA = The beginning location of a Block Address (i.e., 2000h is the beginning location of block 2).

- 2. Block Erase Status is an optional part of the SCS definition and is not incorporated on this device.

## 4.2.4 CFI QUERY IDENTIFICATION STRING

The Identification String provides verification that the component supports the Common Flash Interface specification. Additionally, it indicates which version of the spec and which vendor-specified command set(s) is(are) supported.

**Table 9. CFI Identification**

| Offset | Length<br>(bytes) | Description                                                                                                                          | Intel StrataFlash™<br>Memory |                         |

|--------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------|

| 10h    | 03h               | Query-unique ASCII string "QRY"                                                                                                      | 10:<br>11:<br>12:            | 0051h<br>0052h<br>0059h |

| 13h    | 02h               | Primary Vendor Command Set and<br>Control Interface ID Code<br>16-bit ID code for vendor-specified algorithms                        |                              | 0001h<br>0000h          |

| 15h    | 02h               | Address for Primary Algorithm Extended Query table Offset value = <b>P</b> = 31h                                                     |                              | 0031h<br>0000h          |

| 17h    | 02h               | Alternate Vendor Command Set and Control Interface ID Code second vendor-specified algorithm supported Note: 0000h means none exists |                              | 0000h<br>0000h          |

| 19h    | 02h               | Address for Secondary Algorithm Extended Query table Note: 0000h means none exists                                                   | 19:<br>1A:                   | 0000h<br>0000h          |

## 4.2.5 SYSTEM INTERFACE INFORMATION

The following device information can optimize system interface software.

Table 10. System Interface Information

| Offset | Length<br>(bytes) | Description                                                                                     | Intel<br>StrataFlash™<br>Memory |

|--------|-------------------|-------------------------------------------------------------------------------------------------|---------------------------------|

| 1Bh    | 01h               | V <sub>CC</sub> Logic Supply Minimum<br>Program/Erase voltage                                   | 1B: 0045h                       |

|        |                   | bits 7–4 BCD volts<br>bits 3–0 BCD 100 mv                                                       |                                 |

| 1Ch    | 01h               | V <sub>CC</sub> Logic Supply Maximum<br>Program/Erase voltage                                   | 1C: 0055h                       |

|        |                   | bits 7–4 BCD volts<br>bits 3–0 BCD 100 mv                                                       |                                 |

| 1Dh    | 01h               | V <sub>PP</sub> [Programming] Supply<br>Minimum Program/Erase voltage                           | 1D: 0000h                       |

|        |                   | bits 7–4 HEX volts<br>bits 3–0 BCD 100 mv                                                       |                                 |

| 1Eh    | 01h               | V <sub>PP</sub> [Programming] Supply<br>Maximum Program/Erase voltage                           | 1E: 0000h                       |

|        |                   | bits 7–4 HEX volts<br>bits 3–0 BCD 100 mv                                                       |                                 |

| 1Fh    | 01h               | Typical time-out per single byte/word program, 2 <sup>N</sup> µs                                | 1F: 0007h                       |

| 20h    | 01h               | Typical time-out for max. buffer write, 2 <sup>N</sup> µs                                       | 20: 0007h                       |

| 21h    | 01h               | Typical time-out per individual block erase, 2 <sup>N</sup> ms                                  | 21: 000Ah                       |

| 22h    | 01h               | Typical time-out for full chip erase, 2 <sup>N</sup> ms (0000h = not supported)                 | 22: 0000h                       |

| 23h    | 01h               | Maximum time-out for byte/word program, 2 <sup>N</sup> times typical                            | 23: 0004h                       |

| 24h    | 01h               | Maximum time-out for buffer write,<br>2 <sup>N</sup> times typical                              | 24: 0004h                       |

| 25h    | 01h               | Maximum time-out per individual block erase, 2 <sup>N</sup> times typical                       | 25: 0004h                       |

| 26h    | 01h               | Maximum time-out for chip erase,<br>2 <sup>N</sup> times typical ( <b>00h = not supported</b> ) | 26: 0000h                       |

## 4.2.6 DEVICE GEOMETRY DEFINITION

This field provides critical details of the flash device geometry.

**Table 11. Device Geometry Definition**

| Offset | Length<br>(bytes) | Description                                                                                                       | Intel<br>StrataFlash™<br>Memory                                                                   |

|--------|-------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 27h    | 01h               | Device Size = $2^N$ in number of bytes.                                                                           | 27: 0017h<br>(64-Mbit)                                                                            |

|        |                   |                                                                                                                   | 27: 0016h<br>(32-Mbit)                                                                            |

| 28h    | 02h               | Flash Device Interface description  value meaning  0000h x8 asynchronous 0002h x8/x16 asynchronous                | 28: 0002h<br>29: 0000h                                                                            |

| 2Ah    | 02h               | Maximum number of bytes in write buffer = 2 <sup>N</sup>                                                          | 2A: 0005h<br>2B: 0000h                                                                            |

| 2Ch    | 01h               | Number of Erase Block Regions within device:                                                                      | 2C: 0001h                                                                                         |

|        |                   | bits 7-0 = x = # of Erase Block Regions                                                                           |                                                                                                   |

| 2Dh    | 04h               | Erase Block Region Information  bits 15–0 = y, where y+1 = Number of Erase Blocks of identical size within region | y: 64 Blocks<br>(64-Mbit)<br>2D: 003Fh<br>2E: 0000h                                               |

|        |                   | bits 31–16 = z, where the Erase Block(s) within this Region are (z) times 256 bytes                               | y: 32 Blocks<br>(32-Mbit)<br>2D: 001Fh<br>2E: 0000h<br>z: (128 KB size)<br>2F: 0000h<br>30: 0002h |

## 4.2.7 PRIMARY-VENDOR SPECIFIC EXTENDED QUERY TABLE

Certain flash features and commands are optional. The *Primary Vendor-Specific Extended Query* table specifies this and other similar information.

Table 12. Primary Vendor-Specific Extended Query

| Offset(1) | Length<br>(bytes) | Description                                                                                                                                                                                                                                                                                                             | Intel<br>StrataFlash™<br>Memory |                                  |

|-----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------|

| (P)h      | 03h               | Primary extended Query table unique ASCII string "PRI"                                                                                                                                                                                                                                                                  | 31:<br>32:<br>33:               | 0050h<br>0052h<br>0049h          |

| (P +3)h   | 01h               | Major version number, ASCII                                                                                                                                                                                                                                                                                             | 34:                             | 0031                             |

| (P +4)h   | 01h               | Minor version number, ASCII                                                                                                                                                                                                                                                                                             | 35:                             | 0031                             |

| (P +5)h   | 04h               | Optional Feature and Command Support  bit 0 Chip Erase Supported (1=yes, 0=no) bit 1 Suspend Erase Supported (1=yes, 0=no) bit 2 Suspend Program Supported (1=yes, 0=no) bit 3 Lock/Unlock Supported (1=yes, 0=no) bit 4 Queued Erase Supported (1=yes, 0=no) bits 5–31 Reserved for future use; undefined bits are "0" | 36:<br>37:<br>38:<br>39:        | 000Ah<br>0000h<br>0000h<br>0000h |

| (P +9)h   | 01h               | Supported functions after Suspend  Read Array, Status, and Query are always supported during suspended Erase. This field defines other operations supported.  bit 0 Program supported after Erase Suspend (1=yes, 0=no)  bits 1–7 Reserved for future use; undefined bits are "0"                                       | 3A:                             | 0001h                            |

| (P +A)h   | 02h               | Block Status Register Mask  Defines which bits in the Block Status Register section of Query are implemented.  bit 0 Block Status Register Lock Bit [BSR.0] active (1=yes, 0=no)  bit 1 Block Status Register Valid Bit [BSR.1] active (1=yes, 0=no)  bits 2–15 Reserved for future use; undefined bits are "0"         | 3B:<br>3C:                      | 0001h<br>0000h                   |

## NOTE:

<sup>1.</sup> The Primary Vendor-Specific Extended Query table (P) address may change among SCS-compliant devices. Software should retrieve this address from address 15 to guarantee compatibility with future SCS-compliant devices.

Table 12. Primary Vendor-Specific Extended Query (Continued)

| Offset(1) | Length<br>(bytes) | Description                                                                                                                                                                                 | Intel<br>StrataFlash™<br>Memory |       |

|-----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------|

| (P +C)h   | 01h               | V <sub>CC</sub> Optimum Program/Erase voltage (highest performance)  bits 7–4 bits 3–0 BCD value in volts BCD value in 100 millivolts                                                       | 3D:                             | 0050h |

| (P +D)h   | 01h               | V <sub>PP</sub> [Programming] Optimum Program/Erase voltage  bits 7–4 HEX value in volts bits 3–0 BCD value in 100 millivolts  Note: This value is 0000h; no V <sub>PP</sub> pin is present |                                 | 0000h |

| (P +E)h   | reserved          | Reserved for future use                                                                                                                                                                     |                                 |       |

#### NOTE:

# 4.3 Read Identifier Codes Command

The identifier code operation is initiated by writing the Read Identifier Codes command. Following the command write, read cycles from addresses shown in Figure 6 retrieve the manufacturer, device, block lock configuration and master lock configuration codes (see Table 13 for identifier code values). To terminate the operation, write another valid command. Like the Read Array command, the Read Identifier Codes command functions independently of the  $V_{\text{PEN}}$  voltage and RP# can be  $V_{\text{IH}}$  or  $V_{\text{HH}}$ . This command is valid only when the WSM is off or the device is suspended. Following the Read Identifier Codes command, the following information can be read:

Table 13. Identifier Codes(1)

| Cod                              | е            | Address(1) | Data              |

|----------------------------------|--------------|------------|-------------------|

| Manufacture C                    | ode          | 00000      | (00) 89           |

| Device Code                      | 32-Mbit      | 00001      | (00) 14           |

|                                  | 64-Mbit      | 00001      | (00) 15           |

| Block Lock Cor                   | nfiguration  | X0002(2)   |                   |

| Block Is Unlo                    | cked         |            | $DQ_0 = 0$        |

| Block Is Lock                    | ed           |            | $DQ_0 = 1$        |

| <ul> <li>Reserved for</li> </ul> | Future Use   |            | DQ <sub>1-7</sub> |

| Master Lock C                    | onfiguration | 00003      |                   |

| Device Is Uni                    | ocked        |            | $DQ_0 = 0$        |

| Device Is Loc                    | ked          |            | $DQ_0 = 1$        |

| <ul> <li>Reserved for</li> </ul> | Future Use   |            | DQ <sub>1-7</sub> |

#### NOTE:

- 1.  $A_0$  is not used in either x8 or x16 modes when obtaining the identifier codes. The lowest order address line is  $A_1$ . Data is always presented on the low byte in x16 mode (upper byte contains 00h).

- X selects the specific block's lock configuration code.

See Figure 6 for the device identifier code memory map.

The Primary Vendor-Specific Extended Query table (P) address may change among SCS-compliant devices. Software should retrieve this address from address 15 to guarantee compatibility with future SCS-compliant devices.

## 4.4 Read Status Register Command

The status register may be read to determine when a block erase, program, or lock-bit configuration is complete and whether the operation completed successfully. It may be read at any time by writing the Read Status Register command. After writing this command, all subsequent read operations output data from the status register until another valid command is written. The status register contents are latched on the falling edge of OE# or the first edge of CE<sub>0</sub>, CE<sub>1</sub>, or CE<sub>2</sub> that enables the device (see Table 2, Chip Enable Truth Table). OE# must toggle to VIH or the device must be disabled (see Table 2, Chip Enable Truth Table) before further reads to update the status register latch. The Read Status Register command functions independently of the V<sub>PEN</sub> voltage. RP# can be V<sub>IH</sub>

During a program, block erase, set lock-bit, or clear lock-bit command sequence, only SR.7 is valid until the Write State Machine completes or suspends the operation. Device I/O pins  $DQ_0$ – $DQ_6$  and  $DQ_8$ – $DQ_{15}$  are placed in a high-impedance state. When the operation completes or suspends (check Status Register bit 7), all contents of the Status Register are valid when read.

## 4.5 Clear Status Register Command

Status register bits SR.5, SR.4, SR.3, and SR.1 are set to "1"s by the WSM and can only be reset by the Clear Status Register command. These bits indicate various failure conditions (see Table 16). By allowing system software to reset these bits, several operations (such as cumulatively erasing or locking multiple blocks or writing several bytes in sequence) may be performed. The status register may be polled to determine if an error occurred during the sequence.

To clear the status register, the Clear Status Register command (50H) is written. It functions independently of the applied  $V_{\text{PEN}}$  voltage. RP# can be  $V_{\text{IH}}$  or  $V_{\text{HH}}$ . The Clear Status Register Command is only valid when the WSM is off or the device is suspended.

### 4.6 Block Erase Command

Erase is executed one block at a time and initiated by a two-cycle command. A block erase setup is first written, followed by an block erase confirm. This command sequence requires an appropriate address within the block to be erased (erase changes all block data to FFH). Block preconditioning, erase, and verify are handled internally by the WSM (invisible to the system). After the two-cycle block erase sequence is written, the device automatically outputs status register data when read (see Figure 9). The CPU can detect block erase completion by analyzing the output of the STS pin or status register bit SR.7. Toggle OE#, CE<sub>0</sub>, CE<sub>1</sub>, or CE<sub>2</sub> to update the status register.

When the block erase is complete, status register bit SR.5 should be checked. If a block erase error is detected, the status register should be cleared before system software attempts corrective actions. The CUI remains in read status register mode until a new command is issued.