|                             | <del></del>                                                                                         |        |       |      |                  |                      | ,                 |              | REVIS        | SIONS        |       |                          |             | <u> </u>   |       |       |           |                                       |       |    |

|-----------------------------|-----------------------------------------------------------------------------------------------------|--------|-------|------|------------------|----------------------|-------------------|--------------|--------------|--------------|-------|--------------------------|-------------|------------|-------|-------|-----------|---------------------------------------|-------|----|

| LIR                         |                                                                                                     | _      |       |      | I                | DESCI                | RIPTI             | ON           |              |              |       |                          | 1           | DATE       | (YR-M | O-DA) |           | APPF                                  | SOVEI | )  |

|                             |                                                                                                     |        |       |      |                  |                      |                   |              |              |              |       |                          |             |            |       |       |           |                                       |       |    |

| REV                         |                                                                                                     |        |       |      |                  | ļ                    | ļ                 |              |              |              |       |                          |             |            |       |       |           |                                       |       |    |

| SHEET                       |                                                                                                     |        |       |      |                  |                      |                   |              |              |              |       |                          |             |            |       |       |           |                                       |       |    |

| REV                         |                                                                                                     |        |       |      |                  |                      |                   |              |              |              |       |                          |             |            |       |       |           |                                       |       |    |

| SHEET                       | 15                                                                                                  | 16     | 17    | 18   | 19               | 20                   | 21                | 22           | 23           | 24           | 25    | 26                       | 27          | 28         | 29    | 30    | 31        | 32                                    | 33    | 34 |

| REV STAT<br>OF SHEET        |                                                                                                     |        |       | RE   | <u>V</u>         |                      |                   |              |              |              |       |                          |             |            |       |       |           |                                       |       |    |

| Of Stiffe                   |                                                                                                     |        |       | SH   | EET              |                      | 1                 | 2            | 3            | 4            | 5     | 6                        | 7           | 8          | 9     | 10    | 11        | 12                                    | 13    | 14 |

| PMIC N/A                    |                                                                                                     |        |       | PREP | ARED B           | Y Lar                | ry T.             | Gauder       |              | Di           | EFENS | SE EI                    |             |            |       |       |           | TER                                   |       |    |

| MICRO                       | STANDARD CROCIRCUIT CHECKED BY Thomas M. Hess                                                       |        |       |      |                  |                      | 41110             |              |              | 454          | z-z   |                          |             | i          |       |       |           |                                       |       |    |

| THIS DRAWIN<br>FOR USE BY A | DRAWING  APPROVED BY Monica L.  APPROVED BY Monica L.  APPROVED BY Monica L.  APPROVED BY Monica L. |        | Poelk | ing  | ARI              | CROC<br>BITR<br>LICO | IRCU<br>ATIO<br>N | JIT,<br>ON C | DIO<br>ITNO: | GITA<br>ROLL | ER,   | FUTU<br>MON              | REB         | US<br>THIC | :     |       |           |                                       |       |    |

| DEPARTMEN                   | T OF D                                                                                              | EFENSI | E     | DRAW | ING AP           |                      | . DATE<br>3-15    |              |              | CTC          | Б.    | <i>(</i> 2), <i>(</i> 3) | T. 00       | DE .       |       |       |           |                                       |       |    |

| AMSC N/A                    |                                                                                                     |        |       | REVI | SION L           | EVEL                 |                   |              |              | SIZ          | r.    |                          | 726         |            |       |       | 962-95543 |                                       |       |    |

|                             |                                                                                                     |        |       |      |                  |                      |                   |              |              | SHE          | ET    | 1                        |             | (          | OF    |       | 34        | •                                     | -     |    |

| DESC FORM 193               |                                                                                                     |        |       |      | <del>'''''</del> |                      |                   |              |              | -            |       |                          | <del></del> |            |       |       |           | · · · · · · · · · · · · · · · · · · · |       |    |

UL 94

<u>DISTRIBUTION STATEMENT A.</u> Approved for public release; distribution is unlimited.

5962-E109-95

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). Two product assurance classes consisting of military high reliability (device classes Q and M) and space application (device class V), and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). Device class M microcircuits represent non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

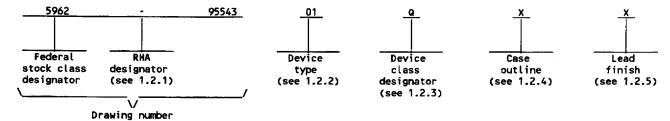

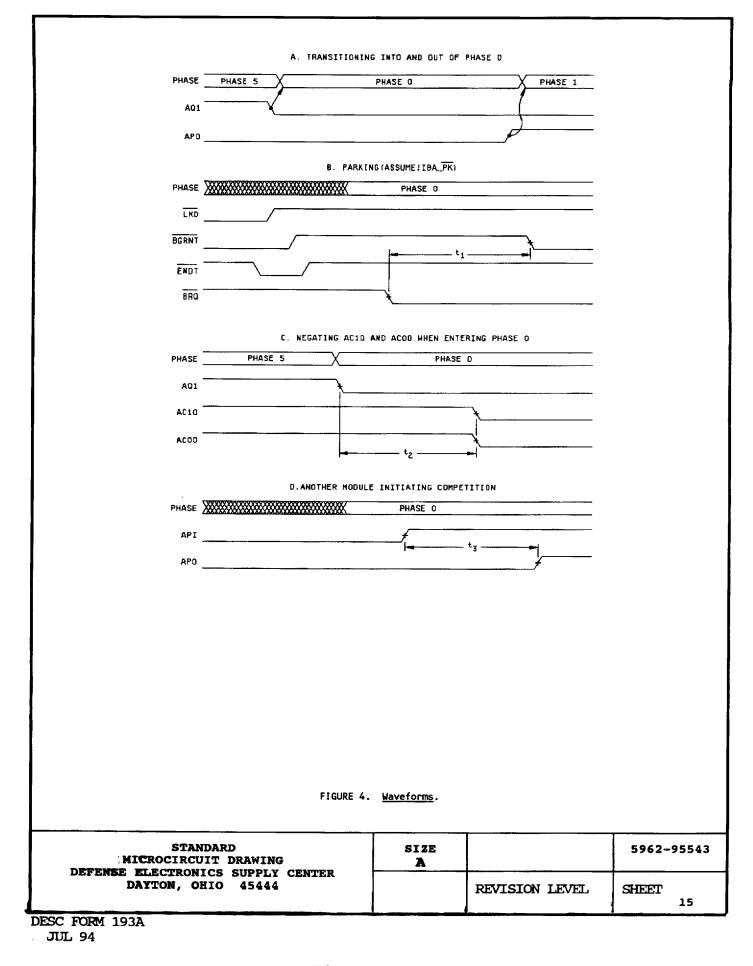

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>RHA designator</u>. Device class M RHA marked devices shall meet the MIL-I-38535 appendix A specified RHA levels and shall be marked with the appropriate RHA designator. Device classes Q and V RHA marked devices shall meet the MIL-I-38535 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>          |

|-------------|----------------|----------------------------------|

| 01          | D\$3875        | futurebus arbitration controller |

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

M

Vendor self-certification to the requirements for non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883

Q or V

Certification and qualification to MIL-I-38535

1.2.4 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | <u>Descriptive designator</u> | <u>Terminals</u> | Package style |

|----------------|-------------------------------|------------------|---------------|

| X              | see figure 1                  | 68               | flat pack     |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-STD-883 (see 3.1 herein) for class M or MIL-I-38535 for classes Q and V. Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                | 5962-95543 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | ,         | REVISION LEVEL | SHEET 2    |

DESC FORM 193A JUL 94

**--** 9004708 0009878 699 **--**

### 1.3 Absolute maximum ratings. 1/ 6.5 V Control input voltage - - - - - - - - - - - - - -5.5 V Storage temperature range (T<sub>STG</sub>) -------65°C to +150°C Maximum power dissipation (PD) 2/-----3.9 ₩ Lead temperature (soldering, 10 seconds) - - - - - - -+260°C Junction temperature (T<sub>J</sub>) +175°C Thermal resistance, junction-to-case ( $\theta_{JC}$ ) - - - - - - Thermal resistance, junction-to-ambient ( $\theta_{JA}$ ) - - - - - -3.4°C/W 38°C/W 1.4 Recommended operating conditions. +4.5 V dc to +5.5 V dc Supply voltage range (VDD) ------Ambient operating temperature range (TA) - - - - - - --55°C to +125°C 1.5 <u>Digital logic testing for device classes Q and V.</u> Fault coverage measurement of manufacturing Logic tests (MIL-STD-883, test method 5012) - - - - -3/ XX percent 2. APPLICABLE DOCUMENTS 2.1 Government specification, standards, bulletin, and handbook. Unless otherwise specified, the following specification, standards, bulletin, and handbook of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein. **SPECIFICATION** MILITARY MIL-1-38535 - Integrated Circuits, Manufacturing, General Specification for. STANDARDS MILITARY MIL-STD-883 - Test Methods and Procedures for Microelectronics. MIL-STD-973 - Configuration Management. MIL-STD-1835 - Microcircuit Case Outlines. BULLETIN MILITARY MIL-BUL-103 - List of Standardized Military Drawings (SMD's). HANDBOOK MILITARY MIL-HDBK-780 - Standardized Military Drawings. (Copies of the specification, standards, bulletin, and handbook required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.) 17 Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at

Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation a the maximum levels may degrade performance and affect reliability.

2/ Derate at 11.5 mW/C above 25°C.

3/ Values will be added when they become available.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                | 5962-95543 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>3 |

DESC FORM 193A JUL 94

📟 9004708 0009879 525 **==**

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device class M shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. The individual item requirements for device classes Q and V shall be in accordance with MIL-I-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not effect the form, fit, or function as described herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-STD-883 (see 3.1 herein) for device class M and MIL-I-38535 for device classes Q and V and herein.

- 3.2.1 <u>Case outline(s)</u>. The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

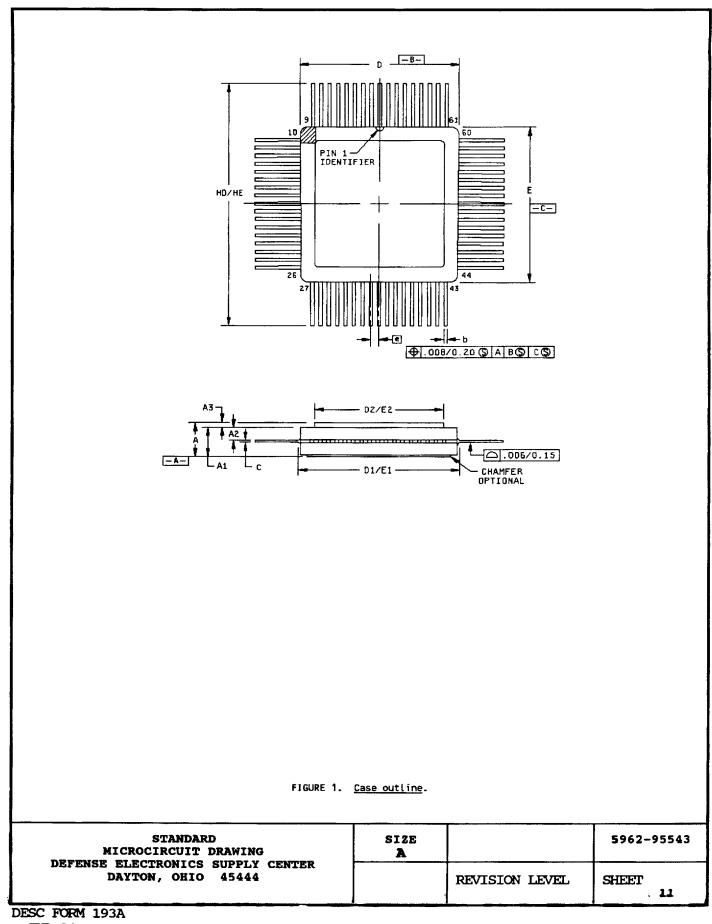

- 3.2.3 Logic diagram. The logic diagram shall be as specified on figure 3.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full ambient operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table 1.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes Q and V shall be in accordance with MIL-I-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-I-38535.

- 3.6 <u>Certificate of compliance</u>. For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7.2 herein). For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.7.1 herein). The certificate of compliance submitted to DESC-EC prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device class M, the requirements of MIL-STD-883 (see 3.1 herein), or for device classes Q and V, the requirements of MIL-I-38535 and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device class M in MIL-STD-883 (see 3.1 herein) or for device classes Q and V in MIL-I-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M</u>. For device class M, notification to DESC-EC of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-973.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 100 (see MIL-1-38535, appendix A).

#### 4. QUALITY ASSURANCE PROVISIONS

4.1 <u>Sampling and inspection</u>. For device class M, sampling and inspection procedures shall be in accordance with MIL-STD-883 (see 3.1 herein). For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-I-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not effect the form, fit, or function as described herein.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                | 5962-95543 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 4    |

DESC FORM 193A JUL 94

9004708 0009880 247

| Test                                                   | Symbol           | -55°C ≤ TA ≤ +125°C                                                             |                            | Group A<br>subgroups | Device<br>type | Limits |      | Unit   |

|--------------------------------------------------------|------------------|---------------------------------------------------------------------------------|----------------------------|----------------------|----------------|--------|------|--------|

|                                                        |                  | V <sub>CC</sub> = 5 <sup>°</sup> V ±10<br>unless otherwise sp                   | 0% <u>1</u> /<br>specified |                      |                | Min    | Max  |        |

| Logical 1 input voltage                                | v <sub>I H</sub> |                                                                                 |                            | 1, 2, 3              | 01             | 2.8    |      | V      |

| Logical O input voltage                                | VIL              |                                                                                 |                            | 1, 2, 3              | 01             |        | 0.75 | ٧      |

| Logical O output voltage                               | V <sub>OL</sub>  | V <sub>CC</sub> = 4.5 V<br>I <sub>OL</sub> = 8 mA                               |                            | 1, 2, 3              | 01             |        | 0.7  | ٧      |

| Logical 1 output voltage                               | v <sub>OH</sub>  | V <sub>CC</sub> = 4.5 V<br>I <sub>OH</sub> = -4 mA                              |                            | 1, 2, 3              | 01             | 2.4    |      | ٧      |

| Input leakage diode current                            | II               | V <sub>CC</sub> = 5.5 V<br>V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub> |                            | 1, 2, 3              | 01             | -3     | 3    | μА     |

| Static supply current                                  | 1 <sub>CC</sub>  | V <sub>CC</sub> = 5.5 V<br>input at standby                                     |                            | 1, 2, 3              | 01             |        | 30   | mA     |

| Dynamic supply current                                 | IDD              | V <sub>CC</sub> = 5.5 V                                                         |                            | 1, 2, 3              | 01             |        | 100  | mA     |

| Functional test                                        |                  | V <sub>CC</sub> = 4.5 V, 5.5 V<br>See 4.4.1b                                    |                            | 7, 8                 |                |        |      |        |

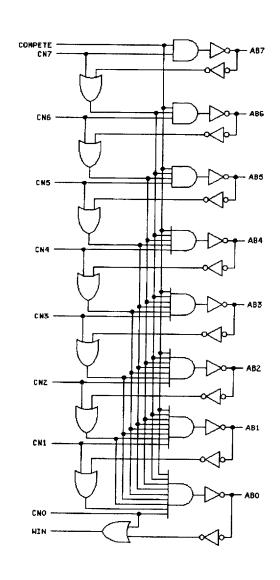

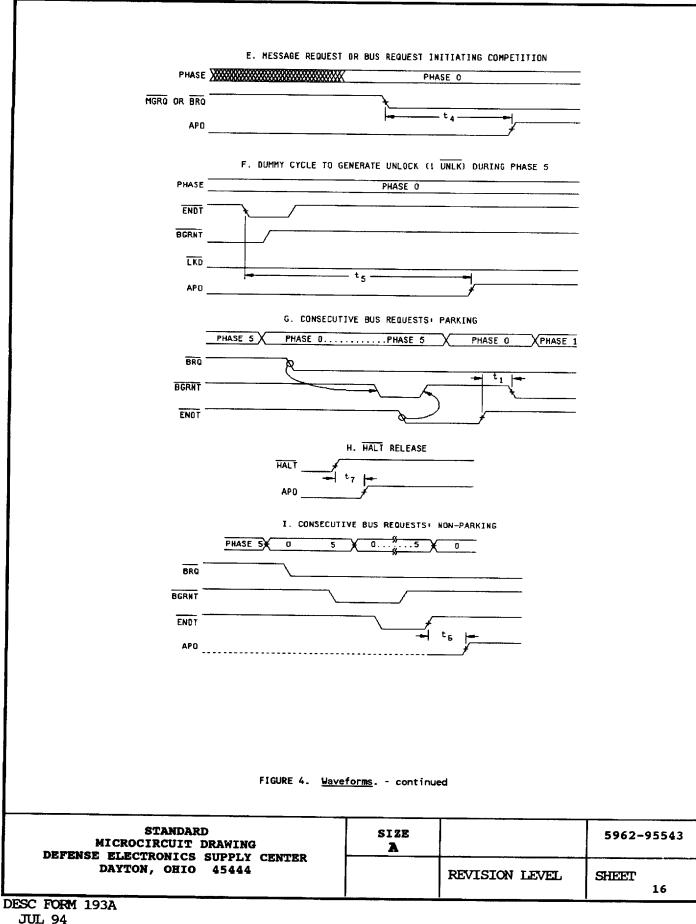

| BRQ <u>asser</u> ted to<br>Bgrant asserted             | t <sub>1</sub>   | V <sub>CC</sub> = 4.5 V<br>See figure 4                                         |                            | 9, 10, 11            | 01             |        | 36   | ns     |

| Aqi negated to<br>AcOo, Aclo                           | t <sub>2</sub>   |                                                                                 |                            | 9, 10, 11            | 01             |        | 30   | ns     |

| Aqi negated to<br>Apo asserted                         | t <sub>3</sub>   |                                                                                 |                            | 9, 10, 11            | 01             |        | 31   | ns     |

| MGRQ or BRQ asserted<br>to Apo asserted                | t4               |                                                                                 |                            | 9, 10, 11            | 01             |        | 38   | ns     |

| ENDT asserted to Apo asserted (dummy cycle)            | t <sub>5</sub>   |                                                                                 |                            | 9, 10, 11            | 01             |        | 46   | ns     |

| BRQ asserted to Apo asserted (consecutive bus request) | <sup>t</sup> 6   |                                                                                 |                            | 9, 10, 11            | 01             |        | 34   | ns     |

|                                                        |                  |                                                                                 |                            |                      |                |        |      |        |

| STAND<br>MICROCIRCUI                                   |                  | ING                                                                             | 2 SIZ                      | 2                    |                |        | 596  | 2-9554 |

| DEFENSE ELECTRONIC DAYTON, OH                          |                  |                                                                                 |                            | RE                   | VISION         | LEVEL  | SHEE | T      |

📟 9004708 0009881 183 **=**

| Test                                                                                   | Symbol           | Conditions<br>-55°C ≤ T <sub>A</sub> ≤ +125°C                       | Group A<br>subgroups | Device<br>type | Limits        |              | Unit |

|----------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------|----------------------|----------------|---------------|--------------|------|

|                                                                                        |                  | V <sub>CC</sub> = 5 V ±10% <u>1</u> /<br>unless otherwise specified |                      |                | Min           | Max          |      |

| Halt negated to Apo asserted                                                           | t <sub>7</sub>   | V <sub>CC</sub> = 4.5 V<br>See figure 4                             | 9, 10, 11            | 01             |               | 28           | ns   |

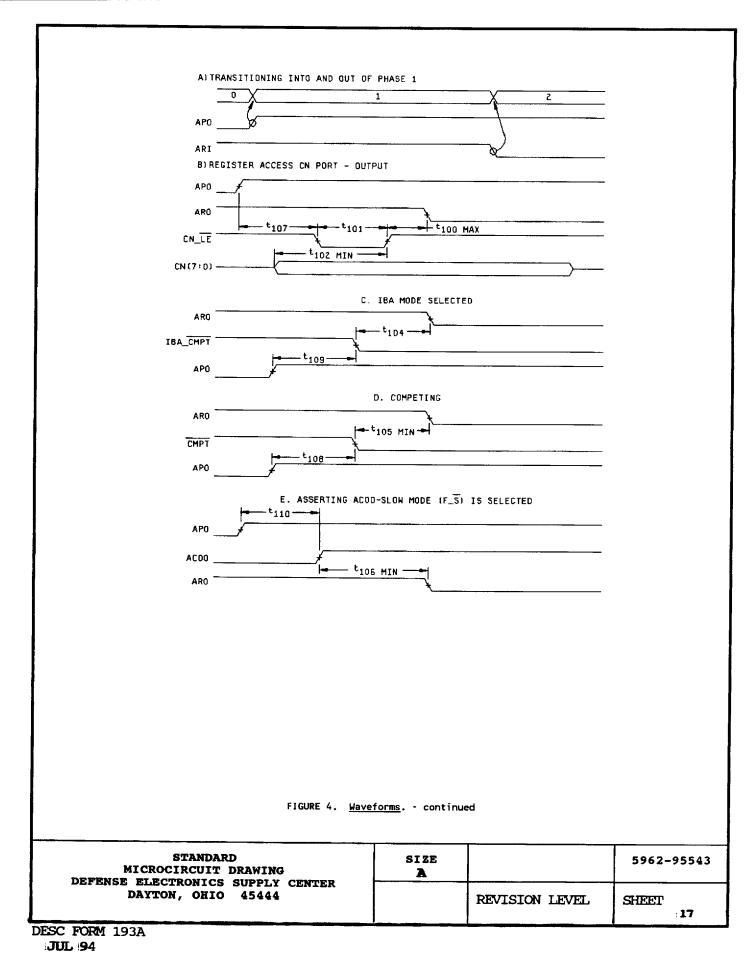

| 4ax CN_LE negated<br>to ARO negated                                                    | t <sub>100</sub> |                                                                     | 9, 10, 11            | 01             |               | 4+<br>(0-25) | ns   |

| CN_LE width                                                                            | t <sub>101</sub> |                                                                     | 9, 10, 11            | 01             | 18            | 28           | ns   |

| CN port setup time                                                                     | <sup>t</sup> 102 |                                                                     | 9, 10, 11            | 01             | 23            |              | ns   |

| (ba-CMPT asserted to Aro<br>negated. (determined by<br>programmable value<br>IBA mode) | t104             |                                                                     | 9, 10, 11            | 01             | 20+<br>(0-25) |              | ns   |

| MPT asserted to Aro<br>negated. (determined by<br>programmable value)                  | <sup>t</sup> 105 |                                                                     | 9, 10, 11            | 01             | 20+<br>(0-25) |              | ns   |

| COO asserted to Aro<br>negated. (determined by<br>programmable value<br>slow mode)     | t <sub>106</sub> |                                                                     | 9, 10, 11            | 01             | 18+<br>(0-25) |              | ns   |

| APO asserted to CN_LE asserted. CTRL3 (0), "go" bit is set                             | <sup>t</sup> 107 |                                                                     | 9, 10, 11            | 01             |               | 32           | ns   |

| PO <u>ass</u> erted to<br>CMPT asserted                                                | <sup>t</sup> 108 |                                                                     | 9, 10, 11            | 01             |               | 24           | ns   |

| PO ass <u>erte</u> d to<br>IBA_CMPT asserted                                           | t <sub>109</sub> |                                                                     | 9, 10, 11            | 01             |               | 22           | ns   |

| PO asserted to ACOO asserted slow mode                                                 | <sup>t</sup> 110 |                                                                     | 9, 10, 11            | 01             |               | 32           | ns   |

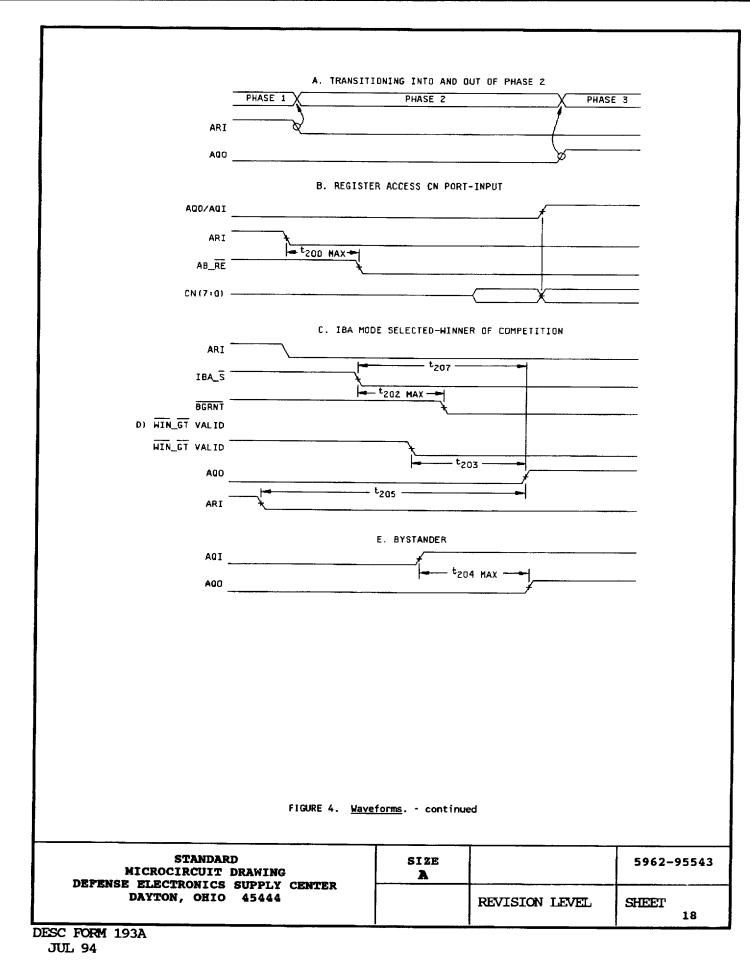

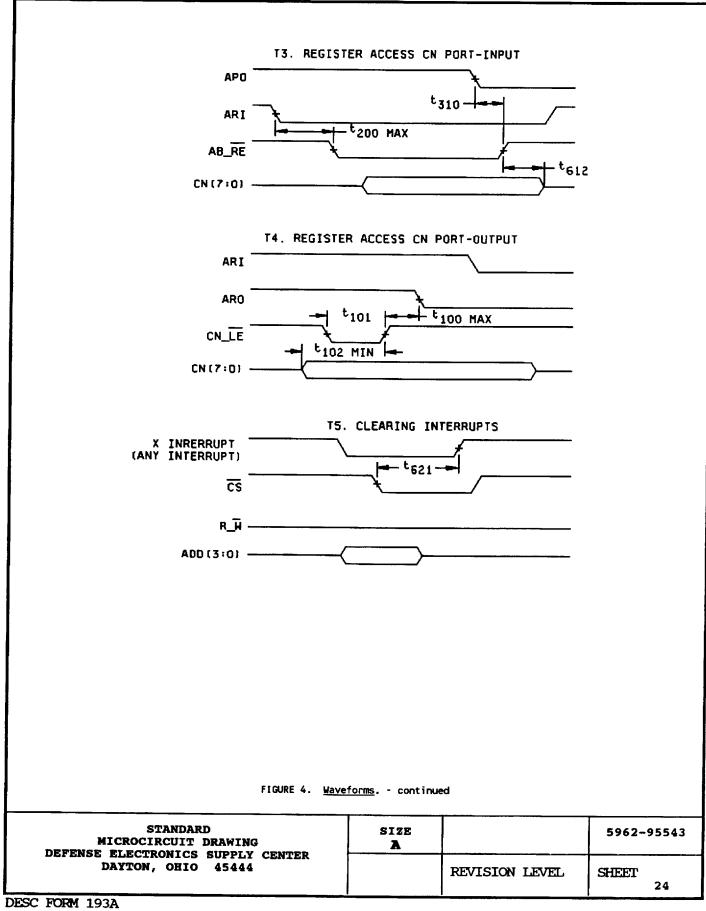

| RI negated to<br>AB_RE asserted                                                        | t <sub>200</sub> |                                                                     | 9, 10, 11            | 01             |               | 62           | ns   |

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

REVISION LEVEL

SHEET

6

DESC FORM 193A JUL 94

■ 7004708 0009882 DlT **■**

| Test                                                   | Symbol           | Conditions<br>-55°C ≤ T <sub>A</sub> ≤ +125°C                           | Group A<br>subgroups | Device<br>type | Limits |       | Unit |

|--------------------------------------------------------|------------------|-------------------------------------------------------------------------|----------------------|----------------|--------|-------|------|

|                                                        |                  | $V_{CC} = 5 \hat{V} \pm 10\% \frac{1}{1}$<br>unless otherwise specified |                      |                | Min    | Max   |      |

| IBA <u>S</u> asserted to<br>BGRNT asserted<br>IBA mode | t <sub>202</sub> | V <sub>CC</sub> = 4.5 V<br>See figure 4                                 | 9, 10, 11            | 01             |        | 40    | ns   |

| WIN_GT asserted to Aqo<br>asserted after TA<br>expired | t <sub>203</sub> |                                                                         | 9, 10, 11            | 01             |        | 35    | ns   |

| AQI asserted to<br>AQO asserted                        | t <sub>204</sub> |                                                                         | 9, 10, 11            | 01             |        | 24    | ns   |

| ARI negated to<br>AQO asserted                         | t <sub>205</sub> |                                                                         | 9, 10, 11            | 01             |        | 30+TA | ns   |

| IBA_S asserted to<br>AQO asserted                      | t <sub>207</sub> |                                                                         | 9, 10, 11            | 01             |        | 35    | ns   |

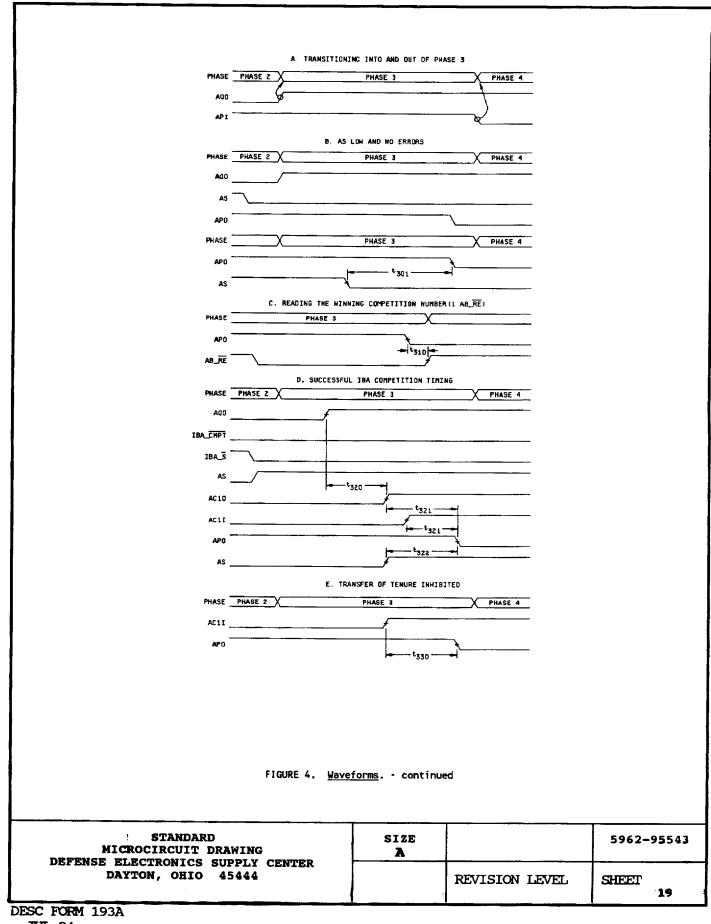

| AC10 asserted to<br>APO negated                        | <sup>‡</sup> 300 |                                                                         | 9, 10, 11            | 01             |        | 29    | ns   |

| AS_Cancel negated<br>to APO negated                    | <sup>t</sup> 301 |                                                                         | 9, 10, 11            | 01             |        | 27    | ns   |

| APO ne <u>ga</u> ted to<br>AB_RE negated               | <sup>†</sup> 310 |                                                                         | 9, 10, 11            | 01             |        | 10    | ns   |

| AQO asserted to<br>AC10 asserted                       | <sup>†</sup> 320 |                                                                         | 9, 10, 11            | 01             |        | 13    | ns   |

| AC1I asserted to<br>APO negated                        | <sup>t</sup> 321 |                                                                         | 9, 10, 11            | 01             | 5      | 21    | ns   |

| AS_Cancel asserted<br>to APC negated                   | t322             |                                                                         | 9, 10, 11            | 01             | 5      | 21    | ns   |

| AC1I asserted to APO negated                           | t330             |                                                                         | 9, 10, 11            | 01             |        | 24    | ns   |

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                | 5962-95543 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 7    |

🔤 9004708 0009883 T56 📟

| Test                                                               | Symbol           | Conditions<br>-55°C ≤ T <sub>A</sub> ≤ +125°C                                      | Group A<br>subgroups | Device<br>type | Li  | imits | Unit |

|--------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------|----------------------|----------------|-----|-------|------|

|                                                                    |                  | -55°C ≤ TA ≤ +125°C<br>V <sub>CC</sub> = 5 V ±10% 1/<br>unless otherwise specified |                      | !              | Min | Max   |      |

| MGRQ or BRQ negated to<br>ACOO, AC10 asserted                      | t340             | V <sub>CC</sub> = 4.5 V<br>See figure 4                                            | 9, 10, 11            | 01             |     | 40    | ns   |

| AQO asserted to<br>ACOO negated                                    | <sup>t</sup> 341 |                                                                                    | 9, 10, 11            | 01             |     | 4     | ns   |

| AQO <u>ass</u> erted to<br>ERIT asserted                           | t342             |                                                                                    | 9, 10, 11            | 01             |     | 23    | ns   |

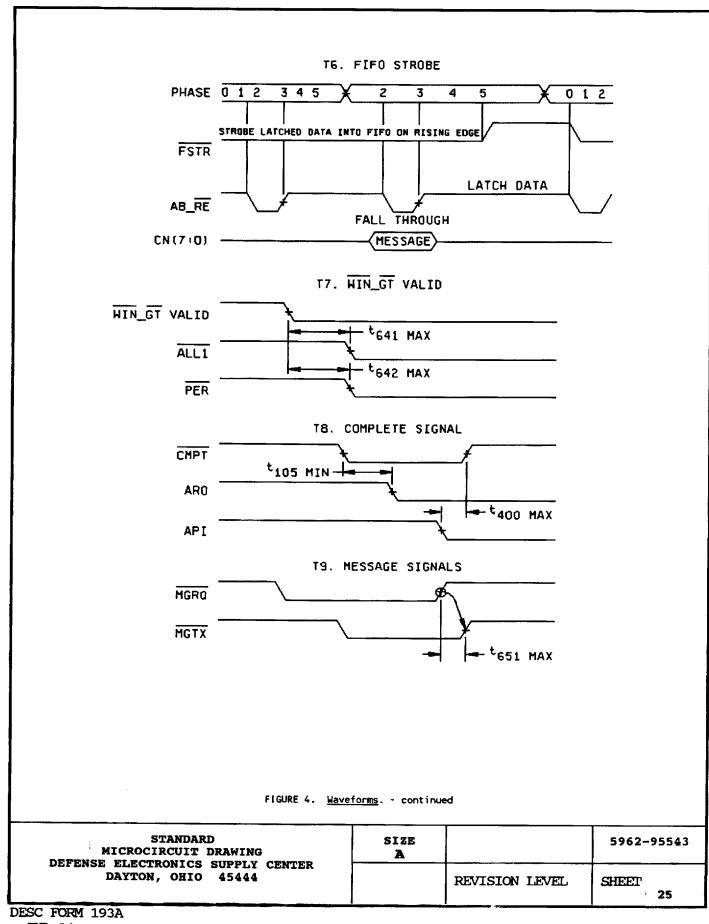

| API <u>neg</u> ated to<br>CMPT negated                             | t400             |                                                                                    | 9, 10, 11            | 01             |     | 34    | ns   |

| ACTI asserted to<br>ARO asserted                                   | <sup>t</sup> 401 |                                                                                    | 9, 10, 11            | 01             |     | 26    | ns   |

| NS_Cancel asserted<br>to AC10 asserted                             | t403             |                                                                                    | 9, 10, 11            | 01             | 7   | 24    | ns   |

| ARI asserted to<br>ARO asserted                                    | <sup>t</sup> 405 | 1                                                                                  | 9, 10, 11            | 01             |     | 25    | ns   |

| ENDT asserted to<br>ARO asserted                                   | t407             | !                                                                                  | 9, 10, 11            | 01             |     | 32    | ns   |

| ARO <u>asse</u> rted to<br>BGRNT asserted                          | t <sub>500</sub> |                                                                                    | 9, 10, 11            | 01             |     | 12    | ns   |

| BGRNT, MGTX, UNLK or any interrupt asserted to AQO negated         | <sup>t</sup> 501 |                                                                                    | 9, 10, 11            | 01             | 3   |       | ns   |

| ARO <u>ass</u> erted to<br>FSTR negated                            | t <sub>502</sub> |                                                                                    | 9, 10, 11            | 01             |     | 10    | ns   |

| ARO ass <u>erte</u> d to<br>IBA_CMPT negated                       | t <sub>503</sub> |                                                                                    | 9, 10, 11            | 01             |     | 10    | ns   |

| ARO <u>ass</u> erted to MGTX,<br>UNLK or any interrupt<br>asserted | t <sub>504</sub> |                                                                                    | 9, 10, 11            | 01             |     | 10    | ns   |

| STANDARD MICROCIRCUIT DRAWING                        | SIZE<br><b>A</b> |                | 5962-95543 |

|------------------------------------------------------|------------------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | SHEET<br>8 |

9004708 0009884 992 🞟 -

| Test                                                   | Symbol            | Conditions<br>-55°C ≤ T <sub>A</sub> ≤ +1          | 25°C                   | Group A<br>subgroups | Device<br>type |       |     | Unit    |

|--------------------------------------------------------|-------------------|----------------------------------------------------|------------------------|----------------------|----------------|-------|-----|---------|

|                                                        |                   | $V_{CC} = 5 \hat{V} \pm 10$<br>unless otherwise sp | <u>l</u> /<br>pecified |                      |                | Min   | Max |         |

| RST Pulse width                                        | <sup>t</sup> 601  | V <sub>CC</sub> = 4.5 V<br>See figure 4            |                        | 9, 10, 11            | 01             | 50    |     | ns      |

| Output reset time                                      | t <sub>602</sub>  |                                                    |                        | 9, 10, 11            | 01             |       | 54  | ns      |

| RST negated to<br>ARO asserted                         | t <sub>603</sub>  |                                                    |                        | 9, 10, 11            | 01             |       | 25  | ns      |

| RINT pulse width                                       | t <sub>604</sub>  | •                                                  |                        | 9, 10, 11            | 01             | 50    |     | ns      |

| Output initialization reset time                       | t <sub>605</sub>  | •                                                  |                        | 9, 10, 11            | 01             |       | 45  | ns      |

| CS pulse width                                         | t <sub>701</sub>  |                                                    |                        | 9, 10, 11            | 01             | 35    |     | ns      |

| CS recovery time                                       | t <sub>702</sub>  |                                                    |                        | 9, 10, 11            | 01             | 15    |     | ns      |

| CS <u>asser</u> ted to<br>DSACK asserted               | t <sub>703</sub>  |                                                    |                        | 9, 10, 11            | 01             |       | 23  | ns      |

| ADD (3:0) setup time                                   | <sup>t</sup> 704  | •                                                  |                        | 9, 10, 11            | 01             | 5     |     | ns      |

| ADD (3:0) hold time                                    | t <sub>705</sub>  |                                                    |                        | 9, 10, 11            | 01             | 9     |     | ns      |

| CS negated to DSACK negated                            | <sup>t</sup> 706  |                                                    |                        | 9, 10, 11            | 01             | 5     |     | ns      |

| R_W set up                                             | t <sub>707</sub>  |                                                    |                        | 9, 10, 11            | 01             | 0     |     | ns      |

| Data (7:0) setup ti <u>me</u><br>With respect to DSACK | <sup>‡</sup> 710  |                                                    |                        | 9, 10, 11            | 01             | 28    |     | ns      |

| Data (7:0) hold time<br>with respect to DSACK          | <sup>t</sup> 711  |                                                    |                        | 9, 10, 11            | 01             | 0     |     | ns      |

|                                                        |                   |                                                    |                        |                      |                |       |     |         |

| STA<br>MICROCIRC                                       | NDARD<br>UIT DRAW | ING                                                | SIZI<br><b>A</b>       | E                    |                |       | 590 | 62-9554 |

| DEFENSE ELECTRON DAYTON, (                             | NICS SUPI         | PLY CENTER                                         | <u> </u>               | RE                   | /ISION         | LEVEL | SHE | ET<br>9 |

9004708 0009885 829 📟

| Test                                               | Symbol           | Conditions<br>-55°C ≤ T <sub>A</sub> ≤ +125°C                            | Group A subgroups | Device<br>type | Li  | Limits |    |

|----------------------------------------------------|------------------|--------------------------------------------------------------------------|-------------------|----------------|-----|--------|----|

|                                                    |                  | V <sub>CC</sub> = 5 <sup>°</sup> V ±10% 1/<br>unless otherwise specified |                   |                | Min | Max    |    |

| SEL hold time                                      | t <sub>712</sub> | V <sub>CC</sub> = 4.5 V<br>See figure 4                                  | 9, 10, 11         | 01             | 5   |        | ns |

| Data (7:0) setup time with respect to CS negated   | t <sub>724</sub> |                                                                          | 9, 10, 11         | 01             | 15  |        | ns |

| Data (7:0) hold time with respect to CS negated    | t <sub>725</sub> |                                                                          | 9, 10, 11         | 01             | 5   |        | ns |

| Data (7:0) access time with respect to CS asserted | t <sub>729</sub> |                                                                          | 9, 10, 11         | 01             |     | 33     | ns |

| AB_RE negated to CN (7:0) TRI-STATE                | <sup>t</sup> 612 |                                                                          | 9, 10, 11         | 01             | 0   |        | ns |

| CS asserted to interrupt negated                   | t <sub>621</sub> |                                                                          | 9, 10, 11         | 01             |     | 43     | ns |

| ALL1 asserted with respect to WIN_GT               | <sup>t</sup> 641 |                                                                          | 9, 10, 11         | 01             |     | 5      | ns |

| PER asserted with respect to WIN_GT                | t <sub>642</sub> |                                                                          | 9, 10, 11         | 01             |     | 5      | ns |

| MGRQ negated to MGTX negated                       | <sup>t</sup> 651 |                                                                          | 9, 10, 11         | 01             |     | 23     | ns |

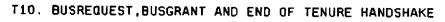

| END <u>T ass</u> erted to<br>BGRNT negated         | <sup>t</sup> 662 |                                                                          | 9, 10, 11         | 01             |     | 25     | ns |

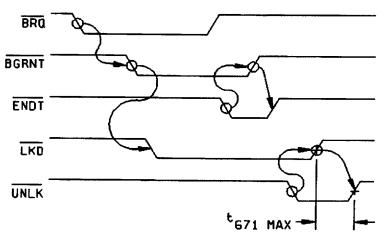

| LKD_negated to UNLK negated                        | t671             |                                                                          | 9, 10, 11         | 01             |     | 25     | ns |

<sup>1/</sup> All testing to be performed, shall be at worst-case tests conditions, unless otherwise specified.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95543  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>10 |

9004708 0009886 765

: JUL 94

■ 9004708 0009887 bTl ■

| Dimensions   | <b>Mi</b> lli | meters    | Inc   | ches  |

|--------------|---------------|-----------|-------|-------|

| D (110101013 | Min           | Max       | Min   | Max   |

| A            | 3.30          | 4.06      | .130  | .160  |

| A1           |               | 3.05      |       | .120  |

| A2           |               | 1.17      |       | .046  |

| A3           | 0.64          |           | .025  |       |

| ь            | 0.46          | 0.56      | .018  | .022  |

| D/E          | 21.90         | 22.40     | .862  | .882  |

| e            | 1.32          | 1.22      | .048  | .052  |

| D1/E1        | 22.8          | 22.86 BSC |       | BSC   |

| 02/E2        | 18.29         | 18.65     | .720  | .734  |

| HD/HE        | 37.97         | 38.23     | 1.495 | 1,505 |

#### NOTES:

- The preferred unit of measurement is millimeters. However, this item was designed using inch-pound units of measurements. In case of problems involving conflicts between the metric and inch-pound units, the inch-pound units shall rule.

- Lead number 1 is identified by a tab located on the lead.

Lead numbers are shown for reference only and do not appear on package.

FIGURE 1. Case outline. - continued

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-95543  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>12 |

DESC FORM 193A JUL 94

9004708 0009888 538 📟

|                 | <del></del>               |                 |                  |

|-----------------|---------------------------|-----------------|------------------|

| Device types    |                           | 01              |                  |

| Case outlines   |                           | X               |                  |

| Terminal number | Terminal symbol           | Terminal number | Terminal symbol  |

| 1               | CN2                       | 35              | DATA4            |

| 2               | CN1                       | 36              | V <sub>DD3</sub> |

| 3               | CNO                       | 37              | DATA5            |

| 4               | CNp                       | 38              | DATA6            |

| 5               | WIN GT                    | 39              | DATA7            |

| 6               | ALL 1                     | 40              | DSACK            |

| 7               | PER                       | 41              | R W              |

| 8               | AC11                      | 42              | cs               |

| 9               | AC10                      | 43              | SEL              |

| 10              | AC01                      | 44              | ADD0             |

| 11              | ACOO                      | 45              | ADD 1            |

| 12              | API                       | 46              | ADD2             |

| 13              | APO                       | 47              | ADD3             |

| 14              | IQA                       | 48              | RST              |

| 15              | AQO                       | 49              | RINT             |

| 16              | ARI                       | 50              | GND1             |

| 17              | ARO                       | 51              | PFINT            |

| 18              | V <sub>DD 1</sub>         | 52              | UNLK             |

| 1 <del>9</del>  | Vod 1<br>HALT             | 53              | LKD              |

| 20              | CLK                       | 54              | ENDT             |

| 21              | GND4                      | 55              | IBA <u>s</u>     |

| 22              | C1                        | 56              | IBA CMPT         |

| 23              | V <sub>DD4</sub>          | 57              | AS CANCEL        |

| 24              | V <sub>DD4</sub><br>MGINT | 58              | FSTR             |

| 25              | ERINT                     | 59              | AB_RE            |

| 26              | MGTX                      | 60              | <u>CN L</u> E    |

| 27              | MGRQ                      | 61              | CMPT             |

| 28              | <u>BGR</u> NT             | 62              | CN7              |

| 29              | BRQ                       | 63              | CN6              |

| 30              | DATAO                     | 64              | CN5              |

| 31              | DATA1                     | 65              | GND2             |

| 32              | DATA2                     | 66              | CN4              |

| 33              | DATA3                     | 67              | V <sub>DD2</sub> |

| 34              | GND3                      | 68              | CÑ3              |

|                 |                           |                 |                  |

FIGURE 2. <u>Terminal connections</u>

| STANDARD MICROCIRCUIT DRAWING                        | SIZE<br>A |                | 5962-95543  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>13 |

**■ 9004708 0009889 474** ■

FIGURE 3. Logic diagram.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-95543 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 14   |

9004708 0009890 196

■ 9004708 0009891 022 **■**

JUL 94

■ 9004708 0009892 T69 **■**

■ 9004708 0009893 9T5 **■**

9004708 0009894 831

. JUL 94

9004708 0009896 604

9004708 0009897 540

9004708 0009898 487

**9004708 0009899 313**

9004708 0009900 965

JUL 94

■ 9004708 0009901 8T1 **■**

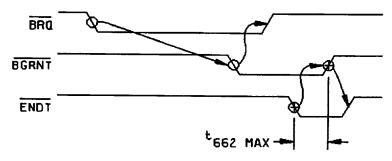

T11. LKD AND UNLK HANDSHAKE SIGNALS

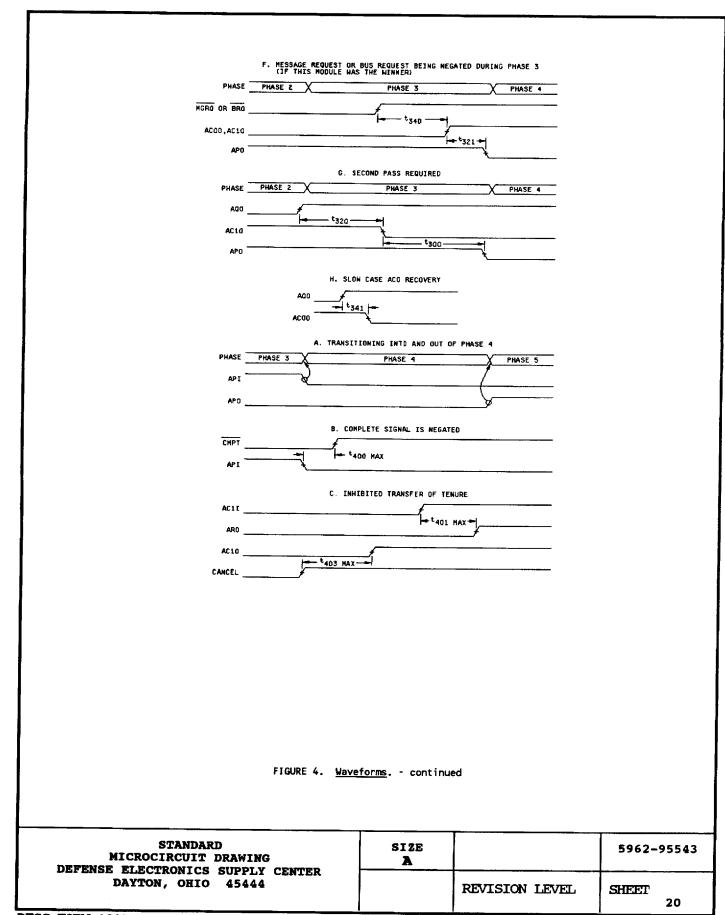

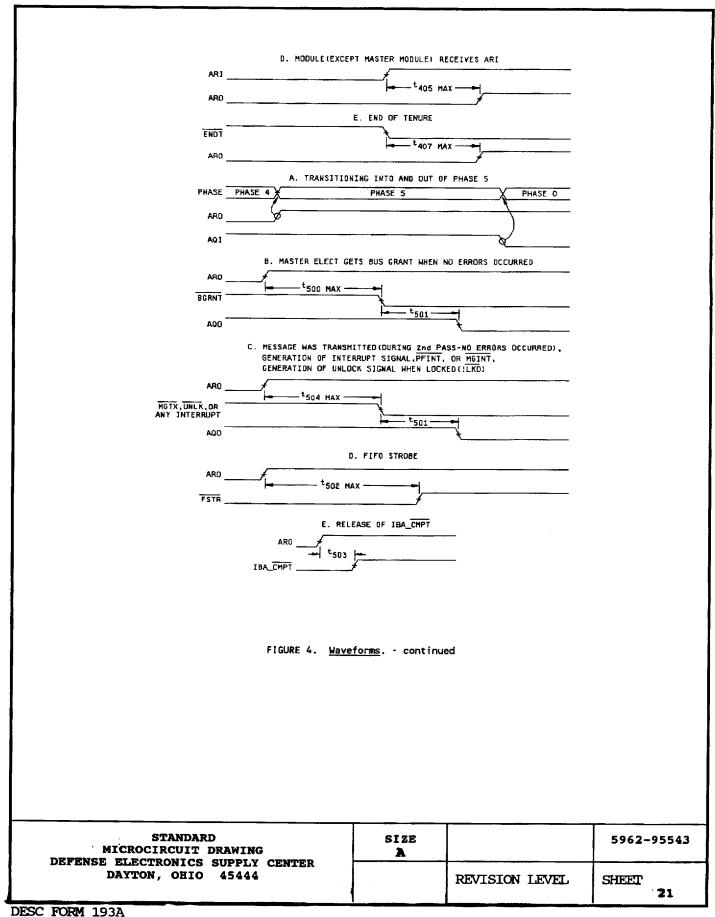

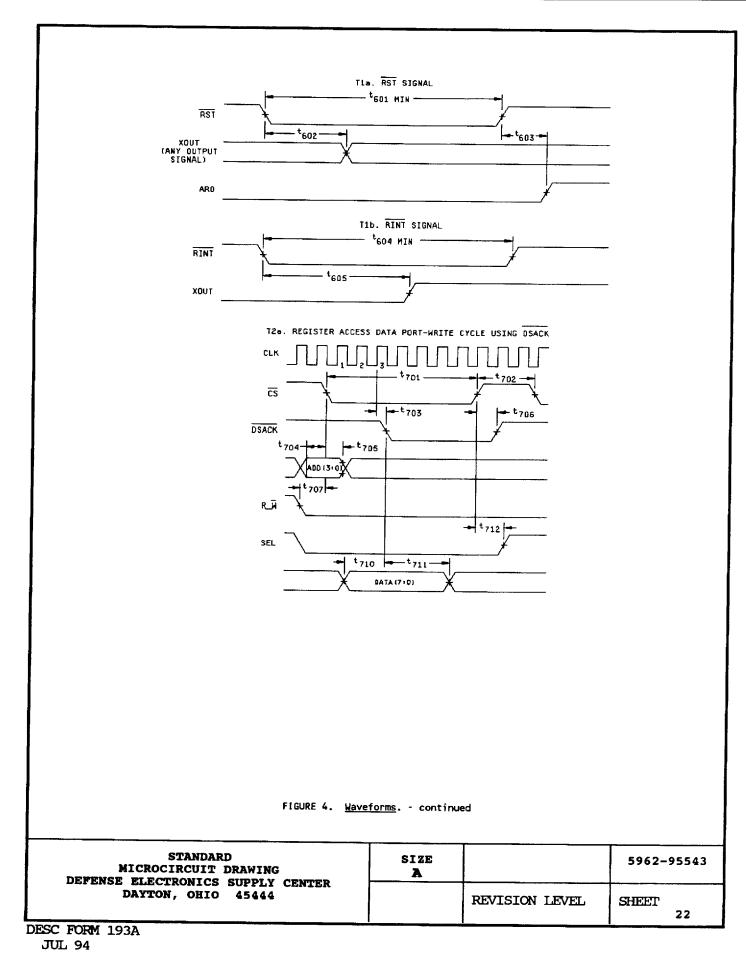

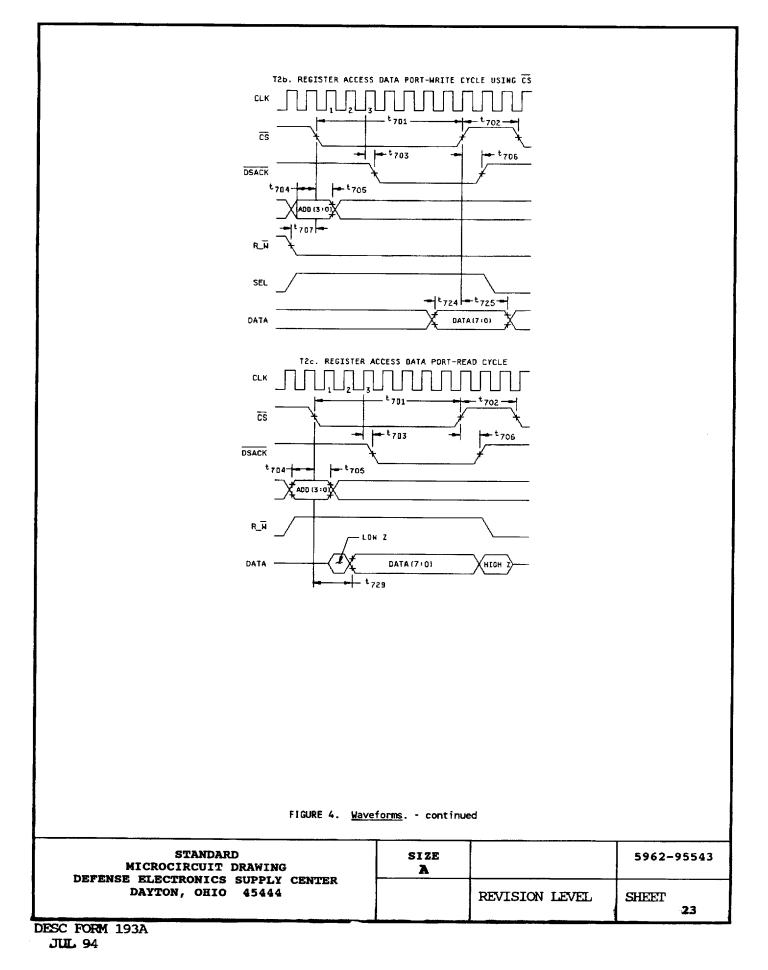

FIGURE 4. Waveforms. - continued

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | size<br><b>A</b> |                | 5962-95543 |

|-----------------------------------------------------------------|------------------|----------------|------------|

| DAYTON, OHIO 45444                                              | ,                | REVISION LEVEL | SHEET 26   |

9004708 0009902 738

- 4.2 <u>Screening</u>. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. For device classes Q and V, screening shall be in accordance with MIL-1-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection.

- 4.2.1 Additional criteria for device class M.

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

- 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-I-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in appendix B of MIL-I-38535.

- 4.3 <u>Qualification inspection for device classes Q and V</u>. Qualification inspection for device classes Q and V shall be in accordance with MIL-I-38535. Inspections to be performed shall be those specified in MIL-I-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

- 4.4 <u>Conformance inspection</u>. Quality conformance inspection for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein) and as specified herein. Inspections to be performed for device class M shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4). Technology conformance inspection for classes Q and V shall be in accordance with MIL-I-38535 including groups A, B, C, D, and E inspections and as specified herein except where option 2 of MIL-I-38535 permits alternate in-line control testing.

- 4.4.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. For device class M, subgroups 7 and 8 tests shall be sufficient to verify the functionality of the device. For device classes Q and V, subgroups 7 and 8 shall include verifying the functionality of the device; these tests shall have been fault graded in accordance with MIL-STD-883, test method 5012 (see 1.5 herein).

- 4.4.2 <u>Group C inspection</u>. The group C inspection end-point electrical parameters shall be as specified in table II herein.

- 4.4.2.1 Additional criteria for device class M. Steady-state life test conditions, method 1005 of MIL-STD-883:

- a. Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005.

- b.  $T_A = +125$ °C, minimum.

- c. Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-95543 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 27   |

JUL 94

■ 9004708 0009903 674 **■**

TABLE II. Electrical test requirements.

| Test requirements                                 | Subgroups<br>(in accordance with<br>MIL-STD-883,<br>TM 5005, table I) | Subgroups<br>(in accordance with<br>MIL-I-38535, table III) |                                   |  |

|---------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------|--|

|                                                   | Device<br>class M                                                     | Device<br>class Q                                           | Device<br>class V                 |  |

| Interim electrical parameters (see 4.2)           | 1                                                                     | 1                                                           | 1                                 |  |

| Final electrical parameters (see 4.2)             | 1, 2, 3, 7, 8, 9, <u>1</u> /<br>10, 11                                | 1, 2, 3, 7, 8, <u>1</u> /<br>9, 10, 11                      | 1,2,3,7,8 <u>2</u> /<br>9, 10, 11 |  |

| Group A test<br>requirements (see 4.4)            | 1, 2, 3, 7, 8, 9,<br>10, 11                                           | 1, 2, 3, 7, 8,<br>9, 10, 11                                 | 1,2,3,7,8,9,<br>10, 11            |  |

| Group C end-point electrical parameters (see 4.4) | 1, 2, 3                                                               | 1, 2, 3                                                     | 1, 2, 3                           |  |

| Group D end-point electrical parameters (see 4.4) | 1, 2, 3                                                               | 1, 2, 3                                                     | 1, 2, 3                           |  |

| Group E end-point electrical parameters (see 4.4) | 1                                                                     | 1                                                           | 1                                 |  |

<sup>1/</sup> PDA applies to subgroup 1.

- 4.4.2.2 Additional criteria for device classes Q and V. The steady-state life test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The test circuit shall be maintained under document revision level control by the device manufacturer's TRB, in accordance with MIL-I-38535, and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005.

- 4.4.3 <u>Group D inspection</u>. The group D inspection end-point electrical parameters shall be as specified in table II herein.

- 4.4.4 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein). RMA levels for device classes Q and V shall be M, D, L, R, F, G, and H and for device class M shall be M and D.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. For device class M, the devices shall be subjected to radiation hardness assured tests as specified in MIL-I-38535, appendix A, for the RHA level being tested. For device classes Q and V, the devices or test vehicle shall be subjected to radiation hardness assured tests as specified in MIL-I-38535 for the RHA level being tested. All device classes must meet the postirradiation end-point electrical parameter limits as defined in table 1 at T<sub>A</sub> = +25°C ±5°C, after exposure, to the subgroups specified in table II herein.

- c. When specified in the purchase order or contract, a copy of the RHA delta limits shall be supplied.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-95543 |

|-----------------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                                    |           | REVISION LEVEL | SHEET 28   |

9004708 0009904 500

<sup>2/</sup> PDA applies to subgroups 1 and 7.

#### 5. PACKAGING

- 5.1 <u>Packaging requirements</u>. The requirements for packaging shall be in accordance with MIL-STD-883 (see 3.1 herein) for device class M and MIL-I-38535 for device classes Q and V.

- 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.1.1 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.1.2 <u>Substitutability</u>. Device class Q devices will replace device class M devices.

- 6.2 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-973 using DD Form 1692, Engineering Change Proposal.

- 6.3 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and which SMD's are applicable to that system. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DESC-EC, telephone (513) 296-6047.

- 6.4 <u>Comments</u>. Comments on this drawing should be directed to DESC-EC, Dayton, Ohio 45444-5765, or telephone (513) 296-8525.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-95543 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET      |

DESC FORM 193A JUL 94 6.5 <u>Abbreviations, symbols, and definitions</u>. The abbreviations, symbols, and definitions used herein are defined in MIL-1-38535 and MIL-STD-1331 and as follows.

# PIN DEFINITIONS.

| PINS           | # OF PINS           | TYPE      | DESCRIPTION                                                                                                                                    |

|----------------|---------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL TO/FROM | M THE HANDSHAKE TRA | ANSCEIVER |                                                                                                                                                |

| APO            | 11                  | 0         | Arbitration handshake signal from the controller.                                                                                              |

| AQO            | 1                   | 0         | Arbitration handshake signal from the controller.                                                                                              |

| ARO            | 1                   | 0         | Arbitration handshake signal from the controller.                                                                                              |

| AC00           | 1 1                 | 0         | Arbitration condition signal from the controller.                                                                                              |

| AC10           | 1                   | 0         | Arbitration condition signal from the controller.                                                                                              |

| API            | 1                   | [         | Arbitration handshake signal from Futurebus +. This signal is<br>the filtered and inverted version of the Futurebus + backplane<br>signal AP*. |

| I DA           | 1                   | I         | Arbitration handshake signal from Futurebus +. This signal is the filtered and inverted version of the Futurebus + backplane signal AQ*.       |

| ARI            | 1                   | 1         | Arbitration handshake signal from Futurebus +. This signal is the filtered and inverted version of the Futurebus + backplane signal AR*.       |

| AC01           | 1                   | I         | Arbitration condition signal from Futurebus +.                                                                                                 |

| AC1I           | 1                   | 1         | Arbitration condition signal from Futurebus +.                                                                                                 |

| PIN                             | # OF PINS            | TYPE              | DESCRIPTION                                                                                  |

|---------------------------------|----------------------|-------------------|----------------------------------------------------------------------------------------------|

| SIGNAL TO/FROM<br>Transceiver). | THE ARBITRATION TRAI | NSCEIVER (Note: 1 | These pins are mapped to/from the Futurebus+ Arbitration                                     |

| CN(7:0)                         | 8                    | 1/0               | The bus to carry competition number to/from the arbitration transceiver.                     |

| CNp                             | 1                    | 0                 | Parity bit of the competition number.                                                        |

| CMPT                            | 1                    | 0                 | Enables the Arbitration number onto Futurebus+.                                              |

| AB_RE                           | 1                    | 0                 | Direction control for the competition number bus to/from the transceiver.                    |

| CN_LE                           | 1                    | 0                 | Latch enable for latching the Arbitration number from the controller into the transceiver.   |

| PER                             | 1                    | I                 | PARITY ERROR: Indicates that a parity error was detected on the winner's arbitration number. |

| WIN _GT                         | 1                    | 1                 | Win signal when competing/greater than signal when not competing (used to preempt).          |

| ALL1                            | 1                    | 1                 | Indicates that all the arbitration number lines on the bus are asserted (used for messages). |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95543  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>30 |

DESC FORM 193A JUL 94

9004708 0009906 383

# PIN DEFINITIONS - continued

| PIN           | # OF PINS            | TYPE           | DESCRIPTION                                                                                                                                                                                                                     |

|---------------|----------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGNALS TO/FRO | M THE PARALLEL PROTO | COL CONTROLLER |                                                                                                                                                                                                                                 |

| BRQ           | 1                    | I              | BUS REQUEST: Indicates to the controller to acquire the bus for the module's use.                                                                                                                                               |

| BGRNT         | 1                    | 0              | BUS GRANT: Signal asserted by the controller after the detection of a bus request. The module can start using the bus.                                                                                                          |

| RINT          | 1                    | ī              | Will put the arbitration controller on phase 0 and release all the bus lines except AR*. A selective reset is performed. The rising edge will release controller from phase 0. This reset is to be used for bus initialization. |

| RST           | 1                    | I              | Reset signal from the host. An internal reset is performed. All bus signals are released. The rising edge will put the controller in phase O (same as power-up reset).                                                          |

| HALT          | 1                    | I              | Will halt the arbitration controller in phase O. This signal is for use during live insertion.                                                                                                                                  |

| ENDT          | 1                    | Ī              | END OF TEMURE: Indicates the true end of bus tenure of the current master. This line may be asserted only after all th parallel protocol lines are released. (Generated via external logic from BRQ* released).                 |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95543  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>31 |

DESC FORM 195A JUL 94

9004708 0009907 21T **3**

# PIN DEFINITIONS - continued

| PIN             | # OF PINS          | TYPE             | DESCRIPTION                                                                                                                                            |

|-----------------|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNALS TO/FROM | THE HOST (CPU Plus | s External Inter | rfcae Logic)                                                                                                                                           |

| DATA(7:0)       | 8                  | 1/0              | Data bus for the host to access the register bank of the controller.                                                                                   |

| ADD(3:0)        | 4                  | 1                | Address bits for the register bank of the controller.                                                                                                  |

| c <u>s</u>      | 1                  | 1                | CHIP SELECT: The host can read or write to/from the controller.                                                                                        |

| R_ V            | 1                  | I                | Read/write signal from the host.                                                                                                                       |

| DSACK           | 1                  | 0                | Data acknowledge pin for host read/write.                                                                                                              |

| SEL             | 1                  | I                | SELECT: Determines how the controller latches in data. A "1" on the pin uses the rising edge of CS*. A "0" on the pin uses the falling edge of DSACK*. |

| MGRQ            | 1                  | I                | MESSAGE REQUEST: Indicates to the controller to send an arbitration message.                                                                           |

| MGTX            | 1                  | 0                | MESSAGE TRANSMIT: Indicates the successful transmission of a arbitration message.                                                                      |

| ERINT           | 1                  | 0                | ERROR INTERRUPT: Indicates that an error occurred during the arbitration cycle.                                                                        |

| MGINT           | 1                  | 0                | MESSAGE INTERRUPT: Indicates the reception of an arbitration message.                                                                                  |

| PFINT           | 1                  | 0                | POWER FAIL INTERRUPT: Indicates that a powerful message was received.                                                                                  |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-95543  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>32 |

DESC FORM 193A JUL 94

9004708 0009908 156

# PIN DEFINITIONS - continued

| PIN            | # OF PINS | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                          |

|----------------|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTERNAL LOGIC |           |      |                                                                                                                                                                                                                                                                                                                      |

| IBACMPT        | 1         | 0    | Signal to indicate that the Parallel Protocol controller may assert its bit on the ADDRESS/DATA bus if it is participating in an Idle Bus Arbitration.                                                                                                                                                               |

| IBAS           | 1         | I    | This signal indicates that IBA was successful. If this module was a competitor in the IBA competition (!BRQ*), then this module is the winner and now the bus master. If this module was the master, but did not compete in the IBA competition and IBA was successful, then the M bit (Status register) is negated. |

| ASCANCEL       | 1         | I    | Indicates the start of the disconnection phase of the current master or cancel the current arbitration cycle.                                                                                                                                                                                                        |

| <u>LKD</u>     | 1         | 1    | LOCKED: Signal to indicate that resources have been locked in the current tenure and hence generate either a dummy cycle if current master or UNLK* otherwise. (Decoded from Futurebus+ Command port output from Data Path Unit).                                                                                    |

| UNLK           | 1         | 0    | UNLOCK: Transfer of tenure indication to the parallel protocol controller for unlocking its resources.  Generated only if the LKD* signal is asserted.  (To external logic).                                                                                                                                         |

| FSTR           | 1         | 0    | FIFO STROBE: Signal generated to load an external FIFO for received arbitration messages.                                                                                                                                                                                                                            |

| CLK            | 1         | I    | Clock input to the internal PLL.                                                                                                                                                                                                                                                                                     |

| C1             | 1         | I    | External capacitor input for PLL0.1 µF.                                                                                                                                                                                                                                                                              |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | size<br><b>A</b> |                | 5962-95543 |

|-----------------------------------------------------------------|------------------|----------------|------------|

| DAYTON, OHIO 45444                                              |                  | REVISION LEVEL | SHEET : 33 |

DESC FORM 193A JUL 94

9004708 0009909 092 📟

6.6 One part - one part number system. The one part - one part number system described below has been developed to allow for transitions between identical generic devices covered by the three major microcircuit requirements documents (MIL-H-38534, MIL-I-38535, and 1.2.1 of MIL-STD-883) without the necessity for the generation of unique PIN's. The three military requirements documents represent different class levels, and previously when a device manufacturer upgraded military product from one class level to another, the benefits of the upgraded product were unavailable to the Original Equipment Manufacturer (OEM), that was contractually locked into the original unique PIN. By establishing a one part number system covering all three documents, the OEM can acquire to the highest class level available for a given generic device to meet system needs without modifying the original contract parts selection criteria.

| Military documentation format                              | Example PIN<br>under new system | Manufacturing source listing | Document<br><u>listing</u> |

|------------------------------------------------------------|---------------------------------|------------------------------|----------------------------|

| New MIL-H-38534 Standard Microcircuit<br>Drawings          | 5962-XXXXXZZ(H or K)YY          | QML - 38534                  | MIL-BUL-103                |

| New MIL-I-38535 Standard Microcircuit<br>Drawings          | 5962-XXXXXZZ(Q or V)YY          | QML - 38535                  | MIL-BUL-103                |

| New 1.2.1 of MIL-STD-883 Standard<br>Microcircuit Drawings | 5962-XXXXXZZ(M)YY               | MIL-BUL-103                  | MIL-BUL-103                |

# 6.7 Sources of supply.

- 6.7.1 Sources of supply for device classes Q and V. Sources of supply for device classes Q and V are listed in QML-38535. The vendors listed in QML-38535 have submitted a certificate of compliance (see 3.6 herein) to DESC-EC and have agreed to this drawing.

- 6.7.2 <u>Approved sources of supply for device class M</u>. Approved sources of supply for class M are listed in MIL-BUL-103. The vendors listed in MIL-BUL-103 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DESC-EC.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95543  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>34 |

DESC FORM 193A JUL 94

■ 9004708 0009910 804 **■**

46658