## Data Shee **29319.**7

## UDS2998V MIL-STD-883 Compliant

## DUAL FULL-BRIDGE MOTOR DRIVER

The UDS2998V dual full-bridge driver is designed for bidirectional operation of 2-phase stepper motors, a pair of dc servo motors, 2-phase brushless dc motors, or two solenoids at up to 50 V with continuous output currents to  $\pm 1.8$  A per bridge or peak (start-up) currents to  $\pm 2.2$  A. The control inputs are compatible with standard logic families. Except for a common supply voltage and thermal shutdown, the two drivers in a device are completely independent. Dynamic burn-in and 100% high-reliability screening to MIL-STD-883, Class B are standard.

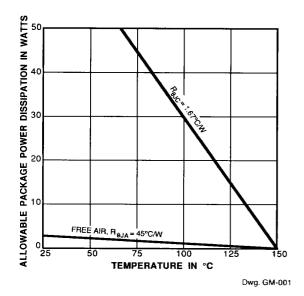

For external PWM control, an OUTPUT ENABLE for each bridge circuit is provided and the sink driver emitters are brought out for connection to external current-sensing resistors. A PHASE input to each bridge determines load-current direction.

Extensive circuit protection is provided on-chip. Output suppression diodes protect the bridges from the transients generated when switching inductive loads. A thermal shutdown circuit disables all of the source drivers if chip temperature rating (package power dissipation) is exceeded. Internal delays provide protection against crossover currents (adjacent source and sink drivers conducting simultaneously) during switching intervals.

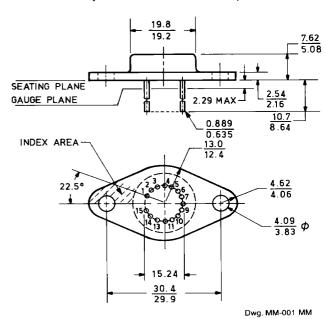

The UDS2998V is supplied in a 15-pin, flange-mount TO-3/TO-204 style hermetic package for improved power dissipation capabilities. An external heatsink is required for high-current applications. The flange is at ground potential and normally needs no isolation.

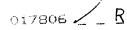

#### UDS2998V

## ABSOLUTE MAXIMUM RATINGS at $T_J \le +150$ °C

| Motor Supply Voltage, V <sub>BB</sub> 50 V         |

|----------------------------------------------------|

| Output Current, I <sub>OUT</sub> (300 ms) ± 2.2 A  |

| (Continuous) ± 1.8 A                               |

| Sink Driver Emitter Voltage, V <sub>E</sub> 1.5 V  |

| Logic Input Voltage Range,                         |

| V <sub>IN</sub> 0.3 V to +15 V*                    |

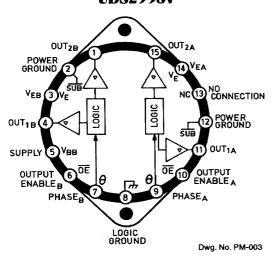

| Package Power Dissipation,                         |

| P <sub>D</sub> See Graph                           |

| Operating Temperature Range,                       |

| T <sub>A</sub> – 55°C to + 125°C                   |

| Storage Temperature Range,                         |

| T <sub>S</sub> −65°C to +150°C                     |

| *V <sub>IN</sub> must not exceed V <sub>BB</sub> . |

Output current rating may be limited by duty cycle, ambient temperature, and heat sinking. Under any set of conditions, do not exceed the specified peak current rating or a junction temperature of  $+150^{\circ}$ C.

#### **FEATURES**

- ± 1.8 A Output Current

- Output Voltage to 50 V

- Integral Output Suppression Diodes

- Output Current Sensing

- Logic Compatible Inputs

- Internal Thermal Shutdown Circuitry

- Crossover-Current Protected

- Hermetically Sealed Package

- High-Reliability Screening

**SPRAGUE**

SEMICONDUCTOR GROUP

## UDS2998V <u>DUAL FULL-BRIDGE MOTOR DRIVER</u>

#### FUNCTIONAL BLOCK DIAGRAM (ONE OF TWO DRIVERS)

Dwg. No. W-107A

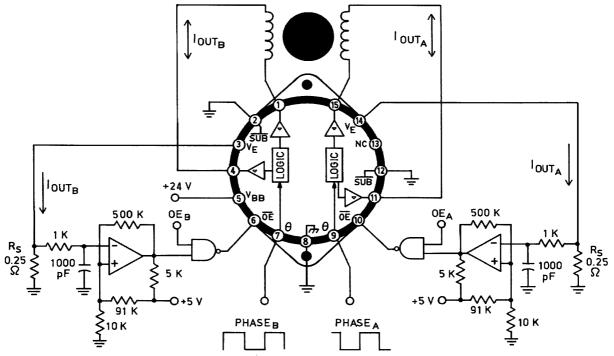

## TYPICAL APPLICATION 2-PHASE BIPOLAR STEPPER MOTOR DRIVE (Chopper Mode)

Dwg. EM-001

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000 Copyright © 1989 Sprague Electric Company, April 1989

# UDS2998V DUAL FULL-BRIDGE MOTOR DRIVER

### ELECTRICAL CHARACTERISTICS at $T_A = -55^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ , $V_{BB} = 50 \text{ V}$ (unless otherwise noted)

|                             |                 |                                                      |      | Limits |      |       |  |

|-----------------------------|-----------------|------------------------------------------------------|------|--------|------|-------|--|

| Characteristic              | Symbol          | Test Conditions                                      | Min. | Тур.   | Max. | Units |  |

| Supply Voltage Range        | V <sub>BB</sub> | Operating                                            | 10   | -      | 50   | V     |  |

| Supply Current              | I <sub>BB</sub> | $V_{\text{ENABLE}(A \& B)} = 0.8 \text{ V, No Load}$ |      | 25     | 40   | mA    |  |

|                             |                 | V <sub>ENABLE(A &amp; B)</sub> = 2.0 V, No Load      |      | _      | 35   | mA    |  |

| Thermal Shutdown Temp.      | TJ              | <u> </u>                                             |      | 175    | _    | °C    |  |

| Thermal Shutdown Hysteresis | $\DeltaT_J$     |                                                      |      | 25     | _    | °C    |  |

#### **Output Drivers**

| Output Leakage Current                          | I <sub>CEX</sub>     | V <sub>OUT</sub> = V <sub>BB</sub> , V <sub>ENABLE</sub> = 2.0 V, Note 3 |          | <5.0  | 50  | μΑ |

|-------------------------------------------------|----------------------|--------------------------------------------------------------------------|----------|-------|-----|----|

|                                                 |                      | V <sub>OUT</sub> = 0V, V <sub>ENABLE</sub> = 2.0 V, Note 3               | _        | <-5.0 | -50 | μΑ |

| Output Saturation Voltage                       | V <sub>CE(SAT)</sub> | Source Driver, I <sub>OUT</sub> = - 1.0 A                                | _        | 1.7   | 2.0 | V  |

| $(T_A = -55^{\circ}C \text{ to } +25^{\circ}C)$ |                      | Sink Driver, I <sub>OUT</sub> = +1.0 A                                   |          | 1.2   | 1.5 | V  |

|                                                 |                      | Source Driver, I <sub>OUT</sub> = -1.8 A                                 | _        | 2.0   | 2.4 | V  |

|                                                 |                      | Sink Driver, I <sub>OUT</sub> = +1.8 A                                   | <b>—</b> | 1.7   | 2.1 | V  |

| Output Saturation Voltage                       | V <sub>CE(SAT)</sub> | Source Driver, $I_{OUT} = -1.0 A$                                        | _        | _     | 1.8 | V  |

| $(T_A = +125^{\circ}C)$                         |                      | Sink Driver, I <sub>OUT</sub> = +1.0 A                                   |          | _     | 1.3 | V  |

|                                                 |                      | Source Driver, I <sub>OUT</sub> = -1.8 A                                 | _        | _     | 2.2 | V  |

|                                                 |                      | Sink Driver, I <sub>OUT</sub> = +1.8 A                                   | _        | _     | 1.9 | V  |

| Output Sustaining Voltage                       | V <sub>CE(sus)</sub> | $I_{OUT} = \pm 1.8 \text{ A, L} = 3.0 \text{ mH,}$                       |          |       |     |    |

|                                                 |                      | $T_A = +25^{\circ}C$ , Note 3                                            | 50       | _     |     | V  |

| Source Driver Rise Time                         | t <sub>r</sub>       | $I_{OUT} = -1.8 \text{ A}$ , Resistive Load, Note 3                      | _        | 500   | _   | ns |

| Source Driver Fall Time                         | t <sub>f</sub>       | $I_{OUT} = -1.8 \text{ A}$ , Resistive Load, Note 3                      |          | 750   | _   | ns |

| Clamp Diode Leakage Current                     | I <sub>R</sub>       | V <sub>R</sub> = 50 V                                                    |          | <5.0  | 50  | μΑ |

| Clamp Diode Forward Voltage                     | V <sub>F</sub>       | $I_F = 1.8 \text{ A}, T_A = -55^{\circ}\text{C to } +25^{\circ}\text{C}$ | _        | 1.5   | 1.9 | V  |

|                                                 |                      | $I_F = 1.8 \text{ A}, T_A = +125^{\circ}\text{C}$                        | _        | _     | 2.1 | V  |

#### **Control Logic**

| TOTAL OF EUGIO         |                                                                            |                                                   |     |       |      |    |

|------------------------|----------------------------------------------------------------------------|---------------------------------------------------|-----|-------|------|----|

| Logic Input Voltage    | Input Voltage V <sub>IN(1)</sub> V <sub>PHASE</sub> or V <sub>ENABLE</sub> |                                                   | 2.0 |       |      | ٧  |

|                        | V <sub>IN(0)</sub>                                                         | V <sub>PHASE</sub> or V <sub>ENABLE</sub>         |     | _     | 0.8  | ٧  |

| Input Current          | I <sub>IN(1)</sub>                                                         | V <sub>PHASE</sub> or V <sub>ENABLE</sub> = 2.0 V |     | <1.0  | 10   | μΑ |

|                        | I <sub>IN(0)</sub>                                                         | V <sub>PHASE</sub> or V <sub>ENABLE</sub> = 0.8 V |     | - 5.0 | - 25 | μΑ |

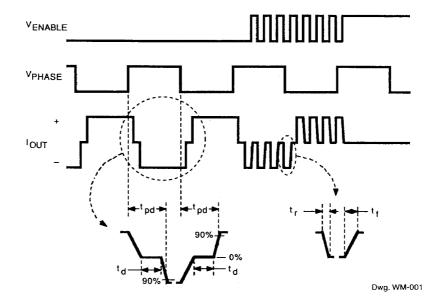

| Propagation Delay Time | t <sub>pd</sub>                                                            | I <sub>OUT</sub> = ± 1.8 A, Note 3,               |     |       |      |    |

|                        |                                                                            | 50% V <sub>PHASE</sub> to 90% I <sub>OUT</sub>    |     | 4.0   | 8.0  | μS |

| Deadtime               | t <sub>d</sub>                                                             | $I_{OUT} = \pm 1.8 A$                             |     | 2.5   |      | μs |

- 1. Typical Data is for design information only and is at  $T_A = +25$ °C.

- 2. Each driver is tested separately.

- Test is performed with V<sub>PHASE</sub> = 0.8 V and then repeated for V<sub>PHASE</sub> = 2.4 V.

Negative current is defined as coming out of (sourcing) the specified device pin.

#### TRUTH TABLE

| ENABLE<br>INPUT | PHASE<br>INPUT | OUTPUT 1 | OUTPUT 2 |

|-----------------|----------------|----------|----------|

| Low             | High           | High     | Low      |

| Low             | Low            | Low      | High     |

| High            | High           | Open     | Low      |

| High            | Low            | Low      | Open     |

### UDS2998V DUAL FULL-BRIDGE MOTOR DRIVER

#### **DIMENSIONS IN INCHES**

#### 0.780 0.755 0.300 0.200 SEATING PLANE 0.100 GAUGE PLANE 0.090 MAX 0.085 0.420 0.035 0 340 0.025 INDEX AREA 0.512 0.488 0.182 22.5° 0.160 $\frac{0.161}{0.151} \phi$ 0.600 1.197 1.177 Dwa. MM-001 IN

## DIMENSIONS IN MILLIMETERS (Based on 1'' = 25.4 mm)

#### NOTES:

- 1. Lead spacing tolerance is non-cumulative.

- 2. Exact body and lead configuration at vendor's option within limits shown.

- Leads missing from their designated positions shall also be counted when numbering leads.

These devices are marked to indicate compliance to the latest issue of MIL-STD-883. For example: UDS2998V-883.

#### MOUNTING OF FLANGE-MOUNT POWER DEVICES

Flange-mount packages are efficient thermal dissipators when properly utilized. In application, the following precautions should be taken:

- 1. Strain relief must be provided if there is any possibility of stress to the leads.

- Thermal grease (Dow Corning 340 or equivalent) should always be used. Thermal compounds are better heat conductors than air but not a good substitute for flat mating surfaces.

- 3. The mounting surface should be flat to within 0.002 inch/inch (0.05 mm/mm).

- "Brute force" mounting to poorly finished heat sinks can cause stresses which may damage the internal silicon chip.

- 5. Mounting holes should be clean of burrs and ridges.

- 6. Use appropriate hardware including lock washers or torque washers.

The Sprague Electric Company reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the design of its products. Components made under military approvals will be in accordance with the approval requirements.

The information included herein is believed to be accurate and reliable. However, the Sprague Electric Company assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

**SPRAGUE**