# Am9341-Am54/74181

# Four Bit Arithmetic Logic Unit/Function Generator

### Distinctive Characteristics:

- Provides 16 arithmetic operations including add, subtract, double and compare.

- Provides ALL 16 possible logic operations of two variables in typically 19 ns.

- Typical add time for 4 bits of only 19 ns, and typical carry time of 12 ns.

- · Full look-ahead for high-speed arithmetic operation on long words.

- 100% reliability assurance testing in compliance with MIL STD 883.

- · Mixing privileges for obtaining price discounts. Refer to price list.

### FUNCTIONAL DESCRIPTION

The Am5/1/31 is a 4-bit high-speed parallel Arithmetic Logic Unit ALLUVIgital Function Generator. When the mode control (M) is held (LOW the circuit performs under control of low function select lines 18 animatic operations, the most important being add and subtract, on two 4-bit parallel highest words. When the mode control of the body control of the forms, under control of the body control of the body

An open collector A = B output is provided so that equivalence of two persiles words can be made by connecting A = B outputs of several ALU's together.

AUL's together. An internal full look-ahead carry scheme is used for high-speed arithmetic operations and provision made for tyrther look-ahead by providing carry propagate (P) and carry generate (S) outputs. These carry signatures can be used as inputs to the Am54/74182 took-ahead carry generator to know long word length high-speed parallal arithmetic providing time to sixteen-all length high-speed parallal arithmetic providing time to sixteen-all length high-speed parallal arithmetic providing the carry generator to sixteen-all length length and one Am 37/1828 book-speed generator is only 31 ns.

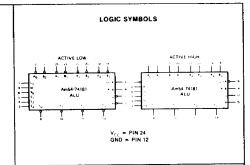

For systems where ultra high-speed is not required, the carry output signal  $\{G_{n+4}\}$  can be used to provide ripple-block arithmetic operations. The ALU can be used with either active HiGH or active LOW inputs and can also be expanded with the Am54/74182 look-ahead carry generator in either mode. The interconnection patterns are identical for both cases.

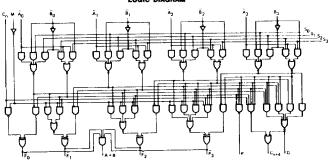

#### LOGIC DIAGRAM

# Am54/74181-Am9341

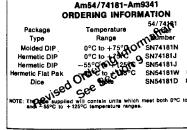

U6N934159X U6N934151X U4M934151X UXX9341XXD

9341

Order Number

Am9341C

supplied will contain units which meet both 0°C to +75°C to +125°C temperature ranges.

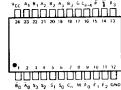

#### CONNECTION DIAGRAM Top View

NOTE: Pin 1 is marked for orientation.

| Temperatur    | e (Amb) Under Blas        |                   |                                                  |              |                   |            | -        |

|---------------|---------------------------|-------------------|--------------------------------------------------|--------------|-------------------|------------|----------|

| Supply Volt   | age to Ground Potential   | (Pin 24 to Pin 12 | Continuous                                       |              |                   | -55        | C to +1  |

|               | Whener in Crithfill 101 I | HIGH Output Stat  |                                                  |              |                   |            | 05041    |

| OC IMPUL V    | ent, Into Outputs         |                   |                                                  |              |                   | -0.5 V t   | D TV     |

| DC Input C    | urrent                    |                   |                                                  |              |                   | -0.6       | 5 V to + |

|               |                           |                   |                                                  |              |                   |            | - 4      |

| ELECTRI       | CAL CHARACTER             | ISTICS OVER       | R OPERATING TEMPERATURE                          |              |                   | -30 n      | nA to +  |

| Am74181       | TA = 0°C to +70°C         | Vac # 5.0         | TOPERATING TEMPERATURE                           | RANGE (U     | nless otherv      | vise noted | 1        |

| Am54181       | TA = -56°C to +125°       |                   | MIN. = 4.75V                                     | MAX. = 5.25V |                   |            | ,        |

| brameters     | Descript                  | tion              |                                                  | MAX 5.5V     | Typ.              |            |          |

|               | Output HIGH Voltage       |                   | Test Conditions (Note 1)                         | Min.         | (Note 2)          | Max.       | l late   |

| VOH           | (Except A=8 Output)       |                   | V <sub>CC</sub> = MIN., I <sub>OH</sub> = -800µA |              |                   |            | Unit     |

|               |                           |                   | VIN = VIH or VIL                                 | 2.4          | 3.4               |            | Valu     |

| VOL           | Output LOW Voltage        |                   | VCC = MIN., IOL = 16mA                           |              |                   | <u> </u>   |          |

|               |                           |                   | VIN * VIH OF VIL                                 | ] [          | 0.2               | 0.4        | Volta    |

| VIH           | Input HIGH Level          |                   | Guaranteed input logical HIGH voltage            |              | $\longrightarrow$ |            |          |

|               |                           | ·                 | for all inputs                                   | 2            | 1                 |            | Voh      |

| VIL           | Input LOW Level           |                   | Guaranteed input logical LOW voltage             |              |                   |            |          |

| Vi            | Input Clemp Voltage       |                   | for all inputs                                   | _ 1          |                   | 0.8        | Volts    |

|               |                           |                   | VCC = MIN., IIN = -12mA                          |              |                   | -1.5       |          |

| юн            | Output HIGH Current fo    | or A=B Output     | VCC = MIN., VOH = 5.5V                           | ++           |                   |            | Volts    |

| $\overline{}$ |                           |                   | VIN = VIH or VIL                                 |              | ł                 | 250        | щА       |

| ,             |                           | M                 |                                                  |              |                   |            |          |

VCC = MAX., VIN = 0.5V

VCC = MAX., VIN = 2.7V

VCC \* MAX., VIN = 5.5V

Note 5

A

Note 5

1. For conditions shown as MIN, or MAX, use the appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical limits are at V<sub>CC</sub> = 5.09, 25 °C ambins and maximum loading.

3. Actual injust currents = 0 Thirsed Load Current and maximum loading.

4. Actual injust currents = 0 Thirsed Load Current and Pacific See Loading Rules).

5. Injustic See Control of the Second See Control of the short circuit test should not exceed one second.

5. Control of the Second See Control of the Short Current See Current See Control of the Short Current See Control of the Short Current See Cu

VCC = MAX.

VCC - MAX.

A or B

A; or B;

S;

Cn м

Si

Cn

A. S<sub>j.</sub> M. A<sub>j</sub> at 4.5V; all other inputs grounded; outputs open B. S<sub>j.</sub> M at 4.5V; all other inputs grounded; outputs open.

## **DEFINITION OF TERMS**

#### SUBSCRIPT TERMS:

M HIGH, applying to a HIGH logic level or when used with  ${\rm V}_{\rm CC}$  to indicate high  $V_{CC}$  value.

Input LOW Current

Input HIGH Current

Input HIGH Current

**Power Supply Current**

**Output Short Circuit Current**

(Note 4) (Except A=B Output)

- $\boldsymbol{L}$  LOW, applying to LOW logic level or when used with  $\boldsymbol{V}_{CC}$  to Indicate low V<sub>CC</sub> value.

- O Output

٩L

ΉН

11

Isc

1cc

(Note 3)

(Note 3)

#### FUNCTIONAL TERMS:

- $\overline{A}_i$  Active LOW Data A inputs i = 0, 1, 2, 3.

- A = B Open collector output. This output can be 'AND tied' to other A = B outputs to form equivalence over complete word length.

- active LOW Data B inputs i = 0, 1, 2, 3.

- C. Active HIGH Carry In to nth ALU bit.

- Cn+4 Active HIGH Carry Out of n+4th ALU bit.

- F. Active LOW Data Outputs of ALU I = 0, 1, 2, 3.

- Fan-Out The logic HIGH or LOW output drive capability in terms of Input Unit Loads.

- & Active LOW carry generate output for use in multi-level lookahead schemes.

- 2-172M Mode input controls whether arithmetic or logic operation.

P Active LOW carry propagate output for use in multi-level low ahead schemes.

-20

--18

88

94

~1.6

-4 R

-64

-8

an

120

160

200

7

-55

-57

127

140

135

mA

μΑ

mA

mΑ

mA

$\mathbf{S}_i$  Control inputs determine the arithmetic or logic function obey i = 0, 1, 2, 3

Unit Load One T<sup>2</sup>L gate input load. In the HIGH state it is equal  $40\mu\text{A}$  at 2.4V and in the LOW state it is equal to 1.6mA at 0.4

### OPERATIONAL TERMS:

Am54

Am74

Am54

Am74

Am54

- $\mathbf{I}_{\mathrm{R}}$  Forward input load current, for unit input load.

- IOH Output HIGH current, forced out of output in VOH test.

- $I_{OL}$  Output LOW current, forced into the output in  $V_{OL}$  test.

- $I_{\rm IH}$  Reverse input load current with  $V_{\rm OH}$  applied to input.

Negative Current Current flowing out of the device.

- Positive Current Current flowing into the device.

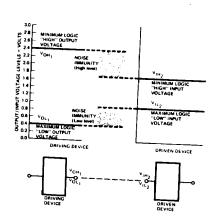

- VIH Minimum logic HIGH input voltage. Refer to figure 3.

- V<sub>IL</sub> Maximum logic LOW input voltage. Refer to figure 3. VOH Minimum logic HIGH output voltage with output HIGH curn IOH flowing out of output.

- Vol. Maximum logic LOW output voltage with output LOW curr Ici into output.

#### TEST TABLES

DIFF MODE TEST TABLE

FUNCTION INPUTS:  $S_1 = S_2 = 4.5 \text{ V}$ ,  $S_0 = S_3 = M = 0 \text{ V}$ Other Input Same Bit Other Data Inputs Output Gutput

| Pert-             | Under    | Apply<br>4.5 V | Apply<br>D V | Apply<br>4.5 V     | Apply<br>0 V            | Test      | torm |

|-------------------|----------|----------------|--------------|--------------------|-------------------------|-----------|------|

| l <sub>po</sub> . | <b>T</b> | Нопе           | В,           | Remaining<br>Ā     | Remaining<br>B, C,      | F,(, ≥ .) | 1    |

| <u>بوا</u>        | B,       | T.             | None         | Remaining<br>A     | Remaining<br>B. C.      | F,(,≥.)   | 2    |

| - <u> </u>        | Ā        | None           | Ē,           | Remaining<br>B, C, | Remaining<br>Ā          | Ē,,,      | 1    |

| l <sub>pd+</sub>  | B,       | Ā              | None         | Remaining<br>B, C, | Remaining<br>Ā          | F.,,      | 2    |

| Pod+              | Ä        | None           | B,           | None               | Remaining<br>A and B. C |           | 1    |

| l <sub>pd+</sub>  | Ē,       | Ā              | None         | None               | Remaining<br>A and B, C |           | 2    |

| t <sub>pd+</sub>  | Ā        | Ē,             | None         | None               | Remaining<br>A and B, C |           | 1    |

| t <sub>pd</sub> + | B,       | None           | Ā,           | None               | Remaining<br>A and 0, 0 |           | 2    |

| l <sub>pd</sub> - | Ā        | Ē,             | None         | Remaining          | Remainin                | A = 1     | 1    |

| t <sub>pd</sub> - | B,       | Ā,             | None         | Remaining<br>Ā     | Hemainin<br>B, C        | 0 A = 1   | 2    |

| l <sub>pd</sub>   | - Ā,     | Ē,             | None         | None               | Remainin<br>Ā and B,    |           | 2    |

| t <sub>pd</sub>   |          | None           | Ā            | None               | Remainin                |           | 1    |

Table 1

None None All And B

SUM MODE TEST TABLE

FUNCTION INPUTS S = S = 45 V. S = S = M = Q V

| 1                                                         | Input         | Other input<br>Same Bit |              | Other Date           | Output                  | Output        |               |

|-----------------------------------------------------------|---------------|-------------------------|--------------|----------------------|-------------------------|---------------|---------------|

| era-                                                      | Under<br>Test | Apply<br>4.5 V          | Apply<br>0 V | Apply<br>4.5 V       | Apply<br>Q V            | Under<br>Test | Wave-<br>form |

| ы.<br>эз                                                  | A             | 8                       | None         | Remaining<br>A and B | c                       | F( 1)         | . 1           |

| ю.<br>М                                                   | В             | A                       | None         | Remaining<br>A and B | С                       | F( - )        | , 1           |

| pd ·                                                      | À             | B,                      | None         | C,                   | Remaining<br>A and B    | F.            |               |

| pd v                                                      | В,            | Ā                       | None         | С                    | Remaining<br>Ā and B    | Ē,            | 1             |

| pd 1                                                      | Ã,            | B                       | None         | None                 | Remaining<br>Ā and B. C | P             | 1             |

| pd -                                                      | B,            | Ã,                      | None         | None                 | Remaining<br>A and B. C | P             | 1             |

| pa<br>pd r                                                | Ã,            | Nane                    | Ē            | Remaining<br>8       | Remaining<br>Ā C        | Ĝ             | 1             |

| t <sub>pn</sub><br>t <sub>pa</sub> .<br>t <sub>pd</sub> . | В,            | None                    | Ā            | Remaining<br>B       | Remaining<br>A. C.      | ē             | 1             |

| t <sub>pd</sub> .                                         | Ā             | None                    | В            | Remaining<br>B       | Remaining<br>Å, C       | С.            | , 2           |

| t <sub>pa</sub> ,                                         | B,            | None                    | Ã            | Remaining            | Remainin<br>A. C.       | 9 c.,         | . 2           |

| t <sub>pd</sub> .                                         | , c.          | None                    | :<br>Nane    | All<br>Ā             | Aii<br>B                | Any<br>or C   | F 1           |

| t <sub>pd</sub>                                           | i             | l                       |              | Table 2              |                         |               |               |

LOGIC MODE TEST TABLE

FUNCTION INPUTS  $S = S_i = M = 4.5 \text{ V}, S_j = S_1 = 0 \text{ V}$

|                              | input | Other Input<br>Same Bit |              | Other Date Inputs |                         |               | Output        |

|------------------------------|-------|-------------------------|--------------|-------------------|-------------------------|---------------|---------------|

|                              |       |                         | Apply<br>6 V | Apply<br>4.5 V    | Apply<br>0 V            | Under<br>Test | Wave-<br>lorm |

| $\mathbf{I}_{\mathrm{pd}}$ . | Ä     | i<br>None               | B            | None              | Remaining<br>A and B. C | F             | 1             |

| t <sub>pd</sub>              | Ē     | ·<br>i None             | Ä            | None              | Remaining<br>Ā and B. C | F             | 1             |

| t <sub>pd</sub>              | l     | 1                       |              | Table 3           |                         |               | • • •         |

SWITCHING CHARACTERISTICS  $V_{CC} = 5 \text{ V}, T_A = 25 ^{\circ}\text{C}, N = 10 \text{ (C}_L = 15 \text{ pF, R}_1 = 400 \Omega)$

None

Test Conditions See also Tables 1, 2, 3 Test Figure

| /ITCHIN                              | G CHARACIE                       | PUICITION CC.      |             | Test Conditions See also Tables 1, 2, 3                                                              | Min | Тур      | Max | Units      |

|--------------------------------------|----------------------------------|--------------------|-------------|------------------------------------------------------------------------------------------------------|-----|----------|-----|------------|

| ecomotor .                           | From (Input)                     | To (Output)        | Test Figure | See also raines 1, 2, 3                                                                              |     | 12       | 18  | A&         |

| t <sub>pd+</sub>                     | C,                               | C,,,               |             |                                                                                                      | 1   | 13       | 19  |            |

| -يوا                                 |                                  |                    |             | M = 0 V                                                                                              | ļ   | 13<br>12 | 18  | n <b>s</b> |

| <b>5</b> 0+                          | G,                               | F,                 |             | (SUM or DIFF mode)                                                                                   | i   | 13       | 19  |            |

| Çe-                                  |                                  |                    |             | $M = 0 \text{ V}, S_0 = S_1 = 45 \text{ V}.$                                                         | - 1 | 13       | 19  | คร         |

| <u> </u>                             | Ā, or B,                         | Ğ                  |             | $S_1 = S_2 = 0 \text{ V (SUM mode)}$                                                                 | +   | 17       | 25  |            |

|                                      |                                  | Ğ                  |             | $M = 0 \text{ V}, S_0 = S_1 = 0 \text{ V},$<br>$S_1 = S_2 = 4.5 \text{ V} \text{ (DIFF mode)}$       | 1   | 17       | 25  | ns         |

| ba-                                  | Ā, or B,                         | 4                  |             |                                                                                                      | 1   | 13       | 19  | ns.        |

| Þd+                                  |                                  | Ď                  |             | M = 0 V, S <sub>0</sub> = 5 <sub>1</sub> = 4 5 V<br>S <sub>1</sub> = S <sub>2</sub> = 0 V (SUM mode) | 1   | 15       | 22  |            |

| <del>уа-</del>                       | A <sub>i</sub> or B <sub>i</sub> |                    |             | M = 0 V, S <sub>0</sub> = S <sub>1</sub> = 0 V.                                                      | t   | 17       | 25  | n <b>s</b> |

| l <sub>pd+</sub>                     | Ā, or B,                         | ē                  |             | S, = S, = 4.5 V (DIPF mode)                                                                          |     | 17       | 25  |            |

| Ç <sub>pd</sub> -                    | 7 0 0                            |                    | 1 and 2     | M = 0 V, S <sub>0</sub> = S, = 45 V                                                                  | - 1 | 18       | 27  | ns         |

| Ļ <sub>d</sub> ,                     | Ā or B                           | <b>F</b> , (j ≥ i) |             | S = S = 0 V (SUM mode)                                                                               | 1   | 12       | 18  |            |

| t <sub>pd</sub> -                    |                                  |                    |             | $M = 0 V, S_1 = S_1 = 0 V.$                                                                          |     | 20       | 30  | ns         |

| ¹ <sub>pd+</sub>                     | Ā, or B,                         | F, (j ≥ 1)         |             | S. = S, = 4.5 V (DIFF mode)                                                                          |     | 16<br>19 | 29  |            |

| <b>L</b>                             |                                  |                    |             | $M = 0 \text{ V}, S_0 = S_1 = 4.5 \text{ V}.$                                                        |     | 20       | 30  | ns.        |

| <u> </u>                             | Ā, or B,                         | <b>F</b> , , ,     |             | S = Sz = 0 V (SUM mode)                                                                              | į.  | 24       | 36  |            |

| <u> </u>                             |                                  |                    |             | $M = 0 \text{ V. } S_0 = S_3 = 0 \text{ V.}$                                                         |     | 21       | 32  | ns.        |

| t <sub>pd+</sub>                     | Ā, or Ē,                         | Ē,₊.               |             | S, = S, = 4.5 V (DIFF mode)                                                                          | ļ   | 19       | 29  | na.        |

| <u> </u>                             |                                  | F,                 |             | M = 4.5 V (LOGIC mode)                                                                               | 1   | 19       | 29  | ***        |

| l <sub>pd+</sub><br>l <sub>pd−</sub> | Ã, or B,                         | •                  |             | M = 0 V, S <sub>0</sub> = S <sub>1</sub> = 4.5 V,                                                    | 1   | 17       | 25  | na.        |

| l <sub>pd+</sub>                     | 15                               | C                  |             | $M = 0 \text{ V. } S_0 = S_1 = 4.3 \text{ V.}$<br>$S_1 = S_2 = 0 \text{ V (SUM mode)}$               | - 1 | 20       | 30  |            |

| l <sub>pd</sub> -                    | – Ā; or B,                       | V. + +             |             | M = 0 V. S. = S. = 0 V.                                                                              |     | 21       | 32  | ns         |

| l <sub>pd+</sub>                     | Ã, or B,                         | C,                 | Į.          | S = S, = 4.5 V (DIFF mode)                                                                           |     | 20       | 30  |            |

| <b>Ş</b> a-                          | 7,00                             |                    |             | M = 0 V S. = S. = 0 V.                                                                               | - 1 | 25       | 37  | ns.        |

| t <sub>p4+</sub>                     | Ã, or B,                         | A = B              |             | S = S = 4.5 V (DIFF mode)                                                                            |     | 21       | 32  |            |

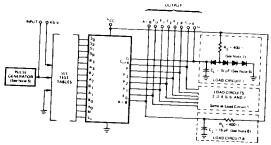

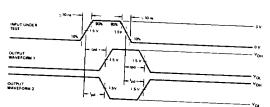

# SWITCHING TIME TEST CIRCUIT AND WAVEFORMS

Figure 1

- Note 5. The pulse generator has the following characteristics: frequency = 1 MHz,  $Z_{\rm rel} \approx 50~\Omega$ . 6. C<sub>c</sub> includes probe and jig capacitance. 7. All diodes are 1N3064.

Figure 2

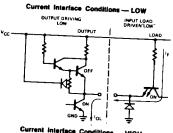

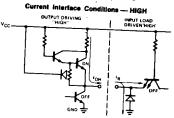

# INPUT/OUTPUT INTERFACE CONDITIONS

## Voltage Interface Conditions -- LOW & HIGH

Figure 3

#### MSI INTERFACING RULES

| Interfacing<br>Digital Family           | Equivalent<br>Input Unit Lose<br>HIGH LOW |   |  |

|-----------------------------------------|-------------------------------------------|---|--|

| Advanced Micro Devices 54/7400 Series   | 1_                                        | 1 |  |

| Advanced Micro Devices 9300/2500 Series | 1                                         | 1 |  |

| FSC Series 9300                         | 11                                        | 1 |  |

| Ti Series 54/7400                       | 1                                         | 1 |  |

| Signetics Series 8200                   | 2                                         | 2 |  |

| National Series DM 75/85                | 1                                         | 1 |  |

| OTL Series 930                          | 12                                        | 1 |  |

Table 4

#### USER NOTES

- 1. Arithmetic operations are performed on a word basis.

- 2. Logic operations are performed on a bit basis.

- Arithmetic in 1's complement arithmetic requires an end around carry.

- 4. Subtraction in 2's complement arithmetic requires a carry in  $(C_n = \text{HIGH})$  active LOW case,  $(\overline{C}_n = \text{LOW})$  active HIGH case.

## Am54/74181 LOADING RULES (in unit loads)

|                       |           |                    | Output         | Output Drive  |  |  |

|-----------------------|-----------|--------------------|----------------|---------------|--|--|

| Input/Output          | Pin No.'s | Input<br>Unit Load | Output<br>HIGH | Output<br>LOW |  |  |

| <b>B</b> <sub>0</sub> | 1         | 3                  | _              |               |  |  |

| Ã                     | 2         | 3                  |                |               |  |  |

| s,                    | 3         | 4                  | -              | -             |  |  |

| S <sub>2</sub>        | 4         | 4                  |                |               |  |  |

| s                     | 5         | 4                  | -              |               |  |  |

| So                    | 6         | 4                  |                | _             |  |  |

| C.                    | . 7       | 5                  |                |               |  |  |

| М.                    | . 8       | 1                  |                |               |  |  |

| F <sub>0</sub>        | 9         |                    | 20             | 10            |  |  |

| F                     | 10        | _                  | 20             | 10            |  |  |

| F,                    | 11        |                    | 20             | 10            |  |  |

| GND                   | 12        | _                  | _              |               |  |  |

| F,                    | 13        |                    | 20             | 10            |  |  |

| A = B                 | 14        | _                  | O/C            | 10            |  |  |

| <b>p</b>              | 15        | -                  | 20             | 10            |  |  |

| C.,,                  | 16        |                    | 20             | 10            |  |  |

| Ğ                     | 17        | -                  | 20             | 10            |  |  |

| ₿,                    | 18        | 3                  | _              | _             |  |  |

|                       | 19        | 3                  |                | _             |  |  |

| <b>B</b> <sub>2</sub> | 20        | 3                  | -              | _             |  |  |

| Ä,                    | 21        | 3                  |                | _             |  |  |

| B,                    | 22        | 3                  | _              | _             |  |  |

| Ā,                    | 23        | 3                  | _              | -             |  |  |

| V <sub>CC</sub>       | 24        | -                  | _              |               |  |  |

O/C = Open Collector

A unit load is defined as  $40\,\mu\text{A}$  at 2.4V and 1.6mA at 0.4V. Table 5

#### **OPERATION TABLE**

| Control Inputs Acti |     |          | -                                                    | Active LOW inputs and | Outputs                                  | Active HIGH Inputs and Outputs |                    |  |  |  |

|---------------------|-----|----------|------------------------------------------------------|-----------------------|------------------------------------------|--------------------------------|--------------------|--|--|--|

| S, S, S, S,         |     |          | Arithmetic (M = L, C <sub>a</sub> = L) Logic (M = H) |                       | Arithmetic (M = L, $\overline{C}_n$ = H) | Logic (M = H)                  |                    |  |  |  |

| B <sub>0</sub> :    | B . | 8,       | 8,                                                   | A minus 1             | Ā                                        | A                              | Ā                  |  |  |  |

| L                   | L   | <u>L</u> | L                                                    |                       | ĀB                                       | A + B                          | A + B              |  |  |  |

| Н                   | L   | L        | L                                                    | AB minus 1            | 1                                        | A + B                          | ĀB                 |  |  |  |

| L                   | н   | L        | L.                                                   | AB minus 1            | Ä+B                                      |                                |                    |  |  |  |

| н                   | н   | 1        | ī                                                    | minus 1 (2's comp.)   | Logic '1'                                | minus 1 (2's comp.)            | Logic '0'          |  |  |  |

| <del></del>         | -   | H        | -                                                    | A plus (A + B)        | A + B                                    | A plus AB                      | ĀB                 |  |  |  |

| -                   | ÷   |          |                                                      | AB plus [A + B]       | В                                        | AB plus [A + B]                | В                  |  |  |  |

| н                   | -   | <u>H</u> |                                                      | A minus B mlnus 1     | A (D B                                   | A minus B minus 1              | A ⊕ B              |  |  |  |

| _                   | Н   | н        |                                                      | A + B                 | A+B                                      | AB minus 1                     | ΑB                 |  |  |  |

| Н                   | Н   | н        | L                                                    |                       | ĀB                                       | A plus AB                      | $\overline{A} + B$ |  |  |  |

| L                   | L   | L        | H                                                    | A plus [A + B]        |                                          | A plus B                       | Ā⊕B                |  |  |  |

| н                   | τ   | L        | н                                                    | A plus B              | A⊕B                                      | 1                              | <b>↓</b>           |  |  |  |

| Ë                   | -   | 1        | н                                                    | AB plus [A + B]       | В                                        | AB plus [A + B]                | В                  |  |  |  |

|                     |     | -        | Н                                                    | A+B                   | A + B                                    | AB minus 1                     | AB                 |  |  |  |

| Н                   | -   |          |                                                      |                       | Logic '0'                                | A plus A (2 x A)               | Logic '1'          |  |  |  |

| L                   | L   |          | H                                                    | A plus A (2 x A)      | AB                                       | A plus [A + B]                 | A + B              |  |  |  |

| Н                   | L   | н        | H                                                    | A plus AB             |                                          | A plus (A + B)                 | A + B              |  |  |  |

| L                   | Н   | Н        | н                                                    | A plus AB             | AB                                       |                                | +A                 |  |  |  |

| ы                   | Н   |          | Н                                                    | Α                     | A                                        | A minus 1                      |                    |  |  |  |

L =LOW Voltage Level

H =HIGH Voltage Level

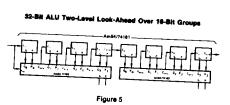

# Am54/74181 APPLICATIONS

Typical addition limes for various configurations are given in the table below. Subtraction filmes are approximately 5 me ionger.

16-Bit ALU Rippie Carry

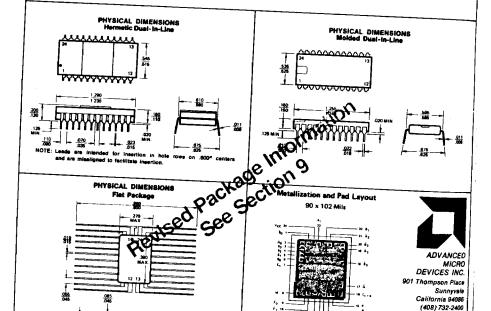

NOTE: Leads are gold plated kovar.

2-176

TYPICAL ADDITION TIMES

| TIPICAL ADDITION TIMES |                    |                 |                |                |  |  |  |  |  |

|------------------------|--------------------|-----------------|----------------|----------------|--|--|--|--|--|

| No. of                 | Total              | Add Time        | Packa          | ge Count       |  |  |  |  |  |

| Bite                   | Addition Time (ne) | Per Bit<br>(ne) | Am<br>54/74181 | Am<br>54/74182 |  |  |  |  |  |

| 4                      | 19                 | 4.8             | 1              | 24774164       |  |  |  |  |  |

| 8                      | 31                 | 3.9             | 2              | i              |  |  |  |  |  |

| 12                     | 43                 | 3.6             | 3              | f              |  |  |  |  |  |

| 12                     | 31                 | 2.6             | 3              |                |  |  |  |  |  |

| 16                     | 55                 | 3.5             |                | 1              |  |  |  |  |  |

| 16                     | 31                 | 2.0             |                |                |  |  |  |  |  |

| 32                     | 103                | 3.2             | 8              | 1              |  |  |  |  |  |

| 32                     | 79                 | 2.5             | - 1            |                |  |  |  |  |  |

| 32                     | 56                 | 1.8             | 8              | 1              |  |  |  |  |  |

| 48                     | 151                | 3.2             | 8<br>12        | 2              |  |  |  |  |  |

| 48                     | 127                | 2.6             |                |                |  |  |  |  |  |

| 48                     | 104                | 2.2             | 12             | 1              |  |  |  |  |  |

| 48                     | 81                 | 1.7             | 12             | 2              |  |  |  |  |  |

| 48                     | 57                 | 1.2             | 12             | 3              |  |  |  |  |  |

| 64                     | 199                | 3.1             | 12             | 4              |  |  |  |  |  |

| 64                     | 152                | 2.4             | 16             |                |  |  |  |  |  |

| 64                     | 129                | 2.0             | 16             | 2<br>3         |  |  |  |  |  |

| 64                     | 106                | 1.7             | 16             |                |  |  |  |  |  |

| 64                     | 57                 | 0.9             | 16             | 4              |  |  |  |  |  |

|                        | L                  | 0.8             | 16             | 5              |  |  |  |  |  |

Table 7

TWX: 910-339-9280

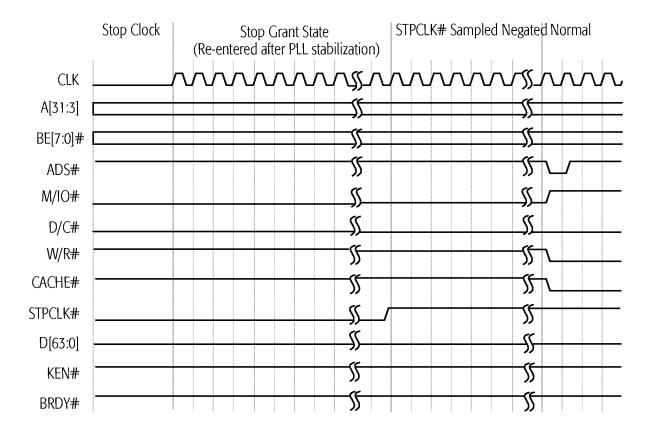

Figure 75. Stop Grant and Stop Clock Modes, Part 2

21850E/0-November 1998

# INIT-Initiated Transition from Protected Mode to Real Mode

INIT is typically asserted in response to a BIOS interrupt that writes to an I/O port. This interrupt is often in response to a Ctrl-Alt-Del keyboard input. The BIOS writes to a port (similar to port 64h in the keyboard controller) that asserts INIT. INIT is also used to support 80286 software that must return to Real mode after accessing extended memory in Protected mode.

The assertion of INIT causes the processor to empty its pipelines, initialize most of its internal state, and branch to address FFFF\_FFF0h—the same instruction execution starting point used after RESET. Unlike RESET, the processor preserves the contents of its caches, the floating-point state, the MMX state, Model-Specific Registers (MSRs), the CD and NW bits of the CR0 register, the time stamp counter, and other specific internal resources.

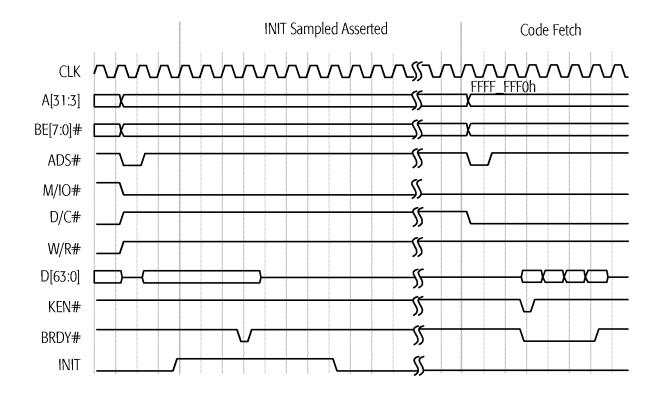

Figure 76 shows an example in which the operating system writes to an I/O port, causing the system logic to assert INIT. The sampling of INIT asserted starts an extended microcode sequence that terminates with a code fetch from FFFF\_FFFOh, the reset location. INIT is sampled on every clock edge but is not recognized until the next instruction boundary. During an I/O write cycle, it must be sampled asserted a minimum of three clock edges before BRDY# is sampled asserted if it is to be recognized on the boundary between the I/O write instruction and the following instruction. If INIT is asserted synchronously, it can be asserted for a minimum of one clock. If it is asserted asynchronously, it must have been negated for a minimum of two clocks, followed by an assertion of a minimum of two clocks.

Figure 76. INIT-Initiated Transition from Protected Mode to Real Mode

21850E/0-November 1998

# **6** Power-on Configuration and Initialization

On power-on the system logic must reset the AMD-K6-2 processor by asserting the RESET signal. When the processor samples RESET asserted, it immediately flushes and initializes all internal resources and its internal state, including its pipelines and caches, the floating-point state, the MMX and 3DNow! states, and all registers. Then the processor jumps to address FFFF FFF0h to start instruction execution.

# 6.1 Signals Sampled During the Falling Transition of RESET

FLUSH#

FLUSH# is sampled on the falling transition of RESET to determine if the processor begins normal instruction execution or enters Tri-State Test mode. If FLUSH# is High during the falling transition of RESET, the processor unconditionally runs its Built-In Self Test (BIST), performs the normal reset functions, then jumps to address FFFF\_FFF0h to start instruction execution. (See "Built-In Self-Test (BIST)" on page 217 for more details.) If FLUSH# is Low during the falling transition of RESET, the processor enters Tri-State Test mode. (See "Tri-State Test Mode" on page 218 and "FLUSH# (Cache Flush)" on page 103 for more details.)

**BF[2:0]**

The internal operating frequency of the processor is determined by the state of the bus frequency signals BF[2:0] when they are sampled during the falling transition of RESET. The frequency of the CLK input signal is multiplied internally by a ratio defined by BF[2:0]. (See "BF[2:0] (Bus Frequency)" on page 92 for the processor-clock to bus-clock ratios.)

**BRDYC#**

BRDYC# is sampled on the falling transition of RESET to configure the drive strength of A[20:3], ADS#, HITM#, and W/R#. If BRDYC# is Low during the fall of RESET, these outputs are configured using higher drive strengths than the standard strength. If BRDYC# is High during the fall of RESET, the standard strength is selected. (See "BRDYC# (Burst Ready Copy)" on page 95 for more details.)

21850E/0-November 1998

# **6.2 RESET Requirements**

During the initial power-on reset of the processor, RESET must remain asserted for a minimum of 1.0 ms after CLK and  $V_{CC}$  reach specification. (See "CLK Switching Characteristics" on page 255 for clock specifications. See "Electrical Data" on page 247 for  $V_{CC}$  specifications.)

During a warm reset while CLK and  $V_{\rm CC}$  are within specification, RESET must remain asserted for a minimum of 15 clocks prior to its negation.

# 6.3 State of Processor After RESET

# **Output Signals**

Table 31 shows the state of all processor outputs and bidirectional signals immediately after RESET is sampled asserted.

**Table 31. Output Signal State After RESET**

| Signal           | State    | Signal   | State    |

|------------------|----------|----------|----------|

| A[31:3], AP      | Floating | LOCK#    | High     |

| ADS#, ADSC#      | High     | M/IO#    | Low      |

| APCHK#           | High     | PCD      | Low      |

| BE[7:0]#         | Floating | PCHK#    | High     |

| BREQ             | Low      | PWT      | Low      |

| CACHE#           | High     | SCYC     | Low      |

| D/C#             | Low      | SMIACT#  | High     |

| D[63:0], DP[7:0] | Floating | TDO      | Floating |

| FERR#            | High     | VCC2DET  | Low      |

| HIT#             | High     | VCC2H/L# | Low      |

| HITM#            | High     | W/R#     | Low      |

| HLDA             | Low      | _        | _        |

# **Registers**

Table 32 on page 175 shows the state of all architecture registers and Model-Specific Registers (MSRs) after the processor has completed its initialization due to the recognition of the assertion of RESET.