|                                                                                       | · • • · · · · · · · · · · · · · · · · ·                                          |                                    |                               |                                                       |         |         | R   | EVIS:        | IONS |           |                    |              |             |                  |                   |           |           |              |   |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------|-------------------------------|-------------------------------------------------------|---------|---------|-----|--------------|------|-----------|--------------------|--------------|-------------|------------------|-------------------|-----------|-----------|--------------|---|

| LTR                                                                                   |                                                                                  |                                    |                               | D                                                     | ESCR    | IPTI    | ON  |              |      |           |                    | DAT          | E (YR       | -MO-DA           | )                 |           | APPR      |              |   |

| A                                                                                     | code<br>Modif                                                                    | devic<br>65896<br>ied fi<br>ghout. | as ve<br>gure                 | ndor                                                  | for     | dev     | ice | type         | 01.  |           |                    |              | 92-0        | 8-04             |                   | M.        | 1         | l'oe         |   |

|                                                                                       |                                                                                  |                                    |                               |                                                       |         |         |     |              |      |           |                    |              |             |                  |                   |           |           |              |   |

|                                                                                       |                                                                                  |                                    |                               |                                                       |         |         |     |              |      |           |                    |              |             |                  |                   |           |           |              |   |

| REV<br>SHEET                                                                          |                                                                                  |                                    |                               |                                                       |         |         |     |              |      |           |                    |              |             |                  |                   |           |           |              |   |

| SHEET                                                                                 |                                                                                  |                                    |                               |                                                       |         |         |     |              |      |           |                    |              |             |                  |                   |           |           |              |   |

| SHEET<br>REV<br>SHEET                                                                 | TIIS                                                                             |                                    | REV                           |                                                       |         | A       | A   | A            | A    | A         | A                  | A            | A           | A                | A                 | A         | A         | A            |   |

| SHEET REV SHEET REV STAT                                                              |                                                                                  |                                    | REV                           |                                                       |         | A 1     | A 2 | A 3          | A 4  | A 5       | A 6                | A 7          | A 8         | A 9              | A 10              | A 11      | A 12      | A 13         | 1 |

| SHEET                                                                                 | rs<br>————                                                                       |                                    | SHE                           | ET<br>RED BY                                          | r A. I  | 1       |     | <del> </del> | 4    | 5         | 6<br>SE EI         | 7<br>LECTR   | 8<br>ONIC   | 9<br>S SU        | 10                | 11<br>CEN | 12        | <del> </del> | - |

| SHEET REV SHEET REV STAT OF SHEET PMIC N/A STANI MII DR                               | DARDIZ<br>LITARY<br>RAWING                                                       | ILABLE                             | SHE<br>PREPAR<br>Chris        | EET RED BY BY H. Noh                                  | er A. I | 1       |     | <del> </del> | 4 DB | 5<br>ROC: | 6 SE EI I IRCU COR | 7 LECTROAYTO | 8 ONIC      | 9<br>S SU<br>HIO | 10<br>PPLY<br>454 | CENT      | 12<br>TER | 13           | 1 |

| SHEET REV SHEET REV STAT OF SHEET PMIC N/A STANI MII DR THIS DRAWI FOR USE BY AND AGE | DARDIZ<br>LITARY<br>RAWING<br>ING IS AVA<br>ALL DEPAR<br>ENCIES OF<br>ENT OF DEF | ILABLE<br>TMENTS<br>THE            | SHE PREPAR Chris CHECKE Tim F | RED BY<br>stophe<br>ED BY<br>H. Noh<br>VED BY<br>Cool | PROVAL  | 1 Rauch | 2   | <del> </del> | 4 DB | FOC:      | 6 SE EI IRCU COF   | 7 LECTROAYTO | 8 ONICON, O | 9<br>S SU<br>HIO | PPLY<br>454       | CENTA44   | 12<br>TER | -BIT         | 1 |

## 1. SCOPE

- 1.1 <u>Scope</u>. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

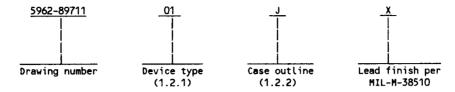

- 1.2 Part or Identifying Number (PIN). The complete PIN shall be as shown in the following example:

1.2.1 Device type(s). The device type(s) shall identify the circuit function as follows:

| Device type | Generic number   | <u>Circuit function</u>                | Correlation Rate |

|-------------|------------------|----------------------------------------|------------------|

| 01          | TMC2023V, L10C23 | CMOS digital output correlator, 64-bit | 25 MHz           |

| 02          | TMC2023V1        | CMOS digital output correlator, 64-bit | 30 MHz           |

| 03          | TMC2023V2        | CMOS digital output correlator, 64-bit | 35 MHz           |

| 04          | TMC2023V3        | CMOS digital output correlator, 64-bit | 50 MHz           |

1.2.2 Case outline(s). The case outline(s) shall be as designated in MIL-STD-1835, and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style               |

|----------------|------------------------|------------------|-----------------------------|

| J              | GDIP1-T24 or CDIP2-T24 | 24               | Dual-in-line package        |

| L              | GDIP3-T24 or CDIP4-T24 | 24               | Dual-in-line package        |

| 3              | cqcc1-N28              | 28               | Square chip carrier package |

1.3 Absolute maximum ratings.

| Supply voltage range                                      | -0.5 V dc to +7.0 V dc                                                |

|-----------------------------------------------------------|-----------------------------------------------------------------------|

|                                                           | $-0.5$ V dc to $V_{DD}$ + 0.5 V dc $-0.5$ V dc to $V_{DD}$ + 0.5 V dc |

| Applied output voltage range 1/                           |                                                                       |

| Forced output current range 2/                            | -3.0 mA to +6.0 mA                                                    |

| Output short circuit duration $\underline{3}/$            | 1.0 second                                                            |

| Power dissipation, unloaded (P <sub>D</sub> ): <u>4</u> / |                                                                       |

| Device type 01                                            | 305 mW                                                                |

| Device type 02                                            | 415 mW                                                                |

| Device type 03                                            | 415 mW                                                                |

| Device type 04                                            | 550 mW                                                                |

| Lead temperature (soldering, 10 seconds)                  | +300°C                                                                |

| Thermal resistance, junction-to-case $(\Theta_{JC})$ :    |                                                                       |

| Case outlines J, L, and 3                                 | See MIL-STD-1835                                                      |

| Junction temperature (T <sub>J</sub> )                    | +175°C                                                                |

- 1/ Applied voltage must be current-limited to specified range and measured with respect to ground.

- 2/ Forcing voltage must be limited to specified range.

- 3/ Applies to single output in high state to ground.

- $\underline{4}$ / Must withstand the added PD due to short circuit test; e.g., IOS.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89711 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET 2    |

| 1.4 Recommended operating conditions.                                                                                                             |                  |                                         |                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|------------------------------------|

| Supply voltage range (V <sub>DD</sub> )                                                                                                           |                  |                                         | .5 V dc to 5.5 V dc                |

| Device type O1                                                                                                                                    |                  |                                         | ons minimum<br>Ans minimum         |

| Device type 02                                                                                                                                    |                  |                                         | ns minimum<br>ns minimum           |

| Device type 04                                                                                                                                    |                  |                                         | ns minimum                         |

| Clock pulse width, high, clocks, LDR (t <sub>PWH</sub> ):                                                                                         |                  | 11                                      | ns minimum                         |

| Device type 01                                                                                                                                    |                  |                                         | 4 ns minimum                       |

|                                                                                                                                                   |                  | 14                                      | 4 ns minimum                       |

|                                                                                                                                                   |                  | 8                                       | ns minimum                         |

| Data input setup time, correlator, IO <sub>O-6</sub> (t <sub>SCOR</sub> ):  Device type 01                                                        |                  | 10                                      | 4 ns minimum                       |

| Device type 02                                                                                                                                    |                  |                                         | ns minimum                         |

| Device type 03                                                                                                                                    |                  |                                         | ) ns minimum                       |

| Device type O4                                                                                                                                    |                  |                                         | ) ns minimum                       |

|                                                                                                                                                   | N ``SSR''        |                                         | 3 ns minimum                       |

| Device type O2                                                                                                                                    |                  | · .                                     | ns minimum                         |

| Device type O3                                                                                                                                    |                  |                                         | ) ns minimum<br>ns minimum         |

| Device type O4                                                                                                                                    |                  |                                         | IIS III II I III III III           |

| Data input hold time, $A_{TN}$ , $B_{TN}$ , $M_{TN}$ , $IO_{O-6}$ ( $t_H$ ).                                                                      |                  | 0                                       | ns minimum                         |

| Data input hold time, $A_{IN}$ , $B_{IN}$ , $M_{IN}$ , $IO_{O-6}$ (th) . Input low voltage ( $V_{IL}$ )                                           |                  | 0                                       | .8 V dc maximum                    |

| Input high voltage (V <sub>IH</sub> )                                                                                                             |                  |                                         | .0 V dc minimum<br>.4 V dc minimum |

| Output low current (I <sub>OL</sub> )                                                                                                             |                  | 4                                       | O mA maximum                       |

| Output high current $(I_{Ou})$                                                                                                                    |                  |                                         | 2.0 mA minimum                     |

| Case operating temperature range (T <sub>C</sub> )                                                                                                |                  |                                         | 55°C to +125°C                     |

| the extent specified herein.  SPECIFICATION                                                                                                       |                  |                                         |                                    |

| MILITARY                                                                                                                                          |                  |                                         |                                    |

| MIL-M-38510 - Microcircuits, General Spec                                                                                                         | ification for.   |                                         |                                    |

| STANDARD                                                                                                                                          |                  |                                         |                                    |

| MILITARY                                                                                                                                          |                  |                                         |                                    |

| MIL-STD-883 - Test Methods and Procedures MIL-STD-1835 - Microcircuit Case Outlines                                                               | for Microelectro | onics.                                  |                                    |

| BULLETIN                                                                                                                                          |                  |                                         |                                    |

| MILITARY                                                                                                                                          |                  |                                         |                                    |

| MIL-BUL-103 - List of Standardized Milita                                                                                                         | ry Drawings (SMD | 's).                                    |                                    |

| (Copies of the specification, standard, and bulletin requ<br>specific acquisition functions should be obtained from the<br>contracting activity.) |                  |                                         | <b>:</b>                           |

| 2.2 Order of precedence. In the event of a conflict bet<br>references cited herein, the text of this drawing shall tak                            |                  | this drawing and the                    |                                    |

| STANDARDIZED<br>MILITARY DRAWING                                                                                                                  | SIZE<br>A        | *************************************** | 5962-89711                         |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444                                                                                              |                  | REVISION LEVEL                          | SHEET                              |

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.2 herein.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

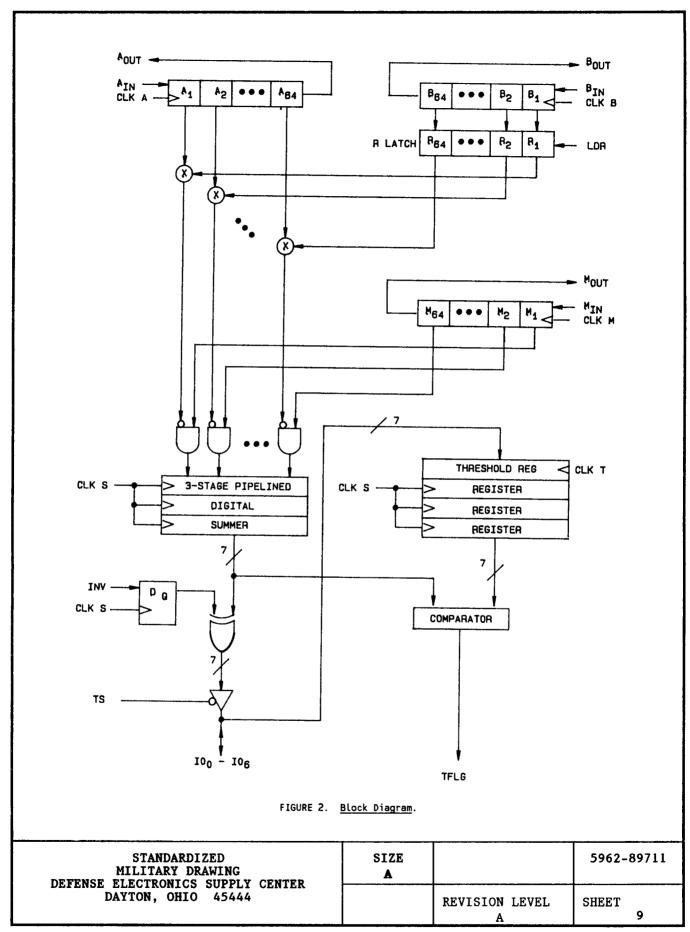

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 2.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103 (see 6.7 herein).

- 3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7 herein). The certificate of compliance submitted to DESC-ECC prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change</u>. Notification of change to DESC-ECC shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.9 <u>Verification and review</u>. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

## 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89711 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>4 |

| Test                                                             | Symbol           |                                                              | tions                                                | Group A   | Device | Lim | its  | Unit |  |

|------------------------------------------------------------------|------------------|--------------------------------------------------------------|------------------------------------------------------|-----------|--------|-----|------|------|--|

|                                                                  |                  | -55°C ≤ T<br>4.5 V ≤ V<br>unless otherwis                    | $0.5 \le 5.5 \text{ V}$ Se specified $1/$            | subgroups | type   | Min | Max  |      |  |

| Quiescent supply<br>current                                      | POOG             | V <sub>DD</sub> = 5.5 V, V<br>TS = 5.0 V                     | / <sub>IN</sub> = 0 V,                               | 1,2,3     | All    |     | 10   | mA   |  |

| Dynamic supply                                                   | I <sub>DD</sub>  | V <sub>DD</sub> = 5.5 V,<br>TS = 5.0 V                       | f = 25 MHz                                           | 1,2,3     | 01     |     | 55   | mA   |  |

| current                                                          |                  | 15 - 3.0 V                                                   | f = 30 MHz <u>2</u> /                                |           | 02     |     | 75   | mA   |  |

|                                                                  |                  |                                                              | f = 35 MHz <u>2</u> /                                | 7         | 03     |     | 75   | mA   |  |

|                                                                  |                  |                                                              | f = 50 MHz <u>2</u> /                                | 1         | 04     |     | 100  | mA   |  |

| Input low current                                                | IIL              | V <sub>DD</sub> = 5.5 V, V                                   | ' <sub>IN</sub> = 0 V                                | 1,2,3     | ALL    |     | -20  | μА   |  |

| Input high current                                               | IIH              | V <sub>DD</sub> = 5.5 V, V                                   | IN = VDD                                             | 1,2,3     | ALL    |     | +20  | μА   |  |

| Output low voltage                                               | V <sub>OL</sub>  | V <sub>DD</sub> = 4.5 V,                                     | 1 <sub>OL</sub> = 4.0 mA                             | 1,2,3     | ALL    |     | 0.4  | ٧    |  |

| Output high voltage                                              | v <sub>OH</sub>  | V <sub>IN</sub> = 0.8 V,                                     | $I_{OL} = 4.0 \text{ mA}$ $I_{OH} = -2.0 \text{ mA}$ | 1,2,3     | ALL    | 2.4 |      | ٧    |  |

| Three-state output<br>leakage current,<br>output low <u>3</u> /  | Iozl             | V <sub>DD</sub> = 5.5 V, V                                   | 'IN = 0 V                                            | 1,2,3     | ALL    |     | -40  | μΑ   |  |

| Three-state output<br>leakage current,<br>output high <u>3</u> / | Іохн             | V <sub>DD</sub> = 5.5 V, V                                   | IN = 5.5 V                                           | 1,2,3     | All    |     | +40  | μА   |  |

| Output short-circuit<br>current <u>2</u> / <u>4</u> /            | Ios              | V <sub>DD</sub> = 5.5 V, or one pin to gro<br>t = 1.0 sec ma | und,                                                 | 1,2,3     | All    |     | -125 | mA   |  |

| Input capacitance                                                | c <sub>IN</sub>  | T <sub>A</sub> = 25°C, f = see 4.3.1c                        | 1.0 MHz,                                             | 4         | All    |     | 10   | pF   |  |

| Output capacitance                                               | COUT             | T <sub>A</sub> = 25°C, f = see 4.3.1c                        | 1.0 MHz,                                             | 4         | All    |     | 10   | pF   |  |

| Functional tests                                                 |                  | V <sub>DD</sub> = 5.0 V, s                                   | ee 4.3.1d                                            | 7,8       | ALL    |     |      |      |  |

| Clk frequency,                                                   | F <sub>CLK</sub> | V <sub>DD</sub> = 4.5 V, s                                   | ee figure 3                                          | 7,8       | 01     | 25  |      | MHz  |  |

| correlator, shift register and flag                              |                  |                                                              |                                                      |           | 02     | 30  |      | MHz  |  |

| <u>5</u> / <u>6</u> /                                            |                  |                                                              |                                                      |           | 03     | 35  |      | MHz  |  |

|                                                                  |                  |                                                              |                                                      | 1         | 04     | 50  |      | MHz  |  |

See footnotes at end of table.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89711 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET 5    |

| Test                               | Symbol            | Conditions $-55^{\circ}C \leq T_{-} \leq +125^{\circ}C$                                                               | Group A   | Device<br>type | Limits       |           | Unit     |

|------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|-----------|----------------|--------------|-----------|----------|

|                                    |                   | $-55^{\circ}$ C ≤ T <sub>C</sub> ≤ +125°C<br>4.5 V ≤ V <sub>DD</sub> ≤ 5.5 V<br>unless otherwise specified <u>1</u> / | <br> <br> |                | Min          | <br>  Max |          |

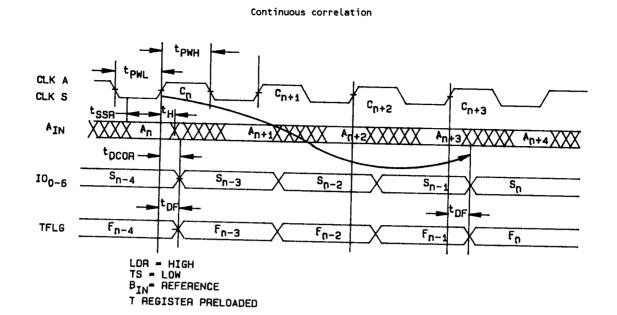

| Digital output delay, correlator   | t <sub>DCOR</sub> | $V_{DD} = 4.5 \text{ V, see figure 3}$                                                                                | 9,10,11   | 01             | 4 <u>2</u> / | 25        | ns       |

| <u>5</u> /                         |                   |                                                                                                                       |           | 02             | 4 2/         | 20        | ns       |

|                                    |                   |                                                                                                                       |           | 03             | 4 2/         | 20        | ns       |

|                                    | j                 |                                                                                                                       | Ì         | 04             | 4 2/         | 18        | ns       |

| Digital output delay, shift        | tDSR              |                                                                                                                       | 9,10,11   | 01             | 4 2/         | 25        | ns       |

| register <u>5</u> /                |                   |                                                                                                                       |           | 02             | 4 2/         | 22        | ns<br>ns |

|                                    |                   |                                                                                                                       | -         | 03             | 4 2/         | 22        |          |

|                                    |                   |                                                                                                                       |           | 04             | 4 2/         | 20        |          |

| Digital output delay, flag 5/      | t <sub>DF</sub>   | -<br> <br>                                                                                                            | 9,10,11   | 01             | 4 2/         | 22        | ns       |

| ====, <u>=</u> ,                   | į                 |                                                                                                                       |           | 02             | 4 <u>2</u> / | 19        | ns       |

|                                    |                   |                                                                                                                       |           | 03             | 4 2/         | 19        | ns       |

|                                    | İ                 |                                                                                                                       |           | 04             | 4 2/         | 17        | ns       |

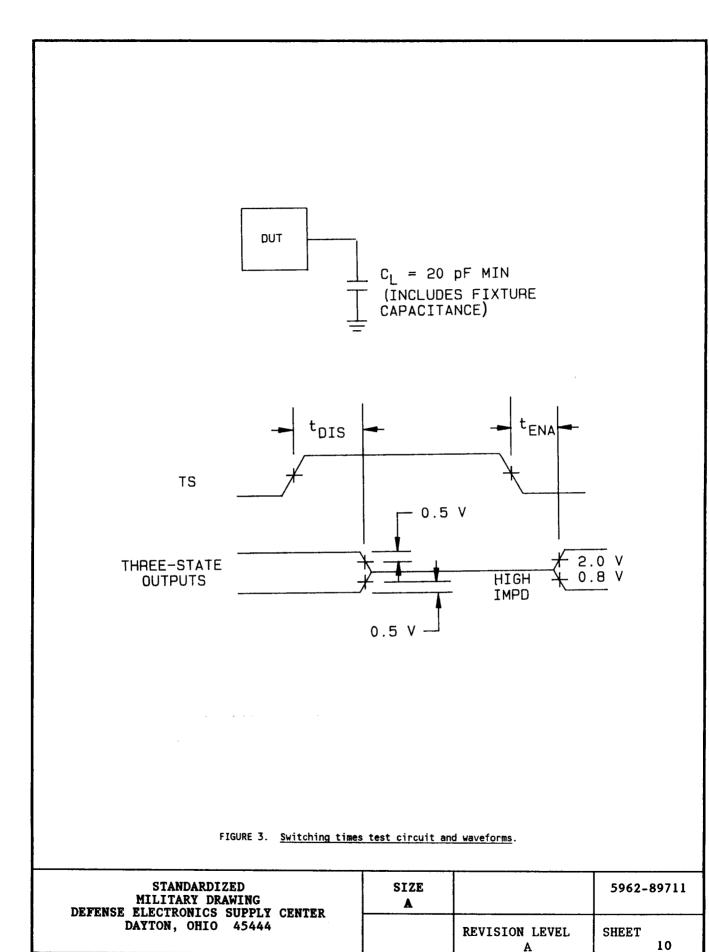

| Three-state output<br>enable delay | t <sub>ENA</sub>  |                                                                                                                       | 9,10,11   | 01             |              | 25        | ns       |

| enable detay                       | }<br>             |                                                                                                                       |           | 02             |              | 20        | ns       |

|                                    |                   |                                                                                                                       |           | 03             |              | 20        | ns       |

|                                    |                   | !<br> <br>                                                                                                            |           | 04             |              | 18        | ns       |

| Three-state output disable delay   | tDIS              | 7<br> <br>                                                                                                            | 9,10,11   | 01             |              | 24        | ns       |

|                                    |                   |                                                                                                                       |           | 02             |              | 18        | ns       |

|                                    |                   |                                                                                                                       |           | 03             |              | 18        | ns       |

|                                    |                   | Ì                                                                                                                     |           | 04             |              | 16        | ns       |

- $\underline{1}/$  All testing will be performed under worst-case conditions unless otherwise specified.

- $\underline{2}/\hspace{0.1in}$  If not tested, shall be guaranteed to the limits specified in table I.

- $\underline{3}$ / Due to the  $\mathrm{IO_{0-6}}$  and T register interconnections, these values are the  $\mathrm{I_{IH}}$  and  $\mathrm{I_{IL}}$  of the T register outputs.

- $\underline{4}/$  Not more than one output should be shorted at a time. Maximum duration of one second.

- 5/ All transitions are measured at a 1.5 V level. Inputs are driven at  $V_{IL} = 0$  V and  $V_{IH} = 3.0$  V during dynamic testing.

- $\underline{6}$ / Not directly tested, but verified during functional tests by operating the device at the specified frequency.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89711 |

|-----------------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                                    |           | REVISION LEVEL<br>A | SHEET 6    |

| Device types    | A               | tt              |

|-----------------|-----------------|-----------------|

| Case Outlines   | J and L         | 3               |

| Terminal number | Termina         | l symbol        |

| 1               | V <sub>DD</sub> | V <sub>DD</sub> |

| 2               | MIN             | V <sub>DD</sub> |

| 3               | A <sub>IN</sub> | M <sub>IN</sub> |

| 4               | BIN             | A <sub>IN</sub> |

| 5               | CLK T           | NC NC           |

| 6               | CLK S           | B <sub>IN</sub> |

| 7               | INV             | CLK T           |

| 8               | TS              | CLK S           |

| 9               | 106             | INV             |

| 10              | 105             | TS              |

| 11              | 104             | 106             |

| 12              | 103             | 105             |

| 13              | 102             | 104             |

FIGURE 1. Terminal Connections

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-89711 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 7    |

| Device types    | A                | ll               |

|-----------------|------------------|------------------|

| Case Outlines   | J and L          | 3                |

| Terminal number | Terminal         | l symbol         |

| 14              | 101              | 103              |

| 15              | 100              | 102              |

| 16              | GND              | 101              |

| 17              | TFLG             | 100              |

| 18              | B <sub>OUT</sub> | NC NC            |

| 19              | <sup>A</sup> out | GND              |

| 20              | M <sub>OUT</sub> | GND              |

| 21              | LDR              | TFLG             |

| 22              | CLK A            | B <sub>OUT</sub> |

| 23              | CLK M            | A <sub>OUT</sub> |

| 24              | CLK B            | M <sub>OUT</sub> |

| 25              |                  | LDR              |

| 26              |                  | CLK A            |

| 27              |                  | CLK M            |

| 28              |                  | CLK B            |

FIGURE 1. <u>Terminal Connections</u> - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89711 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>8 |

| DESC | FORM | 193A |

|------|------|------|

| JUI  | 91   |      |

Cross-correlation

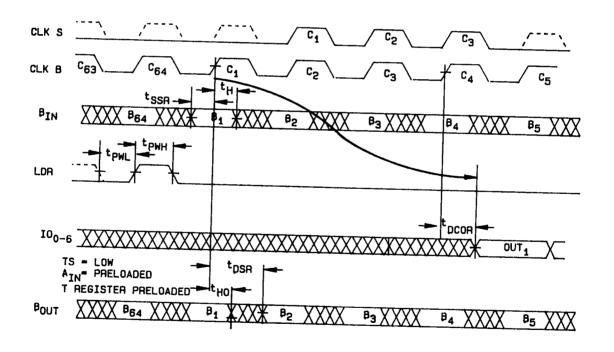

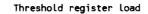

FIGURE 3. Switching times test circuit and waveforms - Continued.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                     | 5962-89711  |

|---------------------------------------------------------------------------------------------|-----------|---------------------|-------------|

|                                                                                             |           | REVISION LEVEL<br>A | SHEET<br>11 |

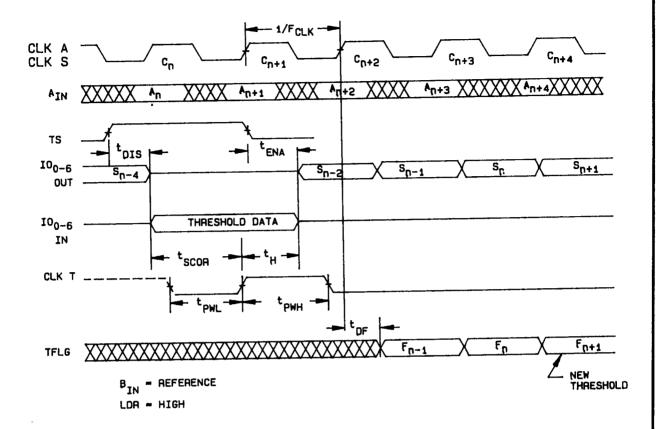

Invert control timing (see note)

NOTE: The INV control must be asserted on or before the rising edge of CLK, and held in the desired state until after the falling edge of CLK.

FIGURE 3. Switching times test circuit and waveforms - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                     | 5962-89711  |

|------------------------------------------------------------------------------------|-----------|---------------------|-------------|

|                                                                                    |           | REVISION LEVEL<br>A | SHEET<br>12 |

#### 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 (C<sub>IN/OUT</sub> measurement) shall be measured only for the initial test and after process or design changes which may affect input capacitance. A minimum sample size of five devices with zero rejects shall be required.

- d. Subgroups 7 and 8 shall consist of verifying the functionality of the device. These tests form a part of the vendors test tape and shall be maintained and available from the approved source of supply.

### 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125$ °C, minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

TABLE II. Electrical test requirements.

| MIL-STD-883 test requirements                                | Subgroups<br>(per method<br>5005, table I) |  |  |

|--------------------------------------------------------------|--------------------------------------------|--|--|

| Interim electrical parameters (method 5004)                  |                                            |  |  |

| Final electrical test parameters (method 5004)               | 1*, 2, 3, 7*, 8, 9, 10,<br>11              |  |  |

| Group A test requirements (method 5005)                      | 1, 2, 3, 4, 7, 8, 9, 10,<br>11             |  |  |

| Groups C and D end-point electrical parameters (method 5005) | 1, 2, 7, 9                                 |  |  |

<sup>\*</sup>PDA applies to subgroups 1 and 7.

# 5. PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

# 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-481 using DD Form 1693, Engineering Change Proposal (Short Form).

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89711  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET<br>13 |

- 6.4 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and the applicable SMD. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronics devices (FSC 5962) should contact DESC-ECT, telephone (513) 296-6022.

- 6.5 Symbols, definitions, and functional descriptions. See table III.

- 6.6 <u>Comments</u>. Comments on this drawing should be directed to DESC-ECC, Dayton, Ohio 45444, or telephone (513) 296-8526.

- 6.7 <u>Approved sources of supply</u>. Approved sources of supply are listed in MIL-BUL-103. The vendors listed in MIL-BUL-103 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DESC-ECC.

TABLE III. Pin functions.

| Pin Number                        | Pin functions                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> , GND             | The device operates from a single +5.0 V supply. All V <sub>DD</sub> and GND pins must be connected.                                                                                                                                                                                                                                                                                         |

| INV                               | Control that inverts the 7-bit digital output. When a high level is applied to this pin, the outputs IO <sub>O-6</sub> are logically inverted.   See figure 3 for constraints if this is to be clocked.                                                                                                                                                                                      |

| TS                                | Control that enables the three-state output. When a high level is applied to this pin, it forces outputs into the high-impedance state.                                                                                                                                                                                                                                                      |

| LDR                               | Control that allows parallel data to be loaded from the B register into the reference latch for correlations. If LDR is held high, the R latch is transparent.                                                                                                                                                                                                                               |

| CLK A, CLK B, CLK M               | Input clocks. Clock input pins for the A, B, and M registers respectively. Each register may be independently clocked.                                                                                                                                                                                                                                                                       |

| CLK T                             | Threshold register clock. Clock input for T register.                                                                                                                                                                                                                                                                                                                                        |

| CLK S                             | Digital summer clock. Clock input that allows independent clocking of pipelined summer network.                                                                                                                                                                                                                                                                                              |

| MIN                               | Mask register input allows the user to choose "no-compare" bit positions. A "O" in any bit location will result in a no-compare state for that location.                                                                                                                                                                                                                                     |

| A <sub>IN</sub> , B <sub>IN</sub> | Shift register inputs to the A and B 64-bit serial registers.                                                                                                                                                                                                                                                                                                                                |

| 100-6                             | Bi-directional data pins. When outputs are enabled, (TS low), data is a 7-bit binary representation of the correlation between the unmasked portions of the R latch and the A register. IO <sub>6</sub> is the MSB. These pins also serve as parallel inputs to load the threshold register. Data present one setup time before CLK T goes high will be latched into the threshold register. |

| TFLG                              | The TFLG output goes high whenever the correlation score is equal to or greater than the number loaded into the T register (O to 64).                                                                                                                                                                                                                                                        |

| Aout, Bout, Mout                  | Shift register outputs of the three 64-bit shift registers:  A, B, and M respectively. These outputs may be used to cascade the device.                                                                                                                                                                                                                                                      |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89711 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET      |