1-49

# Z8<sup>®</sup>L Z86L81/85 Low-Power ROMless Microcomputer

# Zilog

## Preliminary Product Specification

#### April 1985

#### **FEATURES**

- Complete microcomputer, 24 I/O lines, and up to 64K bytes of addressable external space each for program and data memory.

- 143-byte register file, including 124 general-purpose registers, 3 I/O port registers, and 16 status and control registers.

- Vectored, priority interrupts for I/O, counter/timers, and UART.

- On-chip oscillator that accepts crystal or external clock drive.

- Full-duplex UART and two programmable 8-bit counter/timers, each with a 6-bit programmable prescaler.

- Register Pointer so that short, fast instructions can access any one of the nine working-register groups.

- Low-power standby option that retains contents of general-purpose registers.

- Single +5V power supply—all I/O pins TTL compatible.

- 8 MHz

#### **GENERAL DESCRIPTION**

The Z86L81 and Z86L85 are ROMless versions of the Z8 single-chip microcomputer. The Z86L85 has the power-down option implemented. These products differ only slightly and can be used interchangeably with proper system design to provide maximum flexibility in meeting price and delivery needs. The Z86L81/85 offers all the outstanding features of the Z8 family architecture except an on-chip program ROM. Use of external memory, rather than a preprogrammed ROM, enables this Z8 microcomputer to be used in low-volume applications or where code flexibility is required.

The Z86L81/85 can provide up to 16 output address lines, thus permitting an address space of up to 64K bytes of data and/or program memory. Eight address outputs (AD $_0$ -AD $_7$ ) are provided by a multiplexed, 8-bit, Address/Data bus. The remaining 8 bits can be provided by the software configuration of Port 0 to output address bits  $A_8$ - $A_{15}$ .

Available address space can be doubled by programming bit 4 of Port 3 (P3<sub>4</sub>) to act as a data memory select output (DM). The two states of DM together with the 16 address outputs can define separate data and memory address spaces of up to 64K/62Kbytes each.

There are 143 bytes of RAM located on-chip and organized as a register file of 123 general-purpose registers, 16 control and status registers, and four I/O port registers. This register file can be divided into nine groups of 16 working registers each. Configuring the register file in this manner allows the use of short format instructions; in addition, any of the individual registers can be accessed directly.

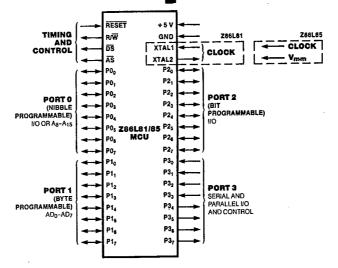

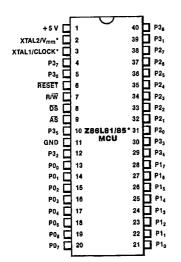

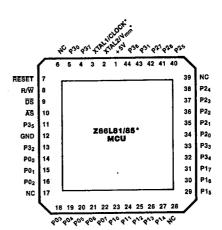

The pin functions and the pin assignments of the Z86L81/85 40-pin DIP and 44-pin Chip Carrier are illustrated in Figures 1 and 2.

Figure 1. Pin Functions

Figure 2a. 40-Pin DIP, **Pin Assignments**

Figure 2b. 44-Pin Chip Carrier Pin Assignments

#### **ARCHITECTURE**

Z86L81/85 architecture is characterized by a flexible I/O scheme, an efficient register and address space structure and a number of ancillary features that are helpful in many applications.

Microcomputer applications demand powerful I/O capabilities. The Z86L81/85 fulfills this with 24 pins available for input and output. These lines are grouped into three ports of eight lines each and are configurable under software control to provide timing, status signals, serial or parallel I/O with or without handshake, and an Address bus for interfacing external memory.

Three basic address spaces are available: program

memory, data memory and the register file (internal). The 143-byte random-access register file is composed of 124 general-purpose registers, three I/O port registers, and 16 control and status registers.

To unburden the program from coping with real-time problems such as serial data communication and counting/timing, an asynchronous receiver/transmitter (UART) and two counter/timers with a large number of user-selectable modes are offered on-chip. Hardware support for the UART is minimized because one f the on-chip timers supplies the bit rate. Figure 3 shows the Z86L81/85 block diagram.

Z-BUS WHEN USED AS ADDRESS/DATA BUS

\*Z86L81 only

Figure 3. Z86L81/85 Functional Block Diagram

#### **PIN DESCRIPTION**

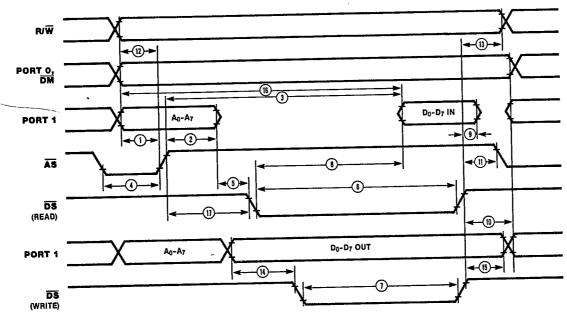

**AS.** Address Strobe (output, active Low). Address Strobe is pulsed once at the beginning of each machine cycle. Addresses output via Port 1 for all external program or data memory transfers are valid at the trailing edge of AS.

CLOCK. Clock, Z86L85. Up to 8 MHz (TTL levels).

**DS.** Data Strobe (output, active Low). Data Strobe is activated once for each external memory transfer.

**P0**<sub>0</sub>-**P0**<sub>7</sub>, **P2**<sub>0</sub>-**P2**<sub>7</sub>, **P3**<sub>0</sub>-**P3**<sub>7</sub>. I/O Port Lines (input/outputs, TTL-compatible). These 24 lines are divided into three 8-bit I/O ports that can be configured under program control for I/O or external memory interface (Figure 3).

**P1<sub>0</sub>-P1<sub>7</sub>.** Address/Data Port (bidirectional). Multiplexed address ( $A_0$ - $A_7$ ) and data ( $D_0$ - $D_7$ ) lines used to interface with program and data memory.

**RESET.** Reset (input, active Low). RESET initializes the Z86L81/85. After Reset, the device is in the extended memory mode. When RESET is deactivated, program execution begins from program location 000C<sub>H</sub>.

**R/W.** Read/Write (output). R/W is Low when the Z86L81/85 is writing to external program or data memory.

**Vmm.** Z86L85. Register power backup must be maintained at 3.0 to 5.25V while  $V_{CC}$  is down.

XTAL1, XTAL2. Crystal 1, Crystal 2, Z86L81 only (timebase input and output). These pins connect a parallelresonant crystal to the on-chip clock oscillator and buffer.

#### **ADDRESS SPACES**

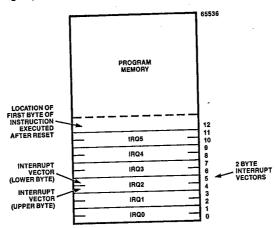

**Program Memory.** The Z86L81/85 addresses 64K/62K bytes of external program memory space (Figure 4).

The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts. Program execution begins at location  $000C_{\rm H}$  after a reset.

**Data Memory.** The Z86L81/85 can address 64K bytes of external data memory. External data memory can be included with, or separated from, the external program memory space. DM, an optional I/O function that can be programmed to appear on pin P3<sub>4</sub>, is used to distinguish between data and program memory space.

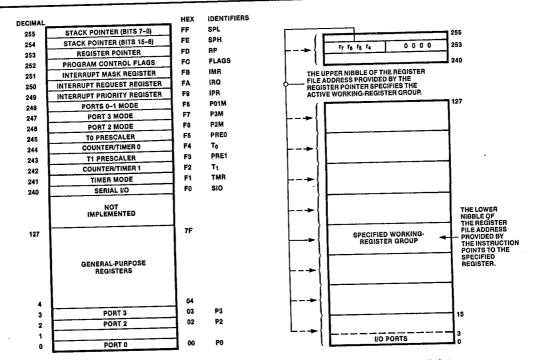

Register File. The 143-byte register file includes three I/O port registers (R0, R2, R3), 124 general-purpose registers (R4-R127) and 16 control and status registers (R240-R255). These registers are assigned the address locations shown in Figure 5.

Z86L81/85 instructions can access registers directly or indirectly with an 8-bit address field. This also allows short 4-bit register addressing using the Register Pointer (one of the control registers). In the 4-bit mode, the register file is divided into nine working-register groups, each occupying

16 contiguous locations (Figure 5). The Register Pointer addresses the starting location of the active working-register group (Figure 6).

**Stacks.** Either the internal register file or the external data memory can be used for the stack. A 16-bit Stack Pointer (R254 and R255) is used for the external stack, which can reside anywhere in data memory. An 8-bit Stack Pointer (R255) is used for the internal stack that resides within the 124 general-purpose registers (R4-R127).

Figure 4. Z86L81/85 Program Memory Map

Figure 5. The Register File

Figure 6. The Register Pointer

## **SERIAL INPUT/OUTPUT**

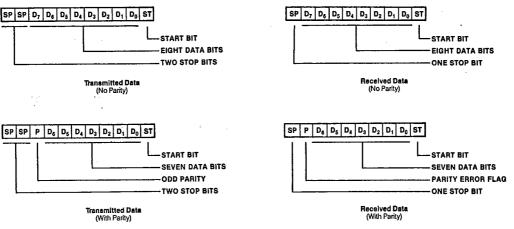

Port 3 lines P3<sub>0</sub> and P3<sub>7</sub> can be programmed as serial I/O lines for full-duplex serial asynchronous receiver/transmitter operation. The bit rate is controlled by Counter/Timer 0, with a maximum rate of 62.5K bits/second at 8 MHz.

The Z86L81/85 automatically adds a start bit and two stop bits to transmitted data (Figure 7). Odd parity is also available as an option. Eight data bits are always transmitted, regardless of parity selection. If parity is

enabled, the eighth data bit is used as the odd parity bit. An interrupt request (IRQ4) is generated on all transmitted

720 05219

Received data must have a start bit, eight data bits, and at least one stop bit. If parity is on, bit 7 of the received data is replaced by a parity error flag. Received characters generate the IRQ3 interrupt request.

Figure 7. Serial Data Formats

#### **COUNTER/TIMERS**

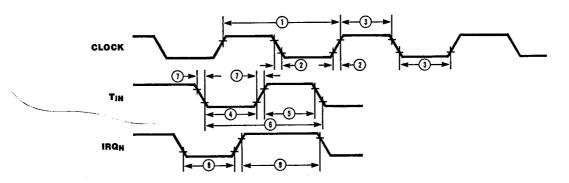

The Z86L81/85 contains two 8-bit programmable counter/ timers ( $T_0$  and  $T_1$ ), each driven by its own 6-bit programmable prescaler. The T<sub>1</sub> prescaler can be driven by internal or external clock sources; however, the To prescaler is driven only by the internal clock.

The 6-bit prescalers can divide the input frequency of the clock source by any number from 1 to 64. Each prescaler drives its counter, which decrements the value (1 to 256) that has been loaded into the counter. When the counter reaches the end of count, a timer interrupt request, IRQ4 (To) or IRQ5  $(T_1)$ , is generated.

The counters can be started, stopped, restarted to continue, or restarted from the initial value. The counters can also be programmed to stop upon reaching zero (single-pass mode) or to automatically reload the initial value and continue counting (modulo-n continuous mode). The counters, but not the prescalers, can be read any time without disturbing their value or count mode.

The clock source for T<sub>1</sub> is user-definable; it can be either the internal microprocessor clock divided by four, or an external signal input via Port 3. The Timer Mode register configures the external timer input as an external clock, a trigger input that can be retriggerable or non-retriggerable, or as a gate input for the internal clock. The counter/timers can be programmably cascaded by connecting the To output to the input of T1. Port 3 line P36 also serves as a timer output (TOUT) through which To, T1 or the internal clock can be

#### I/O PORTS

The Z86L81/85 has 24 lines available for input and output. These lines are grouped into three ports of eight lines each and are configurable as input, output, or address. Under software control, the ports can be programmed to provide address outputs, timing, status signals, serial I/O, and parallel I/O with or without handshake. All ports have active pull-ups and pull-downs compatible with TTL loads.

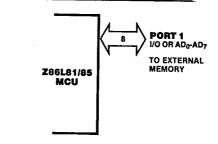

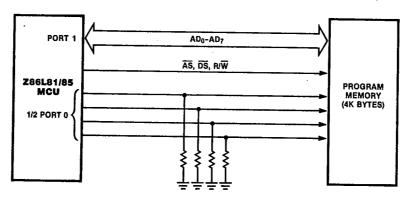

Port 1 is a dedicated Z-BUS-compatible memory interface. The operations of Port 1 are supported by the Address Strobe (AS) and Data Strobe (DS) lines, and by the Read/Write (R/W) and Data Memory (DM) control lines. The low-order program and data memory addresses (A<sub>0</sub>-A<sub>7</sub>) are output through Port 1 (Figure 8) and are multiplexed with data in/out (D<sub>0</sub>-D<sub>7</sub>). Instruction fetch and data memory read/write operations are done through this port.

Port 1 cannot be used as a register nor can a handshake mode be used with this port.

Both the Z86L81 and Z86L85 wake up with the 8 bits of Port 1 configured as address outputs for external memory. If more than eight address line are required, additional lines can be obtained by programming Port 0 bits as address bits. The least-significant four bits of Port 0 can be configured to supply address bits A<sub>8</sub>-A<sub>11</sub> for 4K byte addressing or both nibbles of Port 0 can be configured to supply address bits A<sub>8</sub>-A<sub>15</sub> for 64K byte addressing.

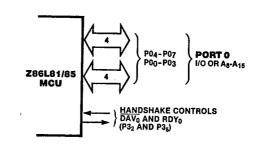

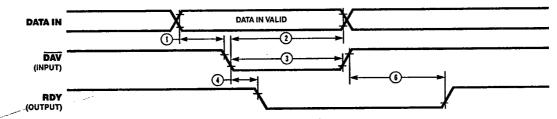

**Port 0** can be programmed as a nibble I/O port or as an address port for interfacing external memory (Figure 9). When used as an I/O port, Port 0 can be placed under handshake control. In this configuration, Port 3 lines P3 $_2$  and P3 $_5$  are used as the handshake controls  $\overline{\text{DAV}}_0$  and RDY $_0$ . Handshake signal assignment is dictated by the I/O direction of the upper nibble P0 $_4$ -P0 $_7$ .

For external memory references, Port 0 can provide address bits  $A_8$ - $A_{11}$  (lower nibble) or  $A_8$ - $A_{15}$  (lower and upper nibbles) depending on the required address space. If the address range requires 12 bits or less, the upper nibble of Port 0 can be programmed independently as I/O while the lower nibble is used for addressing.

Port 0 lines float after reset; their logic state is unknown until the execution of an initialization routine that configures Port 0.

Such an initialization routine must reside within the first 256 bytes of executable code and must be physically mapped into memory by forcing the Port 0 address lines to a known state (Figure 10). The proper port initialization sequence is:

- Write initial address (A<sub>8</sub>-A<sub>15</sub>) of initialization routine to Port 0 address lines.

- 2. Configure Port 0 Mode register to output  $A_8$ - $A_{15}$  (or  $A_8$ - $A_{11}$ ).

To permit the use of slow memory, an automatic wait mode of two oscillator clock cycles is configured for the bus timing of the Z86L81 after each reset. The initialization routine could include reconfiguration to eliminate this extended timing mode.

Figure 8. Port 1

Figure 9. Port 0

The following example illustrates the manner in which an initialization routine can be mapped in a system with 4K of memory.

Example. In Figure 10, the initialization routine is mapped to the first 256 bytes of program memory. Pull-down resistors maintain the address lines at a logic 0 level when these lines are floating. The leakage current caused by fanout must be taken into consideration when selecting the value of the pulldown resistors. The resistor value must be large enough to allow the Port 0 output driver to pull the line to a logic 1. Generally, pulldown resistors are incompatible with TTL loads. If Port 0 drives into TTL input loads ( $I_{LOW} = 1.6 \text{ mA}$ ) the external resistors should be tied to  $V_{CC}$  and the initialization routine put in address space FF00H-FFFFH.

Figure 10. Port 0 Address Lines Tied to Logic 0

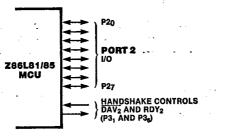

**Port 2** bits can be programmed independently as input or output (Figure 11). This port is always available for I/O operations. In addition, Port 2 can be configured to provide open-drain outputs.

Like Port 0, Port 2 can also be placed under handshake control. In this configuration, Port 3 lines  $P3_1$  and  $P3_6$  are used as the handshake controls lines  $\overline{DAV}_2$  and  $RDY_2$ . The handshake signal assignment for Port 3 lines  $P3_1$  and  $P3_6$  is dictated by the direction (input or output) assigned to bit 7 of Port 2.

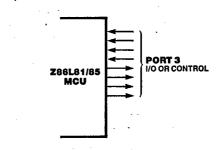

**Port 3** lines can be configured as I/O or control lines (Figure 12). In either case, the direction of the eight lines is fixed as four input (P3<sub>0</sub>-P3<sub>3</sub>) and four output (P3<sub>4</sub>-P3<sub>7</sub>). For serial I/O, lines P3<sub>0</sub> and P3<sub>7</sub> are programmed as serial in and serial out, respectively.

72C O5221

Port 3 can also provide the following control functions: handshake for Ports 0 and 2 (DAV and RDY); four external interrupt request signals (IRQ0-IRQ3); timer input and output signals (T<sub>IN</sub> and T<sub>OUT</sub>) and Data Memory Select (DM).

Figure 11. Port 2

Figure 12. Port 3

#### INTERRUPTS

The Z86L81/85 allows six different interrupts from eight sources: the four Port 3 lines P3<sub>0</sub>-P3<sub>3</sub>, Serial In, Serial Out, and the two counter/timers. These interrupts are both maskable and prioritized. The Interrupt Mask register globally or individually enables or disables the six interrupt requests. When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register.

All interrupts are vectored through locations in program memory. When an interrupt request is granted, an interrupt machine cycle is entered. This disables all subsequent interrupts, saves the Program Counter and status flags, and accesses the program memory vector location reserved for that interrupt. In the Z86L81/85, this memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular interrupt request. The Z86L81/85 takes 26 system clock cycles to enter an interrupt subroutine.

Polled interrupt systems are also supported. To accommodate a polled structure, any or all of the interrupt inputs can be masked and the Interrupt Request register polled to determine which of the interrupt requests needs service.

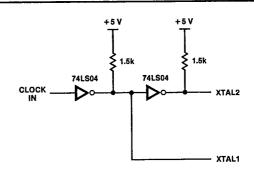

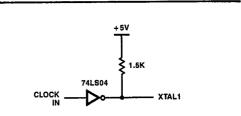

#### **CLOCK**

#### Z86L81

The on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a crystal or to any suitable external clock source (XTAL 1 = Input, XTAL2 = Output).

The crystal source is connected across XTAL1 and XTAL2, using the recommended capacitance ( $C_L=15\,$  pf maximum) from each pin to ground. The specifications for the crystal are as follows:

AT cut, parallel-resonant

- Fundamental type

- Series resistance, R<sub>s</sub> ≤ 100Ω

- 8 MHz maximum

#### Z86L85

The Z86L85 has one pin for external oscillator input.

#### -49-19-59

#### 9984043 ZILOG INC

#### **POWER DOWN STANDBY OPTION**

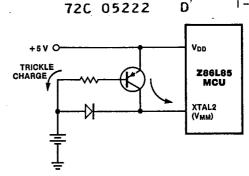

The low-power standby mode allows power to be removed from the Z86L85 without losing the contents of the 124 general-purpose registers. This mode is available only to the user as a bonding option whereby pin 2 (normally XTAL2) is replaced by the  $V_{MM}$  (standby) power supply input. This necessitates the use of an external clock generator (input = XTAL1) rather than a crystal source.

The removal of power, whether intended or due to power failure, must be preceded by a software routine that stores the appropriate status into the register file. Figure 13 shows the recommended circuit for a battery back-up supply system.

Figure 13. Recommended Driver Circuit for Power-Down Operation of Z86L85

#### **INSTRUCTION SET NOTATION**

**Addressing Modes.** The following notation is used to describe the addressing modes and instruction operations as shown in the instruction summary.

| IRR | Indirect register pair or indirect working register pair |

|-----|----------------------------------------------------------|

|     | address                                                  |

**Symbols.** The following symbols are used in describing the instruction set.

| dst | Destination location or contents |

|-----|----------------------------------|

| STC | Source location or contents      |

PC Program counter

IMR Interrupt mask register (control register 251)

Assignment of a value is indicated by the symbol "

-". For example,

indicates that the source data is added to the destination data and the result is stored in the destination location. The notation "addr(n)" is used o refer to bit "n" of a given location. For example,

#### dst (7)

refers to bit 7 of the destination operand.

**Flags.** Control Register R252 contains the following six flags:

| С | Carry flag          |

|---|---------------------|

| Z | Zero flag           |

| S | Sign flag           |

| ٧ | Overflow flag       |

| D | Decimal-adjust flag |

| н | Half-carry flag     |

Affected flags are indicated by:

| 0 | Cleared to zero |

|---|-----------------|

| - | 0-14            |

Unaffected

X Undefined

### 9984043 ZILOG INC **CONDITION CODES**

720 05223

|--|

| Value | Mnemonic | Meaning                        | Flags Set             |

|-------|----------|--------------------------------|-----------------------|

| 1000  |          | Always true                    | -                     |

| 0111  | С        | Carry                          | C = 1                 |

| 1111  | NC       | No carry                       | C = 0                 |

| 0110  | Z        | Zero                           | Z = 0                 |

| 1110  | NZ       | Not zero                       | Z = 0                 |

| 1101  | PL       | Plus                           | S = 0                 |

| 0101  | MI       | Minus                          | S = 1                 |

| 0100  | OV       | Overflow                       | V = 1                 |

| 1100  | NOV      | No overflow                    | V = 0                 |

| 0110  | EQ       | Equal                          | Z = 1                 |

| 1110  | NE<br>NE | Not equal                      | Z = 0                 |

| 1001  | GE       | Greater than or equal          | (S XOR V) = 0         |

| 0001  | LT       | Less than                      | (S XOR V) = 1         |

| 1010  | GT       | Greater than                   | [Z OR (S XOR V)] = 0  |

| 0010  | LE       | Less than or equal             | [Z OR (S XOR V)] = 1  |

| 1111  | UGE      | Unsigned greater than or equal | C = 0                 |

| 0111  | ULT      | Unsigned less than             | C = 1                 |

| 1011  | UGT      | Unsigned greater than          | (C = 0 AND Z = 0) = 1 |

| 0011  | ULE      | Unsigned less than or equal    | (C OR Z) = 1          |

| 0000  | JLL      | Never true                     | _                     |

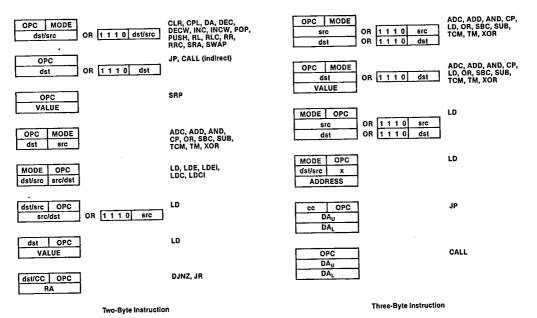

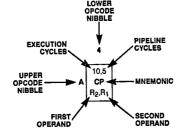

#### **INSTRUCTION FORMATS**

CCF, DI, EI, IRET, NOP, RCF, RET, SCF OPC INC r dst OPC

#### One-Byte Instruction

Figure 14. Instruction Formats

### 9984043 ZILOG INC **INSTRUCTION SUMMARY**

|                                                                                  | Addr Mode      |                             |   |   |   | Flags Affe |   | d |

|----------------------------------------------------------------------------------|----------------|-----------------------------|---|---|---|------------|---|---|

| Instruction<br>and Operation                                                     | dst src        | Byte<br>(Hex)               | С | z | s | ٧          | D | Н |

| ADC dst,src<br>dst ← dst + src + C                                               | (Note 1)       | 10                          | * | * | * | *          | 0 | * |

| ADD dst,src<br>dst ← dst + src                                                   | (Note 1)       | 0□                          | * | * | * | *          | 0 | * |

| AND dst,src<br>dst ← dst AND src                                                 | (Note 1)       | 5□                          |   | * | * | 0          | _ | _ |

| <b>CALL</b> dst<br>SP ← SP - 2<br>@SP ← PC; PC ← ds                              | DA<br>IRR<br>t | D6<br>D4                    | _ | _ | _ | _          | _ | _ |

| CCF<br>C ← NOT C                                                                 |                | EF                          | * | _ | _ | _          | _ | - |

| CLR dst<br>dst ← 0                                                               | R<br>IR        | B0<br>B1                    | _ | _ |   |            | _ | _ |

| COM dst<br>dst ← NOT dst                                                         | R<br>IR        | 60<br>61                    | _ | * | * | 0          | _ | _ |

| CP dst,src<br>dst - src                                                          | (Note 1)       | A□                          | * | * | * | *          |   | _ |

| <b>DA</b> dst<br>dst ← DA dst                                                    | R<br>IR        | 40<br>41                    | * | * | * | Х          | _ | _ |

| DEC dst<br>dst ← dst – 1                                                         | R<br>IR        | 00<br>01                    | _ | * | * | *          | _ | _ |

| DECW dst<br>dst ← dst – 1                                                        | RR<br>IR       | 80<br>81                    | _ | * | * | *          | _ | - |

| <b>DI</b><br>IMR (7) ← 0                                                         |                | 8F                          | _ | _ |   |            |   | _ |

| <b>DJNZ</b> r,dst<br>r ← r − 1<br>if r ≠ 0<br>PC ← PC + dst<br>Range: +127, -128 | RA             | rA $r = 0 - F$              | _ | _ | _ | _          | _ | _ |

| <b>EI</b> IMR (7) ← 1                                                            |                | 9F                          | _ |   | _ | _          | _ | _ |

| INC dst<br>dst ← dst + 1                                                         | r<br>R<br>IR   | rE<br>r = 0 - F<br>20<br>21 |   | * | * | *          | _ | _ |

| INCW dst<br>dst ← dst + 1                                                        | RR<br>IR       | A0<br>A1                    | _ | * | * | *          | _ | _ |

| IRET<br>FLAGS ← @SP; SP ←<br>PC ← @SP; SP ← SF                                   |                | BF<br>←1                    | * | * | * | *          | * | * |

| JP cc,dst<br>if cc is true<br>PC ← dst                                           | DA<br>IRR      | cD<br>c = 0 - F<br>30       |   | _ | _ | _          | _ | _ |

| Instruction                                                       | Addr                   | Mode                      | Opcode<br>Byte                   | Flags Affe |   | cted |   |   |   |

|-------------------------------------------------------------------|------------------------|---------------------------|----------------------------------|------------|---|------|---|---|---|

| and Operation                                                     | dst                    | src                       | (Hex)                            | С          | z | s    | ٧ | D | Н |

| JR cc,dst<br>if cc is true,<br>PC ← PC + dst<br>Range: +127, -128 | RA<br>3                |                           | cB<br>c = 0 - F                  | _          | _ |      | _ | _ | _ |

| LD dst,src<br>dst ← src                                           | r<br>r<br>R            | lm<br>R<br>r              | rC<br>r8<br>r9<br>r = 0 - F      | _          | _ |      | _ | _ | _ |

|                                                                   | r<br>X<br>Ir<br>R<br>R | X<br>Ir<br>Ir<br>IR<br>IM | C7<br>D7<br>E3<br>F3<br>E4<br>E5 |            |   |      |   |   |   |

|                                                                   | IR<br>IR               | IM<br>R                   | E7<br>F5                         |            |   |      |   |   |   |

| LDC dst,src<br>dst ← src                                          | r<br>Irr               | lrr<br>r                  | C2<br>D2                         | _          | _ | _    | _ | _ | _ |

| LDCI dst,src<br>dst ← src<br>r ← r + 1; rr ← rr + 1               | lr<br>1rr              | lrr<br>Ir                 | C3<br>D3                         | _          | _ | _    | _ | - | _ |

| LDE dst,src<br>dst ← src                                          | r<br>irr               | lrr<br>r                  | 82<br>92                         | _          | _ | _    | _ | _ | _ |

| LDEI dst,src<br>dst ← src<br>r ← r + 1; rr ← rr + 1               | lr<br>Irr              | lrr<br>Ir                 | 83<br>93                         | _          | _ | _    | _ | _ | _ |

| NOP                                                               |                        |                           | FF                               | _          | _ | _    | _ | _ | _ |

| OR dst,src<br>dst ← dst OR src                                    | (No                    | te 1)                     | 4□                               | _          | * | *    | 0 | - | - |

| <b>POP</b> dst<br>dst ← @SP;<br>SP ← SP + 1                       | R<br>IR                |                           | 50<br>51                         | _          |   | -    |   |   | _ |

| PUSH src<br>SP ← SP - 1; @SP                                      | ⊷ src                  | R<br>IR                   | 70<br>71                         | _          |   | _    | _ | _ | _ |

| RCF<br>C←0                                                        |                        |                           | CF                               | 0          | _ | _    | _ | _ | _ |

| RET<br>PC ← @SP; SP ← SR                                          | ° + 2                  |                           | AF                               | -          | _ | _    | _ | _ | _ |

| RL dst                                                            | R<br>IR                |                           | 90<br>91                         | *          | * | *    | * | _ |   |

| RLC dst                                                           | R<br>IR                |                           | 10<br>11                         | *          | * | *    | * | _ | _ |

| RR dst G                                                          | P R                    |                           | E0<br>E1                         | *          | * | *    | * | _ | _ |

#### 9984043 ZILOG INC **INSTRUCTION SUMMARY** (Continued)

72C 05225

|                                    | Addr Mode       |       | Opcode        | Flags Affected |   |   |   |   | ed |

|------------------------------------|-----------------|-------|---------------|----------------|---|---|---|---|----|

| Instruction and Operation          | dst             | src   | Byte<br>(Hex) | С              | z | s | ٧ | D | н  |

| RRC dst [_c] -[7 0                 | ₽ <sub>IR</sub> |       | C0<br>C1      | *              | * | * | * | - | _  |

| SBC dst,src<br>dst ← dst ← src ← C | (No             | te 1) | 3□            | *              | * | * | * | 1 | *  |

| SCF<br>C←1                         |                 |       | DF            | 1              | - | _ | _ | _ | _  |

| SRA dst                            | ₽ IR            |       | D0<br>D1      | *              | * | * | 0 | _ | _  |

| SRP src<br>RP ← src                |                 | lm    | 31            | _              | _ | _ | _ | _ | _  |

| SUB dst,src<br>dst ← dst ← src     | (No             | te 1) | 2□            | *              | * | * | * | 1 | *  |

| SWAP dst 7 4 3                     | n R<br>IR       |       | F0<br>F1      | Х              | * | * | Х |   | _  |

| TCM dst,src<br>(NOT dst) AND src   | (No             | te 1) | 6□            | _              | * | * | 0 | _ | _  |

| TM dst,src<br>dst AND src          | (No             | te 1) | <b>7</b> □    | _              | * | * | 0 | _ | _  |

| Instruction                      | Addr Mode |       | Opcode<br>Byte | Flags Affected |   |   |   |   |   |

|----------------------------------|-----------|-------|----------------|----------------|---|---|---|---|---|

| and Operation                    | dst       | src   | (Hex)          | C              | Z | s | ٧ | D | Н |

| XOR dst,src<br>dst ← dst XOR src | (No       | te 1) | В□             | _              | * | * | 0 | _ | _ |

NOTE: These instructions have an identical set of addressing modes, which are encoded for brevity. The first opcode nibble is found in the instruction set table above. The second nibble is expressed symbolically by a  $\square$  in this table, and its value is found in the following table to the left of the applicable addressing mode pair. For example, the opcode of an ADC instruction using the addressing modes r (destination) and Ir (source) is 13.

| Addr | Mode | Lower         |

|------|------|---------------|

| dst  | src  | Opcode Nibble |

| Г    | r    | 2             |

| r    | lr   | 3             |

| R    | R    | 4             |

| R    | IR   | 5             |

| R    | IM   | 6             |

| IR   | IM   | 7             |

0 = NO FUNCTION

1 = LOAD T<sub>0</sub>

0 = DISABLE T<sub>0</sub> COUNT

1 = ENABLE T<sub>0</sub> COUNT

0 = NO FUNCTION 1 = LOAD T<sub>1</sub> 0 = DISABLE T<sub>1</sub> COUNT 1 = ENABLE T<sub>1</sub> COUNT

RESERVED (MUST BE 0)

PRESCALER MODULO (RANGE: 1-64 DECIMAL 01-00 HEX)

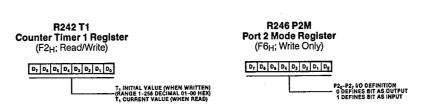

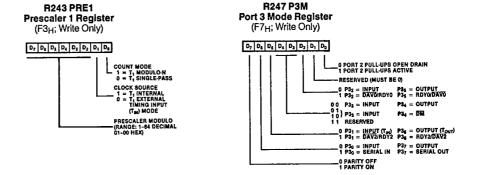

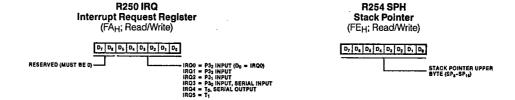

Figure 15. Control Registers

Figure 15. Control Registers (Continued)

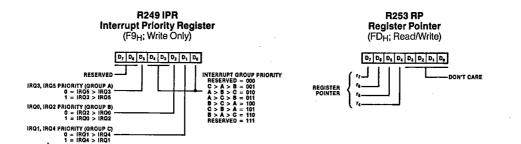

## Z86L81/85 OPCODE MAP

| Lower Nibble | (Hax) |

|--------------|-------|

|                    |   |                                      |                                       |                                                        |                                                          |                                                      |                                                       |                                          | Ower NID                                              | nie (way)                                          |                                                    |                                              |                               |                                        |                               |                  |                   |

|--------------------|---|--------------------------------------|---------------------------------------|--------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------|------------------------------------------|-------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------|-------------------------------|----------------------------------------|-------------------------------|------------------|-------------------|

|                    |   | 0                                    | 1                                     | 2                                                      | 3                                                        | 4                                                    | 5                                                     | 6                                        | 7                                                     | 8                                                  | 9                                                  | A                                            | В                             | С                                      | D                             | E                | F                 |

|                    | 0 | 6,5<br><b>DEC</b><br>R <sub>1</sub>  | 6,5<br>DEC<br>IR <sub>1</sub>         | 6,5<br><b>ADD</b><br>11,12                             | 6,5<br>ADD<br>r <sub>1,</sub> lr <sub>2</sub>            | 10.5<br>ADD<br>R <sub>2</sub> .R <sub>1</sub>        | 10,5<br>ADD<br>IR <sub>2</sub> ,R <sub>1</sub>        | 10,5<br><b>ADD</b><br>R <sub>1</sub> ,IM | 10,5<br><b>ADD</b><br>IR <sub>1</sub> ,IM             | 6,5<br><b>LD</b><br>r <sub>1</sub> ,R <sub>2</sub> | 6,5<br><b>LD</b><br>f <sub>2</sub> ,R <sub>1</sub> | 12/10,5<br><b>DJNZ</b><br>r <sub>1</sub> ,RA | 12/10,0<br><b>JR</b><br>cc,RA | 6,5<br><b>LD</b><br>r <sub>1</sub> ,lM | 12/10,0<br><b>JP</b><br>cc,DA | 6,5<br>INC<br>r1 |                   |

|                    | 1 | 6,5<br>RLC<br>R <sub>1</sub>         | 6,5<br>RLC<br>IR <sub>1</sub>         | 6,5<br>ADC<br>r <sub>1,</sub> r <sub>2</sub>           | 6,5<br>ADC<br>r <sub>1</sub> ,lr <sub>2</sub>            | 10,5<br>ADC<br>R <sub>2</sub> ,R <sub>1</sub>        | 10,5<br>ADC<br>IR <sub>2</sub> ,R <sub>1</sub>        | 10,5<br><b>ADC</b><br>R <sub>1</sub> ,IM | 10,5<br>ADC<br>IR <sub>1</sub> ,IM                    |                                                    |                                                    |                                              |                               |                                        |                               |                  |                   |

|                    | 2 | 6,5<br>INC<br>R <sub>1</sub>         | 6,5<br>INC<br>IR <sub>1</sub>         | 6,5<br>SUB<br>f <sub>1</sub> ,f <sub>2</sub>           | 6,5<br><b>SUB</b><br>r <sub>1</sub> ,lr <sub>2</sub>     | 10,5<br><b>SUB</b><br>R <sub>2</sub> ,R <sub>1</sub> | 10,5<br><b>SUB</b><br>(R <sub>2</sub> ,R <sub>1</sub> | 10,5<br><b>SUB</b><br>R <sub>1</sub> ,IM | 10,5<br><b>SUB</b><br>IR <sub>1</sub> ,IM             |                                                    |                                                    |                                              |                               |                                        |                               |                  |                   |

|                    | 3 | 8,0<br><b>JP</b><br>IRR <sub>1</sub> | 6,1<br>SRP<br>IM                      | 6,5<br>SBC<br>f <sub>1</sub> ,f <sub>2</sub>           | 6,5<br><b>SBC</b><br>f <sub>1,</sub> lr <sub>2</sub>     | 10,5<br><b>SBC</b><br>R <sub>2</sub> ,R <sub>1</sub> | 10,5<br><b>SBC</b><br>IR <sub>2</sub> ,R <sub>1</sub> | 10,5<br><b>SBC</b><br>R <sub>1</sub> ,IM | 10,5<br>SBC<br>IR <sub>1</sub> ,IM                    |                                                    |                                                    |                                              |                               |                                        |                               |                  |                   |

|                    | 4 | 8,5<br><b>DA</b><br>R <sub>1</sub>   | 8,5<br><b>DA</b><br>IR <sub>1</sub>   | 6,5<br><b>OR</b><br>r <sub>1</sub> ,r <sub>2</sub>     | 6,5<br><b>OR</b><br>r <sub>1</sub> ,lr <sub>2</sub>      | 10,5<br><b>OR</b><br>R <sub>2</sub> ,R <sub>1</sub>  | 10,5<br><b>OR</b><br>IR <sub>2</sub> ,R <sub>1</sub>  | 10,5<br><b>OR</b><br>R <sub>1</sub> ,IM  | 10,5<br><b>OR</b><br>IR <sub>1</sub> ,IM              |                                                    |                                                    |                                              |                               |                                        |                               |                  |                   |

|                    | 5 | 10,5<br><b>POP</b><br>R <sub>1</sub> | 10,5<br><b>POP</b><br>IR <sub>1</sub> | 6,5<br>AND<br>r <sub>1</sub> ,r <sub>2</sub>           | 6,5<br>AND<br>r <sub>1</sub> ,lr <sub>2</sub>            | 10,5<br><b>AND</b><br>R <sub>2</sub> ,R <sub>1</sub> | 10,5<br>AND<br>IR <sub>2</sub> ,R <sub>1</sub>        | 10,5<br>AND<br>R <sub>1</sub> ,IM        | 10,5<br>AND<br>IR <sub>1</sub> ,IM                    |                                                    |                                                    |                                              |                               |                                        |                               |                  |                   |

| _                  | 6 | 6,5<br><b>COM</b><br>R <sub>1</sub>  | 6,5<br><b>COM</b><br>IR <sub>1</sub>  | 6,5<br>TCM<br>r <sub>1</sub> ,r <sub>2</sub>           | 6,5<br><b>TCM</b><br>r <sub>1</sub> ,lr <sub>2</sub>     | 10,5<br><b>TCM</b><br>R <sub>2</sub> ,R <sub>1</sub> | 10,5<br>TCM<br>IR <sub>2</sub> ,R <sub>1</sub>        | 10,5<br><b>TCM</b><br>R <sub>1</sub> ,IM | 10,5<br><b>TCM</b><br>IR <sub>1</sub> ,IM             |                                                    |                                                    |                                              |                               |                                        |                               |                  |                   |

| Upper Nibble (Hex) | 7 | 10/12,1<br>PUSH<br>R <sub>2</sub>    | 12/14,1<br>PUSH<br>IR <sub>2</sub>    | 6,5<br><b>TM</b><br>r <sub>1</sub> ,r <sub>2</sub>     | 6,5<br><b>TM</b><br>r <sub>1</sub> .lr <sub>2</sub>      | 10,5<br><b>TM</b><br>R <sub>2</sub> ,R <sub>1</sub>  | 10,5<br><b>TM</b><br>IR <sub>2</sub> ,R <sub>1</sub>  | 10,5<br><b>TM</b><br>R <sub>1</sub> ,IM  | 10,5<br><b>TM</b><br>IR <sub>1</sub> ,IM              |                                                    |                                                    |                                              |                               |                                        |                               |                  | 6,1               |

| Upper Nii          | В | 10,5<br>DECW<br>RR <sub>1</sub>      | 10,5<br>DECW<br>IR <sub>1</sub>       | 12,0<br><b>LDE</b><br>r <sub>1</sub> ,lrr <sub>2</sub> | 18,0<br>LDEI<br>lr <sub>1</sub> ,lrr <sub>2</sub>        |                                                      |                                                       |                                          |                                                       |                                                    |                                                    |                                              |                               |                                        |                               |                  | ĐI                |

|                    | 9 | 6,5<br><b>RL</b><br>R <sub>1</sub>   | 6,5<br><b>AL</b><br>IR <sub>1</sub>   | 12,0<br><b>LDE</b><br>r <sub>2</sub> .lrr <sub>1</sub> | 18,0<br><b>LDEI</b><br>Ir <sub>2</sub> ,Irr <sub>1</sub> |                                                      |                                                       |                                          |                                                       |                                                    |                                                    |                                              |                               |                                        |                               |                  | 6,1<br>El         |

|                    | A | 10,5<br>INCW<br>RR <sub>1</sub>      | 10,5<br>INCW<br>IR <sub>1</sub>       | 6,5<br><b>CP</b><br>r <sub>1</sub> ,r <sub>2</sub>     | 6,5<br><b>CP</b><br>r <sub>1</sub> ,lr <sub>2</sub>      | 10.5<br><b>CP</b><br>R <sub>2</sub> ,R <sub>1</sub>  | 10,5<br><b>CP</b><br>IR <sub>2</sub> ,R <sub>1</sub>  | 10,5<br><b>CP</b><br>R <sub>1</sub> ,IM  | 10,5<br><b>CP</b><br>IR <sub>1</sub> ,IM              |                                                    |                                                    |                                              |                               |                                        |                               |                  | 14,0<br>RET       |

|                    | В | 6,5<br><b>CLR</b><br>R <sub>1</sub>  | 6,5<br><b>CLR</b><br>IR <sub>1</sub>  | 6,5<br><b>XOR</b><br>r <sub>1</sub> ,r <sub>2</sub>    | 6,5<br><b>XOR</b><br>r <sub>1</sub> ,lr <sub>2</sub>     | 10,5<br><b>XOR</b><br>R <sub>2</sub> ,R <sub>1</sub> | 10,5<br><b>XOR</b><br>IR <sub>2</sub> ,R <sub>1</sub> | 10,5<br><b>XOR</b><br>R <sub>1</sub> ,IM | 10,5<br>XOR<br>IR <sub>1</sub> ,IM                    |                                                    |                                                    |                                              |                               |                                        |                               |                  | 16,0<br>IRET      |

|                    | С | 6,5<br><b>RRC</b><br>R <sub>1</sub>  | 6,5<br>RRC<br>IR <sub>1</sub>         | 12,0<br>LDC<br>r <sub>1</sub> ,irr <sub>2</sub>        | 18,0<br><b>LDCI</b><br>lr <sub>1</sub> ,lrr <sub>2</sub> |                                                      |                                                       |                                          | 10,5<br><b>LD</b><br>r <sub>1</sub> ,x,R <sub>2</sub> | 4                                                  |                                                    |                                              |                               |                                        |                               |                  | 6,5<br>RCF        |

|                    | D | 6,5<br><b>SRA</b><br>R <sub>1</sub>  | 6,5<br>SRA<br>IR <sub>1</sub>         | 12,0<br>LDC<br>r <sub>2</sub> ,lrr <sub>1</sub>        | 18,0<br>LDCi<br>Ir <sub>2</sub> ,Irr <sub>1</sub>        | 20,0<br>CALL*<br>IRR <sub>1</sub>                    |                                                       | 20,0<br>CALL<br>DA                       | 10,5<br><b>LD</b><br>r <sub>2</sub> ,x,R <sub>1</sub> |                                                    |                                                    |                                              |                               |                                        |                               |                  | 6,5<br><b>SCF</b> |

|                    | E | 6,5<br><b>RR</b><br>R <sub>1</sub>   | 6,5<br>RR<br>IR <sub>1</sub>          |                                                        | 6,5<br><b>LD</b><br>r <sub>1</sub> ,lR <sub>2</sub>      | 10,5<br><b>LD</b><br>R <sub>2</sub> ,R <sub>1</sub>  | 10,5<br><b>LD</b><br>IR <sub>2</sub> ,R <sub>1</sub>  | 10,5<br><b>LD</b><br>R <sub>1</sub> ,IM  | 10,5<br><b>LD</b><br>IR <sub>1</sub> ,IM              |                                                    |                                                    |                                              |                               |                                        |                               |                  | 6,5<br><b>CCF</b> |

|                    | F | 8,5<br><b>SWAP</b><br>R <sub>1</sub> | 8,5<br>SWAP<br>IR1                    |                                                        | 6,5<br><b>LD</b><br>lr <sub>1</sub> ,r <sub>2</sub>      |                                                      | 10,5<br><b>LD</b><br>R <sub>2</sub> ,IR <sub>1</sub>  |                                          |                                                       |                                                    |                                                    | <u> </u>                                     |                               |                                        | ₩                             |                  | NOP               |

|                    |   |                                      |                                       |                                                        |                                                          |                                                      |                                                       |                                          |                                                       |                                                    |                                                    | <u> </u>                                     | <del> </del>                  |                                        | <b>/</b>                      |                  | <del></del>       |

|                    |   |                                      |                                       | 2                                                      |                                                          |                                                      |                                                       | 3                                        |                                                       |                                                    |                                                    | 2                                            |                               |                                        | 3                             |                  |                   |

Bytes per Instruction

Legend:

R = 8-bit address

r = 4-bit address

R<sub>1</sub> or r<sub>1</sub> = Dst address

R<sub>2</sub> or r<sub>2</sub> = Src address

Sequence: Opcode, First Operand, Second Operand NOTE: The blank areas are not defined.

<sup>\*2-</sup>byte instruction; fetch cycle appears as a 3-byte instruction

72C 05229

### 9984043 ZILOG INC

#### **ABSOLUTE MAXIMUM RATINGS**

Voltages on all pins\* with respect to GND . . . . . . . . . . . . . - 0.3V to +7.0V Operating Ambient Temperature ............See Ordering Information Storage Temperature . . . . . . . . . - 65°C to +150°C

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above these indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### STANDARD TEST CONDITIONS

The DC characteristics listed below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pin.

Standard conditions are as follows:

- +4.75V

V<sub>CC</sub>

+5.25V

- GND = 0V

- $0^{\circ}$ C  $\leq$   $T_{A} \leq$  + 70  $^{\circ}$ C for S (Standard temperature)

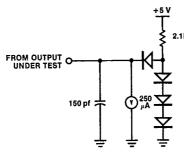

Figure 16. Test Load 1

Figure 17a. Z86L81 External Clock Interface Circuit

Figure 17b. Z86L85 External Clock Interface Circuit

#### **DC CHARACTERISTICS**

| Symbol          | Parameter                      | Min         | Max | Unit | Test Condition                     |

|-----------------|--------------------------------|-------------|-----|------|------------------------------------|

| V <sub>CH</sub> | Clock Input High Voltage       | 3.8         | Vcc | ٧    | Driven by External Clock Generator |

| V <sub>CL</sub> | Clock Input Low Voltage        | -0.3        | 0.8 | ٧    | Driven by External Clock Generator |

| V <sub>IH</sub> | Input High Voltage             | 2.0         | Vcc | ٧    |                                    |

| V <sub>IL</sub> | Input Low Voltage              | -0.3        | 8,0 | V    |                                    |

| V <sub>RH</sub> | Reset Input High Voltage       | 3.8         | Vcc | V    |                                    |

| V <sub>RL</sub> | Reset Input Low Voltage        | -0.3        | 0.8 | V    |                                    |

| VOH             | Output High Voltage            | 2.4         |     | V    | $I_{OH} = -250 \mu\text{A}$        |

| VOL             | Output Low Voltage             |             | 0.4 | V    | $I_{OL} = +2.0 \text{mA}$          |

| l <sub>IL</sub> | Input Leakage                  | <b>– 10</b> | 10  | μΑ   | $0V \le V_{1N} \le +5.25V$         |

| loL             | Output Leakage                 | -10         | 10  | μΑ   | $0V \le V_{IN} \le +5.25V$         |

| I <sub>IR</sub> | Reset Input Current            |             | -50 | μA   | $V_{CC} = +5.25V, V_{RL} = 0V$     |

| Icc             | V <sub>CC</sub> Supply Current |             | 90  | mA   | 8 MHz Clock (86L81/85-8L)          |

| IMM             | V <sub>MM</sub> Supply Current |             | 10  | mA   | Power Down Mode (Z86L85 only)      |

| V <sub>MM</sub> | Backup Supply Voltage          | 3           | Vcc | V    | Power Down (Z86L85 only)           |

2343-014,015,016

<sup>\*</sup>Except RESET

### **AC CHARACTERISTICS**

External I/O or Memory Read and Write Timing

72C 05230

T-49-19-59

Figure 18. External I/O or Memory Read/Write Timing

|               |           |                                           | Z86L81 |     |           |

|---------------|-----------|-------------------------------------------|--------|-----|-----------|

| Number        | Symbol    | Parameter                                 | Min    | Max | Notes‡*†° |

| 1             | TdA(AS)   | Address Valid to AS ↑ Delay               | 50     |     | 1,2       |

| 2             | TdAS(A)   | AS to Address Float Delay                 | 70     |     | 1,2       |

| 3             | TdAS(DR)  | AS to Read Data Required Valid            |        | 360 | 1,2,3     |

| 4             | TwAS      | AS Low Width                              | 80     |     | 1,2       |

| 5             | TdAz(DS)  | Address Float to DS ↓                     | 0      |     |           |

| 6             | TwDSR     | DS (Read) Low Width                       | 250    |     | 1,2,3     |

| <del></del> 7 | TwDSW     | DS (Write) Low Width                      | 160    |     | 1,2,3     |

| 8             | TdDSR(DR) | DS                                        |        | 200 | 1,2,3     |

| 9             | ThDR(DS)  | Read Data to DS † Hold Time               | 0      |     |           |

| 10            | TdDS(A)   | DS to Address Active Delay                | 70     |     | 1,2       |

| 11            | TdDS(AS)  | DS † to AS ↓ Delay                        | 70     |     | 1,2       |

| 12            | TdR/W(AS) | R/W Valid to AS t Delay                   | 50     |     | 1,2       |

| 13            | TdDS(R/W) | DS t to R/W Not Valid                     | 60     |     | 1,2       |

| 14            | TdDW(DSW) | Write Data Valid to DS (Write) ↓ Delay    | 50     |     | 1,2       |

| 15            | TdDS(DW)  | DS to Write Data Not Valid Delay          | 70     |     | 1,2       |

| 16            | TdA(DR)   | Address Valid to Read Data Required Valid |        | 410 | 1,2,3     |

| 17            | TdAS(DS)  | AS ↑ to DS ↓ Delay                        | 80     |     | 1,2       |

#### NOTES:

- NOTES:

1. Timing numbers given are for minimum TpC.

2. Also see clock cycle time dependent characteristics table.

3. When using extended memory timing add 2 TpC.

- ‡ All timing references use 2.0V for a logic "1" and 0.8V for a logic "0".

\* All units in nanoseconds (ns).

† Timings are preliminary and subject to change.

Test Load 1

72C 05231

#### T-49-19-59

## 9984043 ZILOG INC

**AC CHARACTERISTICS**

Additional Timing Table

Figure 19. Additional Timing

|        |             |                                   | Z86L81 |      |         |

|--------|-------------|-----------------------------------|--------|------|---------|

| Number | Symbol      | Parameter                         | Min    | Max  | Notes*† |

| 1      | TpC         | Input Clock Period                | 125    | 1000 | 1       |

| 2      | TrC,TfC     | Clock Input Rise and Fall Times   |        | 25   | 1       |

| 3      | TwC         | Input Clock Width                 | 37     |      | 1       |

| 4      | TwTinL      | Timer Input Low Width             | 100    |      | 2       |

| 5      | TwTinH      | Timer Input High Width            | 3TpC   |      | 2       |

| 6      | TpTin       | Timer Input Period                | 8TpC   |      | 2       |

| 7      | TrTin,TfTin | Timer Input Rise and Fall Times   |        | 100  | 2       |

| 8      | TwiL        | Interrupt Request Input Low Time  | 100    |      | 2,3     |

|        |             |                                   | ЗТрС   |      | 2,4     |

| 9      | TwiH        | Interrupt Request Input High Time | 3TpC   |      | 2,3     |

- 1. Clock timing references use 3.8V for a logic "1" and 0.8V for a logic "0".

2. Timing references use 2.0V for a logic "1" and 0.8V for a logic "0".

3. Interrupt request via Port 3, P3<sub>1</sub>-P3<sub>3</sub>.

- 4. Interrupt request via Port 3, P3<sub>0</sub>.

\* All units in nanoseconds (ns).

† Timings are preliminary and subject to change.

Z86L81/85

#### 9984043 ZILOG INC **AC CHARACTERISTICS**

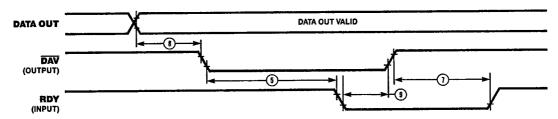

Handshake Timing

Figure 20a. Input Handshake Timing

Figure 20b. Output Handshake Timing

|        |              |                             | Z86L8 | Z86L81/85-8L |         |  |

|--------|--------------|-----------------------------|-------|--------------|---------|--|

| Number | Symbol       | Parameter                   | Min   | Max          | Notes‡† |  |

| 1      | TsDI(DAV)    | Data In Setup Time          | 0     |              |         |  |

| 2      | ThDI(DAV)    | Data In Hold Time           | 230   |              |         |  |

| 3      | TwDAV        | Data Available Width        | 175   |              |         |  |

| 4      | TdDAVIf(RDY) | DAV Input to RDY I Delay    |       | 175          | 1,2     |  |

| 5      | TdDAVOf(RDY) | DAV                         | 0     |              | 1,3     |  |

| 6      | TdDAVIr(RDY) | DAV † Input to RDY † Delay  |       | 175          | 1,2     |  |

| 7      | TdDAVOr(RDY) | DAV † Output to RDY † Delay | 0     |              | 1,3     |  |

| 8      | TdDO(DAV)    | Data Out to DAV ↓ Delay     | 50    |              | 1       |  |

| 9      | TdRDY(DAV)   | Rdy Input to DAV ↑ Delay    | 0     | 200          | 1       |  |

NOTES:

1. Test load 1

‡ All timing references use 2.0V for a logic "1" and 0.8V for a logic "0".

\* All units in nanoseconds (ns).

2. Input handshake 3. Output handshake

† Timings are preliminary and subject to change.

### **CLOCK CYCLE TIME-DEPENDENT CHARACTERISTICS**

|        |           | Z86L81/85-8L<br>8 MHz |        |           | Z86L81/85-8L<br>8 MHz |

|--------|-----------|-----------------------|--------|-----------|-----------------------|

| Number | Symbol    | Equation              | Number | Symbol    | Equation              |

| 1      | TdA(AS)   | TpC-75                | 13     | TdDS(R/W) | TpC-65                |

| 2      | TdAS(A)   | TpC-55                | 14     | TdDW(DSW) | TpC-75                |

| 3      | TdAS(DR)  | 4TpC-140*             | 15     | TdDS(DW)  | TpC-55                |

| 4      | TwAS      | TpC-45                | 16     | TdA(DR)   | 5TpC-215*             |

| 6      | TwDSR     | 3TpC-125*             | 17     | TdAS(DS)  | TpC-45                |

| 7      | TwDSW     | 2TpC-90*              |        |           |                       |

| 8      | TdDSR(DR) | 3TpC-175*             |        |           |                       |

| 10     | Td(DS)A   | TpC-55                |        |           |                       |

| 11     | TdDS(AS)  | TpC-55                |        |           |                       |

| 12     | TdR/W(AS) | TpC-75                |        |           |                       |

<sup>\*</sup>Add 2TpC when using extended memory timing

#### **ORDERING INFORMATION**

| Z8 Low Power ROMIess MCU, 8.0 MHz |  |  |  |  |  |  |  |

|-----------------------------------|--|--|--|--|--|--|--|

| 44-pin PCC                        |  |  |  |  |  |  |  |

| Z86L81 VS†                        |  |  |  |  |  |  |  |

|                                   |  |  |  |  |  |  |  |

|                                   |  |  |  |  |  |  |  |

#### Z8 Low Power-Down ROMless MCU, 8.0 MCU 44-pin LCC 40-pin DIP Z86L85 PS Z86L85 VS† Z86L85 CS

#### Codes

First letter is for package; second letter is for temperature.

C = Ceramic DIP P = Plastic DIP L = Ceramic LCC V = Plastic PCC

**TEMPERATURE**  $S = 0 \,^{\circ}\text{C to} + 70 \,^{\circ}\text{C}$   $E = -40 \,^{\circ}\text{C to} + 85 \,^{\circ}\text{C}$

M\*= -55°C to +125°C

= Protopack = Low Profile Protopack DIP = Dual-In-Line Package LCC = Leadless Chip Carrier PCC = Plastic Chip Carrier (Leaded)

FLOW B = 883 Class B

\*For Military Orders, contact your local Zilog Sales Office for Military Electrical Specifications.

†Available soon.