MOS LSI

# TMS 3126, 3127, 3128, 3129, 3130, 3131, 3132 LC, NC DUAL 96-, 100-, 128-, 132-, 133-, 136-, 144-BIT STATIC SHIFT REGISTERS

BULLETIN NO. DL-S 7512263, MAY 1975

- DC to 2.5-MHz Operation

- Static Configuration

- Single TTL-Compatible Clock

- Inputs and Outputs Fully TTL-Compatible

- **Push-Pull Output Buffers**

- On-Chip Recirculate Logic

- Power Supplies . . . 5 V, -12 V

- Seven Standard Bit Lengths

### description

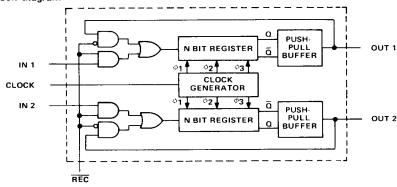

This series is a family of MOS dual static shift registers. These circuits are monolithically constructed by use of thick-oxide techniques and P-channel enhancement-type transistors, which allow TTL-compatibility for ease of system design.

An on-chip clock generator provides three internal phases from a single external TTL-level clock. All inputs including the low-capacitance clock can be driven directly from Series 74 TTL circuits without the need for pull-up resistors. The push-pull outputs are compatible with Series 74 TTL and have a fan-out

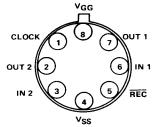

#### TO-99 HERMETICALLY SEALED PACKAGE (TOP VIEW)

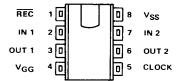

#### 8-PIN PLASTIC DUAL-IN-LINE PACKAGE (TOP VIEW)

capability of one TTL load. A current limiter has been incorporated in the output buffers to reduce power dissipation when driving bipolar logic. No external components are needed for TTL interface.

Cross-coupled inverters (flip-flops) are employed to implement each bit storage location. This static design allows input data rates from dc to 2.5 MHz and long-term data storage. Recirculate logic has been incorporated on the chip to simplify system design.

These devices are offered in the TO-99 hermetically sealed package (suffix LC) and in the 8-pin dual-in-line plastic package (suffix NC). The 8-pin dual-in-line package is designed for insertion in mounting-hole rows on 300-mil centers. These devices are characterized for operation from  $-25^{\circ}$ C to  $85^{\circ}$ C.

### applications

Various bit lengths are offered to cover most computer peripheral applications such as printers, buffer memories, and CRT refresh memories.

### operation

134

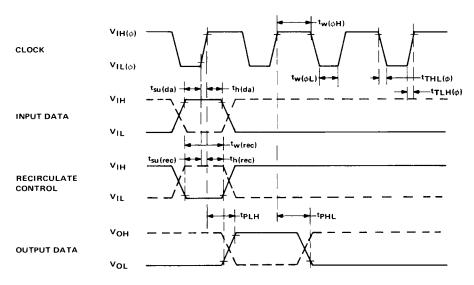

Transfer of data into and out of the shift registers occurs on the low-to-high transition of the clock. Input data must be set up a minimum time before the low-to-high clock transition and must be held for a minimum time after that transition. For long-term data storage, the clock must be maintained high, and in this mode the recirculate and data input levels may change without affecting the data output levels.

Recirculate occurs on the low-to-high clock transition with the recirculate control low. The recirculate control must be set up a minimum time before this transition and held a minimum time after the transition. Data is entered with the recirculate control high. During recirculation, data is continuously available at the output and the data input is inhibited

Texas Instruments

POST OFFICE BOX 5012 . DALLAS, TEXAS 75222

# TMS 3126, 3127, 3128, 3129, 3130, 3131, 3132 LC, NC DUAL 96-, 100-, 128-, 132-, 133-, 136-, 144-BIT STATIC SHIFT REGISTERS

# functional block diagram

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)\*

| Supply voltage, V <sub>GG</sub> (see Note 1) |   |  |  |  |  |  |  |  |  |  |  | -20 V to 0.3 V                    |

|----------------------------------------------|---|--|--|--|--|--|--|--|--|--|--|-----------------------------------|

| Clock input voltage (see Note 1)             |   |  |  |  |  |  |  |  |  |  |  | -20 V to 0.3 V                    |

| Data input voltage (see Note 1)              |   |  |  |  |  |  |  |  |  |  |  | -20  V to $0.3  V$                |

| Operating free-air temperature range         | • |  |  |  |  |  |  |  |  |  |  | $-25^{\circ}$ C to $85^{\circ}$ C |

| Storage temperature range                    |   |  |  |  |  |  |  |  |  |  |  | -55°C to 150°C                    |

NOTE 1: Under absolute maximum ratings, voltage values are with respect to the normally most-positive supply, V<sub>SS</sub> (substrate). Throughout the remainder of this data sheet voltage values are with respect to a floating ground.

## recommended operating conditions

| PARAMETER                                                      | MIN                  | NOM  | MAX     | UNIT |

|----------------------------------------------------------------|----------------------|------|---------|------|

| Supply voltage, V <sub>GG</sub>                                | -11                  | -12  | -13     | V    |

| Supply voltage, VSS                                            | 4.5                  | 5    | 5.5     |      |

| High-level input voltage, V <sub>IH</sub>                      | V <sub>SS</sub> −1.8 |      |         | V    |

| Low-level input voltage, VIL                                   |                      | V    | SS -3.9 | V    |

| Clock pulse transition time, low-to-high level, tTLH( $\phi$ ) |                      | 0.02 | 5       | μs   |

| Clock pulse transition time, high-to-low level, tTHL( $\phi$ ) |                      | 0.02 | 5       | μs   |

| Pulse width, clock high, tw(oH)                                | 300                  |      | ×       | ns   |

| Pulse width, clock low, $t_{W(\phi L)}$                        | 100                  | 1    | 000000  | ns   |

| Recirculate pulse width, tw(rec)                               | 125                  |      |         | ns   |

| Data setup time, t <sub>su(da)</sub>                           | 80                   | _    |         | ns   |

| Recirculate setup time, t <sub>su</sub> (rec)                  | 100                  |      |         | ns   |

| Data hold time, th(da)                                         | 80                   |      |         | ns   |

| Recirculate hold time, th(rec)                                 | 25                   |      |         | ns   |

| Clock frequency, $f_{\phi}$                                    | 0                    |      | 2.5     | MHz  |

| Operating free-air temperature, TA                             | 25                   |      | 85      | C    |

575

TEXAS INSTRUMENTS

POST OFFICE BOX 5012 • DALLAS, TEXAS 75222

135

<sup>\*</sup>Comment: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# TMS 3126, 3127, 3128, 3129, 3130, 3131, 3132 LC, NC DUAL 96-, 100-, 128-, 132-, 133-, 136-, 144-BIT STATIC SHIFT REGISTERS

# electrical characteristics under nominal operating conditions, $T_A = -25^{\circ} C$ to $85^{\circ} C$ (unless otherwise noted)

|                    | PARAMETER                                  | TEST C                   | CONDITIONS              | MIN | TYP <sup>†</sup> | MAX  | UNIT |

|--------------------|--------------------------------------------|--------------------------|-------------------------|-----|------------------|------|------|

| Voн                | High-level output voltage                  | 1 <sub>OH</sub> = 0.2 mA |                         | 4   |                  |      | V    |

| VOL                | Low-level output voltage                   | 1 <sub>OL</sub> = 1.6 mA |                         |     |                  | 0.4  | V    |

| T <sub>I</sub>     | Input current (all inputs)                 | V <sub>I</sub> = 0.8 V   |                         |     |                  | -500 | пA   |

| los                | Short-circuit output current               | V <sub>O</sub> = 0 V,    | V <sub>GG</sub> =11 V   |     |                  | -10  | mA   |

| IGG                | Supply current from VGG                    | f = 2.5 MHz,             | 1 TTL load (see Note 2) |     | -22              | -30  | mA   |

| PD                 | Power dissipation                          | f = 2.5 MHz,             | 1 TTL load (see Note 2) |     | 374              | 510  | mW   |

| Ci                 | Input capacitance, all inputs except clock | V <sub>I</sub> = 5 V,    | f = 1 MHz               |     | 3.5              | 5    | pF   |

| C <sub>i</sub> (φ) | Clock input capacitance                    | $V_{I(\phi)} = 5 V$ ,    | f = 1 MHz               |     | 3.5              | 5    | pF   |

$<sup>^{\</sup>dagger}$  All typical values are at  $T_A = 25^{\circ}$  C.

NOTE 2: For test purposes, a TTL load is simulated by a load of 2.7 k $\Omega$  and 20 pF between the output and V  $_{SS}$  .

# switching characteristics under nominal operating conditions, $T_{\Delta} = -25^{\circ} \text{C}$ to $85^{\circ} \text{C}$

|                  | PARAMETER                            | TEST CONDITIONS                | MIN | MAX | UNIT |

|------------------|--------------------------------------|--------------------------------|-----|-----|------|

|                  | Propagation delay time, low-to-high- |                                |     | 250 |      |

| <sup>†</sup> PLH | level output from clock              | 1 1 - 1 TT) ( A) 2)            |     | 250 | ns   |

|                  | Propagation delay time, high-to-low- | Load = 1 TTL gate (see Note 3) |     | 250 |      |

| <sup>t</sup> PHL | level output from clock              |                                |     | 250 | ns   |

NOTE 3: For test purposes, a TTL load is simulated by a load of 2.7 k $\Omega$  and 20 pF between the output and V  $_{

m NS}$  .

### voltage waveforms

NOTE: All timing measurements are made at 10% or 90% points.

PRINTED IN U.S.A.

575

TEXAS INSTRUMENTS

POST OFFICE BOX 5012 • DALLAS. TEXAS 75222

TEXAS INSTRUMENTS RESERVES THE RIGHT TO MAKE CHANGES AT ANY TIME IN ORDER TO IMPROVE DESIGN AND TO SUPPLY THE BEST PRODUCT POSSIBLE.