# A CMOS KEYBÖARD DATA ENTRY SYSTEM FOR BUS ORIENTED MEMORY SYSTEMS

Prepared by:

Mike Hadley

Digital Systems Applications

This application note describes a keypad to binary data entry system for use with NMOS or CMOS memories, either in a minicomputer/microprocessor application or as a part of any logic system containing random access memory. Manual data entry using a keypad avoids the use of a binary format, offering increased speed and accuracy of manual direct memory accessing.

MOTOROLA Semiconductor Products Inc.

# A CMOS KEYBOARD DATA ENTRY SYSTEMS FOR BUS ORIENTED MEMORY SYSTEMS

#### INTRODUCTION

Manual loading of data into RAM memory systems is at best a tedious process. The method most commonly used is an array of toggle switches that when on, effect a binary "1" and when off a "0". This method requires operation in binary, an inconvenience as well as a time consuming task. This note describes a data entry system using a 4 x 4 keypad switch array coded in hexadecimal. This in effect allows memory loading in calculator style, with each keystroke coding four binary bits. Any CMOS compatible memory system with external control of an address bus up to sixteen bits and a data bus up to eight bits can make use of this keyboard entry system without modifications.

A typical application is in an M6800 Microprocessor system. When the MPU is in HALT, both the address bus drivers and the data bus drivers are in a 3-state mode. This allows control of both buses with an external device such as the data entry system to be described.

#### **DESIGN AND OPERATION**

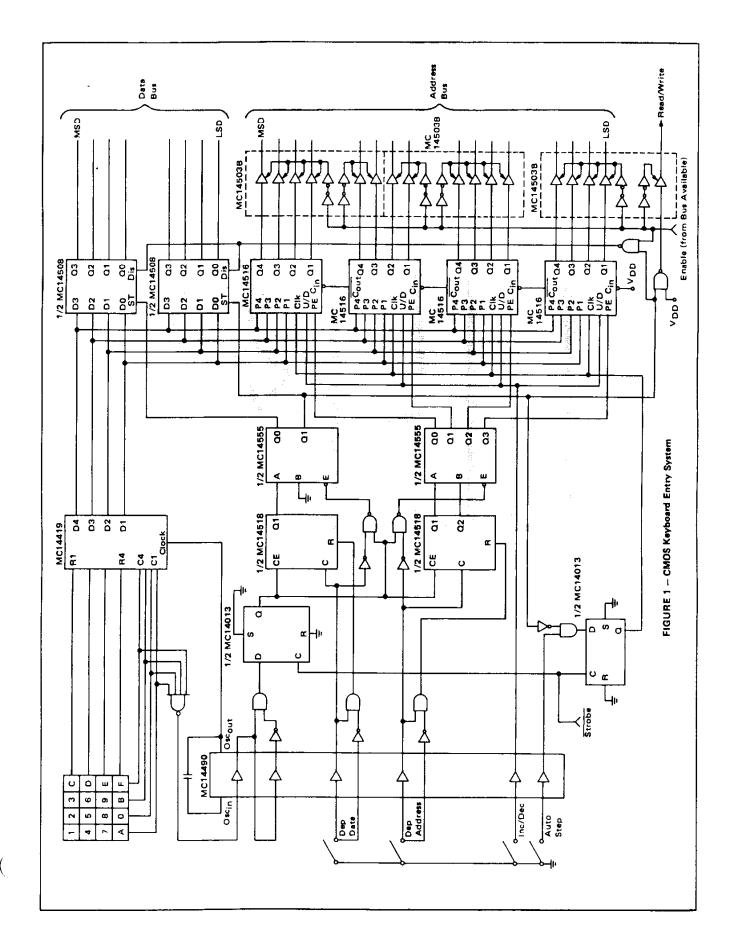

Several relatively new CMOS devices are presented in this design as shown in Figure 1. The MC14419 is a 4 x 4 keypad to binary encoder with an internal strobe generator. When a key is depressed on the keypad, a row and a column input associated with the key are forced to ground, and the binary representation of the depressed key appears on the four output lines. In this way one keystroke encodes four binary lines. Should two or more keys be depressed simultaneously, the MC14419 outputs will remain zeros, with no internal strobe generated (a strobe will be generated with external logic, however). Since both data entry and addressing must be done using the same keyboard, additional circuitry is required to route these binary coded hexadecimal numbers onto either the address bus or the data bus.

Control of data routing is via four SPST toggle switches, all of which use the MC14490 hex bounce eliminator to insure bounce free logic transitions. This leaves two additional bounce eliminators in the MC14490 package, for use in conjunction with a 2-input AND gate, an inverter, and a 4-input NAND gate to generate a strobe pulse when any one of the sixteen keys on the 4 x 4 keypad is depressed. The output from this configuration is a pulse equal to four periods of the internal clock of the MC14490, and occurs eight clock periods after the depressed switch ceases to bounce. Only one pulse is generated when a key is depressed; bouncing or noise cannot generate additional pulses. An extra inverter-

AND gate combination is added to each of the two debouncers used for the Deposit-Address switch and the Deposit-Data switch. The output of the AND gate will produce a "1" whenever the associated switch is toggled from its normally high position to a low (ground) state. The output will bounce with the switch, and then remain high until the debouncer goes low (four clock periods after bouncing ceases). This signal serves to reset the counters immediately before data entry or addressing is to take place, insuring that the first number entered will be the most significant digit (MSD).

As designed, the keyboard will control an eight bit data bus and a sixteen bit address bus. This implies that in addition to controlling data routing to either the address or data bus, control must also determine which of the two 4-bit data positions are to accept data, or which of the four 4-bit address positions are to accept data. This is done with an MC14518 dual 4-bit counter and an MC14555 dual, binary to one-of-four data router. When the counters are enabled with a Deposit Data or a Deposit Address switch, a strobe pulse generated when a key is depressed propagates through the selected decoder to the enable of the most significant counter (for addressing) or latch (for data entry). The trailing edge of the strobe pulse will toggle the selected counter so that the next strobe pulse generated (corresponding to the next number to be entered) will be routed, not to the most significant counter or latch, but to least significant latch (if data) or the third counter (if address). In this manner, if the Deposit Address switch is set, the first number entered will be deposited in the most significant (fourth) counter. the second number entered will be deposited in the third counter, the third number into the second counter, and the fourth number into the first, or least significant counter. The data input system works similarly with the two latches (the single MC14508) whose outputs connect to the data bus.

Since most memory systems are sequential, in that the next data to be used is located at either the next higher or next lower address location, the data routing circuitry was made to automatically increment or decrement the address after entering the least significant (last) 4-bit number. Two toggle switches control this function, the Increment/Decrement switch and the Automatic-Step switch. The Increment/Decrement switch controls the direction of the step. The Auto-Step function enables or disables the automatic step feature. To examine data as it is entered, Auto-Step is disabled, allowing entered data to appear immediately after the least significant data 4-bit

Circuit diagrams external to Motorola products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information in this Application Note has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola inc. or others.

number has been entered. In this mode of operation, Auto-Step must be depressed to step to the next address location that is to receive data. After data entry has been completed, the Auto-Step switch can also be used to step through memory in order to examine previously written memory contents.

A single input line (Enable) controls access by the keyboard entry system. If the Enable line is brought low, all outputs from the system are forced to the 3-state mode. On the data bus, this is accomplished internal to the MC14508 dual latch. The address bus however requires 3-state buffers, and uses three MC14503 packages containing six buffers per package.

The additional input, Strobe, is provided for use with CMOS memory systems, to meet the requirement that CMOS RAMs be disabled before their address location is allowed to change. The MC14013 dual type D flip-flop accomplishes this by synchronizing both the preset inputs and the clock inputs of the MC14516 address counters to the Strobe positive transition. When Strobe goes from "0" to "1", data present at the D inputs (either from clock or preset enable of the MC14516) will propagate to the Q outputs. The address contained in the MC14516 counters is then allowed to change via preset or clock. Thus, the counters are allowed to change state only when the CMOS memory is disabled, assuming that the Strobe input, when high, disables the CMOS RAM memory.

When controlling a memory system that does not require the above synchronization, the MC14013 and the Strobe input can be eliminated.

The remaining output line is a Read/Write line required to control memory operation. When the least significant data 4-bit word is written into the MC14508 latch, the Read/Write line goes low and the MC14508 outputs change from 3-state to active and present the entire 8-bit word to be written onto the data bus.

When the system Enable line goes low (inactive), the Read/Write line goes into a 3-state mode in order to allow another device to control the memory Read/Write function.

# MODIFICATIONS

The keyboard entry system as described is ideally suited for 8-bit data, 16-bit address, bus oriented CMOS memory systems. Modifications of the general design can optimize cost and performance when used with variations of the memory system described.

In 4-bit memory systems, for example, one-half of the MC14518 and MC14555 pertaining to the data bus as well as one-half of the MC14508 latch can be eliminated. In this case the MC14508 could be replaced with a package of MC14503 3-state buffers. Numbers entered would then completely fill the data bus, and no designation of LSD or MSD would be in order. In the same manner a 12 or 16-bit data bus can be controlled with the addition of another MC14508 latch. The only modification required would be the connection of the

MC14555 to the MC14518 (on the data side) as is done for the 16-bit address bus.

Modifications involving the address bus are carried out in a similar manner. Even when using a 16-bit address bus, complexity and cost can be reduced by eliminating the MC14516 counters associated with address locations that contain no memory under control of the keyboard entry system. For example, in an MPU system, RAM may occupy only the locations 0000 through 0FFF. In this case the MSD of the address is always zero and the associated counter can be eliminated.

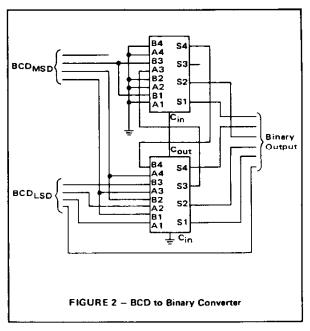

Modifications can also be made for data entry and addressing in BCD format. Data entry is no problem as certain keys are no longer present. Addressing, on the other hand, must have a conversion from BCD to binary in order not to waste memory space corresponding to those addresses that use the hexadecimal digits between 9 and 16. This is accomplished as shown in Figure 2 for 64 words of memory (6 address lines). For larger memory systems this BCD to binary conversion becomes quite complex, requiring a number of packages.

## SUMMARY

This project was designed not only for use as a permanent controller, physically mounted near a memory system (such as a front panel) but also as a hand held unit with only a cable for connection to the buses, read/write line, enable line, strobe, power and ground. In this way, many memory systems can be loaded and controlled with the same data entry system, although access to only one at a time would be realizable. Whether part of a system or hand held, a keyboard entry system greatly simplifies and speeds up manual data entry into memory systems. At the same time erroneous data entered due to the need for entry in binary format is eliminated.

"HI: This item is marked with the letters 'HI' to indicate that these documents are included for Historical Information only. This document was developed at a Design Centre strategically located throughout the global community and was originally written to support a local need. Whilst the basic concepts of this publication may have broad global applicability, specific Motorola semiconductor parts may be referred to that are currently available for limited distribution in a specific region and may only be supported by the country of origin of the document in which it is referenced. However, before attempting to design-in a device referenced, the user should contact the local Motorola supplier or sales office to confirm product availability and if application support is available.

All products are sold on Motorola's Terms & Conditions of Supply. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Motorola's Terms & Conditions of Supply is available on request.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any liconse under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was regligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, inc. Motorola, inc. is an Equal Opportunity/Affirmative Action Employer.

The Customer should ensure that it has the most up to date version of the document by contacting its local Motorola office. This document supersedes any earlier documentation relating to the products referred to herein. The information contained in this document is current at the date of publication. It may subsequently be updated, revised or withdrawn.

### Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motoroia Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

MOTOROLA

A10187-1 PRINTED IN USA 7/93 MPS/POD