12 MACROCELL EPLD

**EP512**

#### **FEATURES**

- High Performance logic replacement for TTL and 74HC or 74HCT SSI and MSI logic.

- High Speed, tpd = 25ns, and 40MHz operating frequency.

- "Zero Power" (150 µA Standby Current).

- Twelve Macrocells with configurable I/O architecture allowing up to 22 inputs (10 dedicated, 12 I/O) and 12 outputs.

- Eight configurable inputs which can implement latch, register, or flow-through mode; synchronous or asynchronous operation.

- Programmable product term allocation allowing up to 16 product terms for a single Macrocell.

- Programmable registers providing D, T, SR or JK flip-flops with Clear, Preset, and Clock control.

- Two product terms for all Macrocell control signals (OE, Preset, Clear and Clock).

- Dual feedback on all Macrocells for buried register implementation and input usage.

- A+PLUS software support featuring Schematic Capture, Netlist, Boolean Equation and State Machine design entry.

- Space saving 24 pin DIP, 300 mil, and 28 pin JLCC/PLCC packages.

#### **CONNECTION DIAGRAM**

## **GENERAL DESCRIPTION**

The Altera EP512 provides a User-Configurable, High-Performance solution for general purpose logic and custom control (state machine) functions. The EP512 features an enhanced PLD architecture to easily integrate 74ALS and HC (HCT) SSI and MSI logic. In addition, a single EP512 can also replace multiple programmable logic devices (22V10, 20RA10, 20L10, 20R10).

The EP512 uses sum-of-products logic providing a configurable AND-OR structure. The device can implement combinatorial, latched, and registered logic functions, active high or low. The EP512 contains a total of 12 I/O Macrocells, 8 user-configurable input structures (latch, register or flow-through operation) and 2 inputs that can be programmed to serve as either combinatorial inputs or clock inputs for the input and output register functions.

A unique feature of the EP512 is the ability to re-allocate product terms between adjacent macrocells allowing a single macrocell to have 8, 12 or 16 product terms. In addition, each macrocell contains two dedicated product terms for each control signal: Output Enable, Preset, Clear, and Asynchronous Clock. Each macrocell also contains dual feedback allowing the logic to be buried while reserving the I/O pin as an additional input.

The EP512 uses advanced CMOS EPROM cells as logic control elements. This technology allows the EP512 to operate in high performance applications while significantly reducing the power consumption. Other advantages include: 100% generic testing (all devices are 100% tested at the factory). The device can be erased with ultraviolet light. Design changes are no longer costly, nor is there a need for testing after programming.

Programming the EP512 is accomplished with the use of Altera's A+PLUS development software which supports four different design entry methods. Once the circuit has been tested, the A+PLUS software performs automatic translation into logical equations, Boolean minimization, and design fitting directly into an EP512.

### PRELIMINARY DATA

NOTICE: THIS IS NOT A FINAL SPECIFICATION. SOME PARAMETRIC LIMITS ARE SUBJECT TO CHANGE.

**REV. 2.0**

2

#### **FUNCTIONAL DESCRIPTION**

The EP512 is an Erasable Programmable Logic Device (EPLD) which uses a CMOS EPROM technology to configure connections in a programmable AND logic array. The EP512's innovative architecture allows it to integrate many standard TTL functions. The device also contains an enhanced I/O architecture which provides advanced functional capability for user-configurable logic.

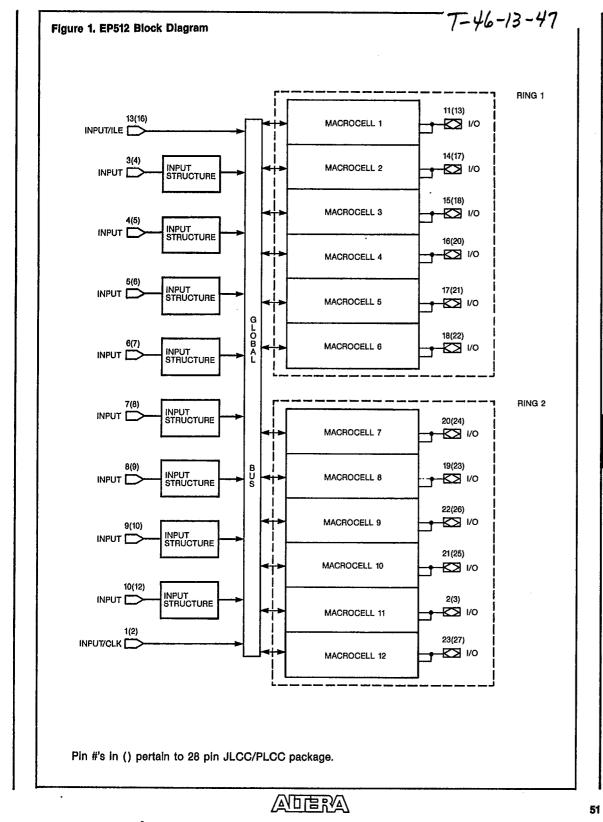

Figure 1 shows the EP512 Block Diagram. Externally, the EP512 provides 10 dedicated inputs and 12 I/O pins programmed for input, output, or bi-directional operation. The device contains 12 macrocells which can be independently configured.

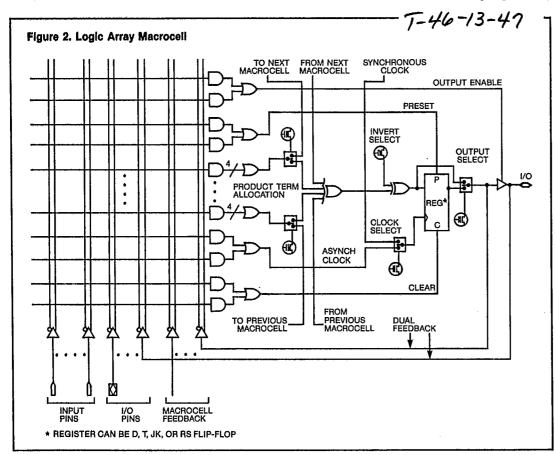

Figure 2 shows an EP512 Macrocell. The internal architecture uses a sum-of-products (AND-OR) structure. Inputs to the programmable AND array come from the true and complement forms of the 10 dedicated inputs, 12 macrocell feedback signals and 12 I/O pins. Each EP512 Macrocell contains 16 product terms. Eight product terms are dedicated to control signals (OE, CLK, Preset and Clear), while eight product terms are used for the general data array. Each EP512 product term represents a 68 input AND gate.

At the intersection point between an AND array input and a product term is an EPROM control cell. In the erased state, all cell connections are made. This means both the true and complement of all array inputs are connected to each product term. During the programming process, selected connections are opened. Therefore, any product term may be connected to the true or complement of any array input signal. When both the true and complement of an array input signal are left connected, a logical false results on the output of the AND gate. If both the true and complement of any array input signal are programmed open, then a logical "don't care" results for that input. If all 68 inputs for a given product term are programmed open, then a logical true results on the output of the corresponding AND gate.

The EP512 contains 10 dedicated inputs, 8 data inputs and 2 programmable system clock inputs (ILE and CLK). ILE (pin 13) provides synchronous clocking to the input structures while CLK (pin 1) provides synchronous clocking to the macrocell registers. These system clocks are connected directly from the EP512 external pins. When using these system clocks, ILE is negative edge triggered (data transitions occur on the falling edge of ILE)

and CLK is positive edge triggered (data transitions occur on the rising edge of CLK). ILE and CLK may also be used as general purpose inputs,

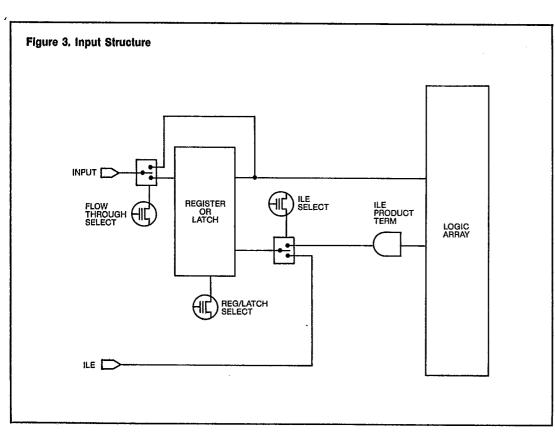

For asynchronous clocking of the input structure, the clock signal is derived from a dedicated product term (see Figure 3). For asynchronous clocking of the macrocell registers, the clock signal is derived from two dedicated product terms (see Figure 2). Each input structure and macrocell register is individually configurable allowing a mixture of synchronous and asynchronous clocking on both the input structures and the macrocell registers.

## **INPUT STRUCTURE**

Figure 3 shows a functional block diagram of the input structure of the EP512. The EP512 contains 8 programmable input structures that may be individually configured as one of the following:

- —Synchronous D-type register

—Asynchronous D-type register

- —Synchronous input latch

- —Asynchronous input latch

- -Flow through latch

The dedicated ILE input (pin 13) serves as a synchronous clock for both synchronous input latch and synchronous input register modes. For

asynchronous clocking, a dedicated product term is available and provides clocking for the Asynchronous Register and Asynchronous Latch modes. The ILE Select Mux, shown in Figure 3, determines whether the input clocking will be provided by the dedicated ILE input (synchronous mode) or the dedicated Product term (asynchronous mode). Table 1 shows the Input Structure Function Table using the ILE (pin 13) input for control. Note, when using synchronous clocks (ILE), the input register is negative edge triggered. Positive edge triggered operation can be achieved by using the ILE product term (asynchronous mode) for clocking control. Flow through input operation can be achieved by connecting the Flow Through Select Mux to Vcc (see Figure 3).

T-46-13-47

TABLE 1 EP512 INPUT FUNCTIONS

| IMBLE I EFSIZ I | MPOI FC |   |    |

|-----------------|---------|---|----|

| input Type      | ILE     | D | Q  |

| Latch           | Н       | Н | Н  |

| Latch           | Н       | L | L  |

| Latch           | L       | X | Qn |

| Register        | Į.      | Н | н  |

| Register        |         | L | L  |

| Flow-Through    | Х       | Н | Н  |

| Flow-Through    | X       | L | L  |

24E D

(Violetially)

53

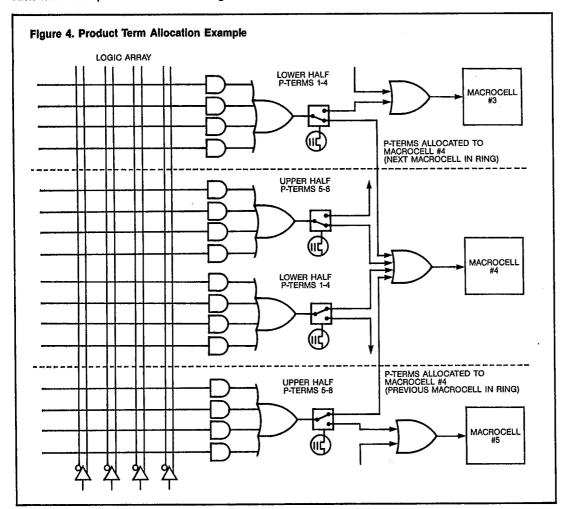

## PRODUCT TERM ALLOCATION

The EP512 supports Product Term Aliocation, allowing unused product terms from one macrocell to be placed into another macrocell. In the EP512, this allocation is done between adjacent macrocells in groups of 4 product terms. Thus, each macrocell has two adjacent macrocells to share product terms. The EP512 macrocells are grouped into two "rings" (Ring 1 and Ring 2) with 6 macrocells per ring. Table 2 shows the structure of the two rings and defines each macrocell's adjacent partners. By using Product Term Allocation, each macrocell can implement logic requiring up to 16 product terms.

For example, if Macrocell 4 requires 16 product terms, Altera's A+PLUS Design Software will allocate four product terms from Macrocell 3 and four product terms from Macrocell 5 to give Macrocell 4 a total of 16 product terms. Macrocells 3 and 5 each have four product terms remaining which

may be kept or used by other macrocells. This example is illustrated in Figure 4. Even if a macrocell has allocated all of its product terms to adjacent macrocells, its register and associated control functions are still usable. In this case the input to the I/O register is tied to GND (VCC if the invert select EPROM bit is programmed). For example, the register preset and clear may used to implement an asynchronous S-R latch.

## I/O ARCHITECTURE

T-46-13-41

The EP512 Input/Output Architecture provides each macrocell with over 50 possible I/O configurations. Each I/O can be individually configured for combinatorial or registered output, with programmable output polarity. Four different types of registers (D, T, JK, SR), can be implemented into every I/O without any additional logic requirements. Each macrocell contains two dedicated product terms (see Figure 2) for every control

| TABLE 2 | PRODUCT | TERM | <b>ALLOCATION</b> |

|---------|---------|------|-------------------|

|         |         |      |                   |

|         | Ring 1 |          | Ring 2  |        |          |  |  |  |

|---------|--------|----------|---------|--------|----------|--|--|--|

| Current | Next   | Previous | Current |        | Previous |  |  |  |

| Macro-  | Macro- | Macro-   | Macro-  |        | Macro-   |  |  |  |

| cell    | cell   | cell     | cell    |        | celi     |  |  |  |

| 1 2     | 2      | 6<br>1   | 7       | 8<br>9 | 12<br>7  |  |  |  |

| 3 4     | 4      | 2        | 9       | 10     | 8        |  |  |  |

|         | 5      | 3        | 10      | 11     | 9        |  |  |  |

| 5       | 6      | 4        | 11      | 12     | 10       |  |  |  |

| 6       | 1      | 5        | 12      | 7      | 11       |  |  |  |

function (Asynchronous Preset, Asynchronous Clear, Asynchronous Clock, and Output Enable).

Each macrocell register may be individually configured to function in either a synchronous or asynchronous clock mode. Synchronous clocking is provided by the dedicated clock pin (pin 1) while asynchronous clocking is provided by the two dedicated asynchronous clock product terms (see Figure 1).

Product Term Allocation is controlled by Altera's A+PLUS Design Software and implemented using the Product Term Allocation Control Muxes shown in Figure 2. The product terms are ORed together to generate the logic signal for the Macrocell Combinatorial output or Macrocell Register input. This scheme allows a more efficient utilization of product terms and greater flexibility in design architecture.

Output polarity is controlled by the Invert Select EPROM bit. This feature allows active high or active low output and also permits DeMorgan's inversion for improved minimization of logic.

#### OUTPUT/FEEDBACK

Every macrocell in the EP512 has Dual Feedback. This architectural feature enables the designer to use the macrocell for buried logic and also use the macrocell's I/O pin as a dedicated input, increasing design flexibility. Dual Feedback is implemented in the EP512 by providing a feedback path from both the input pin and the macrocell register (see Figure 2). These paths are separated by the tri-state buffer controlled by the Output Enable control signal. When the tri-state buffer is disabled (Output Enable grounded), the register uses the internal feedback path, while allowing the second feedback path to function as a dedicated input path. This second feedback path allows the I/O pin to connect directly into the logic array.

In the erased state, the I/O is configured for combinatorial active low output with input (pin) feedback.

#### **FUNCTIONAL TESTING**

The EP512 is fully functionally tested and quaranteed through complete testing of each programmable EPROM bit and all internal logic elements thus ensuring 100% programming yield. As a result, traditional problems associated with fuseprogrammed circuits are eliminated. The erasable nature of the EP512 allows test program patterns to be used and then erased. This facility to use application-independent, general purpose tests is called generic testing and is unique for EPLDs among user-defined LSI logic devices.

T-46-13-47

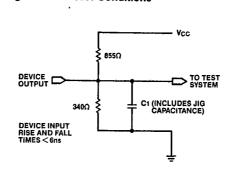

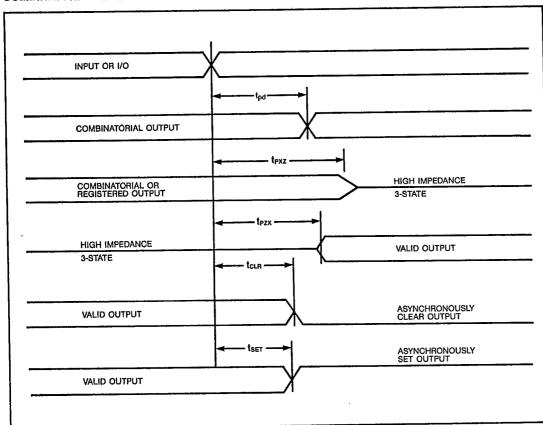

Figure 5. AC Test Conditions

Power supply transients can affect AC measurements, simultaneous transitions of multiple outputs should be avoided for accurate measurement. Do not attempt to perform threshold tests under AC conditions. Large amplitude, fast ground current transients normally occur as the device outputs discharge the load capacitances. These transients flowing through the parasitic inductance between the device ground pin and the test system ground can create significant reductions in observable input noise immunity.

## DESIGN SECURITY

The EP512 contains a programmable design security feature that controls the access to the data programmed into the device. If this programmable feature is used, a proprietary design implemented in the device cannot be copied nor retrieved. This enables a high level of design protection, since programmed data within EPROM cells is invisible. The bit that controls this function, along with all other program data, may be reset simply by erasing the device.

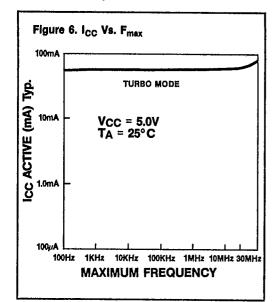

## **TURBO-BIT**

The EP512 contains a programmable option to control the automatic power down feature that enables the low standby power mode of the device. This option is controlled by a TURBO-BIT which can be set using A+PLUS, When the TURBO-BIT is programmed (Turbo = ON), the low standby power mode (Icc1) is disabled. This renders the circuit less sensitive to Vcc noise transients which can be created by the power-up/power-down cycle when operating in the low power mode. The typical icc vs frequency data for both Turbo and Non-Turbo (low power) mode is shown in each EPLD data sheet. All AC values are tested with the TURBO-BIT programmed. If the design requires low power operation then the TURBO-BIT should be disabled (Turbo = OFF). When operating in this mode, some AC parameters are subject to increase. Values given in the AC specifications section under "Non-Turbo Adder" must be added to the respective AC parameter to determine worst-case timing.

## **ABSOLUTE MAXIMUM RATINGS**

COMMERCIAL **OPERATING RANGE**

Note: See Design Recommendations

T-46-13-47

| SYMBOL | PARAMETER                  | CONDITIONS                   | MIN  | MAX  | UNIT                                             |

|--------|----------------------------|------------------------------|------|------|--------------------------------------------------|

| Vcc    | Supply voltage             | 14814                        | -2.0 | 7.0  | V                                                |

| Vpp    | Programming supply voltage | With respect to GND note (3) | -2,0 | 13.5 | 1 ·                                              |

| Vı     | DC INPUT voltage           |                              | -2.0 | 7.0  | <del>                                     </del> |

| MAX    | DC Vcc or GND current      |                              | -150 | 150  | mA                                               |

| lour   | DC OUTPUT current, per pin |                              | -25  | 25   | mA                                               |

| Po     | Power dissipation          |                              |      | 750  | mW                                               |

| Tstg   | Storage temperature        | No bias                      | -65  | +150 | °C                                               |

| TAMB   | Ambient temperature        | Under bias                   | -65  | +135 | •c                                               |

## RECOMMENDED OPERATING CONDITIONS

| SYMBOL         | PARAMETER             | CONDITIONS     | MIN  | MAX             | UNIT                                             |

|----------------|-----------------------|----------------|------|-----------------|--------------------------------------------------|

| Vcc            | Supply Voltage        |                | 4.75 | 5,25            | VIII                                             |

| Vi             | INPUT voltage         | `              | 1.70 |                 | V V                                              |

| V <sub>0</sub> | OUTPUT voltage        |                |      | V <sub>CC</sub> | <del>                                     </del> |

| TA             | Operating temperature | For Commercial | 0    | 70              | °C V                                             |

| T <sub>R</sub> | INPUT rise time       | note (8)       |      | 100             | <u> </u>                                         |

| Τ̈́F           | INPUT fall time       | note (8)       |      | 100             | ns<br>ns                                         |

## DC OPERATING CHARACTERISTICS

( $V_{CC}$  = 5V ±5%,  $T_A$  = 0°C for Commercial) Note (1)

| SYMBOL          | PARAMETER                        | CONDITIONS                                                                   | MIN  | TYP          | MAX          | UNIT             |

|-----------------|----------------------------------|------------------------------------------------------------------------------|------|--------------|--------------|------------------|

| ViH             | HIGH level input voltage         |                                                                              | 2.0  |              | Vcc + 0.3    | V                |

| V <sub>IL</sub> | LOW level input voltage          |                                                                              | -0.3 | <del> </del> | 0.8          | v                |

| VoH             | HIGH level TTL output voltage    | I <sub>OH</sub> = -4mA DC                                                    | 2.4  |              | 1- 4.0       |                  |

| V <sub>OH</sub> | HIGH level CMOS output voltage   | IOH = -2mA DC                                                                | 3.84 | <del> </del> | <del> </del> | v                |

| Vol             | LOW level TTL output voltage     | IOL = 4mA DC                                                                 |      |              | 0.45         |                  |

| lı .            | Input leakage current            | VI = Vcc or GND                                                              | -10  |              | +10          |                  |

| loz             | 3-state output off-state current | Vo = Vcc or GND                                                              | -10  |              | +10          | <u>μ</u> Α<br>μΑ |

| lcc1            | Vcc supply current (standby)     | V <sub>1</sub> = V <sub>CC</sub> or GND<br>No load<br>note (7)               |      |              | 150          | <u>μ</u> Α       |

| lcc2            | Vcc supply current (non-turbo)   | V <sub>1</sub> = V <sub>CC</sub> or GND<br>No load, f = 1.0 MHz<br>note (6)  |      |              | 50           | mA               |

| lcc3            | Vcc supply current (turbo)       | V <sub>1</sub> = V <sub>CC</sub> or GND<br>No load, f = 1.k0 MHz<br>note (6) |      |              | 100          | mA               |

# CAPACITANCE Note (4)

| SYMBOL           | PARAMETER             | CONDITIONS                           | MIN | MAX | UNIT |

|------------------|-----------------------|--------------------------------------|-----|-----|------|

| CiN              | Input Capacitance     | V <sub>IN</sub> = 0V<br>f = 1.0 MHz  |     | 20  | pF   |

| COUT             | Output Capacitance    | V <sub>OUT</sub> = 0V<br>f = 1.0 MHz |     | 20  | pF   |

| C <sub>CLK</sub> | Clock Pin Capacitance | V <sub>IN</sub> = 0V<br>f = 1.0 MHz  |     | 20  | pF   |

## AC CHARACTERISTICS

EP512-25, EP512-30, EP512-35

T-46-13-47

( $V_{CC}$  = 5V ±5%,  $T_A$  = 0°C to 70°C for Commercial)

|        |                                      |                                  | EP512-25 |     | EP512-30 |     | EP612-35 |     | NON-TURBO<br>Adder | j     |  |

|--------|--------------------------------------|----------------------------------|----------|-----|----------|-----|----------|-----|--------------------|-------|--|

| 8YMB0L | PARAMETER                            | CONDITIONS                       | MIN      | MAX | MIN      | MAX | MIN      | MAX | note (5)           | UNITS |  |

| tpD1   | Input to non-registered output       |                                  |          | 25  |          | 30  |          | 35  | 10                 | ns    |  |

| tPD2   | I/O input to non-registered output   | C <sub>1</sub> = 50pF            |          | 25  |          | 30  |          | 35  | 10                 | ns    |  |

| tpzx   | Input or I/O input to output enable  |                                  |          | 25  | Γ        | 30  |          | 35  | 10                 | ns    |  |

| texz   | Input or I/O input to output disable | C <sub>1</sub> = 5pF<br>note (2) |          | 25  |          | 30  |          | 35  | 10                 | ns    |  |

| tclr   | Asynchronous output clear time       | C <sub>1</sub> = 50pF            |          | 25  | Ī        | 30  |          | 35  | 10                 | ns    |  |

| tset   | Asynchronous output preset time      |                                  |          | 25  |          | 30  |          | 35  | 10                 | ns    |  |

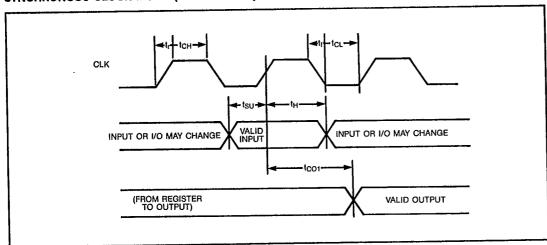

## SYNCHRONOUS CLOCK MODE

|        | PARAMETER                                                                       | CONDITIONS | EP512-25 |     | EP512-30 |     | EP512-35 |     | NON-TURBO<br>Adder | ]     |  |

|--------|---------------------------------------------------------------------------------|------------|----------|-----|----------|-----|----------|-----|--------------------|-------|--|

| SYMBOL |                                                                                 |            | MIN      | MAX | MIN      | MAX | MIN      | MAX | note (5)           | UNITS |  |

| 1MAX   | Maximum frequency                                                               | note (9)   | 50       |     | 40       |     | 40       |     | 0                  | MHz   |  |

| tsu    | Input or 1/O input setup time                                                   |            | 20       |     | 25       |     | 25       | l   | 10                 | ns    |  |

| tH     | Input or I/O Input hold time                                                    |            | 0        |     | 0        |     | 0        |     | 0                  | ns    |  |

| tcH    | Clock high time                                                                 |            | 10       | l   | 12.5     |     | 12.5     |     | 10                 | ns    |  |

| tCL    | Clock low time                                                                  |            | 10       | I   | 12.5     |     | 12.5     |     | 10                 | ns    |  |

| tco1   | Clock to output delay                                                           |            |          | 15  |          | 20  |          | 20  | 10                 | ns    |  |

| tent   | Minimum clock period (register output feedback to register input—internal path) |            |          | 30  | _        | 35  |          | 40  | 10                 | ns    |  |

| font   | Internal maximum frequency<br>(1/t <sub>CNT</sub> )                             | note (6)   | 33       |     | 30       |     | 25       |     | 0                  | MHz   |  |

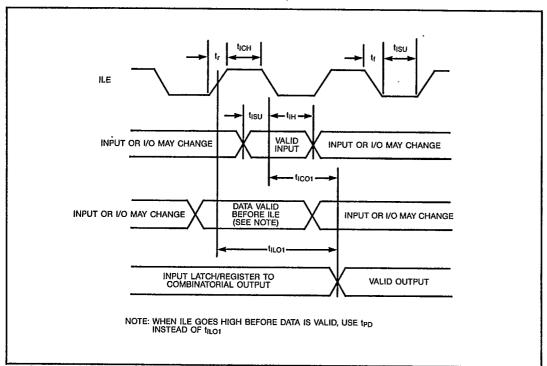

## SYNCHRONOUS CLOCK MODE—INPUT STRUCTURE

|                 |                                                  | CONDITIONS | EP512-25 |     | EP512-30 |     | EP512-35 |     | NON-TURBO<br>Adder |       |

|-----------------|--------------------------------------------------|------------|----------|-----|----------|-----|----------|-----|--------------------|-------|

| SYMBOL          | PARAMETER                                        |            | MIN      | MAX | MIN      | MAX | MIN      | MAX | note (5)           | UNITS |

| fimax           | Maximum Input frequency<br>(I/t <sub>ICP</sub> ) |            | 40       |     | 33       |     | 28.5     |     | 0                  | MHz   |

| fisu            | Input register setup time                        |            | 5        |     | 5        |     | 5        |     | 0                  | пѕ    |

| t <sub>IH</sub> | Input hold time                                  |            | 5        |     | 5        |     | 5        |     | 0                  | ns    |

| tich            | Input clock high time                            |            | 10       |     | 12.5     |     | 12.5     |     | 10                 | ns    |

| ticL            | Input clock low time                             |            | 10       |     | 12.5     |     | 12.5     |     | 10                 | ns    |

| ticos           | Input clock to output                            |            | 1        | 30  |          | 35  |          | 40  | 10                 | กร    |

| tice            | Input clock period<br>minimum                    |            |          | 25  |          | 30  |          | 35  | 10                 | ns    |

| \$(LO1          | Input latch to output                            | note (6)   | Ī        | 35  |          | 40  |          | 40  | 10                 | ns    |

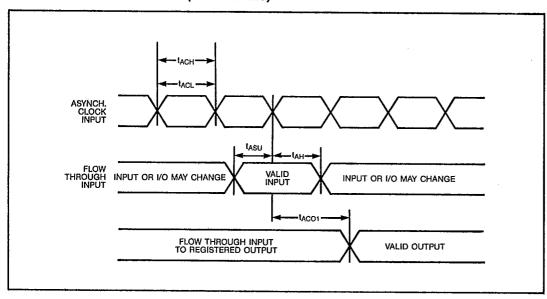

## **ASYNCHRONOUS CLOCK MODE**

EP512-25, EP512-30, EP512-35

T-46-13-47

|                 | 4                                                                               |            | EP512-25 |     | EP512-30 |     | EP512-35     |     | NON-TURBO<br>Adder |       |  |

|-----------------|---------------------------------------------------------------------------------|------------|----------|-----|----------|-----|--------------|-----|--------------------|-------|--|

| SYMBOL          | PARAMETER                                                                       | CONDITIONS | MIN      | MAX | MIN      | MAX | MIN          | MAX | note (5)           | UNITS |  |

| famax           | Maximum frequency<br>1/(tacl + tach)                                            | note (9)   | 20       |     | 16.5     |     | 16.5         |     | 0                  | MHz   |  |

| †ASU            | Input or I/O input setup time                                                   |            | 7        |     | 10       |     | 10           |     | 10                 | ns    |  |

| t <sub>AH</sub> | Input or 1/0 input hold time                                                    | T .        | 23       |     | 27       |     | 30           |     | 10                 | ns    |  |

| tach            | Clock high time                                                                 |            | 25       |     | 30       | 1   | 30           |     | 10                 | ns    |  |

| †ACL.           | Clock low time                                                                  |            | 25       |     | 30       |     | 30           |     | 10                 | ns    |  |

| fACO1           | Clock to output delay                                                           |            | <u> </u> | 35  |          | 45  | <del> </del> | 50  | 10                 | ns    |  |

| tacht           | Minimum clock period (register output feedback to register input—internal path) |            |          | 55  |          | 65  |              | 70  | 10                 | ns    |  |

| facnt .         | Internal maximum frequency<br>(1/tacnt)                                         |            | 18       |     | 15       |     | 14.2         |     | 0                  | MHz   |  |

## ASYNCHRONOUS CLOCK MODE—INPUT STRUCTURE

|        | PARAMETER                    |            | EP512-25 |     | EP512-30 |      | EP512-35 |      | NON-TURBO<br>Adder |       |  |

|--------|------------------------------|------------|----------|-----|----------|------|----------|------|--------------------|-------|--|

| SYMBOL |                              | CONDITIONS | MIN      | MAX | MIN      | MAX  | MIN      | MAX  | note (5)           | UNITS |  |

| TAIMAX | Max. freq. Input reg.        |            |          | 20  |          | 16.5 | <u> </u> | 16.5 | 0                  | MHz   |  |

| †AISU  | Input setup to asynch clk.   |            | 0        |     | 0        | i    | 0        |      | 10                 | ns    |  |

| tajh   | Input hold after asynch clk. |            | 23       |     | 26       |      | 30       |      | 10                 | ns    |  |

| tAICH  | Asynch input high time       |            | 25       |     | 30       |      | 30       |      | 10                 | ns    |  |

| †AICL  | Asynch input low time        |            | 25       |     | 30       |      | 30       |      | 10                 | ns    |  |

| tAICO1 | Asynch input clk, to output  |            |          | 48  |          | 55   |          | 60   | 10                 | ns    |  |

| tAIL01 | Asynch input latch to output |            | 1        | 53  |          | 60   |          | 65   | 10                 | пѕ    |  |

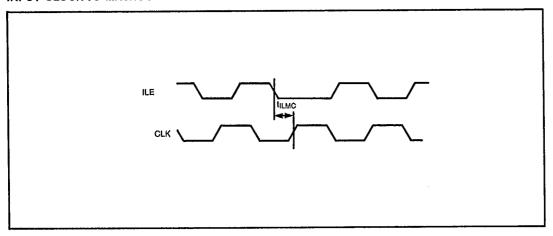

## INPUT-CLOCK-TO-MACROCELL-CLOCK A.C. CHARACTERISTICS

|               |                                                | EP512-25 |     | EP512-30 |     | EP512-35 |     | NON-TURBO<br>Adder |       |

|---------------|------------------------------------------------|----------|-----|----------|-----|----------|-----|--------------------|-------|

| SYMBOL        | PARAMETER                                      | MIN      | MAX | MIN      | MAX | MIN      | MAX | note (5)           | UNITS |

| <b>TILM</b> C | Synchronous ILE<br>Synchronous Macrocell CLK   | 25       |     | 30       |     | 35       |     | 10                 | ns    |

|               | Synchronous ILE<br>Asynchronous Macrocell CLK  | 5        |     | 8        |     | 10       |     | 10                 | ns    |

|               | Asynchronous ILE<br>Synchronous Macrocell CLK  | 48       |     | 55       |     | 65       |     | 10                 | ns    |

|               | Asynchronous ILE<br>Asynchronous Macrocell CLK | 20       |     | 35       | _   | 50       |     | 10                 | ПŚ    |

Typical values are for TA = 25°C, V<sub>CC</sub> = 5V

Sample tested only for an output change of 500mV.

Minimum DC input is -0.3V. During transitions, the inputs may undershoot to -2.0V for periods less than 20ns.

Capacitance measured at 25°C. Sample tested only. Clock pin capacitance for dedicated clock inputs only. Pin 1 (high voltage pin during programming), has capacitance of 50pF max.

See TURBO-BIT", page 56.

Measured with device programmed as a 12 bit counter.

EPLD automatically goes into standby mode if logic transitions do not occur when in non-turbo mode (approximately 100ns after last transition). This feature may not be available on initial production units. Check factory for status.

Clock ta, tr = 100ns.

The fixax values shown represent the highest frequency for pipelined data.

Mote: The recommended erase procedure for this device is to expose it to a standard UV lamp for a minimum of one hour.

| GRADE                       | AVAILABILITY |                      |  |  |  |

|-----------------------------|--------------|----------------------|--|--|--|

| Commercial<br>(0°C to 70°C) | EP512-25     | EP512-30<br>EP512-35 |  |  |  |

ANDIERA

£.\$

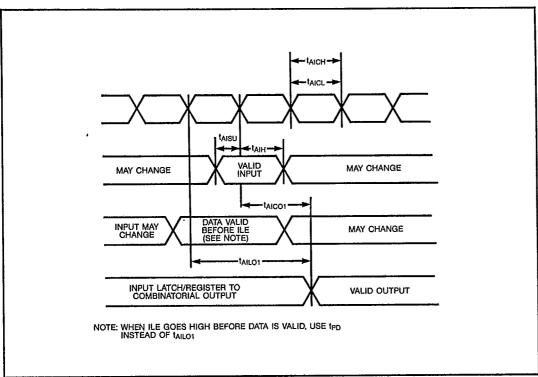

## Figure 8. Switching Waveforms

#### **COMBINATORIAL MODE**

## SYNCHRONOUS CLOCK MODE (MACROCELLS)

T-46-13-47

**Switching Waveforms (Continued)**

## SYNCHRONOUS CLOCK MODE (INPUT STRUCTURE)

## ASYNCHRONOUS CLOCK MODE (MACROCELLS)

61

9

**EP512**

**Switching Waveforms (Continued)**

## ASYNCHRONOUS CLOCK MODE (INPUT STRUCTURE)

#### INPUT CLOCK-TO-MACROCELL CLOCK TIMING

NOTES: 1, AND 1; < 6ns fc, and toH MEASURED AT 0.3V AND 2.7V ALL OTHER TIMING AT 1.5V INPUT VOLTAGE LEVELS AT 0V AND 3V