# microelectronics group

# ATT1MX10 (SPINNAKER) Quad MAC and Transceivers

#### **Features**

- Four 10 Mbits/s Ethernet transceivers and MACs integrated together with separate transmit and receive port FIFOs and a single DMA interface simplify the design of a frame-switching hub. Each port can be configured separately for MAC, AUI, or twisted pair.

- Provides extensive network management capabilities that network administrators demand in today's hub equipment.

- There are nine per-port transmit event counters and 18 per-port receive event counters for hardware-based network management.

- Event counters can be read through a highspeed CPU interface that is separate from the DMA (Frame Data) interface.

- The 16-bit asynchronous CPU interface can be accessed while frames are being read or written

- Receive frame statistics are appended to each frame at the end of the DMA transfer for custom management implementations and routing and switching information.

- Per-port interrupt signals alert the CPU of transmit, receive, or bus errors. Per-port interrupt status registers distinguish the errors as any of the following: packet not transmitted due to late collision, excessive collisions, excessive deferral, or Tx FIFO underrun; packet not received because of receive jabber or FIFO overrun; TP transceiver has detected reversed polarity and corrected itself; link pulses are no longer being received; parity error while writing to Tx FIFO.

- The ATT1MX10 complies with ISO 8802.3 by default, but also can be configured for higher frame switching performance.

- Short preamble generation.

- Immediate retransmission after collision.

- Selectable number of collision retries.

- Separate 128-byte transmit and receive FIFOs are provided per-port.

- Tx and Rx FIFOs can hold multiple frames.

- Deep FIFOs minimize overflows and underruns.

- Frames are retransmitted automatically after a collision if the collision occurs within the first 64 octets of a packet.

- Individual Rx thresholds for start of frame and midframe bursts allows DA (destination address) and SA (source address) to be read fast.

- Undersized and fragment frames along with short events and noise hits can be rejected before any bus activity.

- Direct system interface to FIFOs allows 32-bit single-cycle DMA operations at 16 MHz to 25 MHz.

- The ATT1MX10 can be configured for full-duplex transmission and reception.

- The event counters gather statistics separately for the receive and transmit ports.

- Independent transmit and receive data paths, including FIFOs, allow simultaneous transmit and receive operations on the same port.

- The CRC generator can be enabled or disabled on a per-packet basis through hardware and software control.

- Transmit and receive operations are under hardware control so that CPU accesses are not needed to transmit or receive a frame.

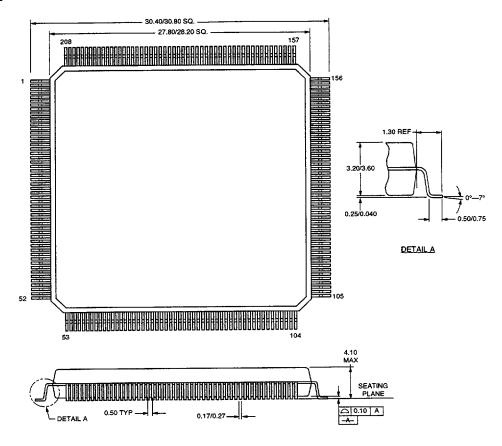

- 208-pin SQFPH.

Note: Advisories are issued as needed to update product information. When using this data sheet for design purposes, please contact your Lucent Technologies Microelectronics Group Account Manager to obtain the latest advisory on this product.

**■ 0050026 0027371 015 ■**

# **Table of Contents**

| Contents                                  | Page     | Tables                                           | Page |

|-------------------------------------------|----------|--------------------------------------------------|------|

| Features                                  | 1        | Table 1. ATT1MX10 Signal According to Its        |      |

| Descriptions and Applications             |          | Pin Number in Numeric Sequence                   | 6    |

| Pin Information                           |          | Table 2. ATT1MX10 Signal According to Its        |      |

| Pin Descriptions                          |          | Name in Alphabetic Sequence                      | 7    |

| Functional Description                    |          | Table 3. Ethernet Media Interface Signals        | 8    |

| Register and Counter Overview             |          | Table 4. DMA Interface Signals                   | 10   |

| Receive Overview                          |          | Table 5. Transmit Control Signals                | 12   |

| Transmit Overview                         | 16       | Table 6. Receive Control Signals                 | 12   |

| Register and Counter Maps                 | 17       | Table 7. CPU Interface Signals                   |      |

| Global Configuration Register             | 20       | Table 8. Miscellaneous Signals                   |      |

| Revision ID Register                      |          | Table 9. Port Addressing Format                  |      |

| Transmit Frame Configuration Register     |          | Table 10. Register and Counter Address Maps      | 17   |

| Receive Frame Configuration Register      | 24       | Table 11. 32-Bit Counter, 16-Bit CPU Data Bus    | 19   |

| Global FIFO Configuration Register        |          | Table 12. Global Configuration Register Bit Ma   | p 20 |

| Port Interrupt Identification Register    |          | Table 13. Global Configuration Register Bit      |      |

| Transmit Port Diagnostic Register         |          | Descriptions                                     | 20   |

| Receive Port Diagnostic Register          |          | Table 14. Revision ID Register Bit Map           | 21   |

| Frame Interrupt Mask Register             |          | Table 15. Revision ID Register Bit Descriptions  | 21   |

| Frame Interrupt Register                  |          | Table 16. Transmit Frame Configuration Regist    | er   |

| Counter Overflow Indication Register      |          | Bit Map                                          | 22   |

| CPU Interrupt Mask Register               | 36       | Table 17. Transmit Frame Configuration Regist    |      |

| DMA Interface                             |          | Bit Descriptions                                 | 22   |

| FIFO Operation                            | 40       | Table 18. Receive Frame Configuration Registe    | er   |

| ISO 8802.3 MAC Functionality              |          | Bit Map                                          | 24   |

| ISO 8802.3 Attachment Unit Interface (AUI |          | Table 19. Receive Frame Configuration Register   |      |

| ISO 8802.3 Twisted-Pair (TP) Transceiver  | 46       | Bit Descriptions                                 | 24   |

| Summary of ATT1MX10 Registers and Co      | unters48 | Table 20. Global FIFO Configuration Register     |      |

| ATT1MX10 Registers                        | 49       | Bit Map                                          | 26   |

| ATT1MX10 Counters                         | 49       | Table 21. Global FIFO Configuration Register     |      |

| Counter Definitions                       | 50       | Bit Descriptions                                 | 26   |

| CPU Interface                             |          | Table 22. Port Interrupt Identification Register |      |

| Application Information                   | 54       | Bit Map                                          | 27   |

| RMON Cross Reference                      |          | Table 23. Port Interrupt Identification Register |      |

| Absolute Maximum Ratings                  | 55       | Bit Descriptions                                 | 27   |

| Handling Precautions                      | 56       | Table 24. Transmit Port Diagnostic Register      |      |

| Electrical Characteristics                | 56       | Bit Map                                          | 28   |

| Timing Characteristics                    |          | Table 25. Transmit Port Diagnostic Register      |      |

| Outline Diagram                           | 77       | Bit Descriptions                                 | 28   |

| 208-Pin SQFPH, 1.3 mm Lead Frame          | 77       | Table 26. Receive Port Diagnostic Register       |      |

| Ordering Information                      | 77       | Bit Map                                          | 30   |

|                                           |          |                                                  |      |

#### **Table of Contents**

| Tables                                           | Page | Figures                                       | Page |

|--------------------------------------------------|------|-----------------------------------------------|------|

| Table 27. Receive Port Diagnostic Register       |      | Figure 1. ATT1MX10 Block Diagram              | 4    |

| Bit Descriptions                                 | 30   | Figure 2. Single-Port Block Diagram           | 4    |

| Table 28. Frame Interrupt Mask Register Bit Ma   |      | Figure 3. ATT1MX10 Pinout Diagram             | 5    |

| Table 29. Frame Interrupt Mask Register Bit      |      | Figure 4. AUI Driver Conditions               | 45   |

| Descriptions                                     | 32   | Figure 5. Capacitive Coupling                 | 45   |

| Table 30. Frame Interrupt Register Bit Map       |      | Figure 6. The AUI Receivers Internal Bias     |      |

| Table 31. Frame Interrupt Mask Register Bit      |      | Network                                       | 46   |

| Descriptions                                     | 33   | Figure 7. Pre-equalization Control Format     | 46   |

| Table 32. Counter Overflow Indication Register   |      | Figure 8. Recommended TP Port Configuration   |      |

| Bit Map—High Word                                |      | Figure 9. Rx FIFO Read, 4-Word, Single-Cycle  |      |

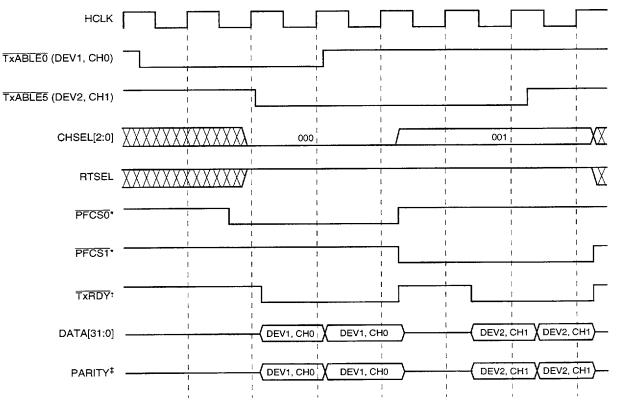

| Table 33. Counter Overflow Indication Register   |      | Access                                        |      |

| Bit Map—Low Word                                 |      | Figure 10. DMA Bus 3-State Timing             | 59   |

| Table 34. Counter Overflow Indication Register   |      | Figure 11. Receive Statistics (32-Bit Bus)    |      |

| Bit Descriptions                                 |      | Figure 12. Rx FIFO Read, 2-Word, Multiple Cy  |      |

| Table 35. CPU Interrupt Mask Register            |      | Access                                        |      |

| Bit Map—High Word                                | 36   | Figure 13. Rx FIFO Read, 2-Word, Multiple FI  |      |

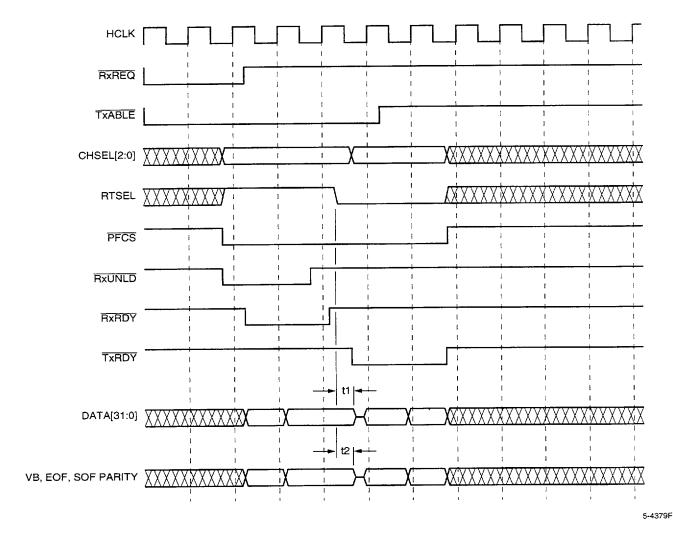

| Table 36. CPU Interrupt Mask Register            |      | Accesses                                      | 62   |

| Bit Map—Low Word                                 | 36   | Figure 14. Rx FIFO Read, 2-Word, Multiple Cl  |      |

| Table 37. CPU Interrupt Mask Register Bit        |      | Accesses                                      |      |

| Descriptions                                     | 37   | Figure 15. Byte Ordering on DATA Bus During   |      |

| Table 38. Valid Byte (VB) Alignment              |      | and Tx FIFO Transfers                         |      |

| Table 39. Word Count Threshold (WCTH)            |      | Figure 16. Byte Order on DATA Bus During      |      |

| Settings                                         | 40   | Rx Status, 32-Bit Bus                         | 64   |

| Table 40. RMON Cross Reference Objects           |      | Figure 17. Tx FIFO Write, 4-Word, Single-Cyc  | le   |

| Table 41. Rx FIFO Read, 4-Word, Single-Cycle     |      | Access                                        | 65   |

| Access                                           |      | Figure 18. Tx FIFO Write, 2-Word, Multiple Cy | /cle |

| Table 42. DATA Bus 3-State Timing                | 59   | Access                                        | 66   |

| Table 43. Receive Statistics (32-bit Bus) Timing |      | Figure 19. Tx FIFO Write, 2-Word, Single-Cyc  | le   |

| Table 44. Tx FIFO Write, 4-Word, Single-Cycle    |      | Access, Last Word Written                     | 67   |

|                                                  | 64   | Figure 20. Tx FIFO Write, 2-Word, Multiple FI | FO   |

| Table 45. Tx FIFO Write, 2-Word, Single Cycle    |      | Accesses                                      | 68   |

| Access, Last Word Written                        |      | Figure 21. Tx FIFO Write, 2-Word, Multiple Ch |      |

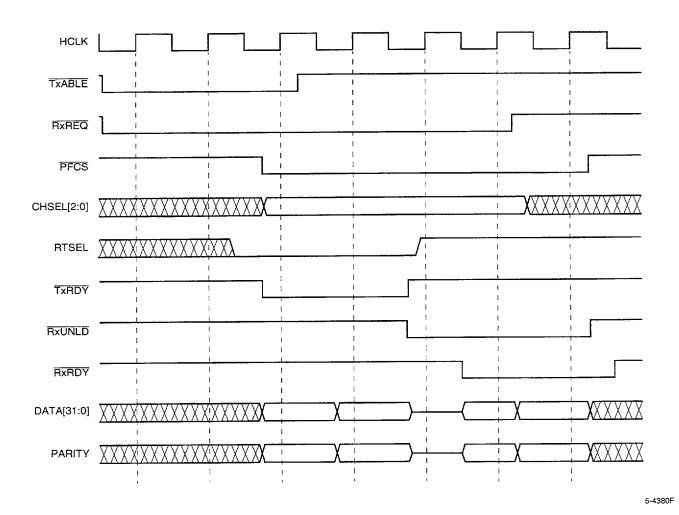

| Table 46. Rx FIFO Read to Tx FIFO Write Bus      |      | Accesses                                      | 69   |

| Turnaround Timing                                | 70   | Figure 22. Rx Read Followed by Tx Write Bus   |      |

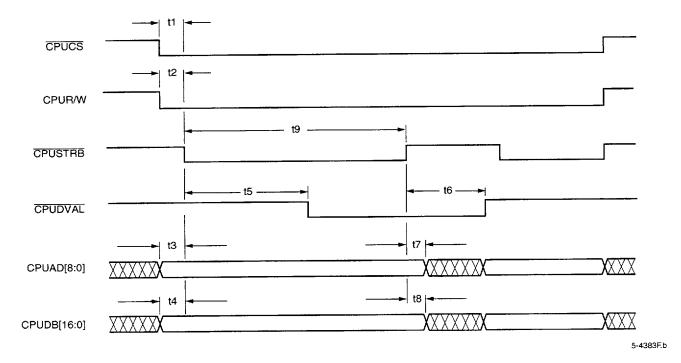

| Table 47. 16-Bit, Asynchronous CPU Write         |      | Turnaround Timing                             | 70   |

| Timing                                           | 72   | Figure 23. Tx FIFO Write to Rx FIFO Read      |      |

| Table 48. 16-Bit, Asynchronous CPU Read          |      | Timing                                        | 71   |

| Timing                                           | 73   | Figure 24. 16-Bit, Asynchronous CPU Write     |      |

| Table 49. MAC Transmit Timing                    |      | Timing                                        | 72   |

| Table 50. MAC Receive Timing                     | 74   | Figure 25. 16-Bit, Asynchronous CPU Read      |      |

| Table 51. MAC Receive Clock Timing               |      | Timing                                        |      |

| Table 52. TP Driver Specification Timing         |      | Figure 26. MAC Transmit Timing                |      |

| Table 53. TP Link-Integrity Timing               | 76   | Figure 27. MAC Receive Timing                 | 74   |

|                                                  |      | Figure 28. MAC Receive Clock Timing           | 75   |

|                                                  |      | Figure 29. TP Driver Specification Timing     |      |

|                                                  |      | Figure 30 Link-Integrity Timing               | 76   |

### **Description and Applications**

The ATT1MX10 provides four ISO 8802.3 10 Mbits/s standard MACs and TP/AUI transceivers in a single 208-pin SQFPH package. With deep internal FIFOs and a high-speed system interface, the ATT1MX10 is intended for Ethernet frame switching and multiple-port bridging and routing applications.

The ATT1MX10 allows single-cycle DMA transfers directly to and from its internal transmit and receive FIFOs. The deep FIFOs enable storing multiple frames on-chip, retransmitting a frame after a collision, and rejecting undersized frames before any DMA activity.

The ATT1MX10 also provides extensive on-chip counters and registers for out-of-band network management.

Typical applications of the ATT1MX10 include:

- Frame switched Ethernet hubs supporting store and forward, crosspoint switch, cut through, and other system architectures.

- Ethernet bridges and routers.

- Multiple-port server cards.

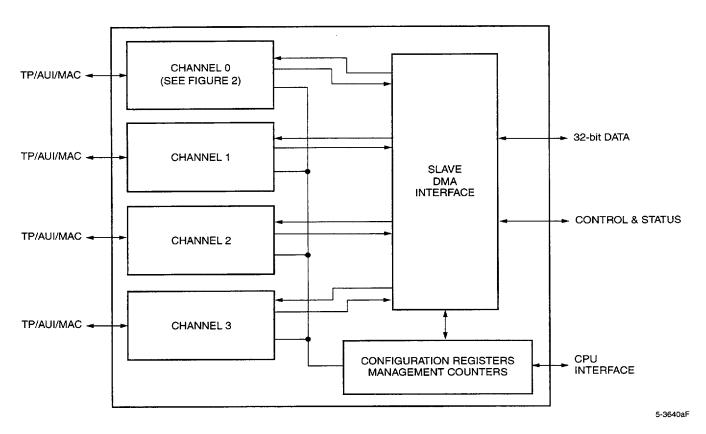

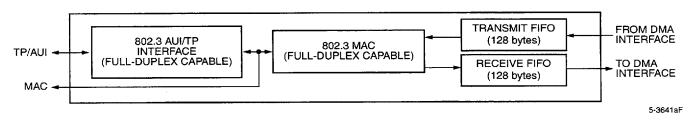

Figure 1 shows a block diagram of the ATT1MX10. An individual port block diagram is shown in Figure 2.

Figure 1. ATT1MX10 Block Diagram

Figure 2. Single-Port Block Diagram

Lucent Technologies Inc.

4

■ 0050026 0027374 824 **■**

#### Pin Information

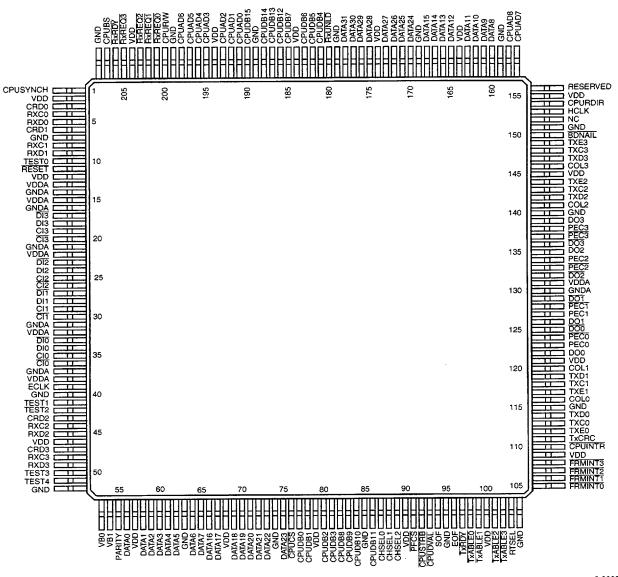

Figure 3. ATT1MX10 Pinout Diagram

5-3668(F).dR2

Table 1. ATT1MX10 Signal According to Its Pin Number in Numeric Sequence

| Pin | Name  | Pin | Name   | Pin | Name    | Pin | Name    | Pin | Name    | Pin | Name    |

|-----|-------|-----|--------|-----|---------|-----|---------|-----|---------|-----|---------|

| 1   | NC3   | 36  | CIO    | 71  | DATA20  | 106 | FRMINT1 | 141 | COL2    | 176 | DATA29  |

| 2   | VDD   | 37  | GNDA   | 72  | DATA21  | 107 | FRMINT2 | 142 | TXD2    | 177 | DATA30  |

| 3   | CRD0  | 38  | VDDA   | 73  | DATA22  | 108 | FRMINT3 | 143 | TXC2    | 178 | DATA31  |

| 4   | RXC0  | 39  | ECLK   | 74  | GND     | 109 | VDD     | 144 | TXE2    | 179 | GND     |

| 5   | RXD0  | 40  | GND    | 75  | DATA23  | 110 | CPUINTR | 145 | Vaa     | 180 | RXUNLD  |

| 6   | CRD1  | 41  | TEST1  | 76  | CPUCS   | 111 | TxCRC   | 146 | COL3    | 181 | CPUDB4  |

| 7   | GND   | 42  | TEST2  | 77  | CPUDB0  | 112 | TXE0    | 147 | TXD3    | 182 | CPUDB5  |

| 8   | RXC1  | 43  | CRD2   | 78  | CPUDB1  | 113 | TXC0    | 148 | TXC3    | 183 | CPUDB6  |

| 9   | RXD1  | 44  | RXC2   | 79  | VDD     | 114 | TXD0    | 149 | TXE3    | 184 | Vdd     |

| 10  | TEST0 | 45  | RXD2   | 80  | CPUDB2  | 115 | GND     | 150 | BDNAIL  | 185 | CPUDB7  |

| 11  | RESET | 46  | VDD    | 81  | CPUDB3  | 116 | COL0    | 151 | GND     | 186 | CPUDB12 |

| 12  | VDD   | 47  | CRD3   | 82  | CPUDB8  | 117 | TXE1    | 152 | NC      | 187 | CPUDB13 |

| 13  | Vdda  | 48  | RXC3   | 83  | CPUDB9  | 118 | TXC1    | 153 | HCLK    | 188 | CPUDB14 |

| 14  | GNDA  | 49  | RXD3   | 84  | CPUDB10 | 119 | TXD1    | 154 | CPURDIR | 189 | GND     |

| 15  | Vdda  | 50  | TEST3  | 85  | GND     | 120 | COL1    | 155 | VDD     | 190 | CPUDB15 |

| 16  | GNDA  | 51  | TEST4  | 86  | CPUDB11 | 121 | VDD     | 156 | NC1     | 191 | CPUAD0  |

| 17  | DI3   | 52  | GND    | 87  | CHSEL0  | 122 | DO0     | 157 | CPUAD7  | 192 | CPUAD1  |

| 18  | DI3   | 53  | VB0    | 88  | CHSEL1  | 123 | PEC0    | 158 | CPUAD8  | 193 | CPUAD2  |

| 19  | CI3   | 54  | VB1    | 89  | CHSEL2  | 124 | PEC0    | 159 | GND     | 194 | Vaa     |

| 20  | CI3   | 55  | PARITY | 90  | VDD     | 125 | DO0     | 160 | DATA8   | 195 | CPUAD3  |

| 21  | GNDA  | 56  | DATA0  | 91  | PFCS    | 126 | DO1     | 161 | DATA9   | 196 | CPUAD4  |

| 22  | VDDA  | 57  | VDD    | 92  | CPUSTRB | 127 | PEC1    | 162 | DATA10  | 197 | CPUAD5  |

| 23  | DI2   | 58  | DATA1  | 93  | CPUDVAL | 128 | PEC1    | 163 | DATA11  | 198 | CPUAD6  |

| 24  | DI2   | 59  | DATA2  | 94  | SOF     | 129 | DO1     | 164 | Voo     | 199 | GND     |

| 25  | Cl2   | 60  | DATA3  | 95  | GND     | 130 | GNDA    | 165 | DATA12  | 200 | CPUR/W  |

| 26  | CI2   | 61  | DATA4  | 96  | EOF     | 131 | Vdda    | 166 | DATA13  | 201 | RxREQ0  |

| 27  | DI1   | 62  | DATA5  | 97  | TxRDY   | 132 | DO2     | 167 | DATA14  | 202 | RxREQ1  |

| 28  | DI1   | 63  | GND    | 98  | TxABLE0 | 133 | PEC2    | 168 | DATA15  | 203 | RxREQ2  |

| 29  | CI1   | 64  | DATA6  | 99  | TxABLE1 | 134 | PEC2    | 169 | GND     | 204 | VDD     |

| 30  | CI1   | 65  | DATA7  | 100 | VDD     | 135 | DO2     | 170 | DATA24  | 205 | RxREQ3  |

| 31  | GNDA  | 66  | DATA16 | 101 | TxABLE2 | 136 | DO3     | 171 | DATA25  | 206 | RxRDY   |

| 32  | VDDA  | 67  | DATA17 | 102 | TxABLE3 | 137 | PEC3    | 172 | DATA26  | 207 | NC2     |

| 33  | DI0   | 68  | Vaa    | 103 | RTSEL   | 138 | PEC3    | 173 | DATA27  | 208 | GND     |

| 34  | D10   | 69  | DATA18 | 104 | GND     | 139 | DO3     | 174 | VDD     |     |         |

| 35  | C10   | 70  | DATA19 | 105 | FRMINT0 | 140 | GND     | 175 | DATA28  |     |         |

Lucent Technologies Inc.

6

Table 2. ATT1MX10 Signal According to Its Name in Alphabetic Sequence

| Name       | Pin | Name    | Pin | Name    | Pin | Name   | Pin | Name    | Pin | Name  | Pin |

|------------|-----|---------|-----|---------|-----|--------|-----|---------|-----|-------|-----|

| BDNAIL     | 150 | CPUDB10 | 84  | DATA19  | 70  | GND    | 7   | PEC3    | 138 | TXD1  | 119 |

| CHSEL0     | 87  | CPUDB11 | 86  | DATA20  | 71  | GND    | 40  | PFCS    | 91  | TXD2  | 142 |

| CHSEL1     | 88  | CPUDB12 | 186 | DATA21  | 72  | GND    | 52  | RESET   | 11  | TXD3  | 147 |

| CHSEL2     | 89  | CPUDB13 | 187 | DATA22  | 73  | GND    | 63  | RTSEL   | 103 | TXE0  | 112 |

| CI0        | 35  | CPUDB14 | 188 | DATA23  | 75  | GND    | 74  | RXC0    | 4   | TXE1  | 117 |

| <u>CI0</u> | 36  | CPUDB15 | 190 | DATA24  | 170 | GND    | 85  | RXC1    | 8   | TXE2  | 144 |

| Cl1        | 29  | CPUCS   | 76  | DATA25  | 171 | GND    | 95  | RXC2    | 44  | TXE3  | 149 |

| CI1        | 30  | CPUDVAL | 93  | DATA26  | 172 | GND    | 104 | RXC3    | 48  | TxRDY | 97  |

| CI2        | 25  | CPUINTR | 110 | DATA27  | 173 | GND    | 115 | RXD0    | 5   | VB0   | 53  |

| CI2        | 26  | CPURDIR | 154 | DATA28  | 175 | GND    | 140 | RXD1    | 9   | VB1   | 54  |

| Cl3        | 19  | CPUR/W  | 200 | DATA29  | 176 | GND    | 151 | RXD2    | 45  | VDD   | 2   |

| CI3        | 20  | CPUSTRB | 92  | DATA30  | 177 | GND    | 159 | RXD3    | 49  | Vaa   | 12  |

| COL0       | 116 | CRD0    | 3   | DATA31  | 178 | GND    | 169 | RxRDY   | 206 | VDD   | 46  |

| COL1       | 120 | CRD1    | 6   | DIO     | 33  | GND    | 179 | RxREQ0  | 201 | VaaV  | 57  |

| COL2       | 141 | CRD2    | 43  | DI0     | 34  | GND    | 189 | RxREQ1  | 202 | Voo   | 68  |

| COL3       | 146 | CRD3    | 47  | DI1     | 27  | GND    | 199 | RxREQ2  | 203 | Vdd   | 79  |

| CPUAD0     | 191 | DATA0   | 56  | DI1     | 28  | GND    | 208 | RxREQ3  | 205 | VDD   | 90  |

| CPUAD1     | 192 | DATA1   | 58  | DI2     | 23  | GNDA   | 14  | RXUNLD  | 180 | Voo   | 100 |

| CPUAD2     | 193 | DATA2   | 59  | DI2     | 24  | GNDA   | 16  | SOF     | 94  | Vpd   | 109 |

| CPUAD3     | 195 | DATA3   | 60  | DI3     | 18  | GNDA   | 21  | TEST0   | 10  | VDD   | 121 |

| CPUAD4     | 196 | DATA4   | 61  | DI3     | 17  | GNDA   | 31  | TEST1   | 41  | VDD   | 145 |

| CPUAD5     | 197 | DATA5   | 62  | DO0     | 122 | GNDA   | 37  | TEST2   | 42  | VDD   | 155 |

| CPUAD6     | 198 | DATA6   | 64  | DO0     | 125 | GNDA   | 130 | TEST3   | 50  | VDD   | 164 |

| CPUAD7     | 157 | DATA7   | 65  | DO1     | 126 | HCLK   | 153 | TEST4   | 51  | VDD   | 174 |

| CPUAD8     | 158 | DATA8   | 160 | DO1     | 129 | NC1    | 156 | NC      | 152 | VDD   | 184 |

| CPUDB0     | 77  | DATA9   | 161 | DO2     | 135 | NC2    | 207 | TxABLE0 | 98  | VDD   | 194 |

| CPUDB1     | 78  | DATA10  | 162 | DO2     | 132 | NC3    | 1   | TxABLE1 | 99  | VDD   | 204 |

| CPUDB2     | 80  | DATA11  | 163 | DO3     | 139 | PARITY | 55  | TxABLE2 | 101 | VDDA  | 13  |

| CPUDB3     | 81  | DATA12  | 165 | DO3     | 136 | PEC0   | 123 | TxABLE3 | 102 | VDDA  | 15  |

| CPUDB4     | 181 | DATA13  | 166 | ECLK    | 39  | PEC0   | 124 | TXC0    | 113 | Vdda  | 22  |

| CPUDB5     | 182 | DATA14  | 167 | EOF     | 96  | PEC1   | 127 | TXC1    | 118 | Vdda  | 32  |

| CPUDB6     | 183 | DATA15  | 168 | FRMINT0 | 105 | PEC1   | 128 | TXC2    | 143 | VDDA  | 38  |

| CPUDB7     | 185 | DATA16  | 66  | FRMINT1 | 106 | PEC2   | 133 | TXC3    | 148 | VDDA  | 131 |

| CPUDB8     | 82  | DATA17  | 67  | FRMINT2 | 107 | PEC2   | 134 | TxCRC   | 111 |       |     |

| CPUDB9     | 83  | DATA18  | 69  | FRMINT3 | 108 | PEC3   | 137 | TXD0    | 114 |       |     |

Lucent Technologies Inc.

**—** 0050026 0027377 \$33 **—**

#### **Pin Descriptions**

**Table 3. Ethernet Media Interface Signals**

| Pin                                          | Signal                                                                   | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------|--------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

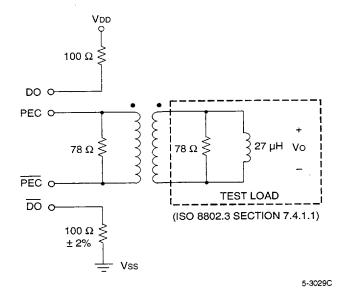

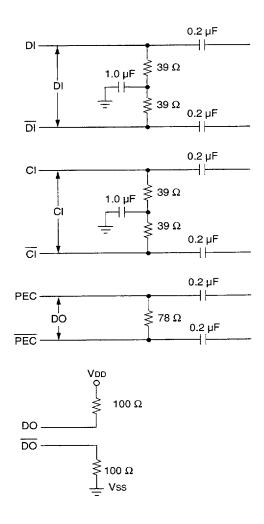

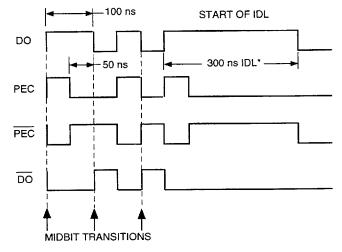

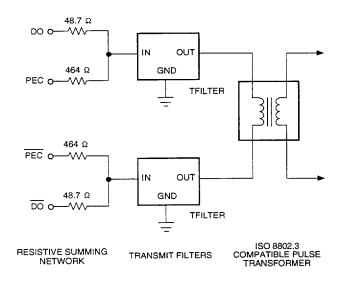

| 122, 125<br>126, 129<br>135, 132<br>139, 136 | DO0, DO0<br>DO1, DO1<br>DO2, DO2<br>DO3, DO3                             | 0    | Transmit Data Differential Pair. If the media bits in the port's receive frame configuration register are 00, these pins are used for twisted-pair transmit data and should be connected to a filter module through a 48.7 $\Omega$ resistor. The data is Manchester encoded with a nominal bit rate of 10 Mbits/s. If the media bits are 01, these pins should be connected to external 100 $\Omega$ pull-up and pull-down resistors to complete the AUI transmit driver. If the media bits are 10 (MAC mode), these signals can be left unconnected.                                                                                                              |

| 123, 124<br>127, 128<br>134, 133<br>138, 137 | PEC0, PEC0<br>PEC1, PEC1<br>PEC2, PEC2<br>PEC3, PEC3                     | 0    | <b>Pre-Equalization Control Differential Pair.</b> If the media bits in the port's receive frame configuration register are 00, these pins are used for TP Manchester data pre-equalization and should be connected to a filter module through a 464 $\Omega$ resistor. If the media bits are 01, these pins are connected, via isolation, to the transmit (DO) pair of the AUI transceiver cable. In AUI configuration, a 78 $\Omega$ resistor should be connected, in parallel, across the PEC and PEC signals. The data is Manchester encoded with a nominal bit rate of 10 Mbits/s. If the media bits are 10 (MAC mode), these signals can be left unconnected. |

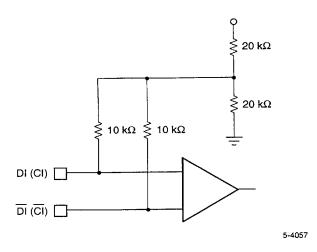

| 34, 33<br>28, 27<br>24, 23<br>18, 17         | DIO, <u>DIO</u><br>DI1, <u>DI1</u><br>DI2, <u>DI2</u><br>DI3, <u>DI3</u> | 1    | <b>Differential Data Inputs.</b> If the media bits in the port's receive frame configuration register are 00, these pins are differential Manchester-encoded receive data from the twisted-pair isolation transformers and filters. If the media bits are 01, these pins are connected via isolation to the receive (DI) pair of the AUI transceiver cable. Data on these pairs is Manchester encoded at the nominal rate of 10 Mbits/s plus any jitter. These pairs include internal 20 k $\Omega$ common-mode bias networks. If the media bits are 10 (MAC mode), these signals can be left unconnected.                                                          |

| 35, 36<br>29, 30<br>25, 26<br>19, 20         | CIO, <u>CIO</u><br>CI1, <u>CI1</u><br>CI2, <u>CI2</u><br>CI3, <u>CI3</u> |      | <b>AUI Collision Differential Pair.</b> If the media bits in the port's receive frame configuration register are 01, these pins are connected, via isolation, to the collision presence (CI) pair of the AUI transceiver cable. The collision presence signal is a 10 MHz $\pm$ 15% square wave. These pairs include internal 20 k $\Omega$ common-mode bias networks. If the media bits are not 01, these pins are not used and can be left unconnected.                                                                                                                                                                                                           |

| 3<br>6<br>43<br>47                           | CRD0<br>CRD1<br>CRD2<br>CRD3                                             | I/O  | Carrier Detect. While the MAC interface is selected (Media = 10), carrier detect is an active-high input driven by an external device to initiate the reception of a frame. Carrier detect is also sensed during a transmission to tell if the media is being driven by another device. While the media bits are not 10, this signal is an output and reflects the state of the internal carrier detect output from the internal transceiver. This input is ignored while the port is programmed for full duplex.                                                                                                                                                   |

| 4<br>8<br>44<br>48                           | RXC0<br>RXC1<br>RXC2<br>RXC3                                             | I/O  | Receive Clock. While the MAC interface is selected (Media = 10), this clock input is driven by an external device. The clock is derived from the recovered Manchester data by a transceiver/clock recovery device. Data is latched into the ATT1MX10 on the rising edge of RXC. During idle condition and reset, RXC can be held high or kept running. Five RXC cycles must be received after CRD is deasserted low at the end of a frame reception. While the media bits are not 10, this signal is an output and represents the internal state of the receive clock output from the internal receiver.                                                            |

#### Pin Descriptions (continued)

Table 3. Ethernet Media Interface Signals (continued)

| Pin          | Signal               | Туре | Name/Description                                                                                                                                                                                                                             |

|--------------|----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>9<br>45 | RXD0<br>RXD1<br>RXD2 | I/O  | <b>Receive Data.</b> While the MAC interface is enabled (Media = 10), this data input is driven by an external device. NRZ data recovered from the transceiver/clock recovery device is driven to the ATT1MX10 on this input. RXD is latched |

| 49           | RXD3                 |      | by the ATT1MX10 on the rising edge of RXC. While the media bits are not 10, this signal is an output and represents the internal state of receive data driven by the internal receiver.                                                      |

| 112          | TXE0                 | 0    | <b>Transmit Enable.</b> While the MAC interface is selected (Media = 10), transmit                                                                                                                                                           |

| 117          | TXE1                 | ŀ    | enable is driven active-high on the rising edge of TXC by the ATT1MX10 to ini-                                                                                                                                                               |

| 144          | TXE2                 |      | tiate a frame transmission. While media is not equal to 10, this signal repre-                                                                                                                                                               |

| 149          | TXE3                 |      | sents the internal state of transmit enable output from the internal MAC.                                                                                                                                                                    |

| 113          | TXC0                 | 1/0  | <b>Transmit Clock.</b> While the MAC interface is selected (Media = 10), transmit                                                                                                                                                            |

| 118          | TXC1                 |      | clock is driven with a 10 MHz clock that must be generated by an external                                                                                                                                                                    |

| 143          | TXC2                 |      | device connected to the ATT1MX10. The ATT1MX10 uses this clock to drive                                                                                                                                                                      |

| 148          | TXC3                 |      | TXD synchronous to the transceiver. When the media bits are not set to 10,                                                                                                                                                                   |

|              |                      |      | this signal is an output and represents the internal state of the transmit clock                                                                                                                                                             |

|              |                      |      | driven by the internal transceiver.                                                                                                                                                                                                          |

| 114          | TXD0                 | 0    | Transmit Data. While the MAC interface is enabled (Media = 10), the                                                                                                                                                                          |

| 119          | TXD1                 |      | ATT1MX10 drives NRZ data synchronous to TXC on transmit data. TXD is                                                                                                                                                                         |

| 142          | TXD2                 | ]    | driven high during idle conditions and reset. While media is not equal to 10, this signal represents the internal state of transmit data output from the inter-                                                                              |

| 147          | TXD3                 |      | nal MAC.                                                                                                                                                                                                                                     |

| 116          | COL0                 | 1/0  | Collision. While the MAC interface is selected (Media = 10), collision is driven                                                                                                                                                             |

| 120          | COL1                 |      | active-high by an external device when a collision is detected on the Ethernet                                                                                                                                                               |

| 141          | COL2                 |      | network. If COL is asserted high and the ATT1MX10 is transmitting, the                                                                                                                                                                       |

| 146          | COL3                 |      | ATT1MX10 will commence its collision backoff algorithm according to the                                                                                                                                                                      |

|              |                      |      | options set in the transmit frame configuration register. When the media bits                                                                                                                                                                |

|              |                      |      | are not set to 10, this signal is an output and represents the internal state of                                                                                                                                                             |

|              |                      |      | the collision output from the internal transceiver. This input is ignored while the                                                                                                                                                          |

|              |                      |      | port is programmed for full duplex.                                                                                                                                                                                                          |

| 39           | ECLK                 | 1    | Ethernet Clock. 20 MHz $\pm$ 0.01%, 50% nominal, 40—60 worst-case duty cycle. This clock must be driven regardless of the port configurations.                                                                                               |

|              |                      |      | <b>Note</b> : ISO 8802.3 requires the ±0.01% frequency tolerance. The tolerance and                                                                                                                                                          |

|              |                      |      | duty cycle figures are specified only to limit the range over which the                                                                                                                                                                      |

|              |                      |      | ATT1MX10 operates correctly. However, since this clock is used for                                                                                                                                                                           |

|              |                      |      | Manchester data transmission, jitter performance degrades if clock                                                                                                                                                                           |

|              |                      |      | sources with relatively large tolerances are used.                                                                                                                                                                                           |

Lucent Technologies Inc.

**3050026 0027379 306**

# Pin Descriptions (continued)

**Table 4. DMA Interface Signals**

| Pin                                                                                                                                                                          | Signal                                                                                                                                                                                                                                               | Type           | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 56, 66<br>58, 67<br>59, 69<br>60, 70<br>61, 71<br>62, 72<br>64, 73<br>65, 75<br>160, 170<br>161, 171<br>162, 172<br>163, 173<br>165, 175<br>166, 176<br>167, 177<br>168, 178 | DATA0, DATA16 DATA1, DATA17 DATA2, DATA18 DATA3, DATA19 DATA4, DATA20 DATA5, DATA21 DATA6, DATA22 DATA7, DATA23 DATA8, DATA24 DATA9, DATA25 DATA10, DATA26 DATA11, DATA27 DATA12, DATA28 DATA13, DATA29 DATA14, DATA29 DATA14, DATA30 DATA15, DATA31 | I/O<br>3-state | Data Bus. The data bus is a 32-bit, bidirectional bus that interfaces to the transmit FIFO and the receive FIFO. The state of RTSEL determines whether the data bus is an input or an output. The ATT1MX10 requires one HCLK cycle to switch the data bus from Tx to Rx or from Rx to Tx.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 55                                                                                                                                                                           | Parity                                                                                                                                                                                                                                               | I/O<br>3-state | <b>Parity.</b> Parity is generated during a DMA read cycle by the ATT1MX10. This bit represents the parity of the data being driven on DATA[31:0]. Parity is expected to be driven on this signal during a DMA write cycle. Parity as an input is not defined; the device is not differentiated between processing of packets with good parity and processing of packets with bad parity. This signal is valid based on the parity selection bits in the global configuration register. Parity should be tied to ground through a 100 kΩ resistor if this function is not being used.                                                                                                                                                  |

| 54<br>53                                                                                                                                                                     | VB1<br>VB0                                                                                                                                                                                                                                           | I/O<br>3-state | Valid Bytes. As an input, valid bytes are sampled on every rising edge of HCLK while PFCS and TxRDY are active and are qualified by EOF and CHSEL. VB signifies the valid bytes in the doubleword transferred to the Tx FIFO. VB is latched for retransmission during a collision. As an output, VB is driven while PFCS, RxUNLD, RxRDY, and CHSEL are active to indicate which bytes in the current doubleword are valid at the end of an Rx frame. VB is qualified with EOF. Note that only the last transfer of frame data can contain invalid bytes. Refer to the section on the global FIFO configuration register for a description of the valid byte decode. The state of RTSEL determines whether VB is an input or an output. |

| 153                                                                                                                                                                          | HCLK                                                                                                                                                                                                                                                 | I              | <b>Host Clock.</b> The host clock is used to clock data to and from the transmit and receive FIFOs, as well as all the internal digital logic of the ATT1MX10. Data can be read or written to one of the FIFOs through the data bus on each rising edge of HCLK. The host clock can be run up from 16 MHz to 25 MHz. HCLK must be active during reset. HCLK should have a 50% nominal duty cycle, $\pm 5\%$ if 22.5 MHz $\leq$ HCLK $\leq$ 25 MHz. If 16 MHz $\leq$ HCLK $<$ 22.5 MHz, then the tolerance on the duty cycle can be $\pm 10\%$ .                                                                                                                                                                                        |

# Pin Descriptions (continued)

Table 4. DMA Interface Signals (continued)

| Pin            | Signal                     | Туре           |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                 |                                                                  | Description                                                                                                                                                                                                                                                                               |

|----------------|----------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 91             | PFCS                       |                | Port FIFO Chip Select (Active-Low). The port FIFO chip select input selects the ATT1MX10 FIFO interface. The data bus will be driven one HCLK cycle after PFCS becomes active-low with RTSEL high. The bus will be inactive (3-state) after PFCS is deasserted high or RTSEL is driven low. All DMA inputs are invalid if PFCS is high (inactive). |                                                                                                                                                                                                                                                                 |                                                                  |                                                                                                                                                                                                                                                                                           |

| 89<br>88<br>87 | CHSEL2<br>CHSEL1<br>CHSEL0 | ſ              | ATT1MX10<br>signal is q                                                                                                                                                                                                                                                                                                                            | Channel Select. The channel select inputs are used to select one of the four ATT1MX10 transmit or receive ports during an access to the Tx or Rx FIFO. This signal is qualified with RTSEL and PFCS. When the bus is parked, all transfer attempts are ignored. |                                                                  |                                                                                                                                                                                                                                                                                           |

|                |                            |                | CHSEL2                                                                                                                                                                                                                                                                                                                                             | CHSEL1                                                                                                                                                                                                                                                          | CHSEL0                                                           | Definition                                                                                                                                                                                                                                                                                |

|                |                            |                | 1                                                                                                                                                                                                                                                                                                                                                  | X                                                                                                                                                                                                                                                               | X                                                                | Bus Parked                                                                                                                                                                                                                                                                                |

|                |                            |                | 0                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                               | 0                                                                | Port 0 selected                                                                                                                                                                                                                                                                           |

|                |                            |                | 0                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                               | 1                                                                | Port 1 selected                                                                                                                                                                                                                                                                           |

|                |                            |                | 0                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                               | 0                                                                | Port 2 selected                                                                                                                                                                                                                                                                           |

|                |                            |                | 0                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                               | 1                                                                | Port 3 selected                                                                                                                                                                                                                                                                           |

| 103            | RTSEL                      | ł              | bus. When<br>low, the da<br>and CHSE<br>EOF, VB1,                                                                                                                                                                                                                                                                                                  | high, the A<br>ta bus is ar<br>L. When R1<br>VB0, Parity                                                                                                                                                                                                        | TT1MX10 DA<br>n input (Tx FI<br>TSEL change<br>r, and DATA[3     | out controls the direction of the ATT1MX10 data ATA bus is an output (Rx FIFO accesses). When FO accesses). This input is qualified with PFCS as from low to high, the ATT1MX10 asserts SOF, B1:0] after the rising edge of HCLK. These signals ial delay when RTSEL switches to a low.   |

| 94             | SOF                        | I/O<br>3-state | cates that<br>SOF is dri<br>RxRDY are<br>active whe<br>access. SO                                                                                                                                                                                                                                                                                  | the current<br>ven on the r<br>e valid. Whe<br>en the first w                                                                                                                                                                                                   | DMA slave to<br>rising edge of<br>en RTSEL is<br>vord of a trans | RTSEL is high (read), SOF is an output and indiransfer contains the first byte of a received frame. If HCLK while PFCS is low and CHSEL and low (write), SOF is an input and should be driven smit frame is valid during the current DMA slave T1MX10 on the rising edge of HCLK by PFCS, |

| 96             | EOF                        | I/O<br>3-state | cates that<br>frame data<br>CHSEL ar<br>should be<br>current DN                                                                                                                                                                                                                                                                                    | the current<br>a. EOF is drind RxRDY a<br>driven actived Aslave ac                                                                                                                                                                                              | DMA slave t<br>iven on the r<br>re valid. Whe<br>we when the !   | RTSEL is high (read), EOF is an output and indiransfer contains the last byte of the received ising edge of HCLK while PFCS is low and en RTSEL is low (write), EOF is an input and ast word of a transmit frame is valid during the qualified by the ATT1MX10 on the rising edge of DY.  |

#### Pin Descriptions (continued)

**Table 5. Transmit Control Signals**

| Pin                    | Signal                                   | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 98<br>99<br>101<br>102 | TxABLE0<br>TxABLE1<br>TxABLE2<br>TxABLE3 | 0    | Transmit FIFO DMA Request (Active-Low). The ATT1MX10 will assert this signal low when the transmit FIFO is capable of accepting data. The amount of free bytes in the FIFO will be equal to or greater than the word count threshold set in the global FIFO configuration register. Note that when a transmit channel is selected, the ATT1MX10 will deassert the corresponding TxABLE signal after one HCLK cycle and TXABLE cannot be reasserted while the corresponding transmit channel remains selected. |

| 97                     | TxRDY                                    | l    | Transmit FIFO Data Ready (Active-Low). The ATT1MX10 will clock data on the rising edge of HCLK from the data bus into the transmit FIFO while this input is active-low. When TXRDY transitions to an inactive state, high, the ATT1MX10 stops clocking data into the transmit FIFO. This signal can be used to insert wait-states in the DMA cycle. This input is qualified with TXABLE, PFCS, RTSEL, and CHSEL.                                                                                              |

| 111                    | TxCRC                                    | I    | Transmit CRC Checksum. This input is sampled on every HCLK while TxRDY is active and is qualified by PFCS, TxRDY, CHSEL, RTSEL, and EOF. If TxCRC is high, the CRC checksum value will be calculated and appended to the transmitted frame. If it is low, the CRC will not be calculated and appended. This input is latched for retransmission during a collision. TxCRC is ignored when HWCRC bit = 0.                                                                                                      |

#### **Table 6. Receive Control Signals**

| Pin                      | Signal                               | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|--------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 201<br>202<br>203<br>205 | RXREQ0<br>RXREQ1<br>RXREQ2<br>RXREQ3 | 0    | Receive FIFO DMA Request (Active-Low). When data in the receive FIFO reaches the threshold indicated by the RxSFTH (receive start of frame threshold), the ATT1MX10 asserts RxREQ indicating that the system can read data. Subsequent assertions of RxREQ during the same frame will occur when the number of data bytes in the FIFO is greater than or equal to the word count threshold. Both thresholds are set in the global FIFO configuration register. Note that when a receive channel is selected, the ATT1MX10 will deassert the corresponding RxREQ signal after one HCLK cycle and the ATT1MX10 cannot assert RXREQ again while the corresponding receive channel is selected. |

| 180                      | RXUNLD                               | 1    | Receive FIFO DMA Acknowledge (Active-Low). The host asserts this signal low to acknowledge an RxREQ when it is able to read data from the Rx FIFO on the ATT1MX10 data bus. When RxUNLD is deasserted high, the ATT1MX10 stops clocking data from the receive FIFO. This signal can be used to insert wait-states into the DMA cycle. This input is qualified with PFCS, RTSEL, and CHSEL.                                                                                                                                                                                                                                                                                                  |

| 206                      | RxRDY                                | 0    | Receive FIFO Data Ready (Active-Low). This output is asserted low when valid Rx data is driven on the ATT1MX10 DATA bus. This signal will be asserted while RxUNLD is held low. When RxRDY is driven low, CHSEL can be changed to start reading data from the next channel.                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### Pin Descriptions (continued)

**Table 7. CPU Interface Signals**

| Pin                                                                                  | Symbol                                                                                                                        | Туре           | Description                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 76                                                                                   | CPUCS                                                                                                                         | I              | <b>CPU Chip Select (Active-Low)</b> . CPUCS must be asserted low in order to access a register or counter in the ATT1MX10. All CPU accesses are qualified with CPUCS.                                                                                                                                                                       |

| 154                                                                                  | CPURDIR                                                                                                                       | 1              | Reserved. Connect this signal to ground.                                                                                                                                                                                                                                                                                                    |

| 191, 197<br>192, 198<br>193, 157<br>195, 158<br>196                                  | CPUAD0, CPUAD5<br>CPUAD1, CPUAD6<br>CPUAD2, CPUAD7<br>CPUAD3, CPUAD8<br>CPUAD4                                                | 1              | CPU Address Bus. The address bus is used during CPU accesses to the ATT1MX10 configuration and control registers and the ATT1MX10 counters. The address specifies which counter or register is being read or written. Data is latched by address; if CPUAD changes state, new data will be driven. CPUAD is qualified by CPUCS and CPUSTRB. |

| 77, 82<br>78, 83<br>80, 84<br>81, 86<br>181, 186<br>182, 187<br>183, 188<br>185, 190 | CPUDB0, CPUDB8 CPUDB1, CPUDB9 CPUDB2, CPUDB10 CPUDB3, CPUDB11 CPUDB4, CPUDB12 CPUDB5, CPUDB13 CPUDB6, CPUDB14 CPUDB7, CPUDB15 | I/O<br>3-state | CPU Data Bus. The 16-bit CPU data bus is used for reading and writing counters and registers in the ATT1MX10. CPUDB is driven by the ATT1MX10 while CPUCS and CPUSTRB are asserted and CPUR/W is high. When doing back-to-back read writes, the ATT1MX10 requires one HCLK cycle to 3-state the bus.                                        |

| 200                                                                                  | CPUR/W                                                                                                                        | 1              | CPU Read/Not Write. The CPUR/W signal indicates which direction the CPU data bus will be in for the current register or counter access. The signal should be driven high when reading a register/counter and low when writing a register. This signal is qualified with CPUCS and CPUSTRB.                                                  |

| 92                                                                                   | CPUSTRB                                                                                                                       | 1              | CPU Data Strobe (Active-Low). The CPU data strobe qualifies an access to the CPU interface. This signal is used to latch data and address into the ATT1MX10 during a write operation. During a read, this signal is used by the CPU to latch data from the ATT1MX10 data bus.                                                               |

# Pin Descriptions (continued)

Table 7. CPU Interface Signals (continued)

| Pin                      | Symbol                                   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------|------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 93                       | CPUDVAL                                  | 0    | CPU Data Valid (Active-Low). This signal is an output and is driven by the ATT1MX10 during a read when data becomes valid. During a write, the ATT1MX10 will drive this signal low when it latches data from the bus.                                                                                                                                                                                                                                   |

| 110                      | CPUINTR                                  | 0    | CPU Interrupt (Active-Low). The CPU interrupt will be active when any one of the event counters reaches its maximum limit. (Counters will roll over and continue to count). The particular counter that caused the interrupt can be determined by reading the counter overflow indication register. As an option, the FRMINT interrupts can be routed to CPUINTR. In this case, CPUINTR will be driven low when any of the FRMINT pins would be driven. |

| 105<br>106<br>107<br>108 | FRMINTO<br>FRMINT1<br>FRMINT2<br>FRMINT3 | 0    | Frame Interrupt (Active-Low). Each port of the ATT1MX10 is capable of interrupting a host when an error occurs while a frame is being received or transmitted. The frame interrupt signal is maskable by the frame interrupt mask register. The frame interrupt register indicates which events caused the interrupt.                                                                                                                                   |

# Pin Descriptions (continued)

Table 8. Miscellaneous Signals

| Pin                                                                                                 | Signal                                          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11                                                                                                  | RESET                                           | I    | Reset (Active-Low). This input places the ATT1MX10 into a reset state. When RESET is deasserted high, the ATT1MX10 will be in an idle state. All counters will be cleared and configuration registers will be set to their default values. In order to effectively reset the ATT1MX10, RESET must be held active until ECLK and HCLK are running. RESET needs to be driven after powerup to put the ATT1MX10 into a known configuration. After a RESET cycle, the ATT1MX10 will be ready to transmit and receive frames; configuration registers only need to be written if the default configuration needs to be changed. |

| 10<br>41<br>42<br>50<br>51<br>152                                                                   | TEST0<br>TEST1<br>TEST2<br>TEST3<br>TEST4<br>NC | 1    | Test Pins. (6 pins.) These pins should be tied low for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2, 121,<br>12, 145,<br>46, 155,<br>57, 164,<br>68, 174,<br>79, 184,<br>90, 194,<br>100, 204,<br>109 | VDD                                             |      | Digital Power. (17 pins.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 13, 32,<br>15, 38,<br>22, 131,                                                                      | VDDA                                            |      | Analog Power. (6 pins.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

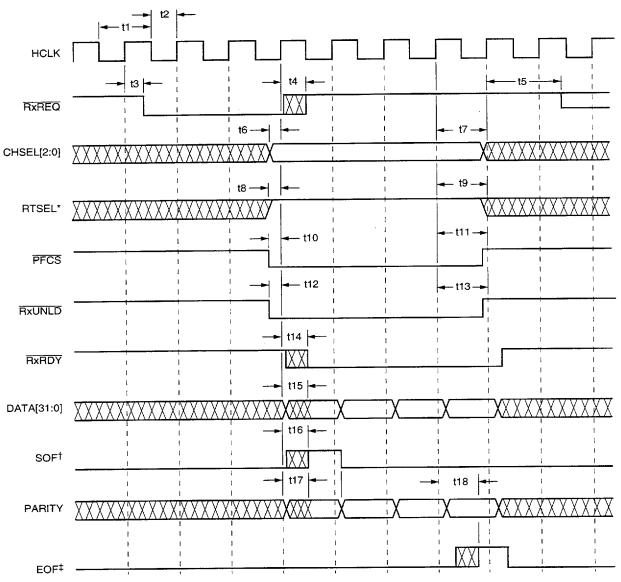

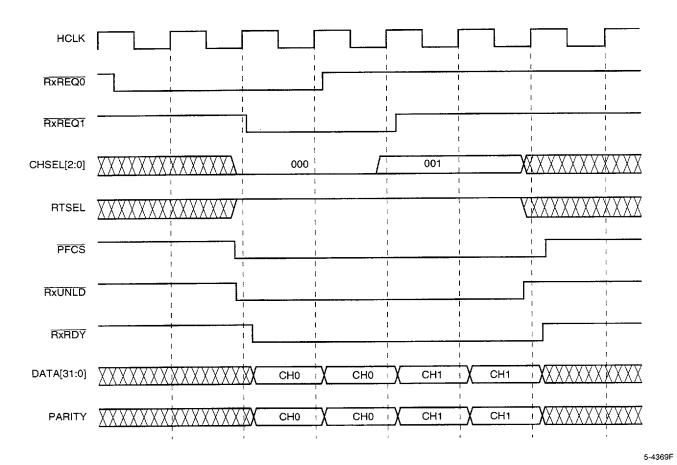

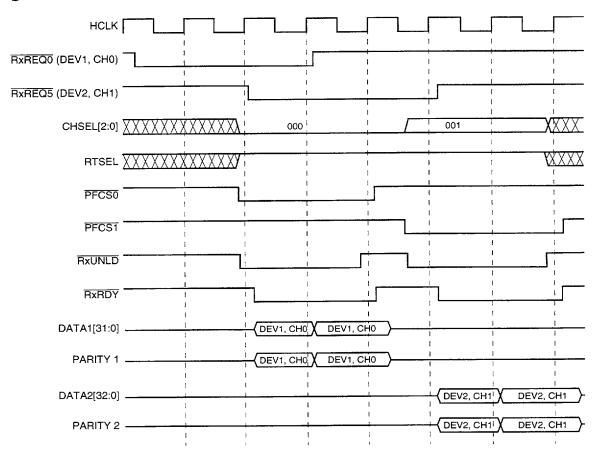

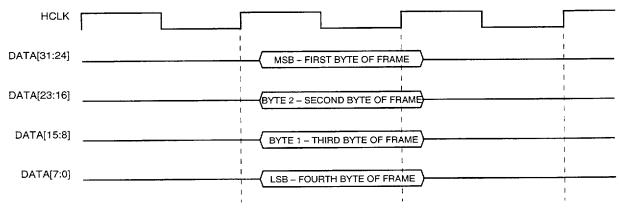

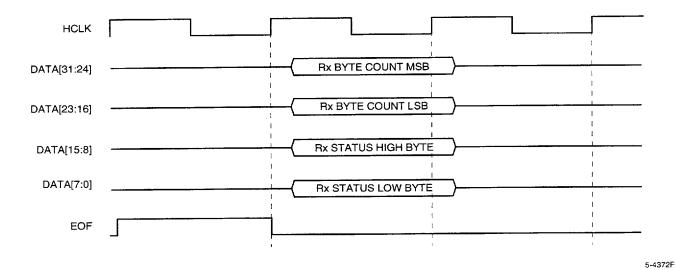

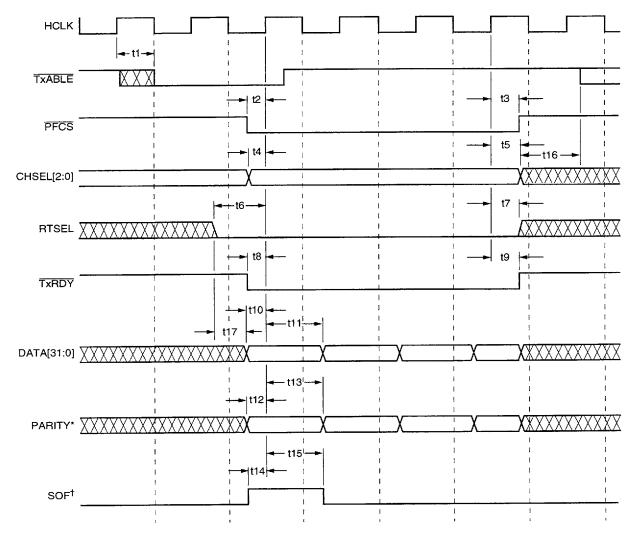

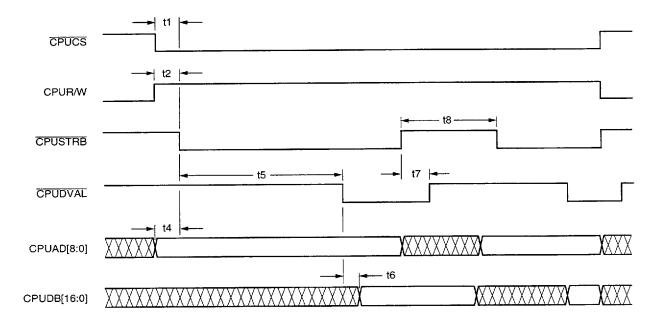

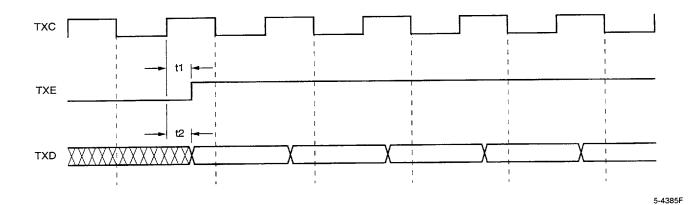

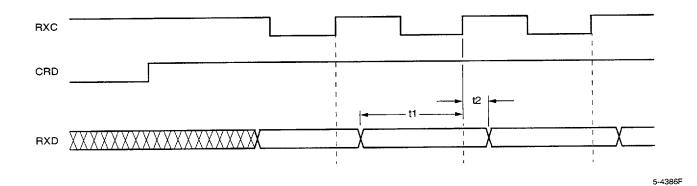

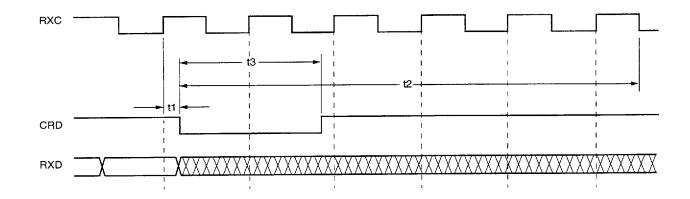

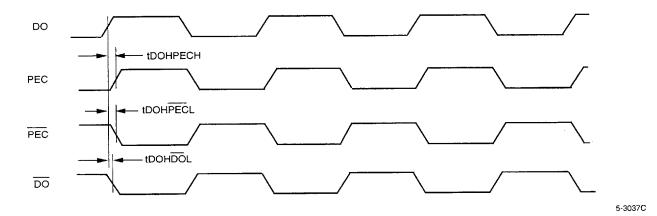

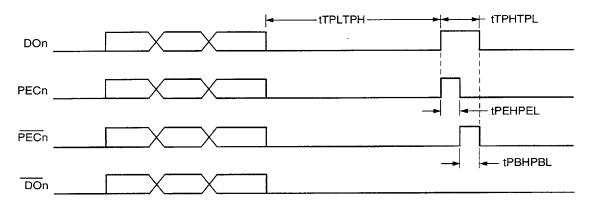

| 7, 140,<br>40, 151,<br>52, 159,<br>63, 169,<br>74, 179,<br>85, 189,<br>95, 199,<br>104, 208,<br>115 | GND                                             | _    | Digital Ground. (17 pins.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |