# AmPAL\*22V10-15/22V10-20T-46-13-47

24-Pin IMOX IIITM Programmable Array Logic (PAL)

### **PRELIMINARY**

### DISTINCTIVE CHARACTERISTICS

- 15-ns performance

- Increased logic power up to 22 inputs and 10 outputs

- Increased product terms average 12 per output

- Variable product-term distribution improves ease of use

- Each output user-programmable for registered or combinatorial operation

- Individually user-programmable output polarity

- Extra terms provide logical synchronous-PRESET and asynchronous-RESET capability

- TTL-level PRELOAD for improved testability

- Packaged in 24-pin Slim DIP and 28-pin chip-carrier packages

- Platinum-Silicide fuses ensure high programming yield, fast programming, and unsurpassed reliability

- AC and DC testing done at the factory utilizing special designed-in test features

- 3000-V Input ESD Protection on all pins

### **GENERAL DESCRIPTION**

The AmPAL22V10 is a second-generation Programmable Array Logic (PAL) device. It utilizes the familiar sum-ofproducts (AND-OR) logic structure, allowing users to program custom logic functions. The AmPAL22V10 is an extension of the PAL concept. First-generation devices were largely limited to TTL-replacement applications. The AmPAL22V10 permits the development of custom LSI functions of 500 to 800 equivalent gate complexity.

The AmPAL22V10 contains up to 22 inputs and 10 outputs. It incorporates the unique capability of defining and programming the architecture of each output on an individual basis. Each output is user-programmable for either registered or combinatorial operation. This allows the designer to optimize the device design by having only as many registers as needed. In addition, each output has userprogrammable output polarity, further simplifying design and contributing to the precise application requirements.

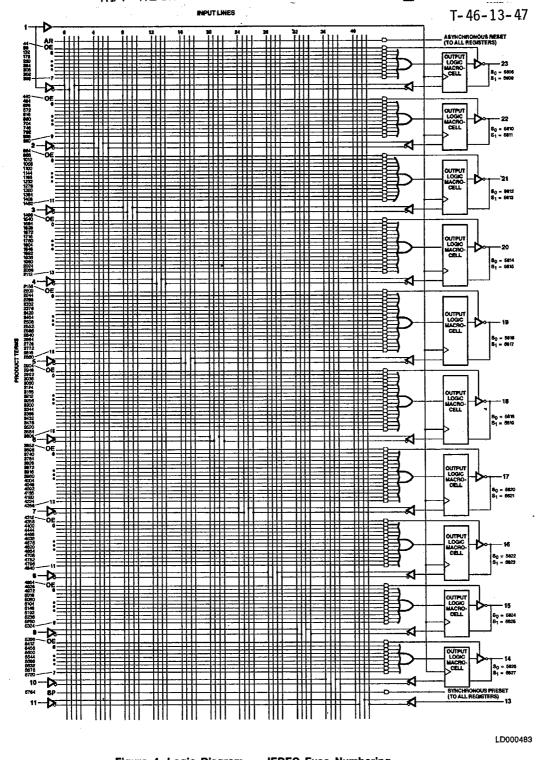

Increased logic power has been built into the AmPAL22V10 by increasing the number of product terms from 8-peroutput to an average of 12-per-output. Further innovation can be seen in the introduction of variable product-term distribution. This technique allocates from 8 to 16 logical product terms to each output (please refer to the Block Diagram for distribution details). This variable allocation of terms allows far more complex functions to be implemented than in previous devices.

System operation has been enhanced by the addition of a synchronous-PRESET and an asynchronous-RESET product term. These terms are common to all output registers.

The AmPAL22V10 also incorporates power-up RESET and the unique capability to PRELOAD the output registers to any desired state during testing. PRELOAD is essential to permit full logical verification during test.

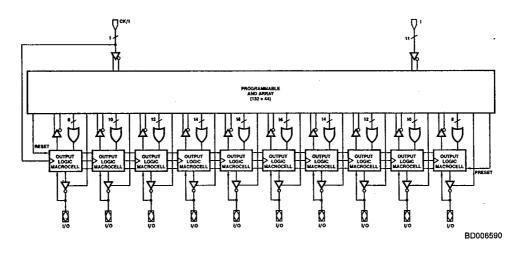

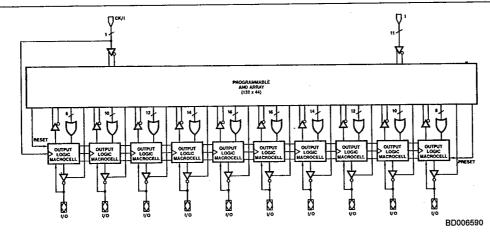

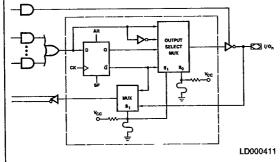

### **BLOCK DIAGRAM**

PAL is a registered trademark of and is used under license from Monolithic Memories, Inc. IMOX is a trademark of Advanced Micro Devices, Inc.

Issue Date: September 1987

18 1/04 16 🗆 17 103 17 🗆 1/03 18 🗖 8 16 1/02 19 🛮 10 15 1/01 i<sub>10</sub> 🗖 11 14 1/00 구울 GND 12 13 🔲 111 CD010001 CD010011

> \*Also available in PLCC. Pinouts identical to LCC. \*\*Also available in Flatpack. Pinouts identical to DIPs.

= Input Pin Designations: I

= Input/Output 1/0

V<sub>CC</sub> = Supply Voltage

GND = Ground CK = Clock

= No Connection

### **ORDERING INFORMATION**

### Standard Products

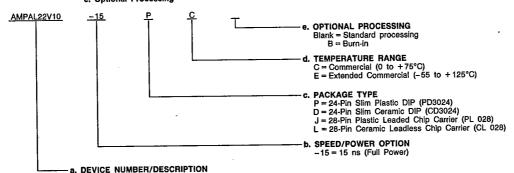

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number b. Speed/Power Option (if applicable) c. Package Type d. Temperature Range e. Optional Processing

AmPAL22V10-15 24-Pin IMOX III Programmable Array Logic

| Valid Com     | binations        |

|---------------|------------------|

| AMPAL22V10-15 | PC, DC, DCB, DE, |

### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

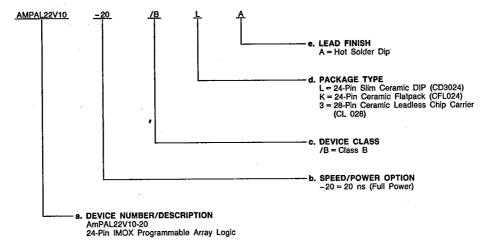

### MILITARY ORDERING INFORMATION

**APL** Products

T-46-13-47

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of: a. Device Number

b. Speed/Power Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

| Valid Comb    | Inations     |

|---------------|--------------|

| AMPAL22V10-20 | /BLA/B3A/BKA |

### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, and 11.

# FUNCTIONAL DESCRIPTION

The AmPAL22V10 is a second-generation Programmable Array Logic device. It contains a programmable fuse array organized in the familiar sum-of-products (AND-OR) structure.

The block diagram below shows the basic architecture of the AmPAL22V10. There are up to 22 inputs and 10 outputs available. The inputs are connected to a programmable-AND array which contains 120 logical product terms. Initially the AND gates are connected, via fuses, to both the TRUE and COMPLEMENT of every input. By selective programming of fuses, the AND gates may be "connected" to only the TRUE input (by blowing the COMPLEMENT fuse), to only the COMPLEMENT input (by blowing the TRUE fuse), or to neither type of input (by blowing both fuses), establishing a logical "don't care." When both the TRUE and COMPLEMENT fuses are left intact, a logical FALSE results on the output of the AND gate. An AND gate with all fuses blown will assume the logical-TRUE state. The outputs of the AND gates are connected to fixed-OR gates. There is an average of 12 product terms per OR gate (output), and as the Block Diagram shows, variable product term distribution has been implemented. This technique allocates different quantities of logical product terms to different outputs, allowing more complex logical functions to be performed than were previously possible. Up to 16 logical terms can be evaluated in one output in a single clock cycle (no feedback necessary).

## Output Logic Macrocells (OLMs)

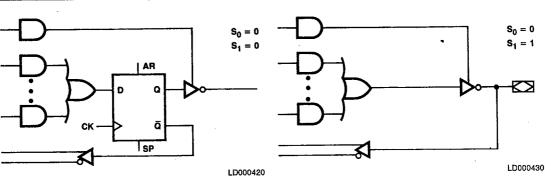

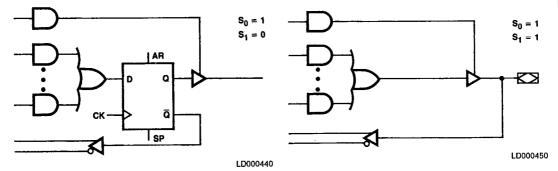

A dramatic innovation in logic design is the implementation on the AmPAL22V10 of variable output architecture. This allows the user to program, on an output-by-output basis, the function of the outputs. As shown in the Output Logic Macrocell (OLM) diagram below, each output cell contains two additional fuses, So and S1. S1 controls whether the output will be registered or combinatorial. So controls the output polarity (active HIGH or active LOW). Depending on the states of these two fuses, an individual output will operate in one of four modes (see the logic diagrams on the next page): Registered/Active LOW, Registered/Active HIGH, Combinatorial/Active LOW, and Combinatorial/Active HIGH (note that the feedback path also changes with output mode). This innovation gives the designer more flexibility and enables optimization of the device for precise application requirements. It also allows for better device utilization - programming only as many registers as are needed.

### PRESET/RESET

To improve in-system functionality, the AmPAL22V10 has additional PRESET and RESET product terms. These terms are connected to all registered outputs. When the synchronous-PRESET product term is asserted (HIGH), the output registers will be loaded with a HIGH on the next LOW-to-HIGH clock transition. When the asynchronous-RESET product term is asserted (HIGH), the output registers will be immediately loaded with a LOW (independent of the clock). These functions are particularly useful for applications such as system power-on and reset.

Figure 1. Block Diagram

| S <sub>1</sub> | S <sub>0</sub> | Output Configuration      |

|----------------|----------------|---------------------------|

| 0              | 0              | Registered/Active LOW     |

| 0              | 1              | Registered/Active HIGH    |

| 1              | 0              | Combinatorial/Active LOW  |

| 1              | 1              | Combinatorial/Active HIGH |

0 = Unblown Fuse 1 = Blown Fuse

Figure 2. Output Logic Macrocell Diagram

To simplify testing, the AmPAL22V10 is designed with unique PRELOAD circuitry that provides an easy method of testing registered devices for logical functionality. PRELOAD allows any arbitrary state value to be loaded into the output registers.

A typical functional test sequence would be to verify all possible state transitions for the device being tested. To verify these transitions requires the ability to set the state registers into an arbitrary "present state" value, and to set the device inputs to any arbitrary "present input" value. Once this is done, the state machine is then clocked into a new state, or "next state." The next state is then checked to validate the transition from the present state. In this way any state transition can be checked.

Without PRELOAD, it is difficult and in some cases impossible to load an arbitrary present state value. This can lead to logic verification sequences that are either incomplete or excessively long. Long test sequences result when the feedback from the state register "interferes" with the inputs, forcing the state machine to go through many state transitions before it can reach an arbitrary state value. Therefore the test sequence will be mostly state initialization and not actual testing. The test sequence becomes excessively long when a state must be reentered many times to test a wide variety of input combina-

In addition, complete logic verification may become impossible when states that need to be tested cannot be entered with normal state transitions. For example, the state which the machine powers-up into cannot be tested because it cannot be entered from the main sequence. Similarly, "forbidden" or don't care states that are not normally entered need to be tested to ensure that they return to the main sequence.

PRELOAD eliminates these problems by providing the capability to go directly to any desired arbitrary state. Thus test sequences may be greatly shortened, and all possible states can be tested, greatly reducing test time and development costs, and guaranteeing proper in-system operation.

T-46-13-47

The AmPAL22V10-15 is manufactured using Advanced Micro Devices' IMOX III slot-isolation process. This advanced process is an extension of the IMOX II process. It uses slot isolation between transistors to permit an increase in density and a decrease in internal capacitance, resulting in the fastest possible programmable-logic devices.

These devices are fabricated with AMD's fast programming, highly reliable Platinum-Silicide Fuse technology. Utilizing an easily implemented programming algorithm, these products can be rapidly programmed to any customized pattern. Extra test words are preprogrammed during manufacturing to ensure extremely high field programming yields (> 98.5%), and to provide extra test paths to achieve excellent parametric correlation.

Platinum Silicide was selected as the fuse-link material to achieve a well-controlled melt rate resulting in large nonconductive gaps that ensure very stable, long-term reliability. Extensive operating testing has proven that this low-field, large-gap technology offers the best reliability for fusible-link programmable logic.

Figure 3-1. Registered/Active LOW

Figure 3-3. Combinatorial/Active LOW

Figure 3-2. Registered/Active HIGH

Figure 3-4 Combinatorial/Active HIGH

Figure 4. Logic Diagram — JEDEC Fuse Numbering

# APV MICRO PLA/PLE/ARRAYS 96

# **OPERATING RANGES**

| ABSOLUTE MAXIMUM RATINGS T-46-                                     | 13-47    |

|--------------------------------------------------------------------|----------|

| · · · · · · · · · · · · · · · · · · ·                              | Comme    |

| Storage Temperature65 to +150°C Supply Voltage to Ground Potential | Tem      |

| (Pin 24 to Pin 12) Continuous0.5 to +7 V                           | Supp     |

| DC Voltage Applied to Outputs                                      | Extende  |

| (Except During Programming)0.5 V to +VCC Max.                      | Tem      |

| DC Voltage Applied to Outputs                                      | Tem      |

| During Programming 16 V                                            | Sup      |

| Output Current into Outputs During Programming                     |          |

| (Max. Duration of 1 sec)                                           | Military |

| DC Input Voltage0.5 to +5.5 V                                      | Tem      |

| DC Input Current30 to +5 mA                                        | Ten      |

| Ambient Temperature with Power Applied + 125°C                     | Sup      |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

|                                         | •                     |

|-----------------------------------------|-----------------------|

| Commercial (C) Devices                  |                       |

| Temperature (T <sub>A</sub> ) Operating | Free Air 0°C to +75°C |

| Supply Voltage (VCC)                    | + 4.75 to +5.25 V     |

Extended Commercial (E) Devices Temperature (T<sub>A</sub>).....-55°C Min. Temperature (T<sub>C</sub>).....+125°C Max. Supply Voltage (V<sub>CC</sub>) .....+4.50 to +5.50 V

Military (M) Devices\* Temperature (T<sub>A</sub>).....-55°C Min. Temperature (T<sub>C</sub>) Operating Case ......+ 125°C Max. Supply Voltage (VCC) .....+4.50 to +5.50 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

\*Military Product 100% tested at  $T_C = +25$ °C, +125°C, and -55°C.

DC CHARACTERISTICS over operating range unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol         | Parameter<br>Description     | Test                                                                            | Conditions                |                  | Min.     | Typ.<br>(Note:1) | Max. | Unit     |

|-----------------------------|------------------------------|---------------------------------------------------------------------------------|---------------------------|------------------|----------|------------------|------|----------|

| <u> </u>                    |                              |                                                                                 | COM'L                     | MIL &<br>E-COM'L |          |                  |      |          |

| VoH                         | Output HIGH Voltage          | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OH</sub> = -3.2 mA | OH = 2 mA        | 2.4      | 3,5              |      | V        |

| V <sub>OL</sub>             | Output LOW Voltage           | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | 1 <sub>OL</sub> = 16 mA   | VOL = 12 mA      | 10 h     |                  | 0.50 | ٧        |

| V <sub>IH</sub><br>(Note 2) | Input HIGH Level             | Guaranteed Input Logical F                                                      | GH Voltage for all        | Inputs           | 2.0      |                  |      | ٧        |

| V <sub>IL</sub><br>(Note 2) | Input LOW Level              | Guaranteed Input Logical L                                                      | OW Voltage for M          | Inputs           |          |                  | 0.8  | V        |

| TIL.                        | Input LOW Current            | V <sub>QC</sub> = Max., V <sub>IN</sub> = 0.40 V                                |                           |                  | <u> </u> | -20              | -100 | μA       |

| I <sub>I</sub> H            | Input HIGH Current           | V <sub>C</sub> G = Max., V <sub>IN</sub> = 2.7 V                                |                           |                  | <u> </u> | ļ                | 25   | μΑ       |

| lı .                        | Input HIGH Current           | VCC + Max., VIN = 5.5 V                                                         |                           |                  | <u> </u> | <u> </u>         | 1.0  | mA       |

| Isc                         | Output Short-Circuit Corrent | V <sub>CC</sub> = Max., V <sub>OUT</sub> = 0.5 V                                | (Note 3)                  |                  | -30      | -50              | -90  | mA       |

|                             | FX XX 1                      | (3) V                                                                           |                           | В                | <u> </u> | 150              | 180  | 1        |

| lcc ڃ                       | Power Supply Current         | V <sub>CC</sub> = Max.                                                          |                           | AL               |          | 75               | 90   | mA       |

| ~~ <b>E</b>                 | 化月冠 炒。                       |                                                                                 |                           | Q                |          | 40               | 55   | <u> </u> |

| Vı                          | Input Clamp Voltage          | V <sub>CC</sub> = Min., I <sub>IN</sub> = -18 mA                                |                           |                  |          | -0.9             | -1.2 |          |

| lozh                        | Output Leakage Current       | V <sub>CC</sub> = Max., V <sub>IN</sub> = V <sub>IL</sub>                       | V <sub>O</sub> = 2.7 V    |                  |          |                  | 100  | μΑ       |

| lozi                        | (Note 4)                     | or VIH                                                                          | V <sub>O</sub> = 0.4 V    | -                |          |                  | -100 |          |

Notes: 1, Typical limits are at V<sub>CC</sub> = 5.0 V and T<sub>A</sub> = 25°C.

2. These are absolute values with respect to device ground, and all overshoots due to system or tester noise are included.

3. Not more than one output should be tested at a time. Duration of the short-circuit test should not exceed one second.

V<sub>OUT</sub> = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

4. I/O pin leakage is the worst case of I<sub>OZX</sub> or I<sub>IX</sub> (where X = H or L).

5. Pinout for DIPs only.

### CAPACITANCE

| Parameter<br>Symbol | Parameter<br>Description | Test Condition                               | ons        | Min. | Typ.<br>(Note 1) | Max. | Unit |

|---------------------|--------------------------|----------------------------------------------|------------|------|------------------|------|------|

|                     |                          |                                              | Pins 1, 13 | _    | 9                |      |      |

| C <sub>IN</sub> †   | Input Capacitance        | V <sub>IN</sub> = 2.0 V @ f = 1 MHz (Note 5) | Others     |      | 6                |      |      |

| C <sub>OUT</sub> †  | Output Capacitance       | V <sub>OUT</sub> = 2.0 V @f = 1 MHz          |            |      | 9                |      | pF   |

<sup>†</sup> Not included in Group A tests.

T-46-13-47

|     | Parameter        | Parameter                                                                                 | 22V  | 10-15 |      |      |      |      |      |

|-----|------------------|-------------------------------------------------------------------------------------------|------|-------|------|------|------|------|------|

| No. | Symbol           | Description                                                                               | Min. | Max.  | Min. | Max. | Min. | Max. | Unit |

| 1   | tpD              | Input or Feedback to Non-Registered Output                                                | 1 .  | 15    |      |      |      |      | ns   |

| 2   | tEA              | Input to Output Enable                                                                    |      | 15    |      |      |      |      | ns   |

| 3   | t <sub>ER</sub>  | Input to Output Disable                                                                   |      | 15    |      |      |      |      | ns   |

| 4   | <sup>†</sup> CO1 | Clock to Output                                                                           |      | 12    |      |      | 1    |      | ns   |

| 5   | tco2             | Register Feedback through Array to<br>Combinatorial Output, Relative to External<br>Clock |      | 22    |      |      |      |      | ns   |

| 6   | ts               | Input or Feedback Setup Time                                                              | 13   | ٠.    |      | il.  | 1    |      | ns   |

| 7   | tн               | Hold Time                                                                                 | 0    | •     |      | A.X  |      |      | ns   |

| 8   | tp               | Clock Period (ts + tco1)                                                                  | 25   |       | V    | V    |      | ,    | ns   |

| 9   | twн              | Clock Width - HIGH Level                                                                  | 10   |       | . 1  | 5    |      |      | ns   |

| 10  | tWL              | Clock Width - LOW Level                                                                   | 40   | E A   |      |      |      |      | ns   |

| 11  | fMAX             | Maximum Frequency                                                                         | EN.  | 10/   | -    |      |      |      | ns   |

| 12  | taw              | Asynchronous - RESET Width                                                                | 15   | 10    |      |      |      |      | ns   |

| 13  | †AR              | Asynchronous - RESET Recovery Time                                                        | 46   |       |      |      |      |      | ns   |

| 14  | tap              | Asynchronous - RESET to Registered Output                                                 |      | 20    |      |      |      |      | ns   |

SWITCHING CHARACTERISTICS over MILITARY and EXTENDED-COMMERCIAL operating ranges (for APL Products, Group A, Subgroups 7, 8, 9, 10 11 and tested unless otherwise noted) (Note 2)

|     | Parameter       | Parameter                                                                     | 22V10-20 |      |      |      |      |         |      |

|-----|-----------------|-------------------------------------------------------------------------------|----------|------|------|------|------|---------|------|

| No. | Symbol          | Description                                                                   | Min.     | Max. | Min. | Max. | Min. | Max.    | Unit |

| 1   | t <sub>PD</sub> | Input or Feedback to Non-Registered Output                                    |          | 20   |      |      |      |         | ns   |

| 2   | tea .           | Input to Output Enable                                                        |          | 20   |      |      | i .  | <b></b> | ns   |

| 3   | t <sub>ER</sub> | Input to Quiput Disable                                                       |          | 20   |      |      |      |         | ns   |

| 4   | tco1            | Clock to Output                                                               |          | 15   |      |      |      |         | ns   |

| 5   | tcoa            | Register Feedback through Array to Combinatorial Output, Relative to External |          | 30   |      |      |      |         | ns   |

| 6   | ts 💜            | Input or Feedback Setup Time                                                  | 17       |      |      |      |      |         | пѕ   |

| 7   | th 🛂            | Hold Time                                                                     | 0        |      |      |      |      | · -     | ns   |

| 8   | tp              | Clock Period (ts + tCO1)                                                      | 32       | 1    |      |      |      |         | ns   |

| 9   | ¹wн             | Clock Width - HIGH Level                                                      | 15       |      |      |      |      |         | ris  |

| 10  | twL             | Clock Width - LOW Level                                                       | 15       |      |      |      |      |         | ns   |

| 11  | fMAX            | Maximum Frequency                                                             | 1        | 31   |      |      |      |         | ns   |

| 12  | tAW             | Asynchronous - RESET Width                                                    | 20       |      |      |      |      |         | ns   |

| 13  | t <sub>AR</sub> | Asynchronous - RESET Recovery Time                                            | 20       |      |      |      |      |         | ns   |

| 14  | tap             | Asynchronous - RESET to Registered Output                                     | 1        | 25   |      |      |      | <b></b> | ns   |

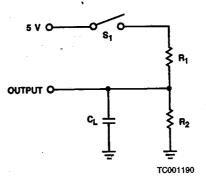

Notes: 1. Commercial Test Conditions: R<sub>1</sub> = 300, R<sub>2</sub> = 390,

2. Military/Extended-Commercial Test Conditions: R<sub>1</sub> = 390, R<sub>2</sub> = 750,

3. tpp is tested with switch S<sub>1</sub> closed and C<sub>L</sub> = 50 pF.

4. For three-state outputs, output enable times are tested with C<sub>L</sub> = 50 pF to the 1.5 V level; S<sub>1</sub> is open for high-impedance to HIGH tests and closed for high-impedance to LOW tests. Output disable times are tested with C<sub>L</sub> = 5 pF. HIGH to high-impedance tests are made to an output voltage of V<sub>OH</sub> - 0.5 V with S<sub>1</sub> open; LOW to high-impedance tests are made to the V<sub>OL</sub> + 0.5 V level with S<sub>1</sub> closed.

T-46-13-47

## **SWITCHING WAVEFORMS** KEY TO SWITCHING WAVEFORMS

| WAVEFORM     | INPUTS                                 | OUTPUTS                                            |

|--------------|----------------------------------------|----------------------------------------------------|

|              | MUST BE<br>STEADY                      | WILL BE<br>STEADY                                  |

| <i>IIIII</i> | MAY CHANGE<br>FROM H TO L              | WILL BE<br>CHANGING<br>FROM H TO L                 |

|              | MAY CHANGE<br>FROM L TO H              | WILL BE<br>CHANGING<br>FROM L TO H                 |

| <u> </u>     | DON'T CARE;<br>ANY CHANGE<br>PERMITTED | CHANGING;<br>STATE<br>UNKNOWN                      |

| ₩            | DOES NOT<br>APPLY                      | CENTER<br>LINE IS HIGH<br>IMPEDANCE<br>"OFF" STATE |

|              |                                        | KS000010                                           |

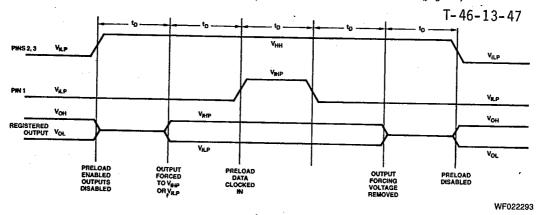

The AmPAL22V10 registered outputs are provided with circuitry to allow loading each register synchronously with either a

HIGH or LOW. This feature will simplify testing since any state can be loaded into the registers to control test sequencing.

The pin levels and timing necessary to perform the PRELOAD function are detailed below. Parameters are listed in the Programming Parameters table (page 12).

| Level forced<br>on registered<br>output pin during<br>PRELOAD cycle | Register Q<br>output state<br>after cycle |

|---------------------------------------------------------------------|-------------------------------------------|

| V <sub>IHP</sub>                                                    | HIGH                                      |

| V <sub>ILP</sub>                                                    | LOW                                       |

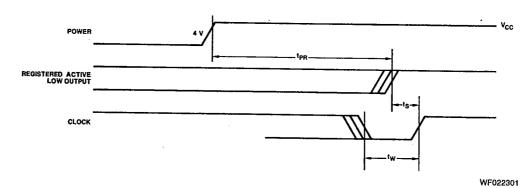

### Power-Up RESET

The registered devices in the AMD PAL Family have been designed with the capability to reset during system power-up. Following power-up, all registers will be reset to LOW. The output state will depend on the polarity of the output buffer. This feature provides extra flexibility to the designer and is especially valuable in simplifying state machine initialization. A timing diagram and parameter table are shown below. Due to

the asynchronous operation of the power-up reset, and the wide range of ways  $V_{CC}$  can rise\*to its steady state, two conditions are required to ensure a valid power-up reset. These conditions are:

- 1. The V<sub>CC</sub> rise must be monotonic.

- Following reset, the clock input must not be driven from LOW to HIGH until all applicable input and feedback setup times are met.

| Parameter<br>Symbol | Parameter<br>Description        | Min.  | Тур.                     | Max. | Unit    |  |

|---------------------|---------------------------------|-------|--------------------------|------|---------|--|

| ter                 | Power-Up<br>Reset Time          |       | 600                      | 1000 | ns      |  |

| ts                  | Input or Feedback<br>Setup Time | See S | Switching                |      | rintina |  |

| tw                  | Clock Width                     |       | See Switching Characteri |      |         |  |

### **Programming and Verification**

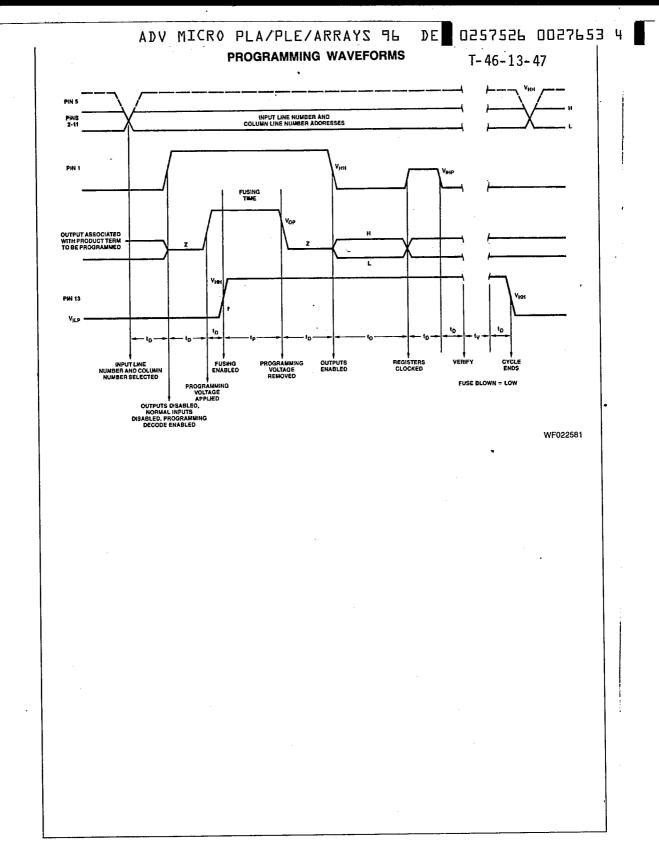

The AmPAL22V10 is programmed and verified using AMD's standard programmable logic programming algorithm. The fuse to be programmed is selected by input line number (array row), product term (array column), and by output (one at a time). The fuse is then programmed and verified by applying a simple sequence of voltages to two control pins (1 and 13).

Input line numbers (0 – 43) are addressed using a full decode scheme via TTL levels on pins 6 – 11 where 6 is the LSB and 11 is the MSB. Even-numbered input lines represent the TRUE version of a signal and odd-numbered lines represent the complement. Input line addressing is shown in Table 1. Note that input lines 44 – 62 are reserved for further expansion, and input line 63 is utilized for selecting the fuses used for programming output polarity and whether the output is registered or combinatorial.

Product terms are addressed using a 1-of-24 addressing scheme on pins 2 – 5 where pin 2 is the LSB and 5 is the MSB. Product term addressing is shown in Table 2. Logical product terms (0 – 15) are selected via TTL levels on the four addressing pins. Note that outputs with fewer than 16 product terms will decode blank space for decoding values greater than the number of product terms on that output. Architectural product terms are selected by placing a zener voltage level (V<sub>HH</sub>) on the MSB (pin 5) and using pins 2 – 4 for an additional eight decoding states (only five are used). The specific decoding of architectural features is best shown in Table 2.

Fuse selection by output must be done one output at a time (following control pin 1 going to  $V_{HH}$ ) as shown in the Programming Waveform diagram.

Once fuses have been selected, the simple programming and verification sequence may be completed as shown in the

Programming Waveform diagram. AC and DC requirements for programming are shown in the Programming Parameters table.

### Security Fuse Programming

T-46-13-47

A single fuse is provided on each AmPAL22V10 part to prevent unauthorized copying of PAL fuse patterns. Once blown, the circuitry enabling fuse verification and registered output PRELOAD is permanently disabled.

Programming of the security fuse is the same as an array fuse. Verification of a blown security fuse is accomplished by verifying the whole fuse array as if every fuse were blown.

### **Programming Yield**

AMD PAL devices have been designed to ensure extremely high programming yields ( > 98%). To help ensure that a part was correctly programmed, once programming is completed, the entire fuse array should be reverified at both LOW and HIGH V<sub>CC</sub>. Reverification can be accomplished by reading all ten outputs in parallel rather than one at a time. This verification cycle checks that the array fuses have been blown and can be sensed by the outputs under varying conditions. Programming yield losses are most likely due to poor programming socket contact, programming equipment out of calibration, or improper usage of said equipment.

### Post-Programming Functional Yield (PPFY)

AMD PAL devices contain many internal test features, including circuitry and extra fuses which allow AMD to test the ability of each part to perform programming before shipping, to assure high programming yields, and to ensure correct logical operation for a correctly programmed part. This designed-in testability enables AMD's programmable logic devices to yield 99.9% PPFY (see Section 2.3 of the AMD Programmable Logic Handbook for further details).

### PROGRAMMING PARAMETERS (TA = 25°C)

| Parameter<br>Symbol | 1                                                    | meter<br>ription                   | Min.                   | Тур.             | Max.                   | Unit     |  |

|---------------------|------------------------------------------------------|------------------------------------|------------------------|------------------|------------------------|----------|--|

|                     | Control Pin Extra HIGH Level                         | Pin 1 @ 10 -40 mA                  | 10                     | 711              | 12                     | . v      |  |

| V <sub>HH</sub>     | (Note 1)                                             | Pin 13 @ 10 -40 mA                 | 10 🕥                   | 12:              | 12                     | <u>\</u> |  |

| VOP                 | Program Voltage Pins 14 - 23 @                       | 15 - 200 mA (Note 1)               | 14                     | . 15             | <b>\</b> 16            | ۷.       |  |

| VIHP                | Input HIGH Level During Program                      | nming and Verify                   | 2.4                    | 5 💽              | 5.5                    | V        |  |

| VILP                | Input LOW Level During Program                       | ming and Verify                    | 0.0                    | 0.3              | 0.5                    | ٧        |  |

| VCCP                | V <sub>CC</sub> During Programming @ I <sub>CC</sub> | = 50 - 200 mA                      | <b>( 1</b> )           | 5.2              | 5.5                    | V        |  |

| VCCL                | V <sub>CC</sub> During First-Pass Verification       | @ 1cc +50-200 mA                   | 4.4                    | 4.5              | 4.6                    | V        |  |

| VCCH                | V <sub>CC</sub> During Second-Pass Verifica          |                                    | 5.4                    | 5.5              | 5.6                    | V        |  |

| VBlown              | Successful Blown Fuse Sense L                        | evel & Quiput                      |                        | 0.3              | 0.5                    | . V      |  |

| V <sub>OP</sub> /dt | Rate of Output Voltage Change                        |                                    | 20                     |                  | 250                    | V/µs     |  |

| V <sub>13</sub> /dt | Rate of Fusing Enable Voltage (Note 1)               | Change (Pin 13 Rising Edge)        | 100                    |                  | 1000                   | V/µs     |  |

|                     | Fusing Time, First Attempt                           |                                    | 10                     | 50               | 100                    | μs       |  |

| ¹P <b>\</b> ( )     | Subsequent Attempts (Maximum                         | 4                                  | 5                      | 10               | ms                     |          |  |

| t <sub>D</sub>      | Delays Between Various Level C                       | Changes                            | 100                    | 200              | 15,000                 | ns       |  |

| tv                  | Period During which Output is S                      | ensed for V <sub>Blown</sub> Level |                        |                  | 500                    | ns       |  |

| VONP                | Pull-Up Voltage on Outputs Not                       | Being Programmed                   | V <sub>CCP</sub> - 0.3 | V <sub>CCP</sub> | V <sub>CCP</sub> + 0.3 | ٧        |  |

| R                   | Pull-Up Resistor on Outputs Not                      |                                    | 1.9                    | 2                | 2,1                    | kΩ       |  |

Notes: 1. Pinout for DIPs only.

TABLE 1. INPUT ADDRESSING

T-46-13-47

| Input Line |                      | Input<br>Addr | t Line<br>ess F | Nun<br>in Si | nber`<br>ates |   | Input Line | Input Line Number<br>Address Pin States |   |      |     |    |    |

|------------|----------------------|---------------|-----------------|--------------|---------------|---|------------|-----------------------------------------|---|------|-----|----|----|

| Number     | 11 10 9 8 7 6 Number |               | Number          | 11           | 10            | 9 | 8          | 7                                       | 6 |      |     |    |    |

| Ó          | L                    | L             | L               | L            | L             | L | 32         | Н                                       | L | L    | L   | L  | L  |

| 1          | L                    | L             | L               | L            | L             | Н | 33         | Η                                       | ٦ | L    | L   | ۲  | Н  |

| 2          | L                    | L             | L               | L            | Н             | L | 34         | Н                                       | L | L    | L   | Ξ  | L, |

| 3          | L                    | L             | L               | L            | Н             | Н | 35         | Н                                       | L | L    | L   | Н  | Н  |

| 4          | L                    | L             | L               | Н            | ٦             | L | 36         | Н                                       | L | L    | Н   | L  | L  |

| 5          | L                    | L             | L               | H            | ٦             | H | 37         | Н                                       | L | L    | Н   | L_ | Н  |

| 6          | L                    | L             | L               | Η            | Ŧ             | r | 38         | Н                                       | L | L    | Н   | Н  | L  |

| 7          | L                    | L             | ٦               | Н            | Ξ             | H | 39         | Н                                       | L | L    | Н   | Н  | Н  |

| 8          | L                    | L             | H               | L            | L             | ٦ | 40         | н                                       | L | Н    | L   | L  | L  |

| 9          | L                    | L             | Ι               | ئـ           | L             | Η | 41         | Н                                       | L | Н    | L   | L  | Н  |

| 10         | L                    | Ļ             | H               | L            | Н             | L | 42         | Н                                       | L | Н    | L   | Н  | L  |

| 11         | L                    | L             | Ξ               | L            | Ι             | Н | 43         | Н                                       | L | Н    | L   | Н  | Н  |

| 12         | L                    | L             | Н               | Н            | ٦             | L |            | •                                       |   |      |     |    |    |

| 13         | L                    | L             | Н               | Ξ            | L             | Н |            | •                                       |   |      |     |    |    |

| 14         | L                    | L             | Н               | н            | Н             | L |            | •                                       |   |      | _   |    |    |

| 15         | L                    | L.            | Н               | Н            | Н             | Н |            | •                                       |   |      |     |    |    |

| 16         | L                    | Н             | L               | L            | L             | L |            | •                                       |   |      |     |    |    |

| 17         | L                    | Н             | L               | L            | L             | Н | _          | •                                       |   |      |     |    |    |

| 18         | L                    | Н             | L               | L            | Н             | L |            | •                                       |   |      |     |    |    |

| 19         | L                    | Н             | L               | L            | Н             | Н |            | •                                       |   |      |     |    |    |

| 20         | L                    | н             | L               | Н            | L             | L |            | •                                       |   |      |     |    |    |

| 21         | L                    | Н             | L               | Н            | L             | Н |            |                                         |   | RESE | RVE | )  |    |

| 22         | L                    | Н             | L               | Н            | Н             | L |            | •                                       |   |      |     |    |    |

| 23         | L,                   | Н             | L               | Н            | Н             | Н |            | •                                       |   |      |     |    |    |

| 24         | L                    | Н             | Н               | L            | L             | L |            | •                                       |   |      |     |    |    |

| 25         | 25 L H H L L H       |               |                 | •            |               |   |            |                                         |   |      |     |    |    |

| 26         | L                    | Н             | Н               | L            | Н             | L |            | •                                       |   |      |     |    |    |

| 27         | L                    | Н             | Н               | L            | Н             | Н |            | •                                       |   |      |     |    |    |

| 28         | L                    | Н             | Н               | Н            | L             | L |            |                                         |   |      | •   |    |    |

| 29         | L                    | Н             | Н               | Н            | L             | Н |            |                                         |   |      | •   |    |    |

| 30         | L                    | Н             | Н               | Н            | Н             | L |            |                                         |   |      | •   |    |    |

| 31         | L                    | Н             | Н               | Н            | Н             | Н | 63*        | Н                                       | Н | н    | Н   | Н  | Н  |

<sup>\*</sup>Architecture row

# ADV MICRO PLA/PLE/ARRAYS 9L TABLE 2. COLUMN NUMBER ADDRESSING

|           |                                   |           | -         |           |           |           |           |           |           | Column Number<br>Select Address<br>Pin States |   |   | 88 |                                            |

|-----------|-----------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------------------------------------------|---|---|----|--------------------------------------------|

|           |                                   |           | Col       | umn       | Numi      | ber       |           |           |           | 5                                             | 4 | 3 | 2  | Description                                |

| 0         | 0                                 | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         | L                                             | L | L | Γ. | Logical PTs                                |

| 1         | 1                                 | 1         | 1         | 1         | 1         | 1         | 1         | 1         | 1         | ٦                                             |   | 4 | I  | Logical PTs                                |

| 2         | 2                                 | 2         | 2         | 2         | 2         | 2         | 2         | 2         | 2         | L                                             | ۲ | Ι | نـ | Logical PTs                                |

| 3         | 3                                 | 3         | 3         | 3         | 3         | 3         | 3         | 3         | 3         | L                                             | L | Н | Н  | Logical PTs                                |

| 4         | 4                                 | 4         | 4         | 4         | 4         | 4         | 4         | 4         | 4         | L                                             | Н | L | L  | Logical PTs                                |

| 5         | 5                                 | 5         | 5         | 5         | 5         | 5         | 5         | 5         | 5         | L                                             | Н | L | H  | Logical PTs                                |

| 6         | 6                                 | 6         | 6         | 6         | 6         | 6         | 6         | 6         | 6         | L                                             | Н | Ξ | L  | Logical PTs                                |

| 7         | 7                                 | 7         | 7         | 7         | 7         | 7         | 7         | 7         | 7         | L                                             | Н | Н | Н  | Logical PTs                                |

| -         | 8                                 | 8         | 8         | 8         | 8         | 8         | 8         | 8         | -         | Н                                             | L | L | L  | Logical PTs                                |

| -         | 9                                 | 9         | 9         | 9         | 9         | 9         | 9         | 9         | -         | Н                                             | L | L | Ξ  | Logical PTs                                |

| -         | -                                 | 10        | 10        | 10        | 10        | 10        | 10        |           | •         | Н                                             | L | Н | L  | Logical PTs                                |

| -         | -                                 | 11        | 11        | 11        | 11        | 11        | 11        | -         | -         | Η                                             | L | Н | Н  | Logical PTs                                |

| -         | -                                 | -         | 12        | 12        | 12        | 12        | -         |           |           | Н                                             | Н | L | L  | Logical PTs                                |

| -         | -                                 | -         | 13        | 13        | 13        | 13        | •         | •         | -         | Н                                             | Н | L | н  | Logical PTs                                |

|           | -                                 | -         | •         | 14        | 14        | -         | •         | •         | -         | Н                                             | Н | Н | L  | Logical PTs                                |

| -         | •                                 | -         | -         | 15        | 15        | -         | •         |           | •         | Н                                             | Ξ | Н | Н  | Logical PTs                                |

| OE        | OE                                | OE        | OE        | OE        | OE        | OE        | ΟE        | OE        | OE        | НН                                            | L | L | L  | Output Enable                              |

| Р         | Р                                 | Р         | Р         | Р         | Р         | Р         | Р         | Р         | Р         | НН                                            | L | L | н  | Output Polarity                            |

| R         | R                                 | R         | R         | R         | R         | R         | R         | R         | R         | НН                                            | L | Н | L  | Register/Non-Register Output               |

| -         | AR*                               | -         | -         | •         | -         | -         | -         | SP**      | -         | нн                                            | L | н | н  | *Asynchronous RESET * **Synchronous PRESET |

| -         | SF                                | -         | -         | •         | -         | -         | -         | -         | -         | нн                                            | Н | L | н  | Security Fuse<br>(Special Verify Required) |

| Pin<br>23 | Pin<br>22                         | Pin<br>21 | Pin<br>20 | Pin<br>19 | Pin<br>18 | Pin<br>17 | Pin<br>17 | Pin<br>15 | Pin<br>14 |                                               |   |   |    |                                            |

| Prog      | Programming Access and Verify Pin |           |           |           |           |           |           |           |           |                                               |   |   |    |                                            |

Legend: L = V<sub>ILP</sub> H = V<sub>IHP</sub> HH = V<sub>HH</sub>

# ADV MICRO PLA/PLE/ARRAYS 96 DE 0257526 0027654 6

## AMPAL22V10 PROGRAMMING EQUIPMENT INFORMATION

T-46-13-47

| Vendor                                                                                      | Programmer Model (s)                        | Personality Module                           | Socket Adapter                                                                        |  |  |

|---------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| Data I/O<br>10525 Willow Road N.E.                                                          | System 19, 29 or 100                        | Logicpak<br>715-1983-003<br>(Rev 4 or Newer) | 303A-004 (Rev 3 or Newer)<br>303A-011A (Rev 1 or Newer)<br>303A-011B (Rev 1 or Newer) |  |  |

| edmond, WA 98052<br>206) 881-6464                                                           | Model 60A or 60H                            | 360A-001 (Rev 4 or<br>Newer)                 | On-Board                                                                              |  |  |

| MC PROMAC Division<br>999 Monterey/Salinas<br>ighway<br>lonterey, CA 83940<br>108) 373-3622 | PROMAC P3<br>(Rev 2.0 or Newer)             | On-Board                                     | On-Board                                                                              |  |  |

| Stag Microsystems<br>128-5 Weddell Drive                                                    | Model PPZ                                   | Zm2200<br>(Rev 10 or Newer)                  | On-Board<br>(Rev 10 or Newer)                                                         |  |  |

| unnyvale, CA 94086<br>108) 745-1991 or<br>300) 227-8836                                     | Model ZL30, ZL30A,<br>ZL32                  | On-Board<br>(Rev 38 or Newer)                | On-Board<br>(Rev 38 or Newer)                                                         |  |  |

| Structured Design<br>188 Bryant Way<br>Sunnyvale, CA 94087<br>408) 988-0725                 | SD 1040 PAL Burner<br>(Rev V1.02A or Newer) | On-Board                                     | On-Board                                                                              |  |  |

| /alley Data Sciences<br>1426 Charleston Road<br>At. View, CA 94043<br>415) 968-2900         | VDS 160 Series                              | On-Board<br>(Rev 1.03 or Newer)              | On-Board                                                                              |  |  |

| /arix Corporation<br>22 Spanish Village<br>Suite 608<br>Dallas, TX 75248<br>214) 437-0777   | Omni-Programmer<br>SP0-300                  | Under Development                            | Under Development                                                                     |  |  |

| DIGELEC<br>1602 Lawrence Ave.,<br>Suite 113                                                 | 803 Series                                  | FAM52<br>(Rev 5.4 or Newer)                  | DA55<br>(Rev B3 or Newer)<br>(Rev V1.02A or Newer)                                    |  |  |

| Ocean,NJ 07712<br>210) 493-2424                                                             | 860 Series (Rev A 1.0 or Newer)             | On-Board                                     | On-Board                                                                              |  |  |

| CONTRON Electronics                                                                         | EPP-80                                      | On-Board                                     | On-Board                                                                              |  |  |

| 230 Charleston Rd<br>Iountain View, CA 94039<br>115) 965-7020                               | MPP-80S                                     | UPM/B Module (Version 1.45 or Newer)         | On-Board                                                                              |  |  |

| 800) 227-8834                                                                               |                                             | UPM/C Module (Version 1.45 or Newer)         |                                                                                       |  |  |

The machines noted above have been qualified by AMD to ensure high programming yields. Check with the factory to determine the current status of vendors noted under development, or other available models.

### Design Aid Software for AmPAL22V10

| Software<br>Vendor                          | Software<br>Package | Comments                                 |

|---------------------------------------------|---------------------|------------------------------------------|

| P-CAD<br>Systems<br>(408) 971-1300          | CUPL                |                                          |

| Advanced<br>Micro Devices<br>(408) 732-2400 | AmCUPL              | Developed and supported by P-CAD Systems |

| Data I/O<br>(206) 881-6444                  | ABEL                |                                          |

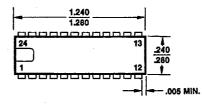

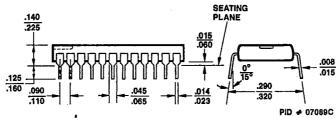

## PHYSICAL DIMENSIONS\*

T-46-13-47

### 'PD3024

### CD3024

PID # 06850B

\*For reference only.

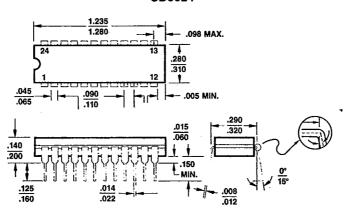

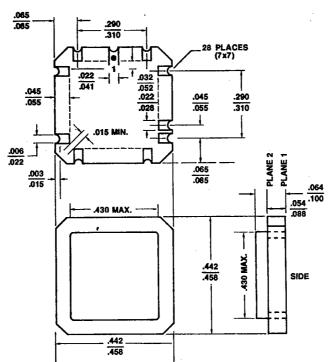

PHYSICAL DIMENSIONS (Cont'd.)

T-46-13-47.

PID # 06595E