### **FEATURES**

Access time: 85 ns (MAX.)

• Current consumption:

Operating: 30 mA (MAX.) 5 mA (MAX.) ( $t_{RC}$ ,  $t_{WC}$  = 1  $\mu$ s) Standby: 30  $\mu$ A (MAX.)

Data Retention:

$0.5 \mu A \text{ (Typ. } V_{CCDR} = 3 \text{ V}, t_A = 25 ^{\circ}\text{C})$

• Single power supply: 2.7 V to 3.6 V

Operating temperature: -25°C to +85°C

Fully-static operation

Three-state output

Not designed or rated as radiation hardened

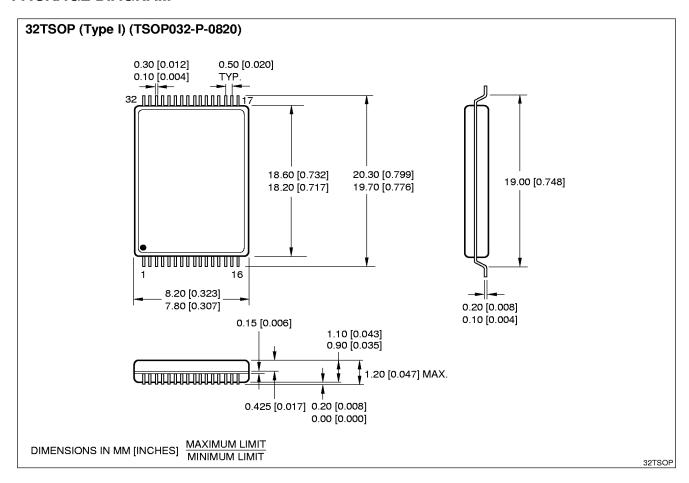

Package: 32-pin TSOP

N-type bulk silicon

### **DESCRIPTION**

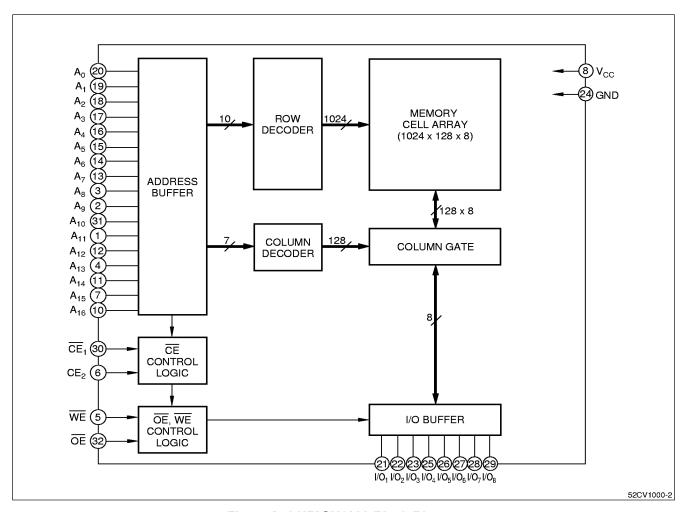

The LH52CV1000 is a static RAM organized as  $131,072\times 8$  bits which provides low-power standby mode. It is fabricated using silicon-gate CMOS process technology.

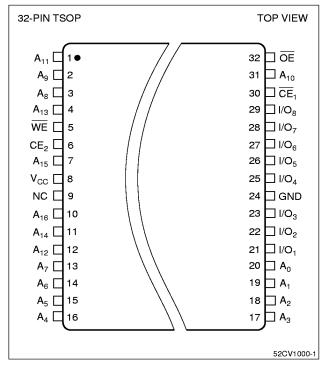

### PIN CONNECTIONS

Figure 1. Pin Connections for TSOP Package

Figure 2. LH52CV1000 Block Diagram

# **PIN DESCRIPTION**

| SIGNAL                           | PIN NAME       |

|----------------------------------|----------------|

| A <sub>0</sub> - A <sub>16</sub> | Address inputs |

| CE <sub>1</sub>                  | Chip enable 1  |

| CE <sub>2</sub>                  | Chip enable 2  |

| WE                               | Write enable   |

| ŌĒ                               | Output enable  |

| SIGNAL                              | PIN NAME                |

|-------------------------------------|-------------------------|

| I/O <sub>1</sub> - I/O <sub>8</sub> | Data inputs and outputs |

| Vcc                                 | Power supply            |

| GND                                 | Ground                  |

| NC                                  | No connection           |

# **TRUTH TABLE**

| CE <sub>1</sub> | CE <sub>2</sub> | WE | ŌĒ | MODE           | I/O <sub>1</sub> — I/O <sub>8</sub>     | SUPPLY CURRENT            | NOTE |

|-----------------|-----------------|----|----|----------------|-----------------------------------------|---------------------------|------|

| Н               |                 |    |    | Standby        | Standby High Standby (I <sub>SB</sub> ) |                           | 1    |

| _               | L               | _  |    | Startuby       | impedance                               | Standby (ISB)             | '    |

| L               | Н               | L  |    | Write          | Data input                              | Active (I <sub>CC</sub> ) | 1    |

| L               | Н               | Н  | L  | Read           | Data output                             | Active (I <sub>CC</sub> ) |      |

| L               | Н               | Н  | Н  | Output disable | High impedance                          | Active (I <sub>CC</sub> ) | _    |

### NOTE:

1. — = Don't care

L = Low

H = High

### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | SYMBOL           | RATING                        | UNIT | NOTE |

|-----------------------|------------------|-------------------------------|------|------|

| Supply voltage        | Vcc              | -0.5 to +4.6                  | ٧    | 1    |

| Input voltage         | V <sub>IN</sub>  | -0.5 to V <sub>CC</sub> + 0.5 | ٧    | 1, 2 |

| Operating temperature | T <sub>OPR</sub> | -25 to +85                    | °C   |      |

| Storage temperature   | T <sub>STG</sub> | -55 to +150                   | °C   | _    |

#### NOTES:

- 1. The maximum applicable voltage on any pin with respect to GND.

- 2. Undershoot of -3.0 V is allowed width of pulse below 50 ns.

# RECOMMENDED DC OPERATING CONDITIONS ( $T_A = -25$ °C to +85°C)

| PARAMETER      | SYMBOL          | MIN. | TYP. | MAX.                  | UNIT | NOTE |

|----------------|-----------------|------|------|-----------------------|------|------|

| Supply voltage | Vcc             | 2.7  | 3.0  | 3.6                   | ٧    | _    |

| Input voltage  | V <sub>IH</sub> | 2.0  |      | V <sub>CC</sub> + 0.3 | ٧    | _    |

| input voitage  | V <sub>IL</sub> | -0.3 |      | 0.8                   | ٧    | 1    |

# NOTE:

1. Undershoot of -3.0 V is allowed width of pulse below 50 ns.

# DC ELECTRICAL CHARACTERISTICS ( $T_A = -25$ °C to +85°C, $V_{CC} = 2.7$ V to 3.6 V)

| PARAMETER              | SYMBOL                                         | CONDITIONS                                                                                                                                                                                     |                           | MIN. | TYP. | MAX. | UNIT |

|------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------|------|------|

| Input leakage current  | ILI                                            | VIR = 0V to V <sub>CC</sub>                                                                                                                                                                    |                           | -1.0 | _    | 1.0  | μА   |

| Output leakage current | I <sub>LO</sub>                                | $\overline{CE_1} = V_{IH} \text{ or } CE_2 = V_{IL} \text{ or } \\ \overline{OE} = V_{IH} \text{ or } \overline{WE} = V_{IL} \\ V_{I/O} = 0 \text{ V to } V_{CC}$                              | -1.0                      |      | 1.0  | μΑ   |      |

| Operating              | 1 100 1 22 33 33 33 33 33 33 33 33 33 33 33 33 |                                                                                                                                                                                                | tcycle =<br>MIN.          |      |      | 30   | mA   |

| supply current         | I <sub>CC1</sub>                               | $\overline{CE}_1 = 0.2 \text{ V}, \text{ V}_{\text{IN}} = 0.2 \text{ V} \text{ or V}_{\text{CC}} - 0.2 \text{ V}$ $CE_2 = V_{\text{CC}} - 0.2 \text{ V}, \text{ I}_{\text{VO}} = 0 \text{ mA}$ | t <sub>CYCLE</sub> = 1 μs | _    | _    | 5    | ША   |

| Standby current        | I <sub>SB</sub>                                | $\overline{\text{CE}}_1,  \text{CE}_2 \ge \text{V}_{\text{CC}} - 0.2  \text{V} \text{ or } $ $\text{CE}_2 \le 0.2  \text{V}$                                                                   |                           | _    |      | 30   | μА   |

|                        | I <sub>SB1</sub>                               | $\overline{CE}_1 = V_{IH} \text{ or } CE_2 = V_{IL}$                                                                                                                                           |                           |      | _    | 0.5  | mA   |

| Output voltage         | V <sub>OL</sub>                                | I <sub>OL</sub> = 2.1 mA                                                                                                                                                                       |                           |      |      | 0.4  | ٧    |

| Output voltage         | V <sub>OH</sub>                                | $I_{OH} = -1.0 \text{ mA}$                                                                                                                                                                     | ·                         | 2.2  | _    | _    | V    |

# AC ELECTRICAL CHARACTERISTICS AC Test Conditions

| PARAMETER                          | MODE                            | NOTE |

|------------------------------------|---------------------------------|------|

| Input pulse level                  | 0.6 V to 2.2 V                  |      |

| Input rise and fall time           | 5 ns                            |      |

| Input and output timing Ref. level | 1.5 V                           |      |

| Output load                        | 1 TTL + C <sub>L</sub> (100 pF) | 1    |

### NOTE:

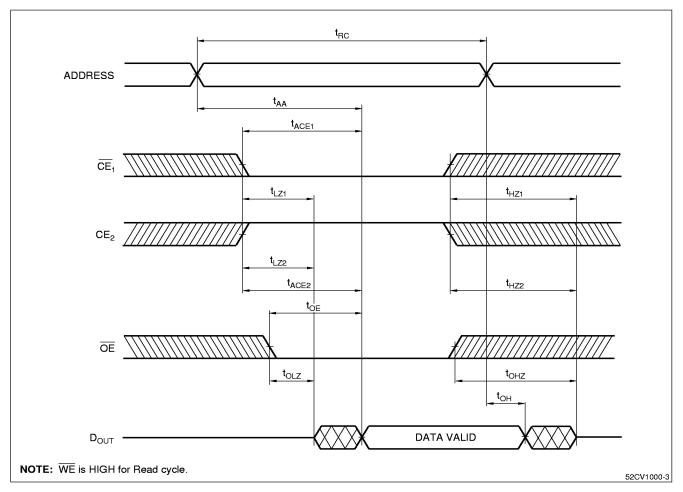

# READ CYCLE ( $T_A = -25^{\circ}C$ to $+85^{\circ}C$ , $V_{CC} = 2.7$ V to 3.6 V)

| PARAMETER                                        | SYMBOL            | MIN. | MAX. | UNIT | NOTE |

|--------------------------------------------------|-------------------|------|------|------|------|

| Read cycle time                                  | t <sub>RC</sub>   | 85   |      | ns   |      |

| Address access time                              | t <sub>AA</sub>   |      | 85   | ns   |      |

| CE <sub>1</sub> access time                      | t <sub>ACE1</sub> |      | 85   | ns   |      |

| CE <sub>2</sub> access time                      | t <sub>ACE2</sub> |      | 85   | ns   |      |

| Output enable to output valid                    | toE               |      | 45   | ns   |      |

| Output hold from address change                  | ton               | 10   |      | ns   |      |

| CE <sub>1</sub> Low to output active             | t <sub>LZ1</sub>  | 10   |      | ns   | 1    |

| CE <sub>2</sub> High to output active            | t <sub>LZ2</sub>  | 10   | _    | ns   | 1    |

| OE Low to output active                          | t <sub>OLZ</sub>  | 0    | _    | ns   | 1    |

| CE <sub>1</sub> High to output in High impedance | t <sub>HZ1</sub>  | 0    | 30   | ns   | 1    |

| CE <sub>2</sub> Low to output in High impedance  | t <sub>HZ2</sub>  | 0    | 30   | ns   | 1    |

| OE High to output in High impedance              | tonz              | 0    | 30   | ns   | 1    |

#### NOTE

# WRITE CYCLE $(T_A = -25^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 2.7 \text{ V to } 3.6 \text{ V})$

| PARAMETER                            | SYMBOL           | MIN. | MAX. | UNIT | NOTE |

|--------------------------------------|------------------|------|------|------|------|

| Write cycle time                     | twc              | 85   |      | ns   |      |

| CE <sub>1</sub> Low to end of write  | tcw1             | 75   |      | ns   | _    |

| CE <sub>2</sub> High to end of write | t <sub>CW2</sub> | 75   |      | ns   | _    |

| Address valid to end of write        | taw              | 70   | _    | ns   | _    |

| Address setup time                   | tas              | 0    |      | ns   | _    |

| Write pulse width                    | t <sub>WP</sub>  | 60   |      | ns   | _    |

| Write recovery time                  | t <sub>WR</sub>  | 0    |      | ns   | _    |

| Input data setup time                | t <sub>DW</sub>  | 35   |      | ns   | _    |

| Input data hold time                 | t <sub>DH</sub>  | 0    |      | ns   | _    |

| WE High to output active             | tow              | 0    |      | ns   | 1    |

| WE Low to output in High impedance   | t <sub>WZ</sub>  | 0    | 30   | ns   | 1    |

| OE High to output in High impedance  | tonz             | 0    | 30   | ns   | 1    |

## NOTE

<sup>1.</sup> Including scope and jig capacitance.

Active output to High impedance and High impedance to output active tests specified for a ±200 mV transition from steady state levels into the test load.

Active output to High impedance and High impedance to output active tests specified for a ±200 mV transition from steady state levels into the test load.

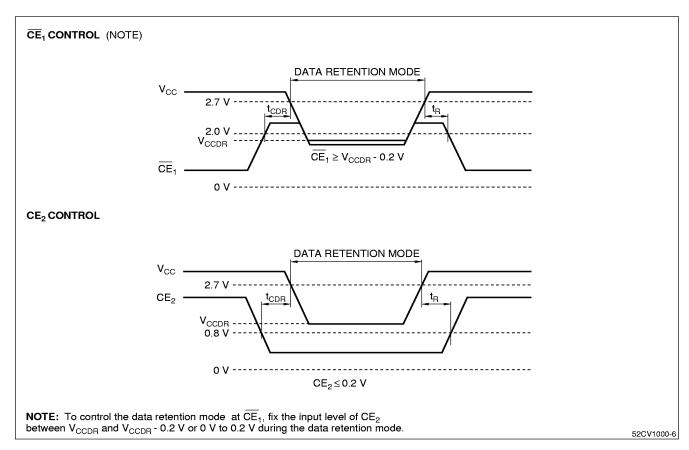

# DATA RETENTION CHARACTERISTICS ( $T_A = 0$ °C to +70°C)

| PARAMETER                     | SYMBOL         | CONDITIONS                                                                                          |                       | MIN.                  | TYP | MAX. | UNIT | NOTE |

|-------------------------------|----------------|-----------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----|------|------|------|

| Data retention supply voltage | Vccdr          | $\frac{\text{CE}_2 \leq 0.2 \text{ V or}}{\text{CE}_1 \geq \text{V}_{\text{CCDR}} - 0.2 \text{ V}}$ |                       | 2.0                   |     | 3.6  | V    | 1    |

| Data retantion                |                | $V_{CCDR} = 3.0 \text{ V}$ $CE_2 \le 0.2 \text{ V or}$ $CE_1 \ge V_{CCDR} - 0.2 \text{ V}$          | T <sub>A</sub> = 25°C |                       | 0.5 | 1.0  | μA   | 1    |

| Data retention supply current | ICCDR          |                                                                                                     |                       | T <sub>A</sub> = 40°C |     |      | 3.0  | μ    |

|                               |                |                                                                                                     |                       |                       |     | 25   | μА   | 1    |

| Chip enable setup time        | tcdr           | _                                                                                                   | _                     |                       |     |      | ns   |      |

| Chip enable<br>hold time      | t <sub>R</sub> | _                                                                                                   |                       | t <sub>RC</sub>       |     |      | ns   | 3    |

#### NOTES:

- 1.  $CE_2 \ge V_{CCDR} 0.2 \text{ V or } CE_2 \le 0.2 \text{ V}$

- 2. Typical values at  $T_A = 25$ °C

- 3. Read cycle

# PIN CAPACITANCE ( $T_A = 25^{\circ}C$ , f = 1 MHz)

| PARAMETER         | SYMBOL           | CONDITIONS             | MIN. | TYP. | MAX. | UNIT | NOTE |

|-------------------|------------------|------------------------|------|------|------|------|------|

| Input capacitance | C <sub>IN</sub>  | V <sub>IN</sub> = 0 V  | _    | _    | 6    | pF   | 1    |

| I/O capacitance   | C <sub>I/O</sub> | V <sub>I/O</sub> = 0 V |      |      | 8    | pF   | 1    |

#### NOTE:

1. This parameter is sampled and not production tested.

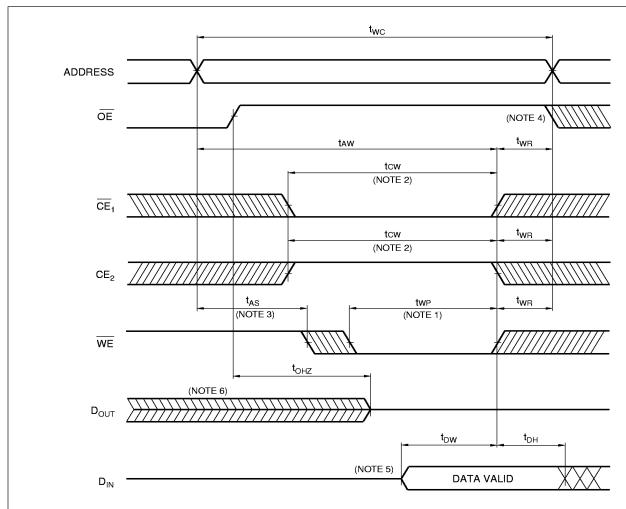

Figure 3. Read Cycle

#### NOTES:

- A write occurs during the overlap of a LOW CE<sub>1</sub>, a HIGH CE<sub>2</sub> and a LOW WE.

A write begins at the latest transition among CE<sub>1</sub> going LOW, CE<sub>2</sub> going HIGH and WE going LOW. A write ends at the earliest transition among CE<sub>1</sub> going HIGH. CE<sub>2</sub> going LOW and WE going HIGH. t<sub>WP</sub> is measured from the beginning of write to the end of write.

- t<sub>CW</sub> is measured from the later of CE<sub>1</sub> going LOW or CE<sub>2</sub> going HIGH to the end of write.

- 3.  $t_{\rm AS}$  is measured from the address valid to the beginning of write.

- t<sub>WR</sub> is measured from the end of write to the address change. t<sub>WR1</sub> applies in case a write ends at CE<sub>1</sub> or WE going HIGH. t<sub>WR2</sub> applies in case a write ends at CE<sub>2</sub> going LOW.

- During this period, I/O pins are in the output state, therefore the input signals of opposite phase to the outputs must not be applied.

- If CE<sub>1</sub> goes LOW simultaneously with WE going LOW or after WE going LOW, the outputs remain in high impedance state.

- 7. If  $\overline{\text{CE}}_1$  goes HIGH simulaneously with  $\overline{\text{WE}}$  going HIGH or before  $\overline{\text{WE}}$  going HIGH, the outputs remain in high impedance state.

52CV1000-4

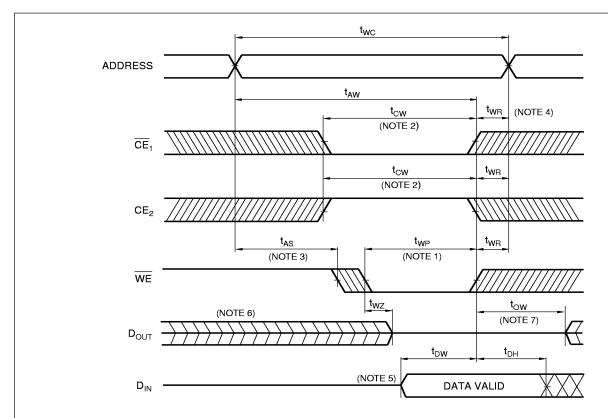

Figure 4. Write Cycle (OE Controlled)

### NOTES:

- A write occurs during the overlap of a LOW CE<sub>1</sub>, a HIGH CE<sub>2</sub> and a LOW WE.

A write begins at the latest transition among CE<sub>1</sub> going LOW, CE<sub>2</sub> going HIGH and WE going LOW. A write ends at the earliest transition among CE<sub>1</sub> going HIGH. CE<sub>2</sub> going LOW and WE going HIGH. t<sub>WP</sub> is measured from the beginning of write to the end of write.

- 2.  $t_{CW}$  is measured from the later of  $\overline{CE}_1$  going LOW or  $CE_2$  going HIGH to the end of write.

- 3.  $\,t_{AS}$  is measured from the address valid to the beginning of write.

- t<sub>WR</sub> is measured from the end of write to the address change. t<sub>WR1</sub> applies in case a write ends at CE<sub>1</sub> or WE going HIGH. t<sub>WR2</sub> applies in case a write ends at CE<sub>2</sub> going LOW.

- 5. During this period, I/O pins are in the output state, therefore the input signals of opposite phase to the outputs must not be applied.

- If CE<sub>1</sub> goes LOW simultaneously with WE going LOW or after WE going LOW, the outputs remain in high impedance state.

- 7. If  $\overline{\text{CE}}_1$  goes HIGH simulaneously with  $\overline{\text{WE}}$  going HIGH or before  $\overline{\text{WE}}$  going HIGH, the outputs remain in high impedance state.

52CV1000-5

Figure 5. Write Cycle (OE Low Fixed)

Figure 6. Data Retention (CE<sub>1</sub> Controlled)

### **PACKAGE DIAGRAM**

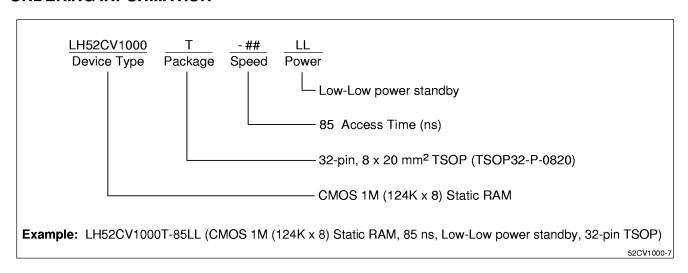

## ORDERING INFORMATION