# GX4404 Wideband, Monolithic 4x1 Video Multiplexer

DATA SHEET

#### **FEATURES**

- · low differential phase and gain

- wide bandwidth, 200 MHz at -3 dB

- · small switching transient

- ±4.5 to ±5.5 volts supplies

- · individual TALLY outputs

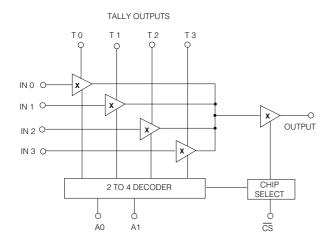

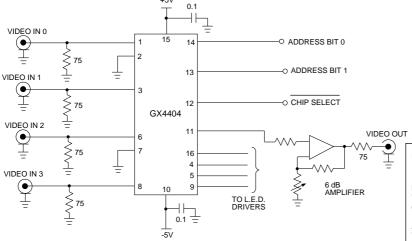

#### **FUNCTIONAL BLOCK DIAGRAM**

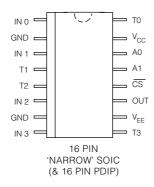

#### PIN CONNECTIONS

## **AVAILABLE PACKAGING**

16 pin PDIP 16 pin SOIC Tape 16 pin (N) SOIC

## **CIRCUIT DESCRIPTION**

The GX4404 is a wideband video multiplexer implemented in bipolar technology. This device is characterized by excellent differential phase and gain in the enabled state, very high off-isolation in the disabled state. Fully buffered unilateral signal paths ensure negligible output to input feedback, while delivering minimal output switching transients through make-before-break switching.

For use in NxM routing matrices, these devices feature a very high, nearly constant input impedance coupled with high output impedance in the disabled state. This allows multiple devices to be paralleled at the inputs and outputs without additional circuitry.

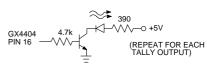

The chip is disabled when a logic HIGH is applied to the CS control pin. In this case, regardless of the ADDRESS data, the output of the device assumes a high impedance state. Individual PNP to  $V_{\rm CC}$  TALLY outputs provide positive indication of crosspoint selection.

All logic inputs are TTL and 5V CMOS compatible. Supply voltages can be between  $\pm 4.5$  to  $\pm 5.5$  volts.

## **APPLICATIONS**

- HDTV

- Very high quality video switching

- Very high density video switching

- Computer graphics

- PCM / data routing matrices

## TRUTH TABLE

|    |    |    |        | TALLY O/Ps |    |    |    |  |

|----|----|----|--------|------------|----|----|----|--|

| cs | A1 | A0 | OUT    | T0         | T1 | T2 | Т3 |  |

| 0  | 0  | 0  | IN 0   | ON         | *  | *  | *  |  |

| 0  | 0  | 1  | IN 1   | *          | ON | *  | *  |  |

| 0  | 1  | 0  | IN 2   | *          | *  | ON | *  |  |

| 0  | 1  | 1  | IN 3   | *          | *  | *  | ON |  |

| 1  | Х  | Х  | HI - Z | *          | *  | *  | *  |  |

X = DON'T CARE \*= OFF (high impedance)

## ORDERING INFORMATION

| Part Number | Package Type        | Temperature Range      |  |  |  |

|-------------|---------------------|------------------------|--|--|--|

| GX4404-CDC  | 16 pin PDIP         | 0 to 70 <sup>0</sup> C |  |  |  |

| GX4404-CKD  | 16 pin (N) SOIC     | 0 to 70 <sup>0</sup> C |  |  |  |

| GX4404-CTD  | Tape16 pin (N) SOIC | 0 to 70 <sup>0</sup> C |  |  |  |

Document No. 520 - 43 - 1

## **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                            | VALUE                                                        |

|--------------------------------------|--------------------------------------------------------------|

| Supply Voltage                       | ±7.5V                                                        |

| Operating Temperature Range          | $0^{\circ}\text{C} \le \text{T}_{A} \le 70^{\circ}\text{ C}$ |

| Storage Temperature Range            | -65°C ≤ T <sub>S</sub> ≤ 150° C                              |

| Lead Temperature (Soldering, 10 Sec) | 260° C                                                       |

| PARAMETER            | VALUE                                    |

|----------------------|------------------------------------------|

| Analog Input Voltage | $(V_{EE} -1.4) < V_{A} < (V_{CC} +0.3)V$ |

| Logic Input Voltage  | $-0.5V \le V_{L} \le +5.5V$              |

| TALLY Output Current | 2 mA                                     |

## **ELECTRICAL CHARACTERISTICS** $(V_S = \pm 5V DC, 0^{\circ}C \le T_A \le 70^{\circ}C, R_L = 10k\Omega, C_L = 30 pF, unless otherwise shown.)$

|              | PARAMETER                   | SYMBOL             | CONDITIONS                                                              |                             | MIN   | TYP   | MAX   | UNITS |

|--------------|-----------------------------|--------------------|-------------------------------------------------------------------------|-----------------------------|-------|-------|-------|-------|

|              | Supply Voltage              | ±V <sub>S</sub>    | Operating Range                                                         |                             | ±4.5  | -     | ±5.5  | V     |

| DC<br>SUPPLY |                             | I <sup>+</sup>     | <u>CS</u> = 0                                                           | -                           | 30    | 37    | mA    |       |

|              | Supply Current              | I-                 | <u>CS</u> = 0                                                           | -                           | 30    | 37    | mA    |       |

|              |                             | I <sup>+</sup>     | <u>CS</u> = 1                                                           |                             | -     | 220   | 300   | μΑ    |

|              |                             | I-                 | CS = 1                                                                  |                             | -     | 220   | 380   | μА    |

| STATIC       | Analog Output Voltage Swing | V <sub>OUT</sub>   | Extremes before clipping occurs                                         |                             | -2.4  | -     | 2.6   | V     |

|              | Analog Input Bias Current   | I <sub>BIAS</sub>  |                                                                         |                             | -     | 12    | -     | μА    |

|              | Output Offset Voltage       | V <sub>OS</sub>    | T <sub>A</sub> = 25°C                                                   |                             | -13   | -4    | 7     | mV    |

|              | Output Offset Voltage Drift | $\Delta V_{OS}$    |                                                                         |                             | -     | 35    | 80    | μV/°C |

| LOGIC        | Chip Enable Time            | t <sub>on</sub>    | Enable input to appearance of signal                                    |                             | -     | 200   | 400   | ns    |

|              | Chip Disable Time           | t <sub>OFF</sub>   | Enable input to disappearance of signal at output.                      |                             | 0.6   | 1.2   | -     | μs    |

|              | Logic Input Thresholds      | V <sub>IH</sub>    | 1                                                                       |                             | 2.0   | -     | -     | V     |

|              |                             | V <sub>IL</sub>    | 0                                                                       |                             | -     | -     | 0.8   | V     |

|              | Logic Input Current         | I                  |                                                                         |                             | -     | -     | 4     | μΑ    |

|              | TALLY Outputs               |                    | $(V_{CC} - V_{TALLY})$ $I_{TALLY} = 1mA$                                |                             | 70    | 150   | 300   | mV    |

|              | Insertion Loss              | I.L.               | 1V p-p sine or sq. wave at 100 kHz                                      |                             | 0.030 | 0.040 | 0.055 | dB    |

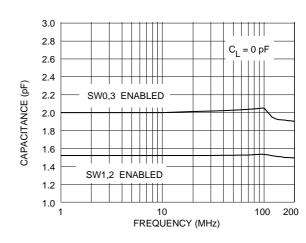

|              | Bandwidth (-3dB)            | B.W.               | small signal C <sub>L</sub> = 0 pF                                      |                             | -     | 300   | -     | MHz   |

| DYNAMIC      | Input Resistance            | R <sub>IN</sub>    | CS = 0, crosspoint on                                                   |                             | 0.5   | -     | -     | ΜΩ    |

| DINAMIC      | Input Capacitance           | C <sub>IN</sub>    | $\overline{\text{CS}}$ = 0, crosspoint on                               |                             | -     | 1.5   | -     | pF    |

|              | Output Resistance           | R <sub>OUT</sub>   | CS = 0, crosspoint on                                                   |                             | -     | 4     | -     | Ω     |

|              | Output Capacitance          | C <sub>OUT</sub>   | CS = 1, chip disabled                                                   |                             | -     | 3.7   | -     | pF    |

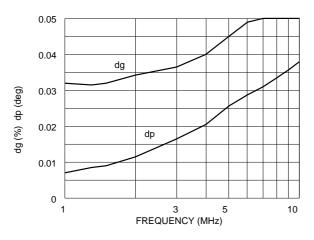

|              | Differential Gain           | dg                 | $f = 3.58 \text{ MHz}, V_{IN} = 40 \text{ IRE}$                         |                             | -     | -     | 0.05  | %     |

|              | Differential Phase          | dp                 | $f = 3.58 \text{ MHz}, V_{IN} = 40 \text{ IRE}$                         |                             | -     | -     | 0.04  | deg   |

|              | All Hostile Crosstalk       | XTLK <sub>AH</sub> | 1Vp-p on 3 inputs 4 th input has $10\Omega$ resistor to gnd $f$ =30 MHz |                             | -     | 70    | -     | dB    |

|              | Chip Disabled Crosstalk     | XTLK <sub>CD</sub> | Enabled device on O/P f=100 MHz                                         |                             | -     | 80    | -     | dB    |

|              | Slew Rate                   | +SR                | V <sub>IN</sub> = 3V p-p (C <sub>L</sub> = 0 pF)                        |                             | 250   | -     | -     | V/µs  |

|              |                             | -SR                | $V_{IN} = 3V p-p (C_L = 0 pF)$                                          |                             | 250   | -     | -     | V/µs  |

|              | Gain Spread at 30 MHz       | $\Delta A_V$       |                                                                         |                             | -     | -     | ±0.05 | dB    |

|              | Crosspoint Scatter          |                    | $R_S = 75\Omega$                                                        | T <sub>A</sub> = 25°C       | -     | -     | ±0.15 | deg   |

|              |                             |                    | f = 3.58  MHz                                                           | 0°C < T <sub>A</sub> < 70°C | -     | -     | ±0.25 | deg   |

520 - 43 - 1

## **TYPICAL PERFORMANCE CURVES**

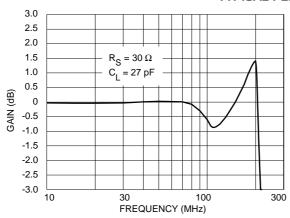

Fig. 1 Flattened Frequency Response

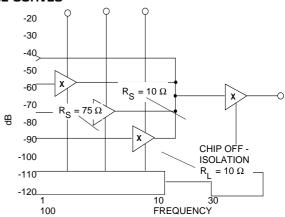

Fig. 2 All Hostile Crosstalk & Isolation

Fig. 3 Differential Gain & Phase

+5V

Fig. 4 Input Capacitance

All resistors in ohms, all capacitors in  $\mu F$  unless otherwise stated Fig. 5 Test Circuit

## **CAUTION**

FLECTROSTATIC SENSITIVE DEVICES DO NOT OPEN PACKAGES OR HANDLE EXCEPT AT A STATIC-FREE WORKSTATION

L.E.D. DRIVER

#### DOCUMENT **IDENTIFICATION**

#### PRODUCT PROPOSAL

This data has been compiled for market investigation purposes only, and does not constitute an offer for sale.

## ADVANCE INFORMATION NOTE

This product is in development phase and specifications are subject to change without notice. Gennum reserves the right to remove the product at any time. Listing the product does not constitute an offer for sale.

#### PRELIMINARY DATA SHEET

The product is in a preproduction phase and specifications are subject to change without notice.

## DATA SHEET

The product is in production. Gennum reserves the right to make changes at any time to improve reliability, function or design, in order to provide the best product possible.