# Military **28C256**

### 256K (32K x 8) CMOS Electrically Erasable PROM

#### **FEATURES**

- · Fast read access time-90, 120, 150 ns maximum

- · CMOS Technology for low power dissipation

- ---80 mA active

- -350 μA standby

- · Fast byte-write time-3 ms or 10 ms

- Fast page-write-time—3 ms or 10 ms

- · Data retention >10 years

- High endurance 10<sup>4</sup> erase/write cycles

- · Automatic write operation

- —Internal control timer

- -Auto-clear before write operation

- -On-chip address and data latches

- Data polling

- · Chip clear operation

- · Enhanced data protection

- —VCC detector

- -Power-up timer

- · Electronic signature for device identification

- · 5-volt-only operation

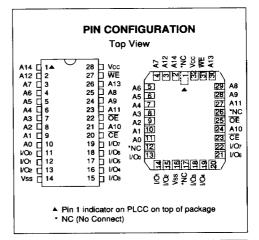

- · Organized 32K x 8 JEDEC standard pinout

- -28-pin Dual In-line Package (DIP)

- -32-pin Leadless Chip Carrier (LCC)

- · Extended Temperature Range:

- -Military (B): -55°C to +125°C

#### DESCRIPTION

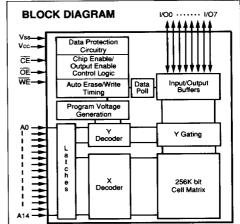

The Microchip Technology Inc. 28C256 high speed, low power page mode 32,768 x 8 bit non-volatile Electrically Erasable and Programmable Read Only Memory with popular, easy to use features. The device is manufactured with Microchip's advanced and reliable non-volatile CMOS technology.

The 28C256 is accessed like a static RAM for the read or write cycles without the need of external components. During a "write" the address and 1 to 64 bytes of data are latched internally, freeing the microprocessor address and data bus for other operations. Following the initiation of a write cycle, the device will go to a busy state and automatically clear the addressed memory cells and write the latched data using an internal control timer.

The completion of a write cycle is detected by either DATA polling of output I/O7 or TOGGLE BIT of I/O6.

Data protection is achieved with Vcc sensing, an additional 5 ms (typical) delay after power on, and a software write protection scheme. Furthermore, holding  $\overline{OE}$  Low,  $\overline{CE}$  high or  $\overline{WE}$  high inhibits writing to the device.

The 28C256 also provides two useful software controlled features; Software Chip Clear and Software Write Protection. The feature of Software Chip Clear allows

users to erase the whole memory with 5 V only power supply. Software Write Protection sets a non-volatile fuse to protect the memory from inadvertent writes.

The 28C256 operates from a single 5 V supply and is packaged in standard JEDEC-approved packages. All necessary programming voltages are internally generated and timed.

The advanced CMOS technology offers fast access times of 90 ns (28C256-90) at low power dissipation of 80 mA. When the chip is deselected, the standby current is less than 350  $\mu$ A.

© 1990 Microchip Technology Inc.

DS60025B-1

| PIN FUNCTION TABLE                               |                                                                                |  |  |

|--------------------------------------------------|--------------------------------------------------------------------------------|--|--|

| Name                                             | Function                                                                       |  |  |

| A0 - A14<br>CE<br>OE<br>WE<br>I/O0 - I/O7<br>Vcc | Address Inputs Chip Enable Output Enable Write Enable Data Inputs/Outputs +5 V |  |  |

| Vss<br>NC                                        | Ground<br>No Connect                                                           |  |  |

# ELECTRICAL CHARACTERISTICS Maximum Ratings\*

Vcc and input voltages w.r.t. Vss.....-0.3 V to + 6.25 V

Voltage on OE w.r.t. Vss.....-0.3 V to + 15 V

Voltage on A9 w.r.t. Vss....-0.3 V to +15 V

Output voltage w.r.t. ....-0.6 V +Vcc +0.6 V

Ambient temp. with power supplies ....-55°C to 125°C

Storage temperature ....-65°C to 150°C

\*Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## READ/WRITE OPERATION DC Characteristics

$VCC = +5 V \pm 10\%$

Military (B): TAMB = -55°C to +125°C

| 20 0114140101101100           | Military (b). 17MB = -00 0 to +125 0 |         |      |           |       |                             |

|-------------------------------|--------------------------------------|---------|------|-----------|-------|-----------------------------|

| Parameter                     | Status                               | Symbol  | Min  | Max       | Units | Conditions                  |

| Input Voltages                | Logic "1"                            | ViH     | 2.0  | Vcc + 0.3 | v     |                             |

|                               | Logic "0"                            | VIL     | -0.1 | 0.8       | V     |                             |

| Input Leakage                 |                                      | ILI     | -10  | 10        | μΑ    | VIN = 0.1 V to VCC + 1      |

| Input Capacitance             |                                      | Cı      |      | 10        | pF    | VIN = 0 V; TAMB = 25°C;     |

|                               |                                      | l       |      |           |       | f = 1 MHz; Vcc = 5.0 V      |

| Output Voltages               | Logic "1"                            | Vон     | 2.4  |           | ٧     | IOH = -4 mA                 |

|                               | Logic "0"                            | Vol     |      | 0.45      | V     | IOL = 6 mA                  |

| Output Leakage                |                                      | lLO     | -10  | 10        | μА    | Vout = 0.1 V to Vcc         |

| Output Capacitance            |                                      | Co      |      | 10        | рF    | VIN = 0 V; TAMB = 25°C;     |

|                               |                                      |         |      |           |       | f = 1 MHz, Vcc = 5.0 V      |

| Power Supply Current, Active  | TTL Input                            | ICC1    |      | 80        | mA    | f = 1TAVAV (min)            |

|                               |                                      |         |      |           |       | Vcc = 5.5 V; OE = CE = VIL, |

|                               |                                      |         |      |           |       | VIH = 2.0 V to VCC          |

| Power Supply Current, Standby | TTL Input                            | ICCa    |      | 3         | mA    | CE = VIH                    |

|                               | CMOS Input                           | ICC(s)3 |      | 350       | μΑ    | CE = Vcc ± 0.3 V            |

DS60025B-2

© 1990 Microchip Technology Inc.

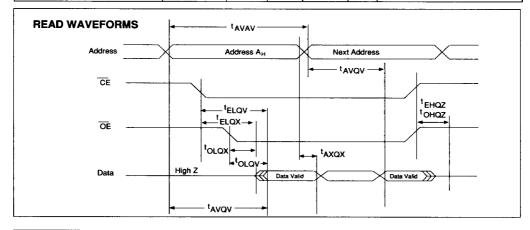

READ OPERATION AC Characteristics

AC Testing Waveform: Output Load:  $V_{IH} = 2.4 \text{ V}$ ;  $V_{IL} = 0.45 \text{ V}$ ;  $V_{OH} = 2.0 \text{ V}$ ;  $V_{OL} = 0.8 \text{ V}$

1 TTL Load + 100 pF ≤ 10 ns

Input Rise and Fall Times: ≤ 10 ns

Ambient Temperature: Military (B):

Measurement Reference Levels:

TAMB = -55°C to 125°C Inputs: 1 V and 2 V

Inputs: 1 V and 2 V Outputs: 0.8 V and 2 V

|                                     | 28C256 -15 |     | 28C256 -12 |     | 28C256 -90 |     |     |       |

|-------------------------------------|------------|-----|------------|-----|------------|-----|-----|-------|

| Parameter                           | Symbol     | Min | Max        | Min | Max        | Min | Max | Units |

| Read Cycle Time                     | TAVAV      | 150 | -          | 120 | -          | 90  | -   | ns    |

| Address Access Time                 | TAVAV (1)  | -   | 150        | -   | 120        | -   | 90  | ns    |

| Chip Enable Access Time             | TELAV (2)  | -   | 150        | -   | 120        | -   | 90  | ns    |

| Output Enable Access Time           | TOLAV      | -   | 80         | •   | 50         | -   | 40  | ns    |

| CE Enable to output in Low Z        | TELAX      | 10  | -          | 10  | -          | 10  | -   | ns    |

| OE Enable to output in Low Z        | TOLAX      |     |            |     |            |     |     |       |

| CE Disable to output in High Z      | TEHQZ      | -   | 60         | -   | 50         | -   | 40  | -     |

| OE Enable to output in High Z       | TOHAZ      |     |            |     |            |     |     |       |

| Output Hold from Address<br>Changes | TAXAX      | 0   | -          | 0   | -          | 0   | -   | ı     |

Notes:(1) OE can be delayed up to (TAVAV - TOLAV) after the address the valid without impact on TAVQV.

(2)  $\overline{\text{OE}}$  can be delayed up to (TELAV - TOLAV) after the falling edge of  $\overline{\text{CE}}$  without impact on TELAV.

#### **DEVICE OPERATION**

The Microchip Technology Inc. 28C256 has five basic modes of operation—read, standby, page or byte write, write inhibit and chip clear —as outlined in the following table.

| Operation      | CE  | ŌĒ     | WE  | I/O         |

|----------------|-----|--------|-----|-------------|

| Read           | VIL | ViL    | VIH | Douт        |

| Standby        | Vıн | X(1)   | Х   | High Z      |

| Write (2)      |     |        |     | -           |

| - Byte/Page    | (4) | Vін    | Q   | Din         |

| Write Inhibit  | X   | VIL    | X   | High Z/Dout |

| Write Inhibit  | Vін | X      | X   | High Z      |

| Write Inhibit  | х   | Х      | VIH | High Z/Dout |

| Chip Clear (3) | VIL | VH (5) | 0   | High Z      |

Notes: (1) X = any TTL level

- (2) Refer to "Programming Waveforms"

- (3) Refer to "Chip Clear Waveforms"

- (4) \( \omega \) = Low going pulse

- (5)  $VH = 12V \pm 5\%$

#### **Read Mode**

The 28C256 has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip enable ( $\overline{CE}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{OE}$ ) is the output control. The outputs are put in a high impedance state whenever  $\overline{CE}$  or  $\overline{OE}$  is high. This dual line control gives designers increased flexibility in preventing bus contention.

#### Standby Mode

The 28C256 is placed in the standby mode by applying a high signal to the  $\overline{CE}$  input. When in the standby mode, the outputs are in a high impedance state, independent of the  $\overline{OE}$  input.

#### **Hardware Data Protection**

In order to ensure data integrity, especially during critical power-up and power-down transitions. The following enhanced data protection circuits are incorportated:

First, an internal VCC detect (3.8 volts typical) will inhibit the initiation of non-volatile programming operation when VCC is less than the VCC detect circuit trip. In addition, upon power-up an internal timer (5ms typical) will inhibit the recognition of any program operation. During this period, all normal read functions will be operational. After both the VCC detection and the internal timer have elapsed, normal programming operation can be performed.

Second, there is a WE filtering circuit that prevents WE pulses of less than 20ns duration from initiating a write cycle.

Third, holding WE or CE high or OE low, inhibits a write cycle during power-on and power-off (VCC).

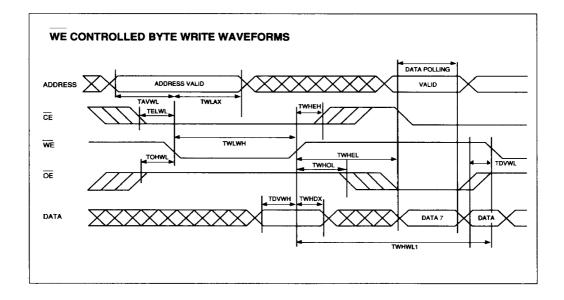

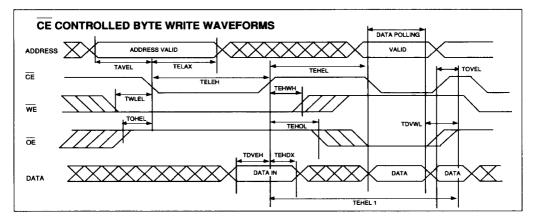

**WRITE OPERATION AC Characteristics**

AC Testing Waveform:

$V_{IH} = 2.4 \text{ V}$ ;  $V_{IL} = 0.45 \text{ V}$ ;  $V_{OH} = 2.0 \text{ V}$ ;  $V_{OL} = 0.8 \text{ V}$ 1 TTL Load + 100 pF

Output Load:

≤10 ns

Input Rise and Fall Times: Ambient Temperature:

Military (B): TAMB = -55°C to 125°C

Measurement Reference Levels:

Inputs: 1 V and 2 V Outputs: 0.8 V and 2 V

| Parameter            | Symbol        | Min | Max   | Units | Remarks         |

|----------------------|---------------|-----|-------|-------|-----------------|

| Address Set-up Time  | TAVWL TAVEL   | 0   |       | ns    | -               |

| Data Set-up Time     | TDVWH TDVEH   | 50  | -     | ns    | -               |

| Address Hold Time    | TWLAX TELAX   | 50  | -     | ns    | -               |

| Data Hold Time       | TWHDX TEHDX   | 0   | -     | ns    | =               |

| Write Pulse Width    | TWLWH TELEH   | 150 | -     | ns    | -               |

| OE Set-up Time       | TOHWL TOHEL   | 0   | -     | ns    | -               |

| OE Hold Time         | TWHOL TEHOL   | 0   | -     | ns    | -               |

| Time to Data Polling | TWHEL TEHEL   | -   | 0     | ns    | -               |

| Delay to Next Write  | TOVWL TOVEL   | 0   | -     | ns    | -               |

| Write Cycle Time     | TWHWL1 TEHEL1 | -   | 3, 10 | ms    | 1, 3 ms Typical |

| Byte A Cycle         | TWHWL2 TEHEL2 | 0.2 | 149   | μs    | For page mode   |

| Write Set-up Time    | TELWL TWLEL   | 0   | -     | ns    | -               |

| Write Hold Time      | TWHEH TEHWH   | 0   | -     | ns    | -               |

DS60025B-4

© 1990 Microchip Technology Inc.

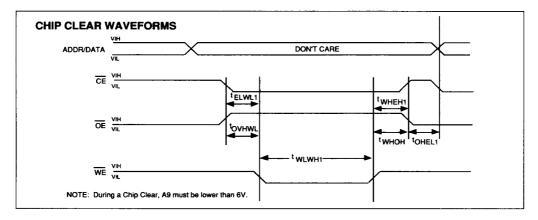

| CHIP CLEAR OPERATION          | AC Testing Waveform:<br>Output Load:<br>Ambient Temperature: |     | VIH = 2.4 V; VIL = 0.45 V<br>1 TTL Load + 100 pF<br>Military (B): TAMB = -55°C to 125 |       |         |

|-------------------------------|--------------------------------------------------------------|-----|---------------------------------------------------------------------------------------|-------|---------|

| Parameter                     | Symbol                                                       | Min | Max                                                                                   | Units | Remarks |

| CE Set-up Time                | TELWL1                                                       | 5   | -                                                                                     | μs    |         |

| OE Set-up Time                | TOVHWL                                                       | 5   | -                                                                                     | μs    | -       |

| CE Hold Time                  | TWHEH1                                                       | 5   | -                                                                                     | μs    | -       |

| OE Hold Time                  | TWHOH                                                        | 5   | -                                                                                     | μs    | -       |

| WE Pulse Width for Chip Erase | TWLWH1                                                       | 10  | -                                                                                     | ms    | -       |

| Time to Next Operation        | TOHEL1                                                       | 5   | -                                                                                     | μs    | -       |

| OE High Voltage               | VH                                                           | 12  | 13                                                                                    | V     | -       |

© 1990 Microchip Technology Inc.

DS60025B-5

| Mode            | ĈĒ  | ŌĒ  | WE  | A9      | Vcc | I/Ot    |

|-----------------|-----|-----|-----|---------|-----|---------|

| Extra Row Read  | VIL | VIL | ViH | A9 = VH | Vcc | Data Ou |

| Extra Row Write | Q)  | ViH | Q   | A9 = VH | Vcc | Data In |

#### **Write Mode**

The 28C256 has a write cycle similar to that of a Static RAM. The write cycle is completely self-timed and initiated by a low going pulse on the  $\overline{WE}$  pin. On the falling edge of  $\overline{WE}$ , the address information is latched. On the rising edge, the data and the control pins ( $\overline{CE}$  and  $\overline{OE}$ ) are latched.

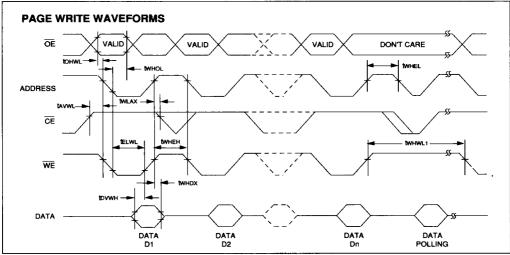

#### Page Write

The page write feature of the 28C256 allows the entire memory to be written in 2 seconds. Page write allows one to sixty-four bytes of data to be written into 28C256 in a single internal programming cycle. Internally, there are 64 byte registers (one page) addressed by A0 through A5. Data are loaded into corresponding registers during the load period and all data will be written into the specified one page of memory at once. The rules for page write are given below:

- A.The page mode is initiated by any write operation and the following bytes can be loaded in the same way.

- B.Each successive byte load cycle, started by the falling edge of write control signals (i.e. WE or CE, whichever occurs last), must begin within 149μ seconds from the rising edge of the preceding write control signal. Otherwise, the load period ends and the internal programming cycle starts.

- C. If page address (A6 through A14) does not stay

- the same through the entire load cycle, all data loaded will be written into the page address of the last data.

- D. If the same byte location (addressed by A0 through A5) is loaded more than once, the latest value will be written into the memory.

- E.There is no page write window limitation as long as rule B is followed.

- F. In order to avoid unnecessary cycling of unused memory cells, only those bytes actually loaded into the page buffer will be written to memory.

#### **Write Operation Status Bits**

The 28C256 provides the user three write operation status bits. I/O7 is used for  $\overline{DATA}$  polling and I/O6 is used as Toggle Bit, and I/O5 is used for the Page-load timer.

#### Data Polling (I/07)

The 28C256 features DATA Polling to signal the completion of a byte write cycle. During a byte write or page write cycle, an attempted read of the last byte written results in the data complement of I/O7 (I/O0 to I/O4 are indeterminable). After completion of the write cycle, true data is available. DATA polling allows a simple read/compare operation to determine the status of the chip eliminating the need for external hardware.

DS60025B-6

© 1990 Microchip Technology Inc.

#### Togale Bit (I/O6)

The Toggle Bit is another method of determining the internal programming status. During the internal programming cycle I/O6 will toggle on each attempted read (i.e. ...0-1-0-1-0...). The first read value is "0". The toggling will cease after the completion of the internal programming cycle.

#### Page Load Timer (I/05)

During the write loading period and internal programming cycle, I/O5 will show the page-load timer status on read operation. "O" means it is still in the loading window. "I tells the user that the loading period has expired and the internal programming cycle has begun.

#### **Software Data Protection**

The 28C256 offers a software controlled data protection feature. Once the software data protection is employed, the 28C256 is automatically protected during power-up and power-down without the need for external circuits. The 28C256 is further protected from inadvertent and accidental writes in the power-on state. That is, a software algorithm must be issued prior to writing any data to the device. The first issuing of the software algorithm sets the write protection circuit, which is non-volatile and will remain set for the lifetime of the device unless the reset command is issued.

#### Write Protection Set/Reset Algorithms

Setting the software write protection mode requires a series of three bytes of data to be written consecutively into three specific addresses. The write sequence must conform to the page write timing specification. The Write Protection setting code listed below shows the sequence of setting the write protection mode. The third byte of the algorithm effectively opens the page write window to enable one page write immediately after the software algorithm. Once the internal programming

| WRITE PROTECTION SETTING CODE |         |  |  |  |

|-------------------------------|---------|--|--|--|

| Data                          | Address |  |  |  |

| AA                            | 5555    |  |  |  |

| 55                            | 2AAA    |  |  |  |

| AO                            | 5555    |  |  |  |

| WRITE PROTECTION RESETTING CODE |         |  |  |

|---------------------------------|---------|--|--|

| Data                            | Address |  |  |

| AA                              | 5555    |  |  |

| 55                              | 2AAA    |  |  |

| 80                              | 5555    |  |  |

| AA                              | 5555    |  |  |

| 55                              | 2AAA    |  |  |

| 20                              | 5555    |  |  |

cycle is completed, the 28C256 will automatically be returned to the write protection state. The write protection circuit can be reset by performing a series of six byte writes as shown in the listed Write Protection Resetting code. Page write is allowed immediately after the sixth write of the reset algorithm.

#### Software Chip Clear

The 28C256 also provides a software controlled chip clear feature. The whole memory can be cleared to state "1" by issuing a series of six-byte codes to specific addresses. The software chip clear algorithm is shown in the Software Chip clear code listing. The software chip clear functions only when write protection is reset. During the 10msec chip clear cycle, both Data Polling and Toggle Bit features can be used to detect the internal programming status.

| SOFTWARE | SOFTWARE CHIP CLEAR CODE |  |  |  |

|----------|--------------------------|--|--|--|

| Data     | Address                  |  |  |  |

| AA       | 5555                     |  |  |  |

| 55       | 2AAA                     |  |  |  |

| 80       | 5555                     |  |  |  |

| AA       | 5555                     |  |  |  |

| 55       | 2AAA                     |  |  |  |

| 10       | 5555                     |  |  |  |

#### **Device Identification**

An extra row of 64 bytes of EEPROM memory is available to the user for device identification. By raising A9 to  $12V \pm 0.5V$  and using address locations 7FCO to 7FFF, the additional bytes can be written to or read from in the same manner as the regular memory array.

#### Hardware Chip Clear

The 28C256 array can be cleaned to state "1" by raising OE to 12V and setting CE to VIL then bringing WE to VIL.

#### Retention Endurance

Read retention for data written into the 28C256 is greater than 10 years, with up to 10<sup>4</sup> write cycles. There is no limit to the number of times data may be read.

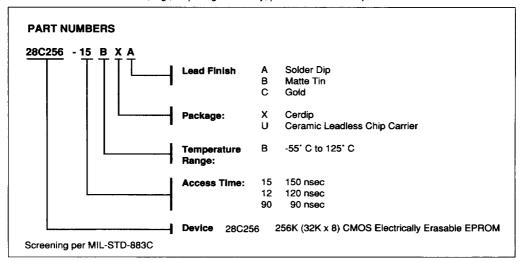

#### **ORDERING INFORMATION**

To order or to obtain information, e.g., on pricing or delivery, please use the listed part numbers.