# www.DataSheet4U.corAm2602/9602

# **Dual Retriggerable Resettable Monostable Multivibrator**

#### Distinctive Characteristics:

- Retriggerable 0 to 100% duty cycle.

- 50ns to ∞ output pulse width range.

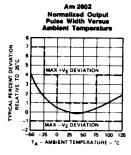

- Am2602 guaranteed pulse width change over temperature range.

- 100% reliability assurance testing including high temperature bake, temperature cycling, centrifuge and

- package hermeticity testing in compliance with MIL-STD-883.

- Mixing privileges for obtaining price discounts. Refer to price list.

- Electrically tested and optically inspected dice for the assemblers of hybrid products.

#### FUNCTIONAL DESCRIPTION

The Am2802 and Am9802 are dual DC-level sensitive resettable retriggerable monostable multivibrators which provide an output pulse whose duration and accuracy depend on external timing components.

Provision is made for triggering on the rising or falling edge of an input signal. All inputs are DC coupled making triggering independent of input rise and fail times. Each time the output from the OR trigger gate goes from a FALSE (LOW) to TRUE (HIGH) condition triggering occurs independent of the state of the monostable.

The direct clear facility allows a timing cycle to be terminated at any time during the cycle. A LOW signal on the  $\overline{C}_D$  input resets the monostable independent of other conditions.

The Am2602 is a selected Am9602 with a guaranteed pulse width change of less than 1% over the temperature range of  $0^{\circ}$ C to  $+75^{\circ}$ C.

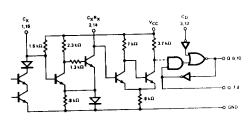

#### INTERNAL TIMING CIRCUITRY

#### nange Official Order Number Office Jack Office Con Jack Office Sto Halls ORDERING INFORMATION Temperature Package Part Number Type AM260259A Am2602 Molded DIP AM260259E Hermetic DIP Am2602 AM260251E Hermetic DIP Am2602 AM260251N Am2602 Hermetic Flat Pak AM2602XXD Dice Am2602 Molded DIP H6M960259X Am9602 Hermetic DIP U7B960259X C to +75°C Am9602 C to +125°C U7B960251X Am9602 Am9602 L14L960251X Hermetic Flat Pak 55°C to +125°C IJXX9602XXD Am9602 Dice Note: The dice supplied will contain units which meet both 6°C to +75°C and -55°C to +125°C temperature ranges.

|                                               | Operating            |                                                    |                                             | LIMITS $ T_A = MIN \qquad \qquad T_A = +25^{\circ}C $ Min Max Min Tyo Max |       |          |            | T <sub>A</sub> = MAX<br>Min Max U |      |               |      |

|-----------------------------------------------|----------------------|----------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------|-------|----------|------------|-----------------------------------|------|---------------|------|

| V <sub>OH</sub><br>Output HIGH                | Range<br>MIL or      | V <sub>CC</sub> = MIN., I <sub>OH</sub> = -0.96 mA |                                             | 2.40                                                                      | max   | Min 2.40 | Тур<br>3.6 | Mex                               | 2.40 | MAX           | Vo   |

| Voltage                                       | COM                  | ACC = WILLY TOH = -0.30 HIV                        |                                             | 2.40                                                                      |       | 2.42     | 0.0        |                                   | 2.40 |               | VOID |

| V <sub>OL</sub>                               | MIL                  | I <sub>OL</sub> = 8 x I <sub>IL</sub> MAX.         |                                             |                                                                           | 0.40  |          | 0.2        | 0.40                              |      | 0.40          | T.,  |

| Output LOW<br>Voltage                         | COM                  | I <sub>OL</sub> = 8 x I <sub>IL</sub> M            | AX.                                         |                                                                           | 0.45  |          | 0.2        | 0.45                              |      | 0.45          | Vol  |

| V <sub>IH</sub>                               | MIL                  |                                                    |                                             | 2.00                                                                      |       | 1.70     |            |                                   | 1.50 |               | Ī.,  |

| Input HIGH<br>Voltage                         | сом                  |                                                    |                                             | 1.90                                                                      |       | 1.80     |            |                                   | 1.60 |               | Vol  |

| V <sub>IL</sub><br>Input LOW<br>Voltage       | MIL                  |                                                    |                                             |                                                                           | 0.85  |          |            | 0.90                              |      | 0.85          | Ī.,  |

|                                               | COM                  |                                                    |                                             |                                                                           | 0.85  |          |            | 0.85                              |      | 0.85          | Voit |

|                                               | MIL                  | V <sub>IN</sub> = 0.40 V                           | $V_{CC} = MAX.$ $V_{CC} = MIN.$             | 1                                                                         | -1.60 |          | -1.10      | -1.60                             |      | -1.60         | mA   |

| i <sub>ii</sub><br>Input Load                 |                      | VIN — 0.40 V                                       | V <sub>CC</sub> = MIN.                      |                                                                           | -1.24 |          | -0.97      | -1.24                             |      | -1.2 <b>4</b> |      |

| Current                                       | сом                  | V <sub>IN</sub> = 0.45 V                           | V <sub>CC</sub> = MAX.                      |                                                                           | -1.60 |          | -1.00      | 1.60                              |      | 1.60          |      |

|                                               |                      |                                                    | V <sub>CC</sub> = MIN.                      |                                                                           | -1.41 |          | -0.90      | -1.41                             |      | -1.41         |      |

| I <sub>IH</sub><br>Reverse Input<br>Current   | MIL or<br>COM        | V <sub>CC</sub> = MAX.,V <sub>IN</sub> = 4.5 V     |                                             |                                                                           | 60    |          | 2          | 60                                |      | 60            | μΑ   |

| l <sub>sc</sub>                               | MIL                  | V <sub>CC</sub> = 5.0 V, V <sub>O</sub> = 1.0 V    |                                             |                                                                           |       | -8       |            | 25                                |      |               |      |

| Short Circuit<br>Current                      | COM                  | V <sub>CC</sub> = 5.0 V,                           | V <sub>O</sub> = 1.0 V                      |                                                                           |       | -8       | •          | -35                               |      |               | m/   |

| I <sub>PD</sub><br>Power<br>Supply<br>Current | 9602 MIL             |                                                    | GND Pins 5 and 11                           |                                                                           | 45    |          | 35         | 45                                |      | 45            |      |

|                                               | 9602 <b>COM</b>      | $R_{\chi} = 10 \text{ k}\Omega$                    |                                             | <u> </u>                                                                  | 52    |          | 35         | 50                                |      | 52            | mA   |

|                                               | 2602 COM<br>2602 MIL |                                                    | GND Pins 5 and 11<br>R <sub>v</sub> = 10 kΩ |                                                                           | 56    |          | 35         | 56                                |      | 56            |      |

|                                                    | 2602 MIL                                                     | H <sub>X</sub> = 10 ld. |                                                                                                    |      |               |      | <u> </u> |        |      | Ш.       |

|----------------------------------------------------|--------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------|------|---------------|------|----------|--------|------|----------|

| Switching                                          | Characteristics (T <sub>A</sub> = 25°C)                      |                         |                                                                                                    | 9    | 2602<br>602 M | )L   | 90       | 502 CC | M    |          |

| arameters                                          |                                                              |                         | Test Conditions                                                                                    | Min  | Тур           | Max  | Min      | Тур    | Max  | U        |

| t <sub>pd+</sub>                                   | Turn Off Delay Negative Trigge                               | r Input to True Output  |                                                                                                    |      | 25            | 35   |          | 25     | 40   | <b>—</b> |

| t <sub>pd</sub> _                                  | Turn On Delay Negative Trigge                                | r Input to False Output | V <sub>CC</sub> = 5.0 V, C <sub>L</sub> = 15 pF                                                    |      | 25            | 35   |          | 25     | 40   | 1        |

| • (min)                                            |                                                              | True Output (Q)         | $R_{\chi} = 5 \text{ k}\Omega, C_{\chi} = 0 \text{ pF}$                                            |      | 45            | 65   |          | 50     | 70   |          |

| t <sub>pw</sub> (min)   Minimum Output Pulse Width | False Output (Q)                                             |                         |                                                                                                    | 55   | 75            |      | 60       | 80     | 1 "  |          |

| t <sub>pe</sub>                                    | Pulse Width                                                  |                         | $V_{CC} = 5.0 \text{ V}, C_L = 15 \text{ pF}$<br>$R_X = 10 \text{ k}\Omega, C_X = 1000 \text{ pF}$ | 3.08 | 3.42          | 3.76 | 3.08     | 3.42   | 3.76 | μ        |

| R <sub>x</sub>                                     | Timing Resistor over Temperat                                | ture Range (Note 2)     |                                                                                                    | 5    |               | 50   | 5        |        | 50   |          |

| $t_{pd-}(\overline{C_p})$                          | Delay from C <sub>D</sub> to Q output LOW                    |                         |                                                                                                    |      | 11            | 17   |          | 11     | 17   | n        |

| lm2602                                             |                                                              |                         |                                                                                                    | N    | lin           | T    | yp       | M      | ax   |          |

|                                                    | Maximum change in Puise Wid<br>over temperature range 0°C to |                         | V <sub>CC</sub> = 5.0 V, C <sub>L</sub> = 15 0 14                                                  | .Da  | taSl          | neef | 4U.      | con    | 10   | Ι.       |

| Δt (T)                                             |                                                              |                         | 10 10 10 1000 F                                                                                    |      |               |      |          |        |      | 1 '      |

$R_{\rm X} = 10 \, \text{k}\Omega, \ C_{\rm X} = 1000 \, \text{pF}$

4.0

7.0

Notes: 1. Tests are conducted with a 10 kD realstor placed between Pin 2 (14) and V<sub>CC</sub> unless otherwise noted.

Maximum change in Pulse Width True Output over

temperature range -55°C to +125°C (Am2602 MIL)

#### **OPERATION RULES**

- 1. An external resistor R, and an external capacitor C, are required as shown in the logic diagram. The values of R, may vary from 5.0 kt/ 10 50 kt/ for 0°C to +75°C operation and 5.0 k0 to 25 k0 for -55°C to +125°C operation. Cy may vary from 0 to any value necessary and obtainable.

- 2. If a fixed value of R<sub>x</sub> is used, the following values are recommended: R<sub>x</sub> = 30 kΩ for 0°C to +75°C operation; R<sub>x</sub> = 10 kΩ for -55°C to +125°C operation.

- 3. The output pulse width T is defined as follows: (For C<sub>y</sub> greater than 10<sup>9</sup> pF) Where: R<sub>y</sub> Is in kQ, C<sub>y</sub> Is in pF, T is in ns. For C, < 10<sup>9</sup> pF see Fig. 2

- $T = 0.32 R_{\chi} C_{\chi} [1 + \frac{0.7}{R_{\chi}}]$ 4. If electrolytic type capacitors are to be used, it is recommended that they have low isakage. For capacitors with a high reverse leakage the following circuits can be used:

This circuit also allows larger value of R to be used for longer output pulse width.

$R < R_x (0.7) (h_x Q)$  $R_k$  (min)  $< R_k < R_s$  (max) Q;: Any NPN silicon device with sufficient his at low currents. such as 2N2511

Both circuits prevent reverse voltage across Cy. The pulse width T for the circuits is defined as follows

$T\approx 0.30~RC_\chi~[1+\frac{0.7}{R}]$  . Where: R is in kΩ, .  $C_\chi$  is in pF, . T is in ns. 5. To obtain variable pulse width, by remote trimming, the following circuit is recommended:

6. Under any operating condition, Ck and Rx (min) must be kept as close to the circuit as possible to minimize stray capacitance and reduce noise pickup 7. Input Trigger Pulse Rules. t, t, t, t, 2 40 ns Input to Pin 5 (11) Pin 4 (12) - LOW

Input to Pin 4 (12) Pin 5 (11) = HIGH Pin 3 (13) = HIGH

8. The retriggerable pulse width is calculated as shown below:  $t_{w} = t_{pw} + t_{ad+} = 0.32 R_{x}C_{x} (1 + \frac{0.7}{n}) + t_{ad+}$

Pin 3 (13) - HIGH

The ratrigger pulse width is equal to the pulse width to plus a delay time. For pulse widths greater than 500 ns, t\_ can be approximated as t\_\_

NOTE: Retriggering will not occur if the retrigger pulse comes within 0.32  $R_{\rm x}C_{\rm x}(\frac{0.7}{g^{-}})$  ns after the initial trigger pulse

9. Reset Operation - The Am2502/9602 have an active LOW reset facility. By applying a low to the reset input, any timing cycle can be terminated or any new cycle inhibited until the low reset input is removed. Trigger inputs will not produce spikes in the output when the reset is held low

## **DEFINITION OF TERMS**

#### SUBSCRIPT TERMS:

N HIGH, applying to a HiGH logic level or when used with V<sub>CC</sub> to indicate high V<sub>CC</sub> value.

I Input.

L LOW, applying to LOW logic level or when used with  $V_{\rm CC}$  to indicate low V<sub>CC</sub> value.

Output.

OL into output.

#### OPERATIONAL TERMS:

I., Forward input load current.

Ion Output HIGH current, forced out of output in Von test. In. Output LOW current, forced into the output in Vol. test.

I Reverse input load current. Negative Current Current flowing out of the device.

Positive Current Current flowing into the device.

Y<sub>M</sub> Minimum logic HIGH input voltage. Refer to figure 2. V. Maximum logic LOW input voltage. Refer to figure 2.

Minimum logic HIGH output voltage with output HIGH current IOH flowing out of output. You Maximum logic LOW output voltage with output LOW current

#### FUNCTIONAL TERMS:

C. The asynchronous direct clear input. A LOW on this input resets the monostable independent of other conditions.

Fan-Out The logic HIGH or LOW output drive capability in terms of Input Unit Loads. The active LOW input of the monostables. With input I, LOW a

HIGH to LOW transition on I will cause triggering. I. The active HIGH input of the monostables. With I, HIGH a LOW

input Unit Load One T2L gate input load.

The TRUE output of the monostables.

The FALSE output of the monostables

Triggering The switching of the monostable from the stable state to the unstable state and start of the timing cycle.

The propagation delay from a HiGH to LOW transition on L to the true (Q) output LOW to HIGH transition.  $\mathbf{I}_{od}$  The propagation delay from a HiGH to LOW transition on  $\overline{\mathbf{I}}_{o}$

t<sub>w</sub>(min) The minimum true (Q) output pulse width with  $R_X = 5k\Omega$ ,  $\dot{C}_{x} = 0 \text{ pF}.$  $t_{pw}$  The pulse width obtained with  $R_{\chi} = 10k\Omega$ ,  $C_{\chi} = 1000 \text{ pF}$ .

Atpu(T) The maximum percentage change in pulse width of the true (Q) output for the Am2602 over the temperature range from

4.23

C νi

łγ V ΙĀ Ϋ́A

3

ì

ı

to HIGH transition on I, will cause triggering.

SWITCHING TERMS.

to the false  $(\overline{\mathbf{Q}})$  output HiGH to LOW transition.

the pulse width at 25°C.

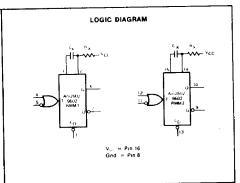

Figure 1

Figure 2

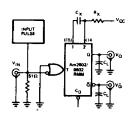

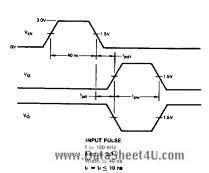

#### SWITCHING TIME TEST CIRCUIT AND WAVEFORMS

Vcc = Pin 16 Gnd. = Pin 5

Figure 3

#### TRUTH TABLE

www.DataSheet4U.com

| Am2602/9602 |      |            |  |  |  |  |  |

|-------------|------|------------|--|--|--|--|--|

| For         | Each | Monostable |  |  |  |  |  |

| Ī,  | I,  | Ċ <sub>D</sub> | Operation |

|-----|-----|----------------|-----------|

| H→L | L   | н              | Trigger   |

| н   | L→H | н              | Trigger   |

| X   | X   | L              | Reset     |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

X = Don't Care  $H \rightarrow L = HIGH$  to LOW Voltage Level transition  $L \rightarrow H = LOW$  to HIGH Voltage Level transition

Table I

#### MSI INTERFACING RULES

| Interfacing                             | Equivalent<br>Input Unit Load |     |  |  |

|-----------------------------------------|-------------------------------|-----|--|--|

| Digital Family                          | HIGH                          | LOW |  |  |

| Advanced Micro Devices 9300/2500 Series | 1                             | 1   |  |  |

| FSC Series 9300                         | 1                             | 1   |  |  |

| Ti Series 54/7400                       | 1                             | 1   |  |  |

| Signetics Series 8200                   | 2                             | 2   |  |  |

| National Series DM 75/85                | 1                             | 1   |  |  |

| DTI Series 930                          | 12                            | 1   |  |  |

Table III

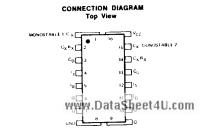

#### Am2602/9602 LOADING RULES

|              |                             |           |                    | Fanout         |     |  |  |

|--------------|-----------------------------|-----------|--------------------|----------------|-----|--|--|

| Input/Outp   | ul                          | Pin No.'s | Input<br>Unit Load | Output<br>HIGH | LOW |  |  |

| Monostable 1 | C,                          | 1         | _                  | _              | _   |  |  |

|              | C, R,                       | 2         |                    |                |     |  |  |

|              | Čυ                          | 3         | 1                  |                | _   |  |  |

|              | 1,                          | 4         | 1                  | _              |     |  |  |

|              | Ī,                          | 5         | 1                  |                |     |  |  |

|              | Q                           | 6         |                    | 16             | 8   |  |  |

|              | Õ                           | 7         |                    | 16             | 8   |  |  |

|              | GND                         | 8         |                    |                | _   |  |  |

| Monostable 2 | ā                           | 9         |                    | 16             | 8   |  |  |

|              | Q                           | 10        | _                  | 16             | 8   |  |  |

|              | Ī <sub>e</sub>              | 11        | 1                  |                | _   |  |  |

|              | 1,                          | 12        | 1                  |                |     |  |  |

|              | $\overline{\mathbf{c}}_{l}$ | 13        | 1                  |                |     |  |  |

|              | C, R,                       | 14        |                    |                |     |  |  |

|              | Cx                          | 15        |                    |                | _   |  |  |

|              | V <sub>CC</sub>             | 16        |                    | _              |     |  |  |

Table II

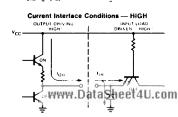

#### INPUT/OUTPUT INTERFACE CONDITIONS

#### Voltage Interface Conditions — LOW & HIGH

O VOL, VIL, DRIVEN DRIVEN

Figure 4

# Current Interface Conditions — LOW OUTPUT DINVINIS ORIGIN LOW OFF

## Am2602/9602 APPLICATIONS

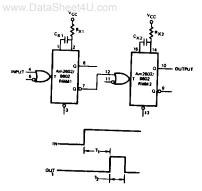

#### **Delayed Pulse Generation**

#### Figure 5

The first monostable determines the time  $\mathbf{T}_i$  before the initiation of the output pulse. The second monostable determines T2, the output pulse width.

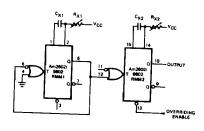

#### Pulse Generator

#### Figure 6

The output frequency produced with the above configuration is determined by  $\mathbf{C}_{\mathbf{X}_1}$  and  $\mathbf{R}_{\mathbf{X}_1}$ , while the pulse width is determined by  $C_{\chi_2}$  and  $R_{\chi_2}$ . Monostable 1 forms an astable multivibrator with an output pulse width of approximately 25 ns, while monostable 2 extends the pulse width to the required value.

21850E/0-November 1998

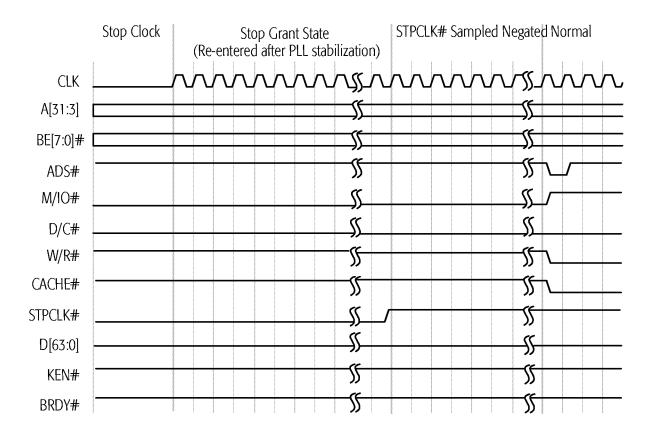

AMD-K6®-2 Processor Data Sheet

Figure 75. Stop Grant and Stop Clock Modes, Part 2

## **Preliminary Information**

AMD-K6®-2 Processor Data Sheet

21850E/0-November 1998

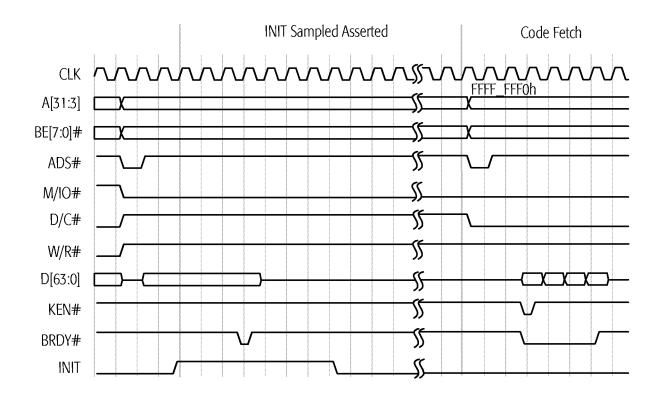

## INIT-Initiated Transition from Protected Mode to Real Mode

INIT is typically asserted in response to a BIOS interrupt that writes to an I/O port. This interrupt is often in response to a Ctrl-Alt-Del keyboard input. The BIOS writes to a port (similar to port 64h in the keyboard controller) that asserts INIT. INIT is also used to support 80286 software that must return to Real mode after accessing extended memory in Protected mode.

The assertion of INIT causes the processor to empty its pipelines, initialize most of its internal state, and branch to address FFFF\_FFF0h—the same instruction execution starting point used after RESET. Unlike RESET, the processor preserves the contents of its caches, the floating-point state, the MMX state, Model-Specific Registers (MSRs), the CD and NW bits of the CR0 register, the time stamp counter, and other specific internal resources.

Figure 76 shows an example in which the operating system writes to an I/O port, causing the system logic to assert INIT. The sampling of INIT asserted starts an extended microcode sequence that terminates with a code fetch from FFFF\_FFFOh, the reset location. INIT is sampled on every clock edge but is not recognized until the next instruction boundary. During an I/O write cycle, it must be sampled asserted a minimum of three clock edges before BRDY# is sampled asserted if it is to be recognized on the boundary between the I/O write instruction and the following instruction. If INIT is asserted synchronously, it can be asserted for a minimum of one clock. If it is asserted asynchronously, it must have been negated for a minimum of two clocks, followed by an assertion of a minimum of two clocks.

21850E/0-November 1998

AMD-K6®-2 Processor Data Sheet

Figure 76. INIT-Initiated Transition from Protected Mode to Real Mode

## **AMD**

# **Preliminary Information**

AMD-K6®-2 Processor Data Sheet

21850E/0-November 1998

21850E/0-November 1998

AMD-K6®-2 Processor Data Sheet

# 6 Power-on Configuration and Initialization

On power-on the system logic must reset the AMD-K6-2 processor by asserting the RESET signal. When the processor samples RESET asserted, it immediately flushes and initializes all internal resources and its internal state, including its pipelines and caches, the floating-point state, the MMX and 3DNow! states, and all registers. Then the processor jumps to address FFFF FFF0h to start instruction execution.

# 6.1 Signals Sampled During the Falling Transition of RESET

### FLUSH#

FLUSH# is sampled on the falling transition of RESET to determine if the processor begins normal instruction execution or enters Tri-State Test mode. If FLUSH# is High during the falling transition of RESET, the processor unconditionally runs its Built-In Self Test (BIST), performs the normal reset functions, then jumps to address FFFF\_FFF0h to start instruction execution. (See "Built-In Self-Test (BIST)" on page 217 for more details.) If FLUSH# is Low during the falling transition of RESET, the processor enters Tri-State Test mode. (See "Tri-State Test Mode" on page 218 and "FLUSH# (Cache Flush)" on page 103 for more details.)

## **BF[2:0]**

The internal operating frequency of the processor is determined by the state of the bus frequency signals BF[2:0] when they are sampled during the falling transition of RESET. The frequency of the CLK input signal is multiplied internally by a ratio defined by BF[2:0]. (See "BF[2:0] (Bus Frequency)" on page 92 for the processor-clock to bus-clock ratios.)

## **BRDYC#**

BRDYC# is sampled on the falling transition of RESET to configure the drive strength of A[20:3], ADS#, HITM#, and W/R#. If BRDYC# is Low during the fall of RESET, these outputs are configured using higher drive strengths than the standard strength. If BRDYC# is High during the fall of RESET, the standard strength is selected. (See "BRDYC# (Burst Ready Copy)" on page 95 for more details.)

AMD-K6®-2 Processor Data Sheet

21850E/0-November 1998

# **6.2 RESET Requirements**

During the initial power-on reset of the processor, RESET must remain asserted for a minimum of 1.0 ms after CLK and  $V_{CC}$  reach specification. (See "CLK Switching Characteristics" on page 255 for clock specifications. See "Electrical Data" on page 247 for  $V_{CC}$  specifications.)

During a warm reset while CLK and  $V_{\rm CC}$  are within specification, RESET must remain asserted for a minimum of 15 clocks prior to its negation.

## 6.3 State of Processor After RESET

## **Output Signals**

Table 31 shows the state of all processor outputs and bidirectional signals immediately after RESET is sampled asserted.

**Table 31. Output Signal State After RESET**

| Signal           | State    | Signal   | State    |

|------------------|----------|----------|----------|

| A[31:3], AP      | Floating | LOCK#    | High     |

| ADS#, ADSC#      | High     | M/IO#    | Low      |

| APCHK#           | High     | PCD      | Low      |

| BE[7:0]#         | Floating | РСНК#    | High     |

| BREQ             | Low      | PWT      | Low      |

| CACHE#           | High     | SCYC     | Low      |

| D/C#             | Low      | SMIACT#  | High     |

| D[63:0], DP[7:0] | Floating | TDO      | Floating |

| FERR#            | High     | VCC2DET  | Low      |

| HIT#             | High     | VCC2H/L# | Low      |

| HITM#            | High     | W/R#     | Low      |

| HLDA             | Low      | _        | _        |

## **Registers**

Table 32 on page 175 shows the state of all architecture registers and Model-Specific Registers (MSRs) after the processor has completed its initialization due to the recognition of the assertion of RESET.