# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

# GEC PLESSEY

SEMICONDUCTORS

2462 - 3.1

# CLA70000 SERIES

# HIGH DENSITY CMOS GATE ARRAYS

(Supersedes January 1992 edition - version 2.1)

Recent advances in CMOS processing technology and improvements in design architecture have led to the development of a new generation of array-based ASIC products with vastly improved gate integration densities. This family of CLA70000 1 micron CMOS arrays brings considerable advantages to the design of next generation systems combining high performance and high complexity.

# **FEATURES**

- Low power channelless arrays from 5,000 to 250,000 available gates (5µW / gate / MHz)

- 1 micron (0.8 micron effective) twin well epitaxial process

- Typical gate delays of 400 ps (NAND2 , Fanout=2)

- Comprehensive cell library including DSP, JTAG/BIST and compiled memory cells (ROM blocks to 64K bits and RAM blocks to 16K bits)

- Extensive Range of Plastic and Ceramic Packages for both Surface Mount and Through Board Assembly

- Flexible I/O structure allows user to define power pad locations

- Fully supported on industry standard workstations and in-house software

- High drive output stages with slew rate control

- Supports JTAG and BIST test philosophies (IEEE 1149-1 Test Procedures)

- MIL 883C compliant product available (paragraph 1.2.1)

# OVERVIEW

The CLA70000 gate array family is GEC Plessey Semiconductors' (GPS's) sixth generation CMOS gate array product. The family consists of nine arrays implemented on the latest generation (1 micron) twin well epitaxial CMOS process. The process in conjunction with the advanced layout and route software, offers extremely high packing densities.

The array architecture is based upon the earlier well proven CLA60000 series with the emphasis being placed on high speed, high packing density, and provision of comprehensive cell libraries. The cell libraries encompass new DSP and other specialized macros.

Full design support is available for major industry standard ASIC design software tools, as well as GEC Plessey Semiconductor's proprietary PDS2 design environment. Design support is provided by GEC Plessey Semiconductor's design centers, each offering a variety of design routes, which may be customized to individual customer requirements.

# **PRODUCT DETAILS**

The CLA70000 array series is shown below with typical figures given for usable gates. Actual gate utilization is dependent on circuit structure, giving a range of 40 -70% for two layer metallisation.

| DEVICE<br>NUMBER | I/O AND<br>POWER PADS | GATE<br>COMPLEXITY | ESTIMATED<br>USABLE GATES |

|------------------|-----------------------|--------------------|---------------------------|

| CLA70000         | 44                    | 5K                 | 2.5K                      |

| CLA71000         | 68                    | 12K                | 6K                        |

| CLA72000         | 84                    | 19K                | 9.5K                      |

| CLA73000         | 100                   | 27K                | 13.5K                     |

| CLA74000         | 120                   | 39K                | 17.5K                     |

| CLA75000         | 160                   | 70K                | 31.5K                     |

| CLA76000         | 200                   | 110K               | 49.5K                     |

| CLA77000         | 256                   | 182K               | 82K                       |

| CLA78000         | 304                   | 256K               | 115K                      |

#### CORE CELL ARRANGEMENT

- Supports compact macros

- Allows high density routing

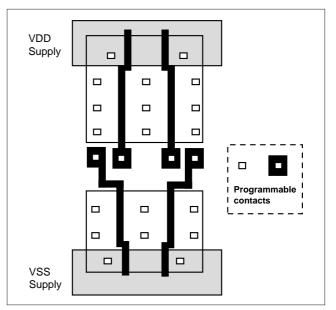

A four transistor group (2 NMOS and 2 PMOS) (fig.1) forms the basic cell of the core array. This array element is repeated in a regular fashion over the complete core area to give an homogenous 'Full Field' (sea of gates) array. This lends itself to hierarchical design, allowing pre-routed user defined subcircuits to be repeated anywhere on the array. The core cell structure together with all associated cell libraries have been carefully designed to maximize the number of nets which may be routed through the cell. This enables optimal routing of both data flow and control signal distribution schemes thus giving very high overall utilization factors. This feature is of particular benefit in designs using highly structured blocks such as memory or arithmetic functions.

#### I/O BUFFER ARRANGEMENT

- Several hundred different I/O cell combinations

- Programmable Slew rate Control on all Outputs

- Excellent Latchup and ESD immunity

The I/O buffers are the interface to external circuitry and are therefore required to be robust and flexible. Both inputs and outputs incorporate electrostatic discharge (ESD) protection structures which can withstand in excess of 2KV, and are highly resistant to latch-up due to the epitaxial process. In addition the construction concepts used for the I/O cells provide the designer with several hundred different options of I/O cell configuration.

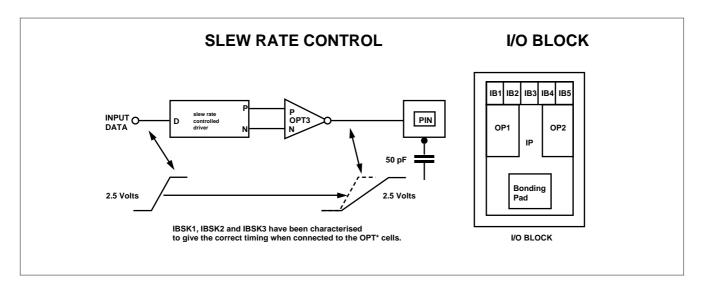

The CLA70000 I/O buffers (fig.2) contain all the components for static protection, CMOS and TTL compatible input stages, and a wide variety of intermediate and output drive configurations. Included are Schmitt triggers, tristate

Fig 1. Diagrammatic representation of Array Core Cell

controls, and slew rate controlled output buffers. All I/O buffer locations can be configured as supply pads (VDD and VSS).

Slew rate control of output drivers is a useful feature when multiple high drive outputs need to be switched simultaneously, as may occur on driving capacitive loads such as buses. Using regular output buffers with their inherently fast edge speed can lead to significant power supply noise transients, with possible mis-operation as a result. To overcome this problem. The CLA70000 family includes a set of slew rate controlled output drivers, which use proprietary design techniques to control the turn-on of the output transistors (di/dt). These cells provide a significant benefit in the trade off between switching current magnitude and the number of supply pads required.

Fig 2. Slew Control & I/O Block

#### POWER SUPPLY DISTRIBUTION

- Three power rings for good noise immunity

- Optimized for efficient routing

- User defined placement of Power and Ground pads

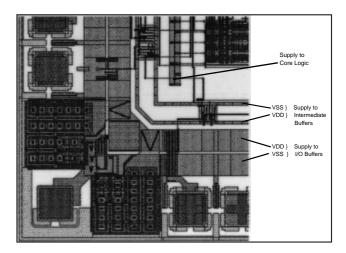

The power supply distribution scheme for the CLA70000 arrays (fig.3) has the flexibility to meet varying applications needs. Three separate power rings are used, one each for the internal core logic, intermediate buffer cells, and large output driver cells. Noise generated in the low impedance output drivers is isolated from the core logic and buffer areas. The distribution of the supply rails can be automatically positioned by the layout software which allows greater design flexibility and optimisation.

The power supply rings may be connected either to separate pad locations or combined at a single location. All I/O cell pads may be configured as either power or ground, giving complete flexibility to the designer.

# PROCESS TECHNOLOGY

- Advanced 1 micron twin well process with epitaxial substrate

- Class 10 six inch wafer fabrication facility

- High density low power process

Fig 3. Power Supply Organisation

The CLA70000 arrays are built using the GEC Plessey 1 micron drawn CMOS process, which is the third generation of our 'V' series process family. Manufacture is at GPS's Class10, 6-inch fabrication facility. The process is a twin well, self aligned oxide-isolated technology on an epitaxial substrate, with an effective channel length of 0.8 micron, giving low defect density, high reliability, and inherently low power dissipation. The process has excellent immunity to latchup, and ESD, and exhibits stable performance characteristics ideal for all commercial, industrial and military applications.

| Parameter           | Min  | Max       | Units   |

|---------------------|------|-----------|---------|

| Supply Voltage      | -0.5 | 7.0       | V       |

| Input Voltage       | -0.5 | Vdd + 0.5 | V       |

| Output Voltage      | -0.5 | Vdd + 0.5 | V       |

| ESD protection      | 2.0  |           | K Volts |

| Current per pad     |      | 100       | mA      |

| Storage Temperature |      |           |         |

| Ceramic             | -65  | 150       | °C      |

| Plastic             | -40  | 125       | °C      |

|                     |      | 1         |         |

#### **ABSOLUTE MAXIMUM RATINGS**

Operation outside these absolute maximum ratings may permanently damage device characteristics and may affect reliability.

#### **RECOMMENDED MAXIMUM OPERATING LIMITS**

| Parameter             | Min | Max   | Units |

|-----------------------|-----|-------|-------|

| Supply Voltage        | 3.0 | 5.5   | V     |

| Input Voltage         | Vss | Vdd   | V     |

| Output Voltage        | Vss | Vdd   | V     |

| Operating Temperature |     |       |       |

| Commercial Grade      | 0   | 70    | °C    |

| Industrial Grade      | -40 | 85*   | °C    |

| Military Grade        | -55 | 125** | °C    |

\* 125°C maximum junction temperature for plastic devices. \*\*Subject to a maximum junction temperature of 150°C for ceramic devices.

# MANUFACTURING FACILITY

- Computer aided manufacturing

- Digital testers with large pinout capacity

- Vibration free for reliable manufacture

The CLA70000 product is manufactured near Plymouth, England in the latest purpose built facility for sub-micron process geometries. The factory uses the latest automated equipment for 6 inch wafers and Computer Aided Manufacturing techniques to ensure production efficiency. Wafer fabrication is carried out in Class 10, or better, clean room conditions in a vibration free environment to assure the lowest possible defect level. In addition to the world class wafer facility there are excellent probe and final test areas equipped with the latest analog and digital testers capable of handling complex test vectors and large pinouts. This large investment shows GEC Plessey Semiconductors commitment to all the market areas needing state-of-the-art CMOS ASICS.

#### **CELL LIBRARY**

### LOGIC ARRAY CELLS

| BUF    | Buffer driver                              |

|--------|--------------------------------------------|

| ST1    | Schmitt trigger                            |

| DELAY  | Delay cell                                 |

| 2INV   | Dual driver                                |

| INV2   | Inverter, dual drive                       |

| INV4   | Inverter, quad drive                       |

| INV8   | Inverter, octal drive                      |

| NAND2  | 2 input NAND gate                          |

| ND3    | 3 input NAND gate                          |

| NAND3  | 3 input NAND gate + inverter               |

| 2NAND3 | Dual 3 input NAND gate                     |

| NAND4  | 4 input NAND gate                          |

| NAND5  | 5 input NAND gate                          |

| NAND6  | 6 input NAND gate                          |

| NAND8  | 8 input NAND gate                          |

| NOR2   | 2 input NOR gate                           |

| NR3    | 3 input NOR gate                           |

| NOR3   | 3 input NOR gate + inverter                |

| 2NOR3  | Dual 3 input NOR gate                      |

| NOR4   | 4 input NOR gate                           |

| NOR5   | 5 input NOR gate                           |

| NOR6   | 6 input NOR gate                           |

| NOR8   | 8 input NOR gate                           |

| A2O21  | 2 input AND to 2 input NOR gate + inverter |

| O2A21  | 2 input OR to 2 input NAND gate + inverter |

| 2A2O21 | Dual 2 input AND to 2 input NOR gate       |

| 2O2A21 | Dual 2 input OR to 2 input NAND gate       |

| 2ANOR  | 2 input ANDs to 2 input NOR gate           |

| 2ONAND | 2 input ORs to 2 input NAND gate           |

# **CELL LIBRARY**

- Comprehensive range of cells

- Specialized DSP and BIST sub-libraries

- Compatible with Megacell and CLA60000

A very comprehensive cell library is available for the CLA70000 series. It contains sub libraries which may be used in specific applications areas such as Digital Signal Processing (DSP) and Built In Self Test (BIST). More details on these specialized libraries can be found in applications notes or the design manual.

The 1.4 micron (drawn) CMOS array (CLA60000) cell library may be converted to the equivalent cells on the CLA70000 to allow system upgrades. Equivalent cells are also available for the corresponding MVA70000 Megacell to enable an easy transition to a standard cell product to minimize silicon area or to add analog functions.

| A2O31<br>O2A31<br>A3O21<br>O3A21<br>A4O21<br>O4A21<br>A2O41<br>O2A41<br>3A2O31<br>3O2A31<br>O2A2O21<br>A2O2A21 | 2 input AND to 3 input NOR gate<br>2 input OR to 3 NAND gate<br>3 input AND to 2 input NOR gate<br>3 input OR to 2 input NAND gate<br>4-input ANDs to 2 input NAND gate<br>2-input ORs to 2 input NAND gate<br>2-input AND to 4 input NOR gate<br>3 2-input ORs to 3 input NAND gate<br>3 2-input ORs to 3 input NAND gate<br>2 input OR to 2 input AND to 2 input<br>NOR gate<br>2 input AND to 2 input OR to 2 input<br>NAND gate |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXOR                                                                                                           | Exclusive OR gate + NAND gate + inverter                                                                                                                                                                                                                                                                                                                                                                                            |

| EXNOR                                                                                                          | Exclusive NOR gate + NOR gate + inverter                                                                                                                                                                                                                                                                                                                                                                                            |

| EXOR2                                                                                                          | 2 input exclusive OR gate                                                                                                                                                                                                                                                                                                                                                                                                           |

| EXNOR2                                                                                                         | 2 input exclusive NOR gate                                                                                                                                                                                                                                                                                                                                                                                                          |

| EX2                                                                                                            | Exclusive OR gate + inverter                                                                                                                                                                                                                                                                                                                                                                                                        |

| EXN2                                                                                                           | Exclusive NOR gate + inverter                                                                                                                                                                                                                                                                                                                                                                                                       |

| EXOR3                                                                                                          | 3 input exclusive OR gate                                                                                                                                                                                                                                                                                                                                                                                                           |

| EXNOR3                                                                                                         | 3 input exclusive NOR gate                                                                                                                                                                                                                                                                                                                                                                                                          |

| EXPRIM                                                                                                         | 2 input exclusive OR gate primitive                                                                                                                                                                                                                                                                                                                                                                                                 |

| HADD                                                                                                           | Half adder + inverter                                                                                                                                                                                                                                                                                                                                                                                                               |

| SUM                                                                                                            | Sum block                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SUM2                                                                                                           | Sum block                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CARRY                                                                                                          | Carry block + NOR gate                                                                                                                                                                                                                                                                                                                                                                                                              |

| CARRY2                                                                                                         | Carry block + inverter                                                                                                                                                                                                                                                                                                                                                                                                              |

| FADD                                                                                                           | Full adder + NOR gate                                                                                                                                                                                                                                                                                                                                                                                                               |

| BMF1                                                                                                           | Full adder 1                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BMF2                                                                                                           | Full adder 2                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MUX2TO1                                                                                                        | 2 to 1 multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MUX4TO1                                                                                                        | 4 to 1 multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MUX8TO1                                                                                                        | 8 to 1 multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MUXI2TO1                                                                                                       | 2 to 1 inverting multiplexer                                                                                                                                                                                                                                                                                                                                                                                                        |

| MUXI4TO1<br>MUXI8TO 1                                                       | 4 to 1 inverting multiplexer<br>8 to 1 inverting multiplexer                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKA<br>2CLKA<br>CLKAP<br>CLKAM<br>CLKB<br>CLKBP<br>CLKE1<br>CLKE2<br>CLKE3 | Basic clock driver<br>Dual basic clock driver<br>Basic clock driver + inverter<br>Basic clock driver + inverter<br>Large clock driver + inverter<br>Clock driver with enable<br>Clock driver with enable<br>Clock driver with enable                                                                                                                                     |

| TM<br>2TM<br>BDR                                                            | Buffered transmission gate<br>Transmission gate for 2 to 1 multiplexing<br>Internal bus driver                                                                                                                                                                                                                                                                           |

| DL<br>DL2<br>DLRS<br>DLARS<br>DF<br>DFRS<br>MDF<br>MDFRS<br>M3DF<br>M3DF    | Data latch<br>Data latch<br>Data latch<br>Data latch with set and reset<br>Data latch with set and reset<br>Master-slave D type flip flop<br>Master-slave D type flip flop with set & reset<br>Multiplexed master-slave D type flip flop<br>Multiplexed m/s D type flip flop<br>Multiplexed m/s D type flip flop<br>Multiplexed m/s D type flip flop<br>with set & reset |

| JK<br>JKRS<br>JBARK<br>JBARKRS                                              | J-K flip-flop<br>J-K flip-flop with set & reset<br>JBAR-K flip-flop<br>JBAR-K flip-flop with set & reset                                                                                                                                                                                                                                                                 |

| BDL<br>BDLRS<br>JBARKRS<br>BDF<br>BDFRS                                     | Buffered data latch<br>Buffered data latch with set & reset<br>Buffered data latch with set & reset<br>Buffered master-slave D type flip-flop<br>Buffered master-slave D type flip-flop<br>with set & reset                                                                                                                                                              |

| BMDF<br>BMDFRS<br>BJBARK<br>BJBARKRS                                        | Buffered mux. master-slave D type flip-flop<br>Buffered mux. m/s D type with set & reset<br>Buffered J-K flip-flop<br>Buffered J-K flip-flop with set & reset                                                                                                                                                                                                            |

| TRID                                                                        | Tristate driver                                                                                                                                                                                                                                                                                                                                                          |

| GND<br>VDD                                                                  | Ground Cell<br>VDD Cell                                                                                                                                                                                                                                                                                                                                                  |

| INTERMED                                                                    | IATE BUFFER CELLS                                                                                                                                                                                                                                                                                                                                                        |

| IBCCMOS1<br>IBCCMOS2<br>IBTTL1<br>IBBTL2<br>IBST1                           | CMOS input buffer + large 2 input NAND gate<br>CMOS input buffer + data latch<br>TTL input buffer + large 2 input NAND gate<br>TTL input buffer + data latch<br>Input Schmitt buffer with CMOS switching<br>levels                                                                                                                                                       |

IBST2 Input Schmitt buffer with 2V switching levels

| IBGATE<br>IBCLKB<br>IBDF<br>IBDFA<br>IBSK1<br>IBSK2<br>IBSK3<br>IBTRID<br>IBTRID1<br>IBTRID2<br>IBTRID3 | NAND2/NOR2 gates<br>Large clock driver<br>Master-slave D type flip flop<br>Master-slave D type flip flop<br>Driver with slewed outputs<br>Driver with slewed outputs<br>Driver with slewed outputs<br>Tri-state driver<br>Tri-state driver with slewed outputs +<br>2 inverters<br>Tri-state driver with slewed outputs +<br>2 inverters<br>Tri-state driver with slewed outputs +<br>2 inverters |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IB2BD                                                                                                   | 2 inverters<br>Dual high powered inverters                                                                                                                                                                                                                                                                                                                                                        |

| DRV3<br>DRV6                                                                                            | Clock driver<br>Clock driver                                                                                                                                                                                                                                                                                                                                                                      |

# PAD INPUT CELLS

| IPNR  | Input cell with no pull up or down resistors |

|-------|----------------------------------------------|

| IPR1P | Input cell with 1KOhm pull up resistor       |

| IPR1M | Input cell with 1KOhm pull down resistor     |

| IPR2P | Input cell with 2KOhm pull up resistor       |

| IPR2M | Input cell with 2KOhm pull down resistor     |

| IPR3P | Input cell with 4KOhm pull up resistor       |

| IPR3M | Input cell with 4KOhm pull down resistor     |

| IPR4P | Input cell with 75KOhm pull up resistor      |

| IPR4M | Input cell with 75kOhm pull down resistor    |

|       |                                              |

# OSCILLATOR CELLS (crystal)

to be defined

# PAD OUTPUT CELLS

| OP1           | Smallest drive output cell                                                     |

|---------------|--------------------------------------------------------------------------------|

| OP2           | Small drive output cell                                                        |

| OP3           | Standard drive output cell                                                     |

| OP6           | Medium drive output cell                                                       |

| OP12          | Large drive output cell                                                        |

| OP5B<br>OP11B | Standard drive non-inverting output cell Large drive non-inverting output cell |

| OPT1          | Smallest drive tri-state output cell                                           |

| OPT2          | Small drive tri-state output cell                                              |

| OPT3          | Standard drive tri-state output cell                                           |

| OPT6          | Medium drive tri-state output cell                                             |

| OPT12         | Large drive tri-state output cell                                              |

| OP4B          | Standard drive non-inverting tri-state output cell                             |

| OP10B         | Large drive non-inverting tri-state output cell                                |

| OPOD1         | Smallest drive open-drain output cell                                          |

| OPOD2         | Small drive open-drain output cell                                             |

| OPOD3         | Standard drive open-drain output cell                                          |

| OPOD6         | Medium drive open-drain output cell                                            |

| OPOD12        | Large drive open-drain output cell                                             |

| OPOD5B                                     | Standard drive non-inverting open-drain                                                                                                                                                                                                      |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPOD11B                                    | output cell<br>Large drive non-inverting open-drain<br>output cell                                                                                                                                                                           |

| OPOS1<br>OPOS2<br>OPOS3<br>OPOS6<br>OPOS12 | Smallest drive open-source output cell<br>Small drive open-source output cell<br>Standard drive open-source output cell<br>Medium drive open-source output cell<br>Large drive open-source output cell                                       |

| OPOS5B                                     | Standard drive non-inverting open-source                                                                                                                                                                                                     |

| OPOS11B                                    | output cell<br>Large drive non-inverting open-source<br>output cell                                                                                                                                                                          |

| POWER SU                                   | JPPLY CELLS                                                                                                                                                                                                                                  |

| OPVP<br>OPVM<br>OPVPB<br>OPVMB<br>OPVPBB   | VDD power pad (outputs)<br>GND power pad (outputs)<br>VDD power pad (outputs) : break in VDD<br>GND power pad (outputs) : break in GND<br>VDD power pad (outputs) : break in VDD &<br>GND<br>GND power pad (outputs) : break in VDD &<br>GND |

| IBVP<br>IBVM<br>IBVPB<br>IBVMB<br>IBVPBB   | VDD power pad (buffers)<br>GND power pad (buffers)<br>VDD power pad (buffers) : break in VDD<br>GND power pad (buffers) : break in GND<br>VDD power pad (buffers) : break in VDD &<br>GND<br>GND power pad (buffers) : break in VDD &<br>GND |

| LAVP<br>LAVM                               | Power pad for logic array                                                                                                                                                                                                                    |

# CLA70000 PDS-BIST (JTAG/IEEE1149-1) LIBRARY

#### **TEST REGISTER CELLS**

|

LAGND | LAVDD

| JTRDU4,8,16,24,32 | 4,8,16,24,32 bit Transparent Test registers with Update Latches |

|-------------------|-----------------------------------------------------------------|

| JTRDD4,8,16,24,32 | 4,8,16,24,32 bit Transparent<br>Test registers                  |

| JTRCU4,8,16,24,32 | 4,8,16,24,32 bit Clocked Test registers with Update Latches     |

| JTRCD4,8,16,24,32 | 4,8,16,24,32 bit Clocked<br>Test Registers                      |

|                   |                                                                 |

## **TESTCONTROL CELLS**

| JTAP     | PDS BIST JTAG Interface Controller                      |

|----------|---------------------------------------------------------|

| JTCLK    | PDS-BIST Clock Gating and Buffer Cell                   |

| JTIDREG  | PDS-BIST JTAG Identification Register                   |

| TEST REG | ISTER COMPONENT CELLS                                   |

| JTDUT    | Test register data bit (transparent) with update latch  |

| JTDUF    | Test register data bit (transparent)] with update latch |

| JTDDT    | Test register data bit (transparent)                    |

| JTDDF    | Test register data bit (transparent)                    |

| JTCUT    | Test register data bit (clocked) with update latch      |

| JTCUF    | Test register data bit (clocked) with update latch      |

| JTCDT    | Test register data bit (clocked)                        |

| JTCDF    | Test register data bit (clocked)                        |

| JTCT     | Test register local controller                          |

| JTBF16   | Test register driver 4-19 databits                      |

| JTBF16   | Test register driver 20-34 databits                     |

# CLA70000 DSP MACROCELL LIBRARY

### RIPPLE CARRY ADDERS

| ADR1  | 1bit adder   |

|-------|--------------|

| ADR3  | 4 bit adder  |

| ADR8  | 8 bit adder  |

| ADR16 | 16 bit adder |

| ADR24 | 24 bit adder |

| ADR32 | 32 bit adder |

#### HIGH SPEED CARRY SELECT ADDERS

| ADS1  | 1bit adder   |

|-------|--------------|

| ADS3  | 4 bit adder  |

| ADS8  | 8 bit adder  |

| ADS16 | 16 bit adder |

| ADS24 | 24 bit adder |

| ADS32 | 32 bit adder |

|       |              |

### CARRY SELECT ADDERS (REDUCED AREA)

| ADT8  | 8 bit adder  |

|-------|--------------|

| ADT16 | 16 bit adder |

| ADT24 | 24 bit adder |

#### ADT32 32 bit adder

#### SUBTRACTOR BLOCKS

| ADSU4  | 4 bit subtractor add-on  |

|--------|--------------------------|

| ADSU8  | 8 bit subtractor add-on  |

| ADSU16 | 16 bit subtractor add-on |

| ADSU24 | 24 bit subtractor add-on |

| ADSU32 | 32 bit subtractor add-on |

|        |                          |

# SHIFTERS ARITHMETIC RIGHT (PADDED WITH MSB)

| SHA4  | 4 stage arithmetic right shifter  |

|-------|-----------------------------------|

| SHA8  | 8 stage arithmetic right shifter  |

| SHA16 | 16 stage arithmetic right shifter |

| SHA24 | 24 stage arithmetic right shifter |

| SHA32 | 31 stage arithmetic right shifter |

|       |                                   |

#### SHIFTERS BARREL RIGHT (PADDED WITH LSB DATA EXITING SHIFTER)

| SHB4  | 4 stage barrel right shifter  |

|-------|-------------------------------|

| SHB8  | 8 stage barrel right shifter  |

| SHB16 | 16 stage barrel right shifter |

| SHB24 | 24 stage barrel right shifter |

| SHB32 | 31 stage barrel right shifter |

# SHIFTERS LOGIC RIGHT/LEFT (PADDED WITH ZERO'S)

| SHL4  | 4 stage logic right shifter  |

|-------|------------------------------|

| SHL8  | 8 stage logic right shifter  |

| SHL16 | 16 stage logic right shifter |

| SHL24 | 24 stage logic right shifter |

| SHL32 | 31 stage logic right shifter |

### LOGIC UNITS (8 FUNCTION)

| 4 logic bit unit  |

|-------------------|

| 8 logic bit unit  |

| 16 logic bit unit |

| 24 logic bit unit |

| 32 logic bit unit |

|                   |

#### **ARITHMETIC UNITS (8 FUNCTION)**

| 4 bit logic unit  |

|-------------------|

| 8 bit logic unit  |

| 16 bit logic unit |

| 24 bit logic unit |

| 32 bit logic unit |

|                   |

#### CLA70000 DSP MACROCELL LIBRARY

#### MULTIPLIERS AND ASSOCIATED CELLS

| BMA8X8   | Mixed mode multiplier (8 x 8 bits)   |

|----------|--------------------------------------|

| BMA16X16 | Mixed mode multiplier (16 x 16 bits) |

| BMA24X24 | Mixed mode multiplier (32 x 32 bits) |

| BMB16X12                | Single pipeline multiplier (16 x 12 bits)                               |

|-------------------------|-------------------------------------------------------------------------|

| BMC24X24                | Mixed mode multiplier (24 x 24 bits)                                    |

| BTHE1<br>BTHD1<br>BTHD2 | Booth encoder<br>Non-Inverting Booth decoder<br>Inverting Booth decoder |

Many of the macro functions perform similar functions to the standard TTL and CMOS logic families. The user is warned, however, that the logic functions may differ slightly and is therefore recommended to refer to the design manual rather than assume an exact functional copy. The PDS simulator uses the constituent microcell models for circuit analysis.

The macrocells are constructed from basic microcells and are placed and routed to give optimum use of chip area.

# MACRO FUNCTION ADDERS

| ADA4 | 4 bit binary full adders with fast carry |

|------|------------------------------------------|

| ADG4 | Look ahead carry generator               |

#### COUNTERS

| CNA4  | BCD counter/4 bit latch decoder/driver   |

|-------|------------------------------------------|

| CNB4  | 4 bit counter latch                      |

| CNC4  | 4 bit synchronous counter                |

| CND4  | 4 bit binary up/down Synchronous counter |

| CND4A | 4 bit binary up/down counter with reset  |

| CNE4  | 4 bit decade counter                     |

| CNF4  | 4 bit binary synchronous counter         |

| CNG4  | 4 bit binary counter                     |

#### DECODERS

| 3 line to 8 line decoder/demultiplexer<br>4 line to 16 line decoder/demultiplexer |

|-----------------------------------------------------------------------------------|

| 4 line to 16 line decoder/demultiplexer                                           |

| no enable                                                                         |

| 3 line to 8 line decoder/demultiplexer                                            |

| with address registers                                                            |

| 3 line to 8 line decoder/demultiplexer                                            |

| with address latches                                                              |

| 2 line to line decoder                                                            |

| 4 line to 10 line BCD decoder                                                     |

| 4 line to 10 line excess 3 to                                                     |

| decimal decoder                                                                   |

| 4 line to 10 line excess gray to                                                  |

| decimal decoder decoder                                                           |

| BCD to decimal decoder/driver                                                     |

| BCD to 7 segment decoder/driver                                                   |

| BCD to 7 segment decoder/driver                                                   |

|                                                                                   |

| DRL7              | BCD to 7 segment decoder/driver                                                                   | SRB8                  |               | bit PISO shift register with clear                                                                                |

|-------------------|---------------------------------------------------------------------------------------------------|-----------------------|---------------|-------------------------------------------------------------------------------------------------------------------|

| ENCODEF           | S                                                                                                 | SRB8A<br>SRC8<br>SRD4 | 8             | bit PISO shift register without clear<br>bit PISO shift register with clear<br>bit SIPO shift register with clear |

| ENA8T3<br>ENB10T4 | 8 line to 3 line priority encoder<br>10 line to 4 line priority encode                            | SRE4                  | 4             | bit PIPO shift register with JKbar<br>nput                                                                        |

| FLIP-FLOF         |                                                                                                   | SRF8                  | tr            | bit shift and store register with ristate outputs                                                                 |

| FFA8              | 8 bit bistable latches                                                                            | SRG4                  | re            | bit bidirectional universal shift<br>egister                                                                      |

| FFB6<br>FFC4      | 6 bit D-type flip-flop with clear<br>4 bit D-type flip-flop with clear &<br>complimentary outputs | SRJ4<br>SRK5          |               | bit parallel access shift register<br>bit shift register                                                          |

| FFD8              | Octal D-type flip-flop with clear                                                                 | PROCESS               | MONITC        | )R                                                                                                                |

| ALU/FUNC          | TIONAL GENERATOR                                                                                  | PERF                  | Perform       | ance monitor                                                                                                      |

| FGA5              | 4 bit ALU/function generator                                                                      | BIST *                |               |                                                                                                                   |

| ADDERS            |                                                                                                   | RGBIT<br>RGTBIT       | Test reg      | ister (one bit)<br>ister (one monitor bit)                                                                        |

| MCA4              | 4 bit magnitude comparators                                                                       | RGDIAG<br>RGCTL       | Test reg      | tic control unit<br>ister controller                                                                              |

| MULTIPLIE         | ERS                                                                                               | RGHOLD                | -             | ister hold circuitry                                                                                              |

| MLA10             | Decade rate multiplier                                                                            | * (early buil         | t in self tes | t cells) see CLA7BIST Library                                                                                     |

| MLB4X4            | 4 by 4 binary multiplier with tristate outputs                                                    | CLA70000              | PARACE        | ELL LIBRARY                                                                                                       |

| MLW7              | 7 bit Wallace trees with tristate outputs                                                         | MEMORY                | CELLS         |                                                                                                                   |

| MULTIPLE          | XERS                                                                                              | RBRAM                 |               | /AX 16384 bits per block<br>VORDS 2:128, bits 1:128 (min:max)                                                     |

| MXA8T1            | 8 line to 1 line data selector / multiplexer                                                      | ROROM                 | ROM N         | MAX 65536 bits per block<br>VORDS 2:2048, bits 2:64 (min:max)                                                     |

| MXB4T1            | Dual 4 line to 1 line data selector / multiplexers                                                |                       |               |                                                                                                                   |

| MXB4T1A           | Dual 4 line to 1 line data selector /<br>multiplexer with inverted tristate                       |                       |               |                                                                                                                   |

| MXC2T1<br>MXC2T1A | outputs<br>Quad 2 to 1 data selector / multiplexers<br>Quad 2 to 1 selector (inverted outputs)    |                       |               |                                                                                                                   |

| MXD4T1            | Quad 2 to 1 selector (inverted outputs)<br>4 to 1 multiplexor with strobe                         |                       |               |                                                                                                                   |

| MXE4T1<br>MXF2T1  | 4 to 1 multiplexor with strobe 2 to 1 multiplexeor with storage                                   |                       |               |                                                                                                                   |

| PARITY G          | ENERATOR                                                                                          |                       |               |                                                                                                                   |

| PGA9              | 9 bit odd/even parity<br>generator/checker                                                        |                       |               |                                                                                                                   |

| SHIFT RE          | GISTERS                                                                                           |                       |               |                                                                                                                   |

| SRA2<br>SRA4      | 2 bit POS shift register with clear<br>4 bit POS shift register with clear                        |                       |               |                                                                                                                   |

| SRA8              | 8 bit SIPO shift register with clear                                                              |                       |               |                                                                                                                   |

| SRA8A<br>SRB2     | 8 bit SIPO shift register without clear<br>2 bit PISO shift register with clear                   |                       |               |                                                                                                                   |

| SRB4              |                                                                                                   |                       |               |                                                                                                                   |

# **DESIGN SUPPORT AND INTERFACES**

- Flexible design route approach

- Design center engineer assigned to every customer circuit

- Full turnkey service capability

Design and layout support for CLA70000 arrays is available from various centers worldwide each of which is connected to our Headquarters via high speed data links. A design center engineer is assigned to each customer's circuit, to ensure good communication, and a smooth and efficient design flow. It should be noted that sign-off simulation against the GPS 'golden' simulator is also supported at our local design centers.

GPS offers a variety of formal design routes as illustrated in the table below. Differing interface methods allow for varying levels of involvement in a manner which complements individual customer design styles, whilst maintaining our responsibility to ensure first time working devices.

As part of the design process GPS operates a thorough design audit procedure to verify compliance with customer specification and to ensure manufacturability. The procedure includes four separate review meetings, with the customer, held at key stages of the design.

Review 1: Held at the beginning of the design cycle

To check and agree on all performance, packaging, specifications and design timescales.

Review 2: Held after Logic Simulation but prior to Layout

Checks to ensure satisfactory functionality, timing performance, and adequate fault coverage.

Review 3: Held after Layout and Post Layout Simulation

Verification of satisfactory design performance after insertion of actual track loads. Final check of all device specifications before prototype manufacture.

```

Review 4: Held after Prototype Delivery

Confirm that devices meet all specifications

and are suitable for full scale production.

```

#### DESIGN TOOLS

The focus of the GEC Plessey design tool methodology is that of maintaining an open CAD system with all interfaces standardized via EDIF 2.0. This enables us to provide full support for a variety of 3rd party ASIC design tools and facilitates rapid updating of associated libraries. It also provides an interface to the GEC Plessey (PDS2) design system, which offers a total design environment including behavioral and functional level modelling.

| CAD SUPPORT                |                         |                          |                    |  |  |  |

|----------------------------|-------------------------|--------------------------|--------------------|--|--|--|

|                            | Desigr                  | Routes                   |                    |  |  |  |

|                            | THIRD PARTY<br>SOFTWARE | PDS IN-HOUSE<br>SOFTWARE | TURNKEY<br>SERVICE |  |  |  |

| OPTIONS                    |                         |                          |                    |  |  |  |

| Design Review 1            |                         |                          |                    |  |  |  |

| Schematic Capture          | CUSTOMER                | CUSTOMER                 | GPS                |  |  |  |

| Logical Design             | CUSTOMER                | CUSTOMER                 | GPS                |  |  |  |

| Design Review 2            |                         |                          |                    |  |  |  |

| Physical Design            | GPS                     | CUSTOMER or GPS          | GPS                |  |  |  |

| Design Review 3            |                         |                          |                    |  |  |  |

| Prototype<br>Manufacturing | GPS                     | GPS                      | GPS                |  |  |  |

| Prototype Evaluation       | CUSTOMER                | CUSTOMER                 | CUSTOMER           |  |  |  |

| Design Review 4            |                         |                          |                    |  |  |  |

| Production                 | GPS                     | GPS                      | GPS                |  |  |  |

#### THIRD PARTY SOFTWARE SUPPORT

- Design Kits for major industry standard ASIC design software tools

- All libraries include fully detailed timing information

- EDIF 2.0 Interface

- Post layout back annotation available

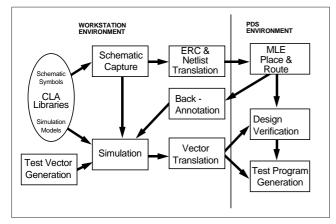

GPS supports a wide range of third party design tools including IKOS, Mentor, Verilog, and Viewlogic at the time of printing. Please check with our Sales Offices for the most recent additions. The design kits offer fully detailed timing information for all cell libraries, netlist extraction utilities, and post layout back annotation capability where applicable. An example of a workstation design flow is shown in fig 5 below. Please contact your local GEC Plessey Semiconductor's sales office for further information about support of particular tools.

Fig 5. Workstation Design Flow

#### PDS2 - THE GPS ASIC DESIGN SYSTEM

- Behavioral, Functional, and Gate Level Modelling

- VHDL and Third Party Links

- Supports Hierarchical Design Techniques

- EDIF 2.0 Interface

PDS2 is GPS's own proprietary ASIC design system. It provides a fully-integrated, technology independent VLSI design environment for all GPS CMOS SemiCustom products.

PDS2 runs on Digital Equipment Computers and is self configuring according to the available machine resources. It comprises design capture (schematic capture or VHDL), testability analysis, logic simulation, fault simulation, auto place and route, and back annotation. The system offers full support for hierarchical design techniques, maintained from design capture through to layout, as well as advanced design management tools. PDS2 may be used either at a GPS Design Center or under licence at the customer's premises. A three day training course is available for first time users.

### **SPECIFICATIONS**

#### THERMAL MANAGEMENT

- Lower power CMOS for better thermal management

- Improved reliability

- Power packages available

The increase in speed and density available through CMOS process geometry reduction, results in a corresponding increase in power dissipation. SemiCustom designers now have the ability to design circuits of 100,000 gates and over, and chip power consumption is (or should be) a very important concern.

The logic core of 100K plus gates is the dominant factor in power dissipation at this complexity. It is essential to offer ultra low power core logic to maintain an acceptable overall chip power budget.

To minimize this problem GPS's CLA70000 arrays offer low power factors and a selection of power packages. Dissipation of  $5 \mu$ W per gate per Mhz gate power and  $1\mu$ W per gate load, is lower than most competitive arrays, with the reduced junction temperatures having the added advantage of improved performance and reliability.

#### **CLA70000 POWER DISSIPATION CALCULATION**

CLA70000 series power dissipation for any array can be estimated by following the example (calculated for the CLA76XXX) below.

| Number of available gates<br>Assume percent gates used<br>Number of used gates (110102 X 0.4)<br>Assume 15% of gates switching during. | 110112<br>40%<br>44045 |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| each clock cycle (44045 X 0.15)<br>Power dissipation/gate/Mhz<br>(gate fanout typically 2 loads)                                       | 6607<br>7μW            |

| Total core dissipation/Mhz (6607 X 0.007)                                                                                              | 46.2 mW                |

| Number of available I/O pads                                                                                                           | 200                    |

| Percent of I/O pads used as Outputs<br>Number of I/O pads used as Outputs<br>Number of output buffers switching                        | 40%<br>80              |

| each clock cycle (20%)                                                                                                                 | 16                     |

| Dissipation/output buffers/Mhz/pF<br>Output loading                                                                                    | 25μW<br>50 pF          |

| Power/output buffer/Mhz<br>Total output buffer dissipation/Mhz                                                                         | 1.25mW<br>20mW         |

| Total Power dissipation/Mhz                                                                                                            | 66.2mW                 |

| Estimated discipation of the circuit at the frequencies h                                                                              |                        |

Estimated dissipation of the circuit at the frequencies below is

| Total Power at 10 Mhz clock rate | 0.66W |

|----------------------------------|-------|

| Total Power at 25Mhz clock rate  | 1.65W |

#### AC CHARACTERISTICS FOR SELECTED CELLS

The CLA70000 technology library contains all the timing information for each cell in the design library. This information is accessible to the simulator, which calculates propagation delays for all signal paths in the circuit design. The simulator can automatically derate timings according to the various factors such as:

> Supply voltage variation (from nominal 5V) Junction temperature Processing tolerance - manufacturing spreads Gate fanout - logic loading on gate outputs Interconnection wiring - net loading on gate outputs

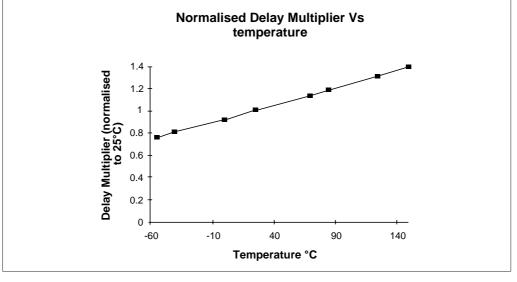

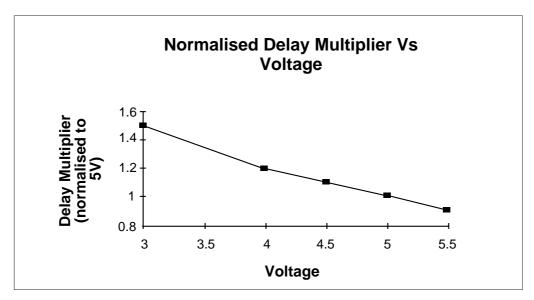

For initial assessments of feasibility, path delay multipliers can be estimated by referring to the following graphs in conjunction with the appropriate delays in the tables.

# AC CHARACTERISTICS

|          |                     |                       |        | Typical     |      | Worst case pro | pagation Delay ( | ns)  |  |

|----------|---------------------|-----------------------|--------|-------------|------|----------------|------------------|------|--|

| INTERNAL | INTERNAL CORE CELLS |                       |        | Propagation | Comr | nercial        | Industrial       |      |  |

| Name     | Cells               | Description           | Symbol | Delay (ns)  | Far  | nout           | Far              | nout |  |

|          |                     |                       |        | Fanout =2   | 2    | 4              | 2                | 4    |  |

| INV2     | 1                   | 1 Invertor Dual Drive | tpLH   | 0.27        | 0.70 | 0.84           | 0.73             | 0.88 |  |

| 11112    | I                   |                       | tpHL   | 0.18        | 0.47 | 0.56           | 0.49             | 0.58 |  |

| NAND2    |                     | 2-Input NAND Gate     | tpLH   | 0.39        | 1.01 | 1.29           | 1.05             | 1.35 |  |

| INAINDZ  | 1                   |                       | tpHL   | 0.30        | 0.79 | 1.04           | 0.82             | 1.09 |  |

| NOR2     | 1                   |                       | tpLH   | 0.50        | 1.30 | 1.81           | 1.35             | 1.89 |  |

| NORZ     |                     | 2-Input NOR Gate      | tpHL   | 0.22        | 0.57 | 0.80           | 0.60             | 0.84 |  |

| 55       |                     | Master Slave          | tpLH   | 0.54        | 1.40 | 1.60           | 1.46             | 1.68 |  |

| DF       | 1                   | D-Type Flip-Flop      | tpHL   | 0.55        | 1.44 | 1.55           | 1.51             | 1.62 |  |

|                           |                                        |                     |             | Typical           | Typical Worst case propagation Delay (ns) |      |        |      |

|---------------------------|----------------------------------------|---------------------|-------------|-------------------|-------------------------------------------|------|--------|------|

| INTERMEDIATE BUFFER CELLS |                                        |                     | Propagation | Comn              | nercial                                   | Indu | strial |      |

|                           |                                        |                     |             | Delay (ns) Fanout |                                           | nout | Fanout |      |

| Name                      | Cells                                  | Description         | Symbol      | Fanout =2         | 2                                         | 4    | 2      | 4    |

| IBGATE                    |                                        | Large 2 Input NAND  | tpLH        | 0.34              | 0.88                                      | 1.02 | 0.92   | 1.02 |

| IBGATE                    | -                                      | Gate +2 Input NOR   | tpHL        | 0.27              | 0.71                                      | 0.84 | 0.75   | 0.88 |

| IBDF                      | -                                      | Master Slave D-type | tpLH        | 0.48              | 1.24                                      | 1.44 | 1.30   | 1.50 |

|                           | _                                      | Flip-Flop           | tpHL        | 0.50              | 1.31                                      | 1.42 | 1.37   | 1.49 |

| IBCMOS1 -                 | CMOS input buffer<br>with 2 input NAND | tpLH                | 0.60        | 1.58              | 1.68                                      | 1.65 | 1.75   |      |

| IBCMOS1                   | _                                      | gate                | tpLH        | 0.45              | 1.17                                      | 1.21 | 1.22   | 1.27 |

|                     |       |                           |             | Typical      | V       | Vorst case propa | agation Delay (na | 5)   |

|---------------------|-------|---------------------------|-------------|--------------|---------|------------------|-------------------|------|

| OUTPUT BUFFER CELLS |       |                           | Propagation | Comr         | nercial | Indu             | strial            |      |

| Num                 |       |                           | 0           | Delay (ns)   | Far     | nout             | Fan               | iout |

| Name                | Cells | Description               | Symbol      | Fanout =10pF | 10pF    | 50pF             | 10pF              | 50pF |

| OP3                 | 013 - | Standard Output<br>Buffer | tpLH        | 0.73         | 1.90    | 6.49             | 1.99              | 6.79 |

| 010                 |       |                           | tpHL        | 0.49         | 1.27    | 4.40             | 1.33              | 4.60 |

| OP6                 | -     | Medium Output<br>Buffer   | tpHL        | 0.50         | 1.30    | 3.59             | 1.35              | 3.76 |

|                     | 060 - |                           | tpLH        | 0.33         | 0.85    | 2.42             | 0.89              | 2.53 |

| OP12                |       | Large Output              | tpLH        | 0.38         | 0.99    | 2.14             | 1.04              | 2.24 |

| 0P12                | -     | Buffer                    | tpHL        | 0.25         | 0.66    | 1.50             | 0.69              | 1.56 |

Note : Commercial worst case is 4.5V, 70°C operating Industrial worst case is 4.5V, 85°C operating

# DC ELECTRICAL CHARACTERISTICS

All characteristics at Commercial Grade voltage and temperature (note1)

| Characteristic                                         | Symbol                             | Min.                  | Тур.                  | Max.    | Units  | Conditions                                             |

|--------------------------------------------------------|------------------------------------|-----------------------|-----------------------|---------|--------|--------------------------------------------------------|

| Low Level Input Voltage                                | V <sub>IL</sub>                    |                       |                       |         | V      |                                                        |

| TTL Inputs (IBTTL1/IBTTL2)                             | ۰IL                                |                       |                       | 0.80    | ,      |                                                        |

| CMOS Inputs (IBCMOS1/IBCMOS2)                          |                                    |                       |                       | 1.00    |        |                                                        |

|                                                        | V <sub>IH</sub>                    |                       |                       | 1.00    | V      |                                                        |

| High Level Input Voltage<br>TTL Inputs (IBTTL1/IBTTL2) | ¥ІН                                | 0.00                  |                       |         | v      |                                                        |

|                                                        |                                    | 2.00                  |                       |         |        |                                                        |

| CMOS Inputs (IBCMOS1/IBCMOS2)                          | V <sub>T+</sub>                    | V <sub>DD</sub> -1.00 | 0.00                  |         | V      |                                                        |

| Input Hysterisis (IBST1) Rising                        | v <sub>т+</sub><br>V <sub>т-</sub> |                       | 3.09                  |         | v      | $V_{\mu}$ to $V_{\mu}$                                 |

| Falling                                                |                                    |                       | 1.89                  |         |        | V <sub>IH</sub> to V <sub>IL</sub>                     |

| (IBST2) Rising                                         | V <sub>T+</sub>                    |                       | 1.72                  |         |        | V <sub>IL</sub> to V <sub>IH</sub>                     |

| Falling                                                | V <sub>T-</sub>                    |                       | 1.10                  |         |        | $V_{IH}$ to $V_{IL}$                                   |

| Input Current CMOS/TTL Inputs                          | I <sub>IN</sub>                    |                       |                       |         |        |                                                        |

| (without resistor)                                     |                                    | -1.00                 |                       | +1.00   | μA     | V <sub>IN</sub> =V <sub>DD</sub> OR V <sub>SS</sub>    |

| Inputs with 1K ohm resistor                            |                                    | ±2.20                 | ±5.00                 | ±11.00  | mA     | V <sub>IN</sub> =V <sub>DD</sub> OR V <sub>SS</sub>    |

| Inputs with 2K ohm resistor                            |                                    | ±1.10                 | ±2.50                 | ±5.50   | mA     | $V_{IN} = V_{DD} OR V_{SS}$                            |

| Inputs with 4K ohm resistor                            |                                    | ±0.56                 | ±1.25                 | ±2.75   | mA     | $V_{IN} = V_{DD} OR V_{SS}$                            |

| Inputs with 75K ohm resistor                           |                                    | ±18.00                | ±66.00                | ±275.00 | μΑ     | $V_{IN} = V_{DD} OR V_{SS}$                            |

| Resistor values nominal (note2)                        |                                    |                       |                       |         |        |                                                        |

| High Level Output Voltage                              | V <sub>OH</sub>                    |                       |                       |         | v      |                                                        |

| All Outputs                                            |                                    |                       | $V_{_{DD}}$ -0.05     |         |        | I <sub>он</sub> =-1.00µА                               |

| Smallest drive cell OP1/OPOS1/OPT1                     |                                    | V <sub>DD</sub> -1.00 | $V_{_{DD}}$ -0.50     |         |        | I <sub>он</sub> =-2.00mА                               |

| Low drive cell OP2/OPOS2/OPT2                          |                                    |                       | $V_{_{DD}}$ -0.50     |         |        | I <sub>он</sub> =-4.00mА                               |

| Standard drive cell OP3/OPOS3/OPT3                     |                                    | V <sub>DD</sub> -1.00 | $V_{_{DD}}$ -0.50     |         |        | I <sub>он</sub> =-6.00mА                               |

| Medium drive cell OP6/OPOS6,OPT6                       |                                    | V <sub>DD</sub> -1.00 | $V_{_{DD}}$ -0.50     |         |        | I <sub>он</sub> =-12.00mA                              |

| Large drive cell OP12/OPOS12/OPT12                     |                                    | V <sub>DD</sub> -1.00 | V <sub>DD</sub> -0.50 |         |        | I <sub>он</sub> =-24.00mА                              |

| Low Level Output Voltage                               | V <sub>OL</sub>                    |                       |                       |         | v      |                                                        |

| All Outputs                                            |                                    |                       | V <sub>ss</sub> +0.05 |         |        | Ι <sub>οL</sub> =1.00μΑ                                |

| Smallest drive cell OP1/OPOD1/OPT1                     |                                    |                       | 0.20                  | 0.40    |        | I <sub>oL</sub> =2.00mA                                |

| Low drive cell OP2/OPOD2/OPT2                          |                                    |                       | 0.20                  | 0.40    |        | I <sub>oL</sub> =4.00mA                                |

| Standard drive cell OP3/OPOD3/OPT3                     |                                    |                       | 0.20                  | 0.40    |        | I <sub>oL</sub> =6.00mA                                |

| Medium drive cell OP6/OPOD6,OPT6                       |                                    |                       | 0.20                  | 0.40    |        | I <sub>oL</sub> =12.00mA                               |

| Large drive cell OP12/OPOD12/OPT12                     |                                    |                       | 0.20                  | 0.40    |        | I <sub>oL</sub> =24.00mA                               |

| Tristate Output Leakage Current                        |                                    |                       |                       |         |        |                                                        |

|                                                        | I <sub>oz</sub>                    | -1.00                 |                       | 1.00    | μΑ     | $V_{OH} = V_{SS} \text{ or } V_{DD}$                   |