## MFT62340-J

### **Parallel Fiber Transmitter**

Preliminary Information

**Features**

- Data rate 155Mbps to 2.5Gbps per channel

- 12 parallel channels, total 30Gbps capacity

- Differential CML (Current-Mode Logic) interface

- Link length up to 300m (with 500MHz·km fiber)

- Channel BER 10<sup>-12</sup> when used with MFR62340

- Designed for multimode fiber ribbon

- MPO/MTP or MPX connector options

- Surface-mount package

- · Pick-and-placeable, reflow soldering

- Relaxed Class 1 IEC 60825-1 Amd. 2 compliant

- Matches the MFR62340 Receiver

- EMI shield available

DS5396 15094.00.10

ISSUE 1.2

Dec 2000

#### **Ordering Information**

MFT62340-JO MPO/MTP Connector MFT62340-JOS With EMI shield MFT62340-JX MPX Connector

#### **Applications**

- High-speed interconnects

- Switches, Routers, Transport equipment

- Interconnects within and between equipment

- Rack-to-rack

- · Shelf-to-shelf

- Board-to-board

- Board-to-optical backplane

#### **Description**

The MFT62340 and MFR62340 is a very high speed transmitter and receiver pair for parallel fiber applications. This pair, together with a multimode parallel fiber ribbon cable, constitute a complete parallel fiber link. The link provides high-speed interconnects for use within and between large capacity switches, routers and data transport equipment. The transmitter and receiver have a differential CML interface and support MPO/MTP and MPX fiber connectors. An EMI shield is available for the MPO/MTP connector for use in front panel applications.

Figure 1 - MFT62340-JO: MPO/MTP Connector Option

# **Absolute Maximum Ratings\***

|   | Parameter                           | Symbol           | Min  | Max                  | Unit |

|---|-------------------------------------|------------------|------|----------------------|------|

| 1 | Supply voltage                      | V <sub>CC</sub>  | -0.3 | 3.6                  | V    |

| 2 | Voltage on any pin                  | $V_{PIN}$        | -0.3 | V <sub>CC</sub> +0.3 | V    |

| 3 | Operating and storage moisture      | M <sub>OS</sub>  | 20   | 85                   | %    |

| 4 | Storage temperature                 | T <sub>STG</sub> | -20  | 100                  | °C   |

| 5 | ESD resistance all I/O except CML** | V <sub>E</sub>   | -2   | 2                    | kV   |

| 6 | ESD resistance CML I/O**            | V <sub>EC</sub>  | -500 | 500                  | V    |

<sup>\*</sup> Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

\*\* Human body model.

## **Recommended Operating Conditions\***

|   | Parameter                                              | Symbol                            | Min                | Max                | Unit       |

|---|--------------------------------------------------------|-----------------------------------|--------------------|--------------------|------------|

| 1 | Case temperature                                       | T <sub>CASE</sub>                 | 0                  | 80                 | °C         |

| 2 | Supply voltage                                         | V <sub>CC</sub>                   | 3.3-5%             | 3.3+5%             | V          |

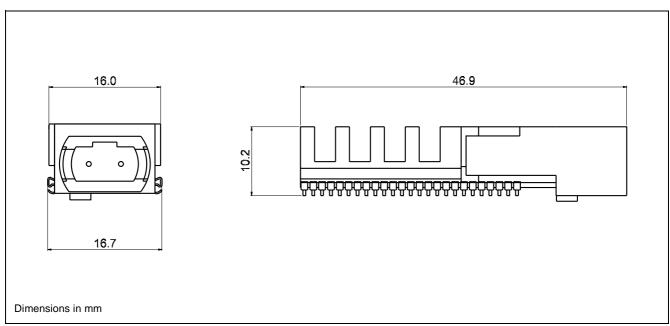

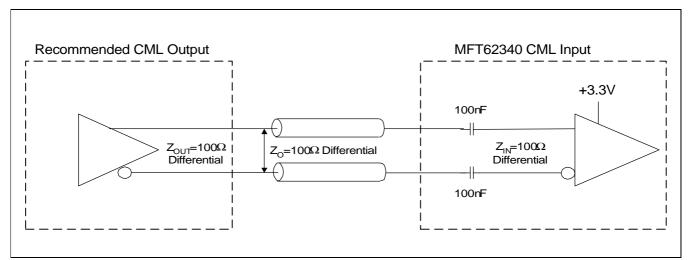

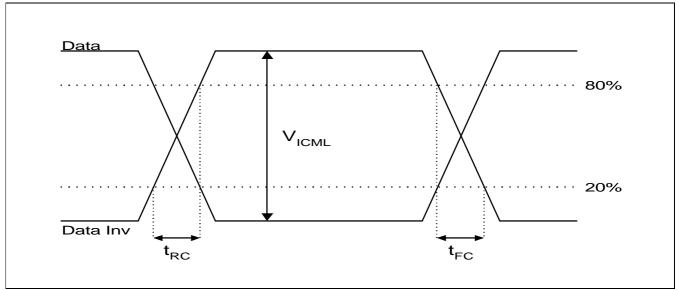

| 3 | CML differential input voltage (Fig. 2,3)              | V <sub>ICML</sub>                 | 200                | 800                | mV         |

| 4 | Data rate per channel                                  | f <sub>D</sub>                    | 0.155              | 2.5                | Gbps       |

| 5 | CML differential input rise/fall time (20-80%, Fig. 3) | t <sub>RC</sub> , t <sub>FC</sub> |                    | 160                | ps         |

| 6 | CMOS input voltage low                                 | V <sub>LCMOS</sub>                | 0                  | 30%V <sub>CC</sub> | V          |

| 7 | CMOS input voltage high                                | V <sub>HCMOS</sub>                | 70%V <sub>CC</sub> | V <sub>CC</sub>    | V          |

| 8 | Power supply noise (1MHz to 2GHz)                      | V <sub>NPS</sub>                  |                    | 100                | $mV_{p-p}$ |

<sup>\*</sup> Maximum run length: 72 consecutive 1's or 0's; DC balance to be maintained within 144 bits. Fiber: 50/125μm or 62.5/125μm.

### Characteristics\*

|    | Parameter                                         | Symbol                           | Min | Тур | Max  | Unit              |

|----|---------------------------------------------------|----------------------------------|-----|-----|------|-------------------|

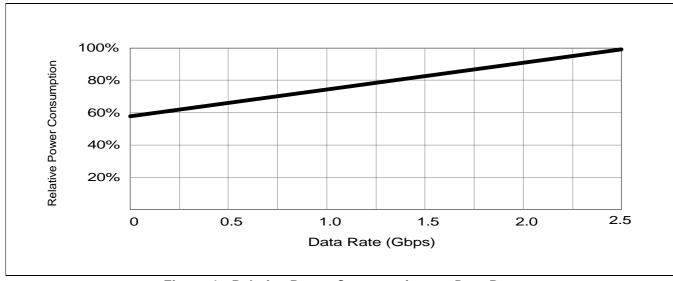

| 1  | Power consumption (2.5 Gbps, Fig. 4)              | P <sub>D</sub>                   |     | 1.8 | 2.4  | W                 |

| 2  | Power supply current                              | I <sub>CC</sub>                  |     | 580 |      | mA                |

| 3  | CML differential input impedance (Fig. 2)         | Z <sub>IN</sub>                  | 80  | 100 | 120  | Ω                 |

| 4  | Optical rise/fall time (20-80%)                   | t <sub>RO,</sub> t <sub>FO</sub> |     |     | 130  | ps                |

| 5  | Average fiber output power per channel            | P <sub>F</sub>                   | -7  |     | -3   | dBm               |

| 6  | Deterministic jitter                              | DJ                               |     |     | 50   | ps <sub>p-p</sub> |

| 7  | Random jitter (ER = 6dB)                          | RJ                               |     |     | 5.2  | ps <sub>rms</sub> |

| 8  | Optical wavelength                                | λ                                | 830 | 840 | 860  | nm                |

| 9  | Spectral width                                    | Δλ                               |     |     | 0.85 | nm                |

| 10 | Extinction ratio                                  | ER                               | 6   |     |      | dB                |

| 11 | NMOS output voltage low (I <sub>sink</sub> = 3mA) | V <sub>LNMOS</sub>               |     |     | 0.4  | V                 |

| 12 | NMOS output voltage high                          | V <sub>HNMOS</sub>               | 2.4 |     |      | V                 |

| 13 | Channel skew                                      | t <sub>SK</sub>                  |     |     | 175  | ps                |

| 14 | Relative intensity noise                          | RIN                              | -   |     | -118 | dB/Hz             |

<sup>\*</sup> Operating conditions are as per Recommended Operating Conditions. Test pattern PRBS 2<sup>31</sup>-1 at 2.5Gbps and 50% duty cycle unless otherwise specified.

Figure 2 - Differential CML Interface

Figure 3 - Differential CML Timing Diagram

Figure 4 - Relative Power Consumption vs. Data Rate

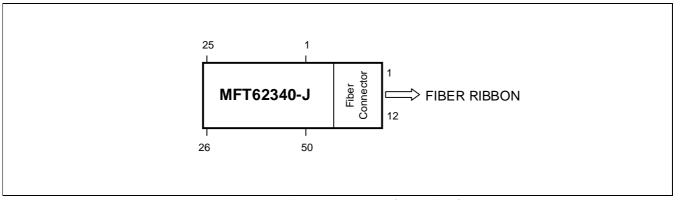

Figure 5 - Pin Assignment (Top View)

## **Pin Description**

| No | Name                | Logic | Description                         |

|----|---------------------|-------|-------------------------------------|

| 1  | Gnd                 |       | Ground                              |

| 2  | V <sub>cc</sub>     |       | Positive power supply               |

| 3  | V <sub>cc</sub>     |       | Positive power supply               |

| 4  | V <sub>EN1-4</sub>  | CMOS  | VCSELs enable ch. 1-41              |

| 5  | $V_{EN5^{-8}}$      | CMOS  | VCSELs enable ch. 5-8 <sup>1</sup>  |

| 6  | V <sub>EN9-12</sub> | CMOS  | VCSELs enable ch. 9-12 <sup>1</sup> |

| 7  | Gnd                 |       | Ground                              |

| 8  | DI1C                | CML   | Data input No 1, inv.               |

| 9  | DI1                 | CML   | Data input No 1.                    |

| 10 | Gnd                 |       | Ground                              |

| 11 | DI2C                | CML   | Data input No 2, inv.               |

| 12 | DI2                 | CML   | Data input No 2.                    |

| 13 | Gnd                 |       | Ground                              |

| 14 | DI3C                | CML   | Data input No 3, inv.               |

| 15 | DI3                 | CML   | Data input No 3.                    |

| 16 | Gnd                 |       | Ground                              |

| 17 | DI4C                | CML   | Data input No 4, inv.               |

| 18 | DI4                 | CML   | Data input No 4.                    |

| 19 | Gnd                 |       | Ground                              |

| 20 | DI5C                | CML   | Data input No 5, inv.               |

| 21 | DI5                 | CML   | Data input No 5.                    |

| 22 | Gnd                 |       | Ground                              |

| 23 | DI6C                | CML   | Data input No 6, inv.               |

| 24 | DI6                 | CML   | Data input No 6.                    |

| 25 | Gnd                 |       | Ground                              |

| No | Name            | Logic | Description                  |

|----|-----------------|-------|------------------------------|

| 50 | Gnd             |       | Ground                       |

| 49 | V <sub>cc</sub> |       | Positive power supply        |

| 48 | V <sub>cc</sub> |       | Positive power supply        |

| 47 | NFLT            | NMOS  | Fault detection <sup>2</sup> |

| 46 |                 |       | Not Connected                |

| 45 |                 |       | Not Connected                |

| 44 | Gnd             |       | Ground                       |

| 43 | DI12            | CML   | Data input No 12.            |

| 42 | DI12C           | CML   | Data input No 12, inv.       |

| 41 | Gnd             |       | Ground                       |

| 40 | DI11            | CML   | Data input No 11.            |

| 39 | DI11C           | CML   | Data input No 11, inv.       |

| 38 | Gnd             |       | Ground                       |

| 37 | DI10            | CML   | Data input No 10.            |

| 36 | DI10C           | CML   | Data input No 10, inv.       |

| 35 | Gnd             |       | Ground                       |

| 34 | DI9             | CML   | Data input No 9.             |

| 33 | DI9C            | CML   | Data input No 9, inv.        |

| 32 | Gnd             |       | Ground                       |

| 31 | DI8             | CML   | Data input No 8.             |

| 30 | DI8C            | CML   | Data input No 8, inv.        |

| 29 | Gnd             |       | Ground                       |

| 28 | DI7             | CML   | Data input No 7.             |

| 27 | DI7C            | CML   | Data input No 7, inv.        |

| 26 | Gnd             |       | Ground                       |

<sup>&</sup>lt;sup>1</sup>High = Lasers active. Internal pull-down resistor 50kΩ.

$<sup>^{2}</sup>$ Low = Driver not ready. Open drain with internal pull-up resistor 10k $\Omega$ .

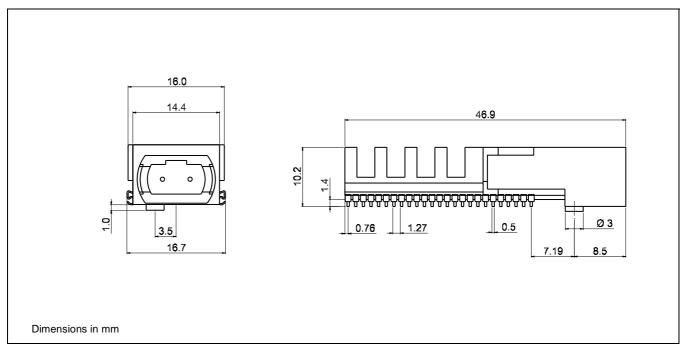

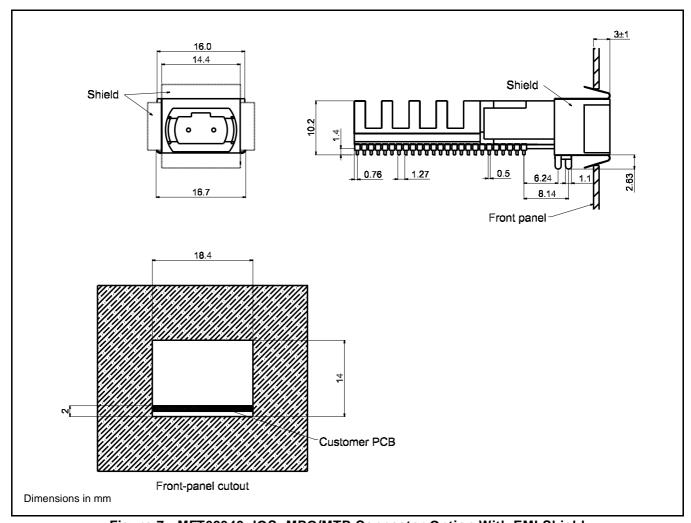

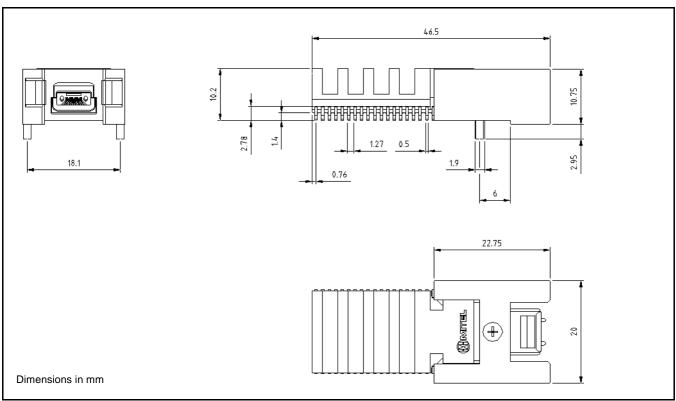

## **Mechanical Drawings**

Figure 6 - MFT62340-JO: MPO/MTP Connector Option

Figure 7 - MFT62340-JOS: MPO/MTP Connector Option With EMI Shield

Figure 8 - MFT62340-JX: MPX Connector Option

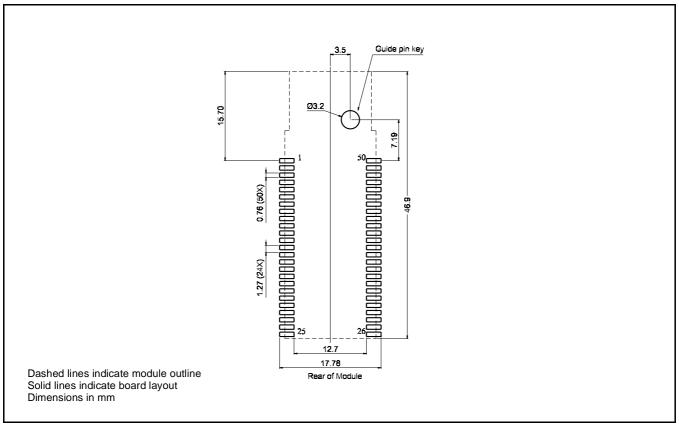

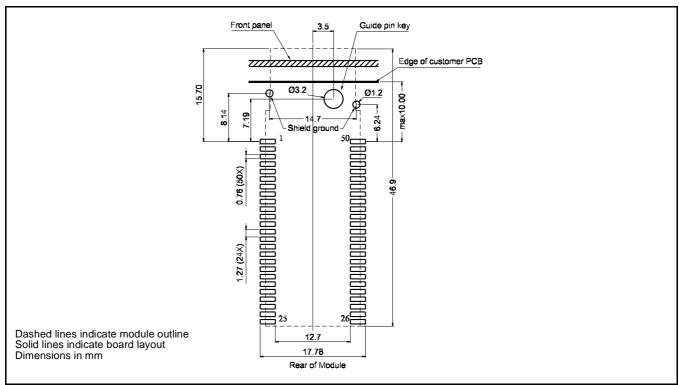

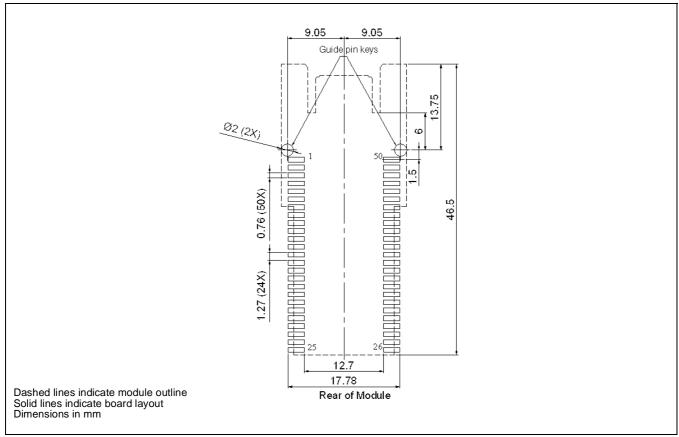

# **PCB** Footprints

Figure 9 - MFT62340-JO: MPO/MTP Connector Option (Top View)

Figure 10 - MFT62340-JOS: MPO/MTP Connector Option With EMI Shield (Top View)

Figure 11 - MFT62340-JX: MPX Connector Option (Top View)

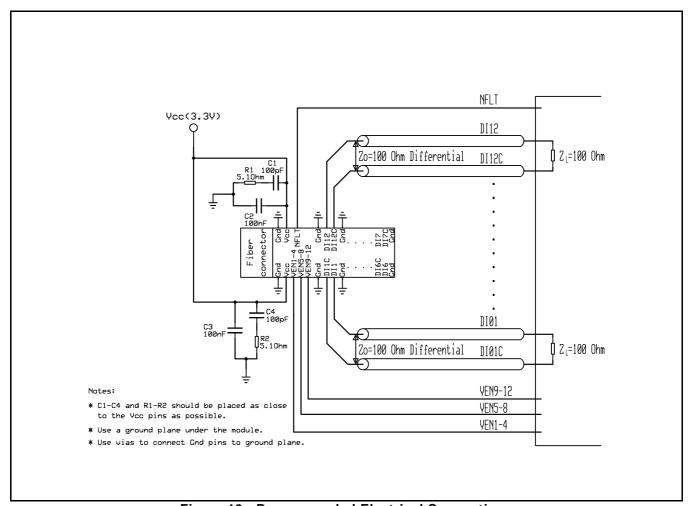

### **Electrical Connections**

Figure 12 - Recommended Electrical Connections

http://www.mitelsemi.com

World Headquarters - Canada

Tel: +1 (613) 592 2122 Fax: +1 (613) 592 6909

Asia/Pacific

Tel: +65 333 6193 Fax: +65 333 6192 Europe, Middle East, and Africa (EMEA)

Tel: +44 (0) 1793 518528 Fax: +44 (0) 1793 518581

Information relating to products and services furnished herein by Mitel Corporation or its subsidiaries (collectively "Mitel") is believed to be reliable. However, Mitel assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Mitel or licensed from third parties by Mitel, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Mitel, or non-Mitel furnished goods or services may infringe patents or other intellectual property rights owned by Mitel.

This publication is issued to provide information only and (unless agreed by Mitel in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Mitel without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Mitel's conditions of sale which are available on request.

M Mitel (design) and ST-BUS are registered trademarks of MITEL Corporation Mitel Semiconductor is an ISO 9001 Registered Company Copyright 1999 MITEL Corporation All Rights Reserved Printed in CANADA

**North America**

Tel: +1 (770) 486 0194

Fax: +1 (770) 631 8213