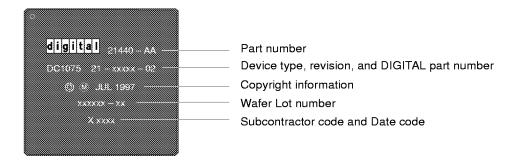

# 1 DIGITAL Semiconductor 21440 Overview

The DIGITAL Semiconductor 21440 Multiport 10/100Mbps Ethernet Controller (also called the 21440) provides eight 10/100-Mb/s intelligent, high-performance MAC ports. It includes network management support and is optimized for switch applications.

# 1.1 General Description

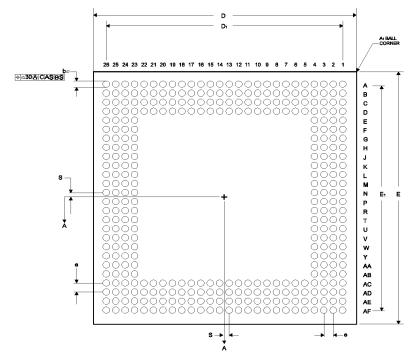

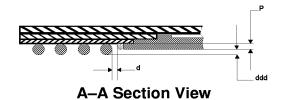

The 21440 Multiport Ethernet Controller includes eight independent 10/100-Mb/s Ethernet MACs and interfaces directly to MII standard PHYs or SYM 100BASE-TX physical devices. The 21440 handles SNMP and RMON management counter sets, accessible through a generic CPU interface, which is also used for mode programming. Each MAC includes two 256-byte independent FIFOs for packet transmit and receive. All the packets are transferred onto a high-performance, common FIFO interface. The 21440 is fully compatible with IEEE standards, including Fast Ethernet and flow-control support. It is implemented in a low-power 3.3V CMOS device within a 352-BGA package.

# 1.2 Integration Features

The 21440:

- Offers eight Ethernet 10/100-Mb/s MAC ports

- Includes onchip scrambler, descrambler, and PCS functions for 100BASE-X connections

- Handles SNMP and RMON counters

#### 1.3 FIFO Bus Features

The 21440:

- Supports a 4-Gb/s high bus bandwidth

- Offers a variable bus speed of 25 to 66 MHz, operational, for testing, from 16 MHz

- Interfaces a 64-bit bus with a 32-bit optional mode

- Provides transmit- and receive-independent 256-byte FIFOs for each port

- Offers a generic slave FIFO interface

#### **Performance Features**

- Supports little or big endian byte ordering

- Supports transmit and receive byte alignment

- Supports receive packet fragmentation on byte boundaries (replay feature)

- Provides programmable transmit and receive bus thresholds

- Appends packet status to received packet

#### 1.4 Performance Features

The 21440:

- Allows no CPU intervention during packet transfer

- Enables early address filtering ability, with packet header preprocessing and VLAN detection ability

- Offers retry or ignore options following packet transmission errors

- Supports automatic retransmission following excessive collisions

- Provides programmable automatic discard of badly received packets such as runts, CRC errors, and too long packets

#### 1.5 Serial Features

The 21440:

- Enables independent 10- or 100-Mb/s port operation

- Provides full-duplex support

- Enables standard flow-control functionality in full-duplex mode

- Offers backpressure logic capability

- Interfaces standard MII connections

- Supports 10BASE-T, 100BASE-TX, 100BASE-T4, and 100BASE-FX connections

- Provides programmable CRC generation and removal

- Allows backoff limit programming

- Provides full collision support, including jamming, backoff, and automatic retransmission

- 2 DIGITAL Semiconductor 21440 Overview

#### **CPU Interface Features**

• Complies with IEEE 802.3 Standard

#### 1.6 CPU Interface Features

The 21440:

- Supports fully programmable independent ports through a dedicated generic CPU port

- Enables interrupt programming

#### 1.7 Device Features

The 21440:

- Is optimized for switch, bridge, and router applications

- Includes internal and external loopback capabilities

- Provides software reset support

- Supports JTAG boundary scan

- Is implemented in a low-power 3.3 V and 5 V tolerant CMOS device

- Is provided in a 352-BGA package

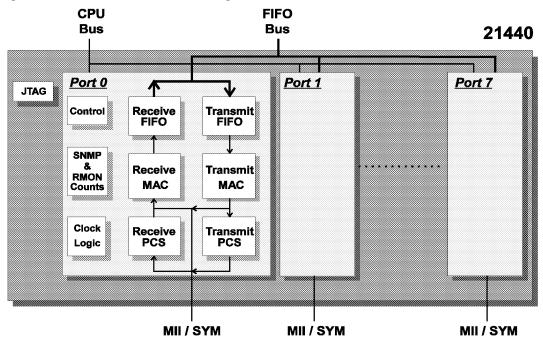

# 21440 Block Diagram

# 1.8 21440 Block Diagram

Figure 1 shows the 21440 controller block diagram.

Figure 1 21440 Controller Block Diagram

4 DIGITAL Semiconductor 21440 Overview

#### **Hardware Overview**

#### 1.9 Hardware Overview

Table 1 describes the 21440 components.

Table 1 21440 Components Description

| Component     | Description                                                                                                                                         |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit FIFO | Handles the transmitted packets while taking care of retransmission in case of collision. The transmit FIFO has direct interface to the FIFO bus.   |

| Receive FIFO  | Handles the received packets and supports packet deletion in case of errors. The receive FIFO has direct interface to the FIFO bus.                 |

| Transmit MAC  | Implements the IEEE 802.3 transmit MAC functions while interfacing between the transmit FIFO and the front-end ENDEC, providing full MII interface. |

| Receive MAC   | Implements the IEEE 802.3 receive MAC functions while interfacing between the front-end ENDEC through MII interface and the receive FIFO.           |

| PCS           | ENDEC implementing the 100BASE-X PCS layer, including the 100BASE-TX scrambler/descrambler function.                                                |

| SNMP and RMON | Handles network statistic counters for SNMP and RMON.                                                                                               |

| Control       | Handles the chip registers accessible through the CPU bus.                                                                                          |

| Clock Logic   | Generates the clocks required by the chip.                                                                                                          |

| JTAG          | Includes the JTAG boundary scan logic.                                                                                                              |

# 2 Pinout

This chapter describes the 21440 pinout.

# 2.1 Signal Description

Table 2 describes the signals that the 21440 uses.

The following conventions are used in the signal names:

\_l: Indicates that the pin is active low.

**(i):** The i subscript appended to pin names indicates that each port has its own pin (numbered from 0 to 7).

The following abbreviations are used in Table 2:

I = Input

O = Output

OD = Open Drain

I/O = Input/Output

**Table 2 Signal Descriptions**

(Sheet 1 of 6)

| Signal Name      | I/O | Pin Description                                                                                                                                                                   |

|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU<br>Interface |     |                                                                                                                                                                                   |

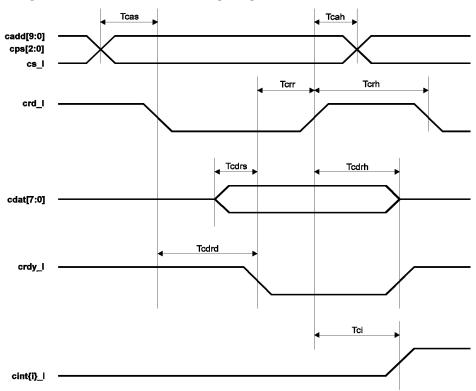

| cs_l             | I   | Chip select. This pin must be asserted to enable CPU access to the chip registers.                                                                                                |

| cps[2:0]         | Ι   | <b>CPU port select.</b> Selects one of the 8 internal ports for register accesses.                                                                                                |

| crd_l            | I   | Read strobe. Upon assertion, the address signals cadd[9:0], cs_l, and cps[2:0] are latched by the chip. Deassertion occurs after the read data is latched from the cdat[7:0] bus. |

| Table  | 2.9 | idnal  | Descri | ntions        |

|--------|-----|--------|--------|---------------|

| I abic |     | ngilai | DC3011 | <b>DUDII3</b> |

(Sheet 2 of 6)

| Signal Name       | I/O | Pin Description                                                                                                                                                                                                     |  |  |

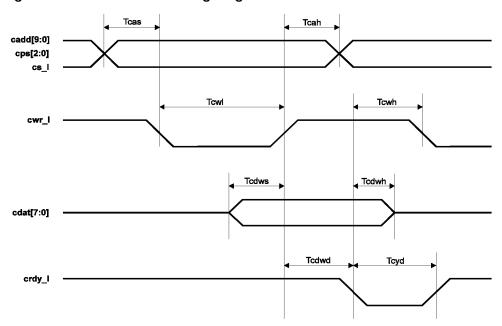

|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| cwr_l             | I   | Write strobe. Upon assertion, the address signals cadd[9:0], cs_1, and cps[2:0] are latched by the chip. Deassertion must occur while the data is valid on the cdat[7:0] bus.                                       |  |  |

| crdy_l            | OD  | Ready indication. When asserted, indicates that either data is stable on the cdat[7:0] bus during read access or that data was latched by the chip during write access.                                             |  |  |

| cadd[9:0]         | Ι   | Address bus. Selects one of the internal registers to be accessed.                                                                                                                                                  |  |  |

| cdat[7:0]         | I/O | CPU data bus. Carries data to be written to or read from the registers.                                                                                                                                             |  |  |

| cint{i}_l         | OD  | Interrupt lines. These signals are asserted following a variety of programmable conditions. Deassertion occurs after reading the events that cause the interrupt, unless another interrupt is registered meanwhile. |  |  |

| reset_l           | I   | General reset. Upon reset, all the registers are reset to their default values and the FIFOs are flushed.                                                                                                           |  |  |

| FIFO<br>Interface |     |                                                                                                                                                                                                                     |  |  |

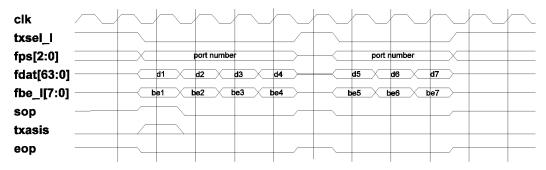

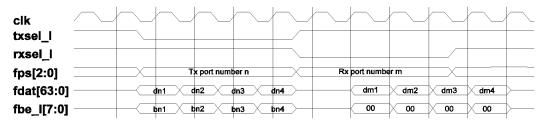

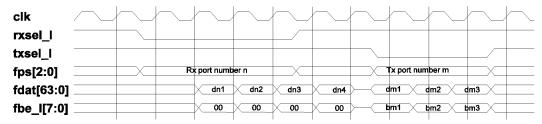

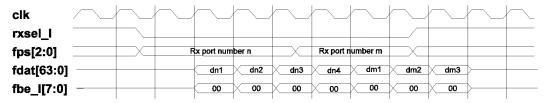

| clk               | I   | System clock. All the FIFO data transfers are synchronized to this clock.                                                                                                                                           |  |  |

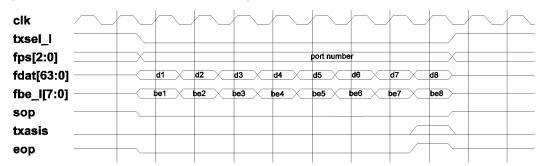

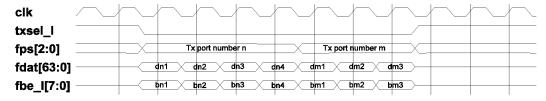

| txsel_l           | Ι   | <b>Transmit select.</b> This pin must be asserted to enable transmit FIFO write access.                                                                                                                             |  |  |

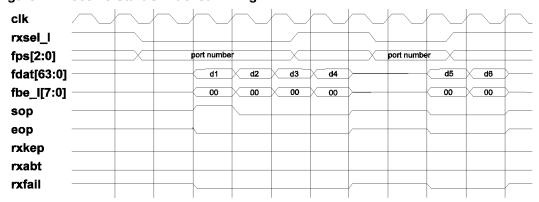

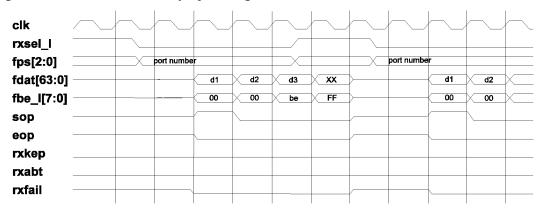

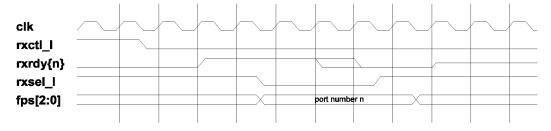

| rxsel_l           | I   | Receive select. This pin must be asserted to enable receive FIFO read access. The following signals are driven upon assertion of rxsel_l: fdat[63:0], fbe_I[7:0], sop, eop and rxfail.                              |  |  |

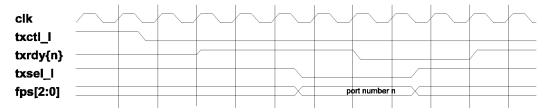

| fps[2:0]          | I   | FIFO port select. Selects one of the port FIFOs for data transfer.                                                                                                                                                  |  |  |

| fdat[63:0]        | I/O | FIFO data bus. Carries the data to be written to the transmit FIFO or read from the receive FIFO of the selected port.                                                                                              |  |  |

**Table 2 Signal Descriptions**

(Sheet 3 of 6)

| Signal Name  | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fbe_l[7:0]   | I/O | FIFO byte enable. During transmit, indicates which of the bytes driven onto fdat[63:0] contain valid data (valid bytes need to be contiguous and at least one byte must be valid). During receive, indicates which bytes are valid. Each fbe_l signal relates to a different fdat byte (for example, fbe_l[0] relates to fdat[7:0] and fbe_l[5] relates to fdat[47:40]).                                                              |

| rxkep        | I   | Receive keep.  When asserted, this signal causes the last read data to be kept in the receive FIFO. May be asserted only with rxsel_l assertion.                                                                                                                                                                                                                                                                                      |

| sop          | I/O | Start of packet.  When asserted during transmit, indicates that the first data in the packet is written to the transmit FIFO. During receive, this signal is asserted when the first data of the packet is read from the receive FIFO.                                                                                                                                                                                                |

| еор          | I/O | End of packet.  When asserted during transmit, indicates that the final data in the packet is written to the transmit FIFO. During receive, eop is asserted when the final data of the packet is read from the receive FIFO. In the following FIFO access, the packet status is driven onto the bus.                                                                                                                                  |

| txasis/txerr | I   | Transmit as is/Transmit error.  When asserted during transmit, upon transfer of the packet's first data (together with sop assertion), no padding and/or CRC is appended to the packet even if the port was programmed to do so. When asserted upon transfer of the packet's final data (together with eop assertion), the packet is transmitted with an MII error (if the port is programmed to append CRC) and with a symbol error. |

| rxfail       | 0   | Receive packet failure.  This signal is asserted if a packet was received with errors, had started to appear on the FIFO bus, and was discarded from the receive FIFO.                                                                                                                                                                                                                                                                |

| rxabt        | I   | Receive abort.  This signal forces a received packet to be aborted and flushed from the receive FIFO. May be asserted only with rxsel_l assertion.                                                                                                                                                                                                                                                                                    |

**Table 2 Signal Descriptions**

(Sheet 4 of 6)

| Signal Name | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| flet{i}     | I   | Flow control.  When asserted in the half-duplex mode, a collision is generated on each received packet. When asserted in the full-duplex mode, a flow-control packet with the programmed pause time is transmitted. Upon deassertion, a flow-control packet with time equal to 0 is sent if programmed accordingly.                                                                                                 |

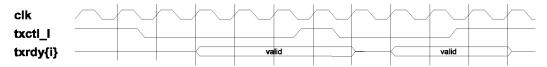

| txctl_l     | I   | Transmit control enable.  When asserted, this pin enables the txrdy{i} output drivers to report the transmit FIFO status.                                                                                                                                                                                                                                                                                           |

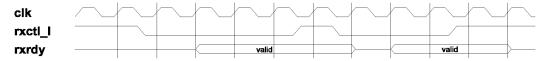

| rxctl_l     | I   | Receive control enable.  When asserted, this pin enables the rxrdy{i} output drivers to report the receive FIFO status.                                                                                                                                                                                                                                                                                             |

| txrdy{i}    | Ο   | Transmit FIFO ready. Indicates whether there is enough available space in the transmit FIFO to load data according to the programmable threshold value. Following transmission stop due to an error, the txrdy signal remains deasserted until the transmit error status is read.                                                                                                                                   |

| rxrdy{i}    | 0   | Receive FIFO ready. Indicates whether there is enough available data in the receive FIFO to be stored according to the programmable threshold value or if the end of the transferred packet is in the FIFO. The rxrdy signal may also be asserted when the packet header is in the FIFO. rxrdy can also be asserted to report packet discard from the receive FIFO due to an error together with the rxfail signal. |

| Vdd_clmp    | I   | Vdd clamp. Should be connected to the power of the highest signal level used on the FIFO bus.                                                                                                                                                                                                                                                                                                                       |

| Table 2 | Signal | <b>Descriptions</b> |

|---------|--------|---------------------|

|---------|--------|---------------------|

(Sheet 5 of 6)

| Signal Name            | I/O | Pin Descripti | on                                                                                     |  |  |

|------------------------|-----|---------------|----------------------------------------------------------------------------------------|--|--|

| MII / SYM<br>Interface |     |               |                                                                                        |  |  |

|                        | •   |               | ions according to the port mode: MII or SYM. See apter 6, Network Interface Operation. |  |  |

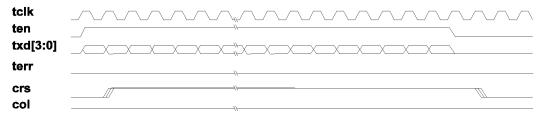

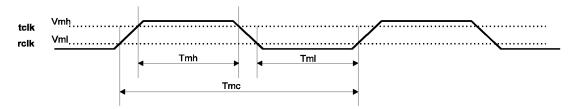

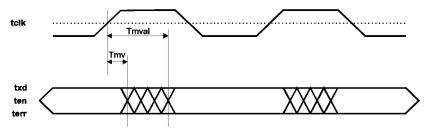

| tclk{i}                | I   | Transmit cloc | Transmit clock.                                                                        |  |  |

| txd{i}[3:0]            | O   | MII mode:     | Nibble transmit data.                                                                  |  |  |

|                        |     | SYM mode:     | Four low bits of the encoded transmit data.                                            |  |  |

| $ten\{i\}/txd\{i\}[4]$ | Ο   | MII mode:     | Transmit enable signal.                                                                |  |  |

|                        |     | SYM mode:     | The fifth bit of the encoded transmit data.                                            |  |  |

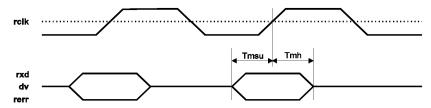

| rclk{i}                | I   | Receive recov | vered clock.                                                                           |  |  |

| rxd{i}[3:0] I          |     | MII mode:     | Nibble receive data.                                                                   |  |  |

|                        |     | SYM mode:     | Four low bits of the encoded received data.                                            |  |  |

| $dv\{i\}/rxd\{i\}[4]$  | I   | MII mode:     | Receive enable signal.                                                                 |  |  |

|                        |     | SYM mode:     | The fifth bit of the encoded received data.                                            |  |  |

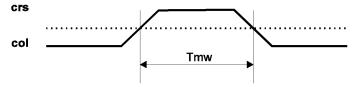

| col{i}/act{i}          | I/O | MII mode:     | Collision detection signal (input).                                                    |  |  |

|                        |     | SYM mode:     | Activity indication (output).                                                          |  |  |

| $crs\{i\}/sd\{i\}$     | I   | MII mode:     | Carrier detection signal.                                                              |  |  |

|                        |     | SYM mode:     | Signal detection indicating link status.                                               |  |  |

| rerr{i}                | I   | MII mode:     | Receive error signal.                                                                  |  |  |

|                        |     | SYM mode:     | Must be connected to 0.                                                                |  |  |

| terr{i}/lnk{i}         | O   | MII mode:     | Transmit error signal.                                                                 |  |  |

|                        |     | SYM mode:     | Link indication.                                                                       |  |  |

| mdc                    | O   | MII managem   | nent clock.                                                                            |  |  |

| mdio                   | I/O | MII managem   | MII management input/output serial data.                                               |  |  |

**Table 2 Signal Descriptions**

(Sheet 6 of 6)

| Signal Name       | I/O | Pin Description                                                             |

|-------------------|-----|-----------------------------------------------------------------------------|

| JTAG<br>Interface |     |                                                                             |

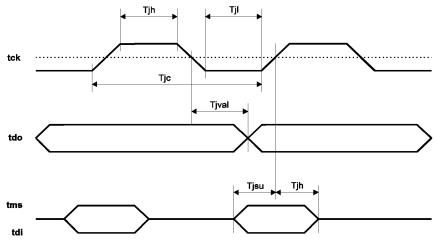

| tck               | I   | JTAG clock. If this pin is not used, it must be connected to 0.             |

| tms               | Ι   | JTAG test mode. If this pin is not used, it must be connected to 1.         |

| tdi               | I   | JTAG data serial input. If this pin is not used, it must be connected to 1. |

| tdo               | О   | JTAG data serial output.                                                    |

# 2.2 Pin Count

Table 3 summarizes the 21440 pin count.

Table 3 21440 Pin Count

|           | Common | Per Port | Total |

|-----------|--------|----------|-------|

| CPU       | 26     | 1        | 34    |

| FIFO      | 87     | 3        | 111   |

| MII/SYM   | 2      | 16       | 130   |

| JTAG      | 4      | _        | 4     |

| Total i/o | 119    | 20       | 279   |

| Gnd       | 28     |          | 28    |

| Vdd       | 24     |          | 24    |

| Reserved  | 21     |          | 21    |

| Total     |        |          | 352   |

# 2.3 Connection Rules

- All the reserved pins must remain unconnected.

- All the OD (Open Drain) signals must be connected to a pull-up device.

- All signals connected to a fixed value should be connected through a resistive device.

# 2.4 Pin List

Table 4 lists the 21440 pins and their associated names.

Table 4 Pin List (Sheet 1 of 5)

| Pin<br>Number | Pin Name | Pin<br>Number | Pin Name | Pin<br>Number | Pin Name |

|---------------|----------|---------------|----------|---------------|----------|

| <b>A</b> 1    | Gnd      | B1            | Gnd      | <b>C</b> 1    | sop      |

| A2            | Gnd      | B2            | Vdd      | C2            | Gnd      |

| A3            | fdat[0]  | В3            | Gnd      | C3            | Vdd      |

| A4            | fdat[4]  | B4            | fdat[1]  | C4            | RESERVED |

| A5            | fdat[8]  | В5            | fdat[5]  | C5            | fdat[2]  |

| A6            | fdat[12] | В6            | fdat[9]  | C6            | fdat[6]  |

| A7            | fdat[15] | В7            | fdat[13] | C7            | fdat[10] |

| A8            | fdat[19] | B8            | fdat[16] | C8            | fdat[14] |

| A9            | fdat[22] | В9            | fdat[20] | C9            | fdat[17] |

| A10           | fdat[26] | B10           | fdat[24] | C10           | fdat[21] |

| A11           | fdat[29] | B11           | fdat[27] | <b>C</b> 11   | fdat[25] |

| A12           | txsel_l  | B12           | fdat[31] | C12           | fdat[30] |

| A13           | Gnd      | B13           | rxsel_l  | C13           | RESERVED |

| A14           | Gnd      | B14           | RESERVED | C14           | RESERVED |

| A15           | clk      | B15           | fdat[32] | C15           | fdat[33] |

| A16           | fdat[34] | B16           | fdat[36] | C16           | fdat[38] |

| A17           | fdat[37] | B17           | fdat[39] | C17           | fdat[42] |

| A18           | fdat[41] | B18           | fdat[43] | C18           | fdat[46] |

| A19           | fdat[44] | B19           | fdat[47] | C19           | fdat[49] |

| A20           | fdat[48] | B20           | fdat[50] | C20           | fdat[53] |

| A21           | fdat[51] | B21           | fdat[54] | C21           | fdat[57] |

| A22           | fdat[55] | B22           | fdat[58] | C22           | fdat[61] |

| A23           | fdat[59] | B23           | fdat[62] | C23           | RESERVED |

| A24           | fdat[63] | B24           | Gnd      | C24           | Vdd      |

| A25           | Gnd      | B25           | Vdd      | C25           | Gnd      |

| A26           | Gnd      | B26           | Gnd      | C26           | fps[0]   |

|               |          |               |          |               |          |

Table 4 Pin List (Sheet 2 of 5)

| Pin<br>Number | Pin Name | Pin<br>Number | Pin Name                | Pin<br>Number | Pin Name |

|---------------|----------|---------------|-------------------------|---------------|----------|

| D1            | fbe_l[6] | E4            | RESERVED                | J1            | cdat[4]  |

| D2            | eop      | E23           | RESERVED                | J2            | cdat[6]  |

| D3            | RESERVED | E24           | <b>fps</b> [ <b>2</b> ] | Ј3            | cint1_l  |

| D4            | Vdd      | E25           | rxfail                  | J4            | Vdd      |

| D5            | RESERVED | E26           | txctl_l                 | J23           | Vdd      |

| D6            | fdat[3]  | F1            | cint6_l                 | J24           | txrdy7   |

| D7            | fdat[7]  | F2            | fbe_l[1]                | J25           | rxrdy2   |

| D8            | fdat[11] | F3            | fbe_l[4]                | J26           | rxrdy4   |

| D9            | Vdd      | F4            | fbe_l[7]                | <b>K</b> 1    | cdat[0]  |

| D10           | fdat[18] | F23           | txasis /txerr           | K2            | cdat[2]  |

| D11           | fdat[23] | F24           | rxkep                   | K3            | cdat[5]  |

| D12           | fdat[28] | F25           | rxctl_l                 | K4            | cint0_l  |

| D13           | RESERVED | F26           | txrdy2                  | K23           | rxrdy0   |

| D14           | Vdd      | G1            | cint3_l                 | K24           | rxrdy3   |

| D15           | fdat[35] | G2            | cint5_l                 | K25           | rxrdy6   |

| D16           | fdat[40] | G3            | fbe_1[0]                | K26           | flet0    |

| D17           | fdat[45] | G4            | fbe_l[3]                | L1            | crd_l    |

| D18           | Vdd      | G23           | rxabt                   | L2            | crdy_l   |

| D19           | fdat[52] | G24           | txrdy0                  | L3            | cdat[1]  |

| D20           | fdat[56] | G25           | txrdy3                  | L4            | cdat[3]  |

| D21           | fdat[60] | G26           | txrdy5                  | L23           | rxrdy5   |

| D22           | RESERVED | H1            | cdat[7]                 | L24           | rxrdy7   |

| D23           | Vdd      | H2            | cint2_l                 | L25           | flet1    |

| D24           | RESERVED | Н3            | cint4_l                 | L26           | flet3    |

| D25           | fps[1]   | H4            | cint7_l                 | <b>M</b> 1    | cps[1]   |

| D26           | RESERVED | H23           | txrdy1                  | M2            | cps[2]   |

| E1            | fbe_l[2] | H24           | txrdy4                  | M3            | cs_l     |

| E2            | fbe_l[5] | H25           | txrdy6                  | M4            | cwr_l    |

| E3            | Vdd_clmp | H26           | rxrdy1                  | M23           | flet2    |

Table 4 Pin List (Sheet 3 of 5)

|               | 2.00          |               |              |               | (8/1001 0 01 0) |

|---------------|---------------|---------------|--------------|---------------|-----------------|

| Pin<br>Number | Pin Name      | Pin<br>Number | Pin Name     | Pin<br>Number | Pin Name        |

| M24           | flet4         | Т3            | mdio         | W26           | txd7[2]         |

| M25           | flet5         | T4            | col0/act0    | <b>Y</b> 1    | rclk0           |

| M26           | flet6         | T23           | ten7/txd7[4] | Y2            | dv0/rxd0[4]     |

| <b>N</b> 1    | Gnd           | T24           | rerr7        | Y3            | rxd0[2]         |

| N2            | cadd[9]       | T25           | dv7/rxd7[4]  | Y4            | col1/act1       |

| N3            | <b>cps[0]</b> | T26           | rxd7[1]      | Y23           | terr6/lnk6      |

| N4            | Vdd           | <b>U</b> 1    | mdc          | Y24           | dv6/rxd6[4]     |

| N23           | flet7         | U2            | crs0/sd0     | Y25           | rxd6[1]         |

| N24           | reset_l       | U3            | txd0[2]      | Y26           | rxd6[3]         |

| N25           | tdo           | U4            | txd0[0]      | AA1           | rxd0[0]         |

| N26           | Gnd           | U23           | txd7[3]      | AA2           | rxd0[3]         |

| P1            | Gnd           | U24           | txd7[0]      | AA3           | txd1[3]         |

| P2            | cadd[8]       | U25           | terr7/lnk7   | AA4           | txd1[0]         |

| P3            | cadd[7]       | U26           | rclk7        | AA23          | txd6[2]         |

| P4            | cadd[6]       | <b>V</b> 1    | txd0[3]      | AA24          | ten6/txd6[4]    |

| P23           | Vdd           | V2            | txd0[1]      | AA25          | rerr6           |

| P24           | tms           | V3            | ten0/txd0[4] | AA26          | rclk6           |

| P25           | tdi           | V4            | Vdd          | AB1           | crs1/sd1        |

| P26           | Gnd           | V23           | Vdd          | AB2           | txd1[2]         |

| R1            | cadd[5]       | V24           | col7/act7    | AB3           | terr1/lnk1      |

| R2            | cadd[4]       | V25           | txd7[1]      | AB4           | RESERVED        |

| R3            | cadd[3]       | V26           | telk7        | AB23          | RESERVED        |

| R4            | cadd[1]       | $\mathbf{W}1$ | telk0        | AB24          | txd6[3]         |

| R23           | rxd7[0]       | <b>W</b> 2    | terr0/lnk0   | AB25          | txd6[0]         |

| R24           | rxd7[2]       | <b>W</b> 3    | rerr0        | AB26          | telk6           |

| R25           | rxd7[3]       | <b>W</b> 4    | rxd0[1]      | AC1           | txd1[1]         |

| R26           | tck           | W23           | rxd6[0]      | AC2           | ten1/txd1[4]    |

| T1            | cadd[2]       | W24           | rxd6[2]      | AC3           | RESERVED        |

| T2            | cadd[0]       | W25           | crs7/sd7     | AC4           | Vdd             |

|               |               |               |              |               |                 |

Table 4 Pin List (Sheet 4 of 5)

| Pin<br>Number | Pin Name     | Pin<br>Number | Pin Name     | Pin<br>Number | Pin Name     |

|---------------|--------------|---------------|--------------|---------------|--------------|

| AC5           | RESERVED     | AD8           | terr2/lnk2   | AE11          | txd3[1]      |

| AC6           | rxd1[0]      | AD9           | dv2/rxd2[4]  | AE12          | terr3/lnk3   |

| AC7           | crs2/sd2     | AD10          | rxd2[2]      | AE13          | dv3/rxd3[4]  |

| AC8           | txd2[1]      | AD11          | txd3[3]      | AE14          | rxd3[0]      |

| AC9           | Vdd          | AD12          | ten3/txd3[4] | AE15          | crs4/sd4     |

| AC10          | rxd2[0]      | AD13          | rerr3        | AE16          | txd4[1]      |

| AC11          | crs3/sd3     | AD14          | rxd3[1]      | AE17          | terr4/lnk4   |

| AC12          | txd3[0]      | AD15          | col4/act4    | AE18          | dv4/rxd4[4]  |

| AC13          | Vdd          | AD16          | txd4[0]      | AE19          | rxd4[3]      |

| AC14          | rxd3[2]      | AD17          | rerr4        | AE20          | txd5[3]      |

| AC15          | txd4[2]      | AD18          | rxd4[2]      | AE21          | ten5/txd5[4] |

| AC16          | ten4/txd4[4] | AD19          | col5/act5    | AE22          | rerr5        |

| AC17          | rxd4[1]      | AD20          | txd5[0]      | AE23          | rxd5[2]      |

| AC18          | Vdd          | AD21          | dv5/rxd5[4]  | AE24          | Gnd          |

| AC19          | txd5[1]      | AD22          | rxd5[1]      | AE25          | Vdd          |

| AC20          | terr5/lnk5   | AD23          | RESERVED     | AE26          | Gnd          |

| AC21          | rxd5[0]      | AD24          | Vdd          | AF1           | Gnd          |

| AC22          | RESERVED     | AD25          | Gnd          | AF2           | Gnd          |

| AC23          | Vdd          | AD26          | crs6/sd6     | AF3           | relk1        |

| AC24          | RESERVED     | AE1           | Gnd          | AF4           | rxd1[1]      |

| AC25          | col6/act6    | AE2           | Vdd          | AF5           | col2/act2    |

| AC26          | txd6[1]      | AE3           | Gnd          | AF6           | txd2[0]      |

| AD1           | telk1        | AE4           | dv1/rxd1[4]  | AF7           | telk2        |

| AD2           | Gnd          | AE5           | rxd1[2]      | AF8           | relk2        |

| AD3           | Vdd          | AE6           | txd2[3]      | AF9           | rxd2[3]      |

| AD4           | RESERVED     | AE7           | ten2/txd2[4] | AF10          | txd3[2]      |

| AD5           | rerr1        | AE8           | rerr2        | AF11          | telk3        |

| AD6           | rxd1[3]      | AE9           | rxd2[1]      | AF12          | relk3        |

| AD7           | txd2[2]      | AE10          | col3/act3    | AF13          | Gnd          |

Table 4 Pin List (Sheet 5 of 5)

| Pin<br>Number | Pin Name | Pin<br>Number | Pin Name | Pin<br>Number | Pin Name |

|---------------|----------|---------------|----------|---------------|----------|

| AF14          | Gnd      | AF19          | rxd4[0]  | AF24          | rxd5[3]  |

| AF15          | rxd3[3]  | AF20          | crs5/sd5 | AF25          | Gnd      |

| AF16          | txd4[3]  | AF21          | txd5[2]  | AF26          | Gnd      |

| AF17          | telk4    | AF22          | telk5    |               |          |

| AF18          | rclk4    | AF23          | relk5    |               |          |

# **3 Register Descriptions**

This section describes the 21440 registers. Each of the 21440 ports includes an independent register set, enabling maximum flexibility.

The registers in each port are divided into two groups:

- Control and status registers (CSRs)

- Network statistics counters

# 3.1 Register Conventions

All the registers in the 21440 are implemented in each of its eight ports, unless mentioned otherwise in the text.

In the register description tables throughout this chapter, the following abbreviations are used to indicate register access modes:

R = Readable only. W = Writable only.

R/W = Readable and writable.

#### 3.1.1 Access Rules

The following access rules must be followed when accessing registers:

- Unlisted addresses are reserved and must not be accessed.

- Reserved bits on registers must be written as "0" and are unpredictable on read.

- The configuration and the serial registers are writable only when the port is in stop state (as reported in the interrupt status register INT-STT), following transmit and receive disable programming.

- Multibyte registers are ordered from low to high (the lower address points to the lower byte).

# 3.2 CSR Register

This section describes the 21440 CSR register mapping.

#### 3.2.1 Register Mapping

Table 5 lists each CSR register name, mnemonic, address offset, and the section that describes the register.

**Table 5 CSR Register Mapping**

(Sheet 1 of 2)

| Register Description                    | Mnemonic | I/O Address<br>Offset | Section |

|-----------------------------------------|----------|-----------------------|---------|

| Base Reg                                | isters   |                       | 3.2.2   |

| Chip interrupt summary register         | CHIP_INT | 00H                   | 3.2.2.1 |

| Interrupt status register               | INT_STT  | 01H                   | 3.2.2.2 |

| Interrupt enable register               | INT_EN   | 02H                   | 3.2.2.3 |

| Transmit status register                | TXMT_STT | 03H                   | 3.2.2.4 |

| Receive status register                 | RECV_STT | 04H                   | 3.2.2.5 |

| Port control register                   | PORT_CTR | 05H                   | 3.2.2.6 |

| Device identification number register   | DEV_ID   | 06H                   | 3.2.2.7 |

| Revision identification number register | REV_ID   | 07H                   | 3.2.2.8 |

| Serial command register                 | SER_COM  | 08H                   | 3.2.2.9 |

Table 5 CSR Register Mapping

(Sheet 2 of 2)

| Register Description                                         | Mnemonic     | I/O Address<br>Offset | Section |

|--------------------------------------------------------------|--------------|-----------------------|---------|

| Configuration                                                |              | 3.2.3                 |         |

| FIFO threshold register                                      | FFO_TSHD     | 11H                   | 3.2.3.1 |

| FIFO bus mode register                                       | FFO_BUS      | 12H                   | 3.2.3.2 |

| Transmit parameters register                                 | TX_PARAM     | 13H                   | 3.2.3.3 |

| Transmit error mode register                                 | TX_ERR_MOD   | 14H                   | 3.2.3.4 |

| Transmit packet sending threshold and backoff limit register | TX_TSHD_BOFF | 15H                   | 3.2.3.5 |

| Receive parameters register                                  | RX_PARAM     | 16H                   | 3.2.3.6 |

| Receive filtering mode register                              | RX_FILT_MOD  | 17H                   | 3.2.3.7 |

| Transmit flow-control pause time register                    | PAUSE_TIME   | 18H – 19H             | 3.2.3.8 |

| Maximum packet size register                                 | PKT_MAX_SIZE | 1AH – 1BH             | 3.2.3.9 |

| Serial Reg                                                   | gisters      |                       | 3.2.4   |

| Serial mode register                                         | SER_MOD      | 21H                   | 3.2.4.1 |

| Link status register                                         | LNK_STT      | 22H                   | 3.2.4.2 |

| Physical address register                                    | PHY_ADD      | 28H – 2DH             | 3.2.4.3 |

#### 3.2.2 Base Registers

The following sections describe the individual base registers.

#### 3.2.2.1 Chip Interrupt Summary Register

This register handles the interrupt status of all the ports. A set bit indicates that the corresponding port has generated an interrupt, and several bits located in its port status register have been set. A bit will reset when the corresponding port interrupt resets. The interrupt summary register is valid only in port 0.

#### CHIP\_INT

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| INT7 | INT6 | INT5 | INT4 | INT3 | INT2 | INT1 | INT0 |

| Bit Name          | Bit Number | Bit Description  |

|-------------------|------------|------------------|

| INT7              | 7          | Port 7 interrupt |

| INT6              | 6          | Port 6 interrupt |

| INT5              | 5          | Port 5 interrupt |

| INT4              | 4          | Port 4 interrupt |

| INT3              | 3          | Port 3 interrupt |

| INT2              | 2          | Port 2 interrupt |

| INT1              | 1          | Port 1 interrupt |

| INT0              | 0          | Port 0 interrupt |

| Access Rules      |            |                  |

| Register access   |            | R                |

| Value after reset |            | 00H              |

#### 3.2.2.2 Interrupt Status Register

The interrupt status register handles information regarding events that cause an interrupt. A specific event sets a bit if it was programmed to generate an interrupt in the interrupt enable register (INT\_EN).

Reading this register will reset all the bits, except for the TXER and RXEV bits. These bits are reset only when the corresponding status register is read.

#### INT\_STT

| 7 | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---|------|------|------|------|------|------|------|

|   | STOP | OVFC | LNCH | TXER | тхок | RXEV | RXOK |

| Bit Name | Bit Number | Bit Description                                                                                                                                                                                                                                            |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _        | 7          | RESERVED                                                                                                                                                                                                                                                   |

| STOP     | 6          | Port stop. Indicates that transmit or receive path is in the stop state, following disable programming in the port control register. If both transmit and receive paths are programmed to be stopped, this bit is set when they both reach the stop state. |

| OVFC     | 5          | Counter overflow.  Indicates that at least one management counter has reached its highest possible value (and is stuck there). The overflowed counter needs to be reset to prevent further interrupt.                                                      |

| LNCH     | 4          | Link change. Indicates that a link change has occurred while working in SYM mode. The actual link status is reported in the link status register.                                                                                                          |

| TXER     | 3          | <b>Transmit error.</b> A logical OR bit for all the bits in the transmit error status register.                                                                                                                                                            |

| TXOK     | 2          | Transmit OK. Indicates successful packet transmission.                                                                                                                                                                                                     |

| RXEV     | 1          | Receive event.  A logical OR of all the bits in the receive status register. This bit is set only after the packet is fully received by the chip.                                                                                                          |

| Bit Name    | Bit Number   | Bit Description                                                                                                                                 |  |  |  |

|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RXOK        | 0            | Receive OK.  Indicates that a packet has been received without error. This bit is set only after the packet is fully transferred onto the chip. |  |  |  |

| Access Ru   | Access Rules |                                                                                                                                                 |  |  |  |

| Register ac | cess         | R                                                                                                                                               |  |  |  |

| Value after | reset        | 00H                                                                                                                                             |  |  |  |

#### 3.2.2.3 Interrupt Enable Register

Each bit in this register enables the generation of an interrupt when the corresponding event occurs. The event causing the interrupt will be reported in the interrupt status register (INT\_STT).

#### INT\_EN

| 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---|-------|-------|-------|-------|-------|-------|-------|

|   | STOPE | OVFCE | LNCHE | TXERE | TXOKE | RXEVE | RXOKE |

| Bit Name    | Bit Number | Bit Description                   |  |  |

|-------------|------------|-----------------------------------|--|--|

| _           | 7          | RESERVED                          |  |  |

| STOPE       | 6          | Port stop interrupt enable        |  |  |

| OVFCE       | 5          | Counter overflow interrupt enable |  |  |

| LNCHE       | 4          | Line change interrupt enable      |  |  |

| TXERE       | 3          | Transmit error interrupt enable   |  |  |

| TXOKE       | 2          | Transmit OK interrupt enable      |  |  |

| RXEVE       | 1          | Receive event interrupt enable    |  |  |

| RXOKE       | 0          | Receive OK interrupt enable       |  |  |

| Access Ru   | les        |                                   |  |  |

| Register ac | cess       | R/W                               |  |  |

| Value after | reset      | 00Н                               |  |  |

#### Register Descriptions

#### 3.2.2.4 Transmit Status Register

This register handles the causes for transmit stops. All bits, except PKC bits, are reset upon reading this register. The bits in this register are set only if packet transmission is programmed to be stopped following the corresponding error in the transmit error mode register (TX\_ERR\_MOD).

#### TERR\_STT

| 7  | 6  | 5 | 4 | 3 | 2   | 1   | 0   |   |

|----|----|---|---|---|-----|-----|-----|---|

| Pł | кс |   |   |   | XCL | LCL | UNF | 1 |

| Bit Name          | Bit Number | Bit Description                                                                                                                                                                                                                                                  |  |  |

|-------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PKC               | 7:6        | Packet count. Indicates the number of packets currently stored in the transmit FIFO. The packet count is incremented while loading the first byte of a packet and decremented following transmission of a packet. The packet count can get a maximum value of 2. |  |  |

| _                 | 5:3        | RESERVED                                                                                                                                                                                                                                                         |  |  |

| XCL               | 2          | Excessive collision.  Indicates that a packet was sent 16 times unsuccessfully due to consecutive collisions.                                                                                                                                                    |  |  |

| LCL               | 1          | Late collision. Indicates that a collision has occurred after transmission of 64 bytes.                                                                                                                                                                          |  |  |

| UNF               | 0          | FIFO underflow. Indicates that data was not available in the transmit FIFO during packet transmission, after transmission of 64 bytes.                                                                                                                           |  |  |

| Access Ru         | iles       |                                                                                                                                                                                                                                                                  |  |  |

| Register ac       | cess       | R                                                                                                                                                                                                                                                                |  |  |

| Value after reset |            | 00H                                                                                                                                                                                                                                                              |  |  |

#### 3.2.2.5 Receive Status Register

This register reports events that have occurred during packet reception. All bits are reset upon reading this register. The bits in this register are set only if the receive logic is programmed to pass packets with the corresponding event in the receive filtering mode register (RX\_FILT\_MOD). If a packet with multiple errors is to be passed and not all the corresponding bits in the receive filtering mode register (RX\_FILT\_MOD) are set, none of the bits in this register are set. The receive status is also appended to the end of the packet in the receive FIFO.

#### **RECV\_STT**

| 7   | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|---|-----|-----|-----|-----|-----|-----|

| FLC |   | MER | RTL | SRT | DRB | CRC | OVF |

| Bit Name | Bit Number | Bit Description                                                                                                                                                |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLC      | 7          | Flow control packet. Indicates that a flow-control packet was received.                                                                                        |

| _        | 6          | RESERVED                                                                                                                                                       |

| MER      | 5          | MII error. Indicates either that a symbol error was detected in the SYM mode or that an MII error signal was asserted in the MII mode during packet reception. |

| RTL      | 4          | <b>Too long packet.</b> Indicates that a packet longer than the maximum allowable size has been received.                                                      |

| SRT      | 3          | <b>Short packet.</b> Indicates that a packet shorter than 64 bytes has been received.                                                                          |

| DRB      | 2          | Alignment error. Indicates that a packet was received with CRC and framing errors.                                                                             |

| CRC      | 1          | CRC error.  Indicates that a packet was received with a CRC error but without a framing error.                                                                 |

| OVF      | 0          | FIFO overflow.  Indicates that there was not enough space available in the receive FIFO during packet reception.                                               |

#### 24 Register Descriptions

| Bit Name          | Bit Number | Bit Description |  |  |  |

|-------------------|------------|-----------------|--|--|--|

| Access Ru         | iles       |                 |  |  |  |

| Register ac       | cess       | R               |  |  |  |

| Value after reset |            | 00H             |  |  |  |

# 3.2.2.6 Port Control Register

The port control register handles all the control bits of the port.

# PORT\_CTR

| 7 | 6 | 5     | 4    | 3    | 2     | 1     | 0     |

|---|---|-------|------|------|-------|-------|-------|

|   |   | TXSTT | TXEN | RXEN | PTRST | CTRST | CNRST |

| Bit Name    | Bit Number | Bit Description                                                                                                                                                                                                                                                           |  |  |  |

|-------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Dit Name    | 7:6        | RESERVED                                                                                                                                                                                                                                                                  |  |  |  |

| _           |            |                                                                                                                                                                                                                                                                           |  |  |  |

| TXSTT       | 5          | <b>Transmit restart.</b> When set, the chip restarts the transmission process after stopping due to a transmit error. The TXSTT is a trigger bit (does not require reset before setting).                                                                                 |  |  |  |

| TXEN        | 4          | <b>Transmit enable.</b> When this bit is set, the port enters the working mode. When reset, the port completes transmission of the packet currently processed, and then stops. Stop state is reported in the STOP bit located in the interrupt status register (INT_STT). |  |  |  |

| RXEN        | 3          | Receive enable. When this bit is set, the port enters the working mode. When reset, the port completes reception of the packet currently processed, and then stops. Stop state is reported in the STOP bit located in the interrupt status register (INT_STT).            |  |  |  |

| PTRST       | 2          | Port reset. When set, this bit causes the transmit and receive logic to reset.                                                                                                                                                                                            |  |  |  |

| CTRST       | 1          | Control reset.  When set, this bit resets all the registers, except PORT_CTR, to their default values. Transmit and receive logic are also reset.                                                                                                                         |  |  |  |

| CNRST       | 0          | Counter reset.  When set, this bit resets all the network statistic counters. The reset process takes 100 cycles. During this time, the counters and PORT_CTR must not be accessed. This bit must not be set together with the CTRST bit.                                 |  |  |  |

| Access Ru   | les        |                                                                                                                                                                                                                                                                           |  |  |  |

| Register ac | cess       | R/W                                                                                                                                                                                                                                                                       |  |  |  |

| Value after | reset      | 00H                                                                                                                                                                                                                                                                       |  |  |  |

|             |            |                                                                                                                                                                                                                                                                           |  |  |  |

#### Register Descriptions

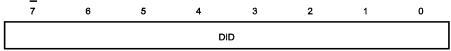

#### 3.2.2.7 Device ID Register

The device ID register is valid only in port 0.

# DEV\_ID

| Bit Name          | Bit Number | Bit Description |

|-------------------|------------|-----------------|

| DID               | 7:0        | Device ID.      |

| Access Ru         | les        |                 |

| Register access   |            | R               |

| Value after reset |            | 01H             |

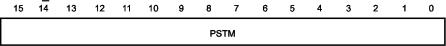

# 3.2.2.8 Revision ID Register

The revision ID register is valid only in port 0.

# REV\_ID

| 7 | 6  | 5   | 4 | 3 | 2  | 1  | 0 |

|---|----|-----|---|---|----|----|---|

|   | MF | RID |   |   | SR | ID |   |

| Bit Name        | Bit Number | Bit Description                                                                                     |  |  |

|-----------------|------------|-----------------------------------------------------------------------------------------------------|--|--|

| MRID            | 7:4        | Main revision ID. This number is incremented for subsequent 21440 revisions.                        |  |  |

| SRID 3:0        |            | Sub revision ID. This number is incremented for subsequent 21440 steps within the current revision. |  |  |

| Access Ru       | ıles       |                                                                                                     |  |  |

| Register access |            | R                                                                                                   |  |  |

#### 3.2.2.9 Serial Command Register

The serial command register handles the control of the serial interface.

# SER\_COM

| 7 | 6 | 5   | 4    | 3   | 2   | 1   | 0 |

|---|---|-----|------|-----|-----|-----|---|

|   |   | MDM | MDIO | MDC | ВКР | FCT |   |

| Bit Name      | Bit Number | Bit Description                                                                                                                                                                                                                                                                                         |  |  |  |

|---------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| _             | 7:6        | RESERVED                                                                                                                                                                                                                                                                                                |  |  |  |

| MDM           | 5          | MII data mode. When set, the mdio signal is in the output mode. When reset, the mdio signal is in the input mode. This bit is effective only in port "0".                                                                                                                                               |  |  |  |

| MDIO          | 4          | MII data IO.  During write access to the MII management, the value written to this bit is driven onto the mdio signal. During read access, the mdio signal value is latched into this bit.  This bit is effective only in port "0".                                                                     |  |  |  |

| MDC           | 3          | MII management clock.  The value written to this bit is driven onto the mdc signal. Each new written value must remain stable for at least 200 ns.  This bit is effective only in port "0".                                                                                                             |  |  |  |

| ВКР           | 2          | Backpressure mode. When set, a transmission is generated upon reception of each packet to force a collision while the port is in the half-duplex mode.                                                                                                                                                  |  |  |  |

| FCT           | 1          | Flow-control packet trigger.  When set, this bit initiates a flow-control packet transmission to the remote node, as defined in the 802.3 IEEE Standard, while the port is in the full-duplex mode. This bit can be used only if the XON disable bit on transmit parameters register (TX_PARAM) is set. |  |  |  |

| _             | 0          | RESERVED                                                                                                                                                                                                                                                                                                |  |  |  |

| Access Rul    | les        |                                                                                                                                                                                                                                                                                                         |  |  |  |

| Register acc  | eess       | R/W                                                                                                                                                                                                                                                                                                     |  |  |  |

| Value after 1 | reset      | 00H                                                                                                                                                                                                                                                                                                     |  |  |  |

#### Register Descriptions

#### 3.2.3 Configuration Registers

The following sections describe the individual configuration registers.

#### 3.2.3.1 FIFO Threshold Register

The FIFO threshold register handles the transmit and receive FIFO threshold.

#### FFO\_TSHD

| 7 | 6 | 5  | 4 | 3 | 2  | 1  | 0 |

|---|---|----|---|---|----|----|---|

|   | Т | гн |   |   | R. | ГН |   |

| Bit Name    | Bit Number | Bit Description                                                                                                                                                                                                                  |  |  |  |

|-------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TTH         | 7:4        | This field defines the minimum amount of free space required in the transmit FIFO in order to assert the <b>txrdy</b> signal. The effective threshold in bytes is equal to $8 \times (TTH + 1)$ . A value of "0" is not allowed. |  |  |  |

| RTH         | 3:0        | This field defines the minimum amount of data required in the receive FIFO in order to assert the <b>rxrdy</b> signal. The effective threshold in bytes is equal to $8 \times (RTH + 1)$ . A value of "0" is not allowed.        |  |  |  |

| Access Ru   | ıles       |                                                                                                                                                                                                                                  |  |  |  |

| Register ac | cess       | R/W                                                                                                                                                                                                                              |  |  |  |

| Value after | reset      | 77H                                                                                                                                                                                                                              |  |  |  |

| Register field value<br>(RTH or TTH) | Effective threshold (bytes) | Register field value<br>(RTH or TTH) | Effective threshold (bytes) |

|--------------------------------------|-----------------------------|--------------------------------------|-----------------------------|

| 0                                    | not allowed                 | 8                                    | 72                          |

| 1                                    | 16                          | 9                                    | 80                          |

| 2                                    | 24                          | 10                                   | 88                          |

| 3                                    | 32                          | 11                                   | 96                          |

| 4                                    | 40                          | 12                                   | 104                         |

| 5                                    | 48                          | 13                                   | 112                         |

| 6                                    | 56                          | 14                                   | 120                         |

| 7                                    | 64                          | 15                                   | 128                         |

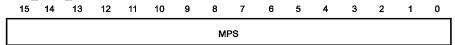

# 3.2.3.2 FIFO Bus Mode Register

The FIFO bus mode register controls the FIFO bus mode of work.

# FFO\_BUS

| 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|---|---|---|---|---|------|------|------|

|   |   |   |   |   | HRYD | BWID | BEND |

| Bit Name     | Bit Number | Bit Description                                                                                                                                                            |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _            | 7:3        | RESERVED                                                                                                                                                                   |

| HRYD         | 2          | Header ready disable. When set, the <b>rxrdy</b> signal will not be asserted when a packet header is in FIFO, but only according to FIFO threshold values.                 |

| BWID         | 1          | <b>Bus width.</b> Defines the number of bits used on the FIFO bus. When set, 64 bits are used. When reset, the lower 32 bits are used.                                     |

| BEND         | 0          | <b>Big or little endian mode.</b> Defines the byte ordering mode on the FIFO bus. When set, the port uses the big endian mode. When reset, the little endian mode is used. |

| Access Ru    | les        |                                                                                                                                                                            |

| Register acc | cess       | R/W                                                                                                                                                                        |

| Value after  | reset      | 00H                                                                                                                                                                        |

# 3.2.3.3 Transmit Parameters Register

The transmit parameters register handles the control of the transmit serial interface.

#### TX\_PARAM

| 7 | 6 | 5 | 4   | 3    | 2    | 1    | 0    |

|---|---|---|-----|------|------|------|------|

|   |   |   | SPM | XOND | FLCE | CRCD | PADD |

| Bit Name    | Bit Number | Bit Description                                                                                                                                                                                                                                                                   |

|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _           | 7:5        | RESERVED                                                                                                                                                                                                                                                                          |

| SPM         | 4          | Single packet mode. When set, a packet is loaded in the transmit FIFO only after the previous packet was fully transmitted without any error.                                                                                                                                     |

| XOND        | 3          | XON disable. When set, a flow-control packet will not be sent upon flet{i} signal deassertion.                                                                                                                                                                                    |

| FLCE        | 2          | Flow-control mode enable. When set, transmission is stopped in the full-duplex mode while receiving flow-control packets.                                                                                                                                                         |

| CRCD        | 1          | CRC appending disable. When set, packets are transmitted without padding or CRC appending to the end of the packet. This field is ignored if the txasis signal is asserted during the start of packet loading.                                                                    |

| PADD        | 0          | Padding appending disable. When set, short packets are transmitted without the addition of bytes complementing their sizes to 64 bytes. When the CRCD bit is set, this bit is ignored. This field is ignored if the txasis signal is asserted during the start of packet loading. |

| Access Ru   | ıles       |                                                                                                                                                                                                                                                                                   |

| Register ac | cess       | R/W                                                                                                                                                                                                                                                                               |

| Value after | reset      | 00H                                                                                                                                                                                                                                                                               |

|             |            |                                                                                                                                                                                                                                                                                   |

#### 3.2.3.4 Transmit Error Mode Register

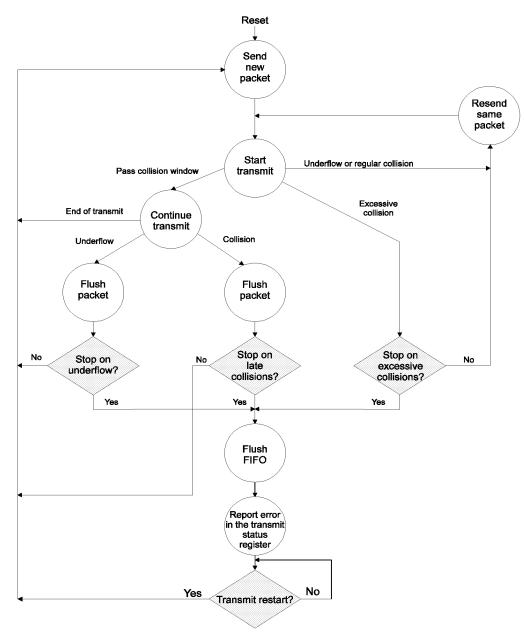

The transmit error mode register controls the events that cause transmission stop. If, during packet transmission, an error occurs and the corresponding bit is set, the transmit FIFO is flushed, and transmission stops. The error is then reported in the transmit error status register (TERR\_STT), and can generate an interrupt according to the interrupt enable register (INT\_EN).

#### TX\_ERR\_MOD

| 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|---|---|---|---|---|------|------|------|

|   |   |   |   |   | XCLS | LCLS | UNFS |

| Bit Name    | Bit Number | Bit Description                                                                                                                                                                                                                          |

|-------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _           | 7:3        | RESERVED                                                                                                                                                                                                                                 |

| XCLS        | 2          | Stop transmission after excessive collisions. When set, packet retransmission stops after 16 attempts. When reset, packets will always be retransmitted following a collision until a successful transmission is achieved.               |

| LCLS        | 1          | Stop transmission after late collision. When set, transmission stops if a collision occurs after transmission of 64 bytes. When reset, the packet will be flushed from the transmit FIFO and the following packet will be transmitted.   |

| UNFS        | 0          | Stop transmission after FIFO underflow. When set, transmission stops if an underflow occurs after transmission of 64 bytes. When reset, the packet will be flushed from the transmit FIFO, and the following packet will be transmitted. |

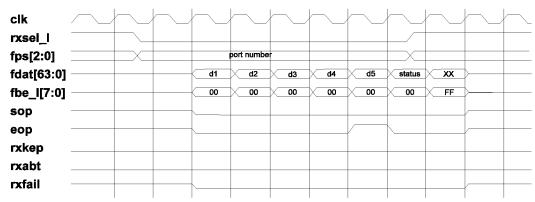

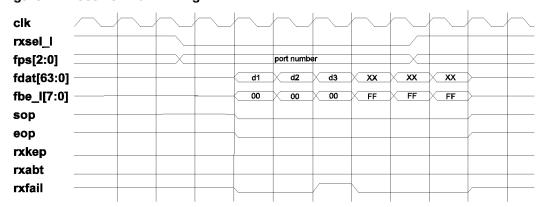

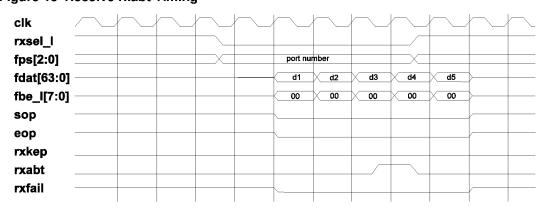

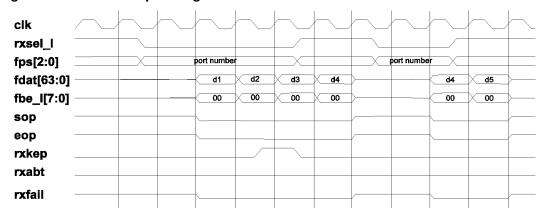

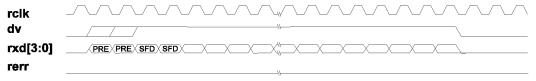

| Access Ru   | ıles       |                                                                                                                                                                                                                                          |