# PowerPC 403GB 32-Bit RISC Embedded Controller

### **Features**

- PowerPC™ RISC CPU and instruction set architecture

- Glueless interfaces to DRAM, SRAM, ROM, and peripherals, including byte and half-word devices

- Separate instruction cache and write-back data cache, both two-way set-associative

- Minimized interrupt latency

- Individually programmable on-chip controllers for:

- -Two DMA channels

- -DRAM, SRAM, and ROM banks

- -Peripherals

- -External interrupts

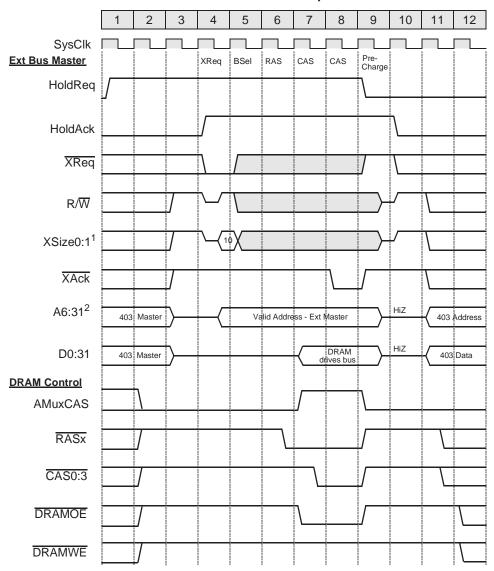

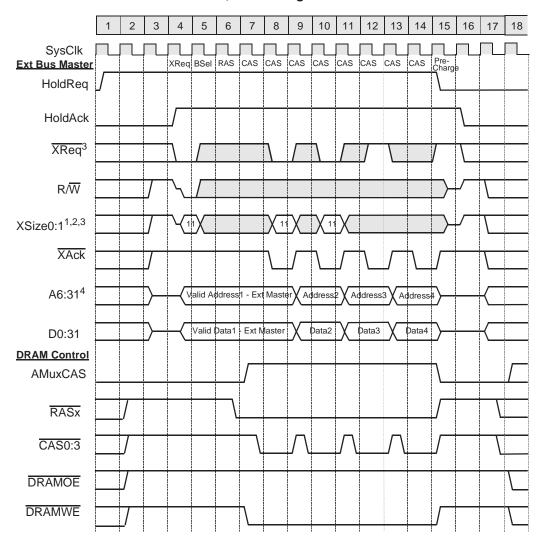

- Flexible interface to external bus masters

- Hardware multiplier and divider for faster integer arithmetic

- Thirty-two 32-bit general purpose registers

# **Applications**

- Set-top boxes

- Consumer electronics and video games

- Telecommunications and networking

- Office automation (printers, copiers, fax machines)

### **Specifications**

- 28MHz operation

- Interfaces to both 3V and 5V technologies

- Low-power 3.3V operation with built-in power management and stand-by mode

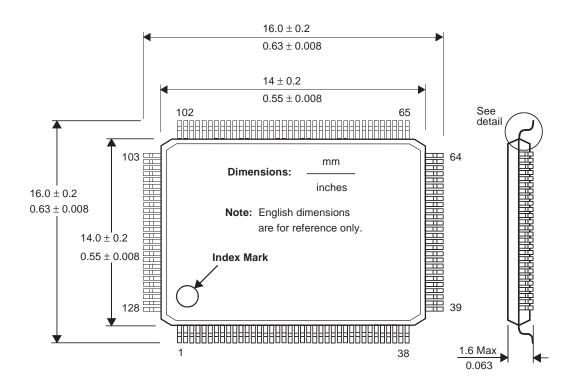

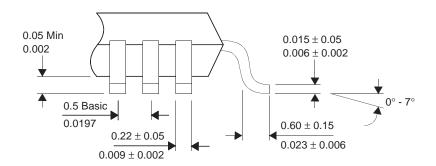

- Low-cost 128 lead TQFP package

- 0.5 μm triple-level-metal CMOS

#### Overview

The PowerPC 403GB 32-bit RISC embedded controller offers high performance and functional integration with low power consumption. The 403GB RISC CPU executes at sustained speeds approaching one cycle per instruction. On-chip caches and integrated DRAM and SRAM control functions reduce chip count and design complexity in systems, while improving system throughput.

External I/O devices or SRAM/DRAM memory banks can be directly attached to the 403GB bus interface unit (BIU). Interfaces for up to six memory banks and I/O devices, including a maximum of two DRAM banks, can be configured individually, allowing the BIU to manage devices or memory banks with differing control, timing, or bus width requirements.

### IBM PowerPC 403GB

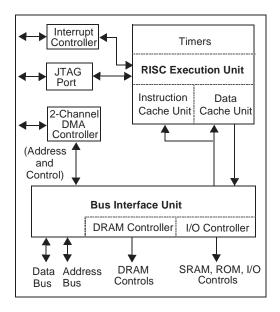

The 403GB RISC controller consists of a pipelined RISC processor core and several peripheral interface units: BIU, DMA controller, asynchronous interrupt controller, and JTAG debug port.

The RISC processor core includes the internal 2KB instruction cache and 1KB data cache, reducing overhead for data transfers to or from external memory. The instruction queue logic manages branch prediction, folding of branch and condition register logical instructions, and instruction prefetching to minimize pipeline stalls.

### **RISC CPU**

The RISC core comprises three tightly coupled functional units: the execution unit (EXU), the data cache unit (DCU), and the instruction cache unit (ICU). Each cache unit consists of a data array, tag array, and control logic for cache management and addressing. The execution unit consists of general purpose registers (GPR), special purpose registers (SPR), ALU, multiplier, divider, barrel shifter, and the control logic required to manage data flow and instruction execution within the EXU.

The EXU handles instruction decoding and execution, queue management, branch prediction, and branch folding. The instruction cache unit passes instructions to the queue in the EXU or, in the event of a cache miss, requests a fetch from external memory through the bus interface unit.

### **General Purpose Registers**

Data transfers to and from the EXU are handled through the bank of 32 GPRs, each 32 bits wide. Load and store instructions move data operands between the GPRs and the data cache unit, except in the cases of noncacheable data or cache misses. In such cases the DCU passes the address for the data read or write to the BIU. When noncacheable operands are being transferred, data can pass directly between the EXU and the BIU, which interfaces to the external memory being accessed.

### Special Purpose Registers

Special purpose registers are used to control debug facilities, timers, interrupts, the protection mechanism, memory cacheability, and other

architected processor resources. SPRs are accessed using move to/from special purpose register (mtspr/mfspr) instructions, which move operands between GPRs and SPRs.

Supervisory programs can write the appropriate SPRs to configure the operating and interface modes of the execution unit. The condition register (CR) and machine state register (MSR) are written by internal control logic with program execution status and machine state, respectively. Status of external interrupts is maintained in the external interrupt status register (EXISR). Fixed-point arithmetic exception status is available from the exception register (XER).

### **Device Control Registers**

Device control registers (DCR) are used to manage I/O interfaces, DMA channels, SRAM and DRAM memory configurations and timing, and status/address information regarding bus errors. DCRs are accessed using move to/from device control register (mtdcr/mfdcr) instructions, which move operands between GPRs and DCRs.

### Instruction Set

Table 1 summarizes the 403GB instruction set by categories of operations. Most instructions execute in a single cycle, with the exceptions of load/store multiple, load/store string, multiply, and divide instructions.

#### **Bus Interface Unit**

The bus interface unit integrates the functional controls for data transfers and address operations other than those which the DMA controller handles. DMA transfers use the address logic in the BIU to output the memory addresses being accessed.

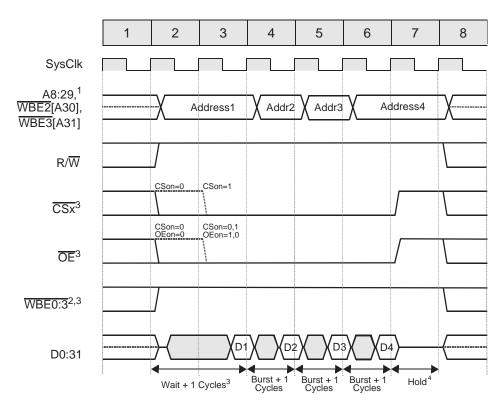

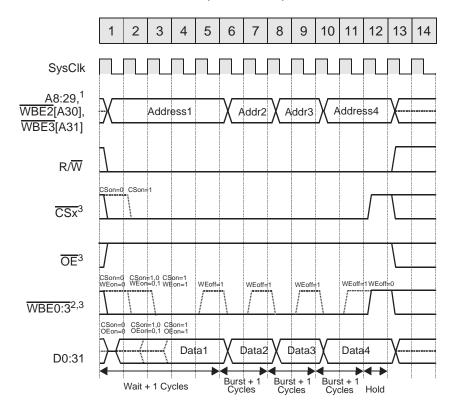

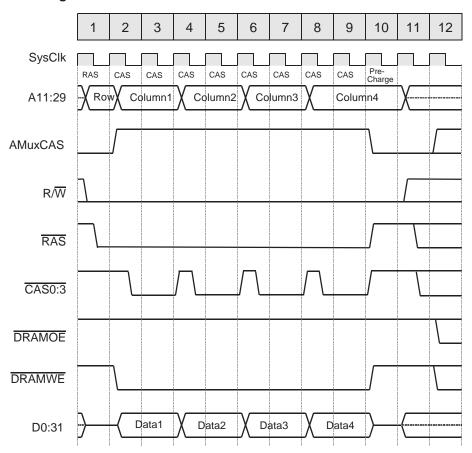

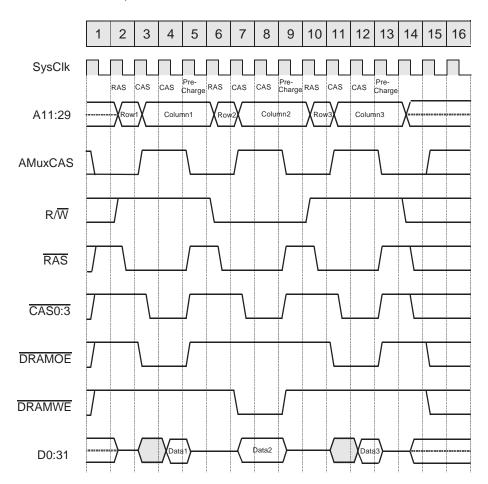

Control functions for direct-connect I/O devices and for DRAM, SRAM, or ROM banks are provided by the BIU. Burst access for SRAM, ROM, and page-mode DRAM devices is supported for cache fill and flush operations.

The BIU controls the transfer of data between the external bus and the instruction cache, the data cache, or registers internal to the processor core. The BIU also arbitrates among external bus master and DMA transfers, the internal buses to the

cache units and the register banks.

# **Memory Addressing Regions**

The 403GB can address an effective range of 3.192 GB (128 MB DRAM; 64 MB SRAM, ROM or other I/O; and 3GB reserved). SRAM banks can be up to 16MB and DRAM banks for internally multiplexed access can be up to 64MB. Cacheability with respect to the instruction or data cache is programmed via the instruction and data cache control registers, respectively.

Within the DRAM and SRAM/ROM regions, a total of six banks of devices are supported. Each bank can be configured for 8-, 16-, or 32-bit devices.

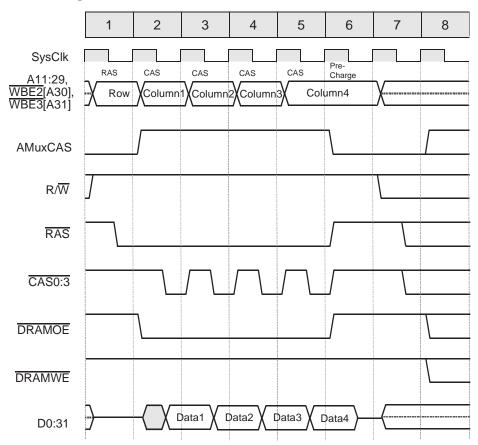

For individual DRAM banks, the number of wait states, bank size, RAS-to-CAS timing, use of an external address multiplexer (for external bus masters), and refresh rate are user-programmable. For each SRAM/ROM bank, the bank size, bank location, number of wait states, and timings of chip selects, byte enables, and output enables are all user-programmable.

#### Instruction Cache Unit

The instruction cache unit (ICU) is a two-way setassociative 2KB cache memory unit with enhancements to support branch prediction and folding. The ICU is organized as 64 sets of 2 lines, each line containing 16 bytes. A separate bypass path is available to handle cache-inhibited instructions and to improve performance during line fill operations.

The cache can send two cached instructions per cycle to the execution unit, allowing instructions to be folded out of the queue without interrupting normal instruction flow. When a branch instruction is folded and executed in parallel with another instruction, the ICU provides two more instructions to replace both of the instructions just executed so that bandwidth is balanced between the ICU and the execution unit.

### **Data Cache Unit**

The data cache unit is provided to minimize the access time of frequently used data items in main store. The 1KB cache is organized as a two-way set associative cache. There are 32 sets of 2 lines, each line containing 16 bytes of data. The cache features byte-writeability to improve the performance of byte and halfword store operations.

Cache operations are performed using a writeback strategy. A write-back cache only updates locations in main storage that corresponds to changed locations in the cache. Data is flushed from the cache to main storage whenever changed data needs to be removed from the

| Category             | Base Instructions                                                                                                                  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Data Movement        | load, store                                                                                                                        |

| Arithmetic / Logical | add, subtract, negate, multiply, divide, and, or, xor, nand, nor, xnor, sign extension, count leading zeros                        |

| Comparison           | compare, compare logical, compare immediate                                                                                        |

| Branch               | branch, branch conditional                                                                                                         |

| Condition            | condition register logical                                                                                                         |

| Rotate/Shift         | rotate, rotate and mask, shift left, shift right                                                                                   |

| Cache Control        | invalidate, touch, zero, flush, store                                                                                              |

| Interrupt Control    | write to external interrupt enable bit, move to/from machine state register, return from interrupt, return from critical interrupt |

| Processor Management | system call, synchronize, move to/from device control registers, move to/from special purpose registers                            |

Table 1. 403GB Instructions by Category

### IBM PowerPC 403GB

cache to make room for other data.

The data cache may be disabled for a 128MB memory region via control bits in the data cache control register. A separate bypass path is available to handle cache-inhibited data operations and to improve performance during line fill operations.

Cache flushing and filling are triggered by load, store, and cache control instructions executed by the processor. Cache blocks are loaded starting at the requested fullword, continuing to the end of the block and then wrapping around to fill the remaining fullwords at the beginning of the block.

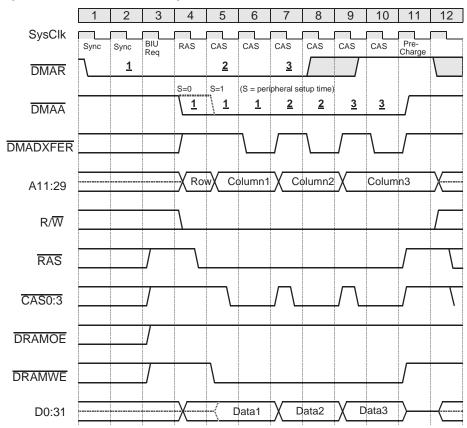

#### **DMA Controller**

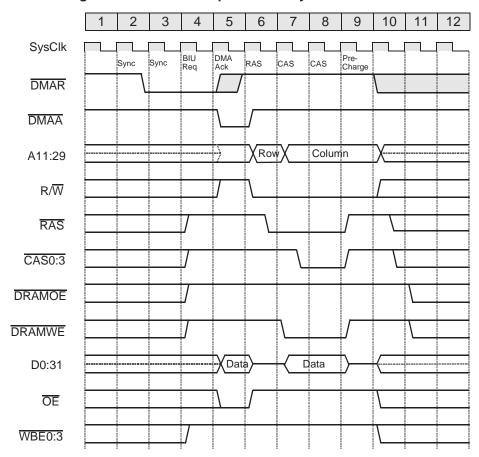

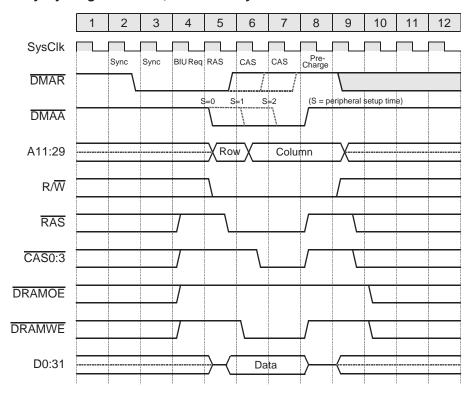

The two-channel DMA controller manages block data transfers in buffered, fly-by and memory-to-memory transfer modes with options for burst-mode operation. In fly-by and buffered modes, the DMA controller supports transactions between memory and peripheral devices.

Each DMA channel provides a control register, a source address register, a destination address register, a transfer count register, and a chained count register. Peripheral set-up cycles, wait cycles, and hold cycles can be programmed into each DMA channel control register. Each channel supports chaining operations. The DMA status register holds the status of both channels.

### **Exception Handling**

Table 2 summarizes the 403GB exception priorities, types, and classes. Exceptions are generated by interrupts from internal and external peripherals, instructions, the internal timer facility, debug events or error conditions. Six external interrupt signals are provided on the 403GB: one critical and five general-purpose, all individually maskable.

All exceptions fall into three basic classes: asynchronous imprecise exceptions, synchronous precise exceptions, and asynchronous precise exceptions. Asynchronous exceptions are caused by events external to processor execution, while synchronous exceptions are caused by instructions.

Except for a system reset or machine check, all

403GB exceptions are handled precisely. Precise handling implies that the address of the excepting instruction (synchronous exceptions other than system call) or the address of the next sequential instruction (asynchronous exceptions and system call) is passed to the exception handling routine. Precise handling also implies that all instructions prior to the excepting instruction have completed execution and have written back their results.

Asynchronous imprecise exceptions include system resets and machine checks. Synchronous precise exceptions include most debug exceptions, program exceptions, protection violations, system calls, and alignment error exceptions. Asynchronous precise exceptions include the critical interrupt exception, external interrupts, and internal timer facility exceptions and some debug events.

Only one exception is handled at a time. If multiple exceptions occur simultaneously, they are handled in priority order.

The 403GB processes exceptions as reset, critical, or noncritical. Four exceptions are defined as critical: machine check exceptions, debug exceptions, exceptions caused by an active level on the critical interrupt pin, and the first time-out from the watchdog timer.

When a noncritical exception is taken, special purpose register Save/Restore 0 (SRR0) is loaded with the address of the excepting instruction (synchronous exceptions other than system call) or the next sequential instruction to be processed (asynchronous exceptions and system call). If the 403GB is executing a multicycle instruction (load/store multiple, load/store string, multiply or divide), the instruction is terminated and its address stored in SRR0. Save/Restore Register 1 (SRR1) is loaded with the contents of the machine state register. The MSR is then updated to reflect the new context of the machine. The new MSR contents take effect beginning with the first instruction of the exception handling routine.

At the end of the exception handling routine, execution of a return from interrupt (rfi) instruction forces the contents of SRR0 and SRR1 to be

loaded into the program counter and the MSR, respectively. Execution then begins at the address in the program counter.

The four critical exceptions are processed in a similar manner. When a critical exception is taken, SRR2 and SRR3 hold the next sequential address to be processed when returning from the exception and the contents of the machine state register, respectively. After the critical exception handling routine, return from critical interrupt (rfci) forces the contents of SRR2 and SRR3 to be loaded into the program counter and the MSR, respectively.

#### **Timers**

The 403GB contains four timer functions: a time base, a programmable interval timer (PIT), a fixed interval timer (FIT), and a watchdog timer. The time base is a 56-bit counter incremented at the timer clock rate. The timer clock is driven by an internal signal equal to the processor clock rate. No interrupts are generated when the time base rolls over.

The programmable interval timer is a 32-bit register that is decremented at the same rate as the time base is incremented. The user preloads the PIT register with a value to create the desired delay. When the register is decremented to zeros, the timer stops decrementing, a bit is set in the timer status register (TSR), and a PIT interrupt is generated. Optionally, the PIT can be pro-

grammed to reload automatically the last value written to the PIT register, after which the PIT begins decrementing again. The timer control register (TCR) contains the interrupt enable for the PIT interrupt.

The fixed interval timer generates periodic interrupts based on selected bits in the time base. Users may select one of four intervals for the timer period by setting the correct bits in the TCR. When the selected bit in the time base changes from 0 to 1, a bit is set in the TSR and a FIT interrupt is generated. The FIT interrupt enable is contained in the TCR.

The watchdog timer generates a periodic interrupt based on selected bits in the time base. Users may select one of four time periods for the interval and the type of reset generated if the watchdog timer expires twice without an intervening clear from software. If enabled, the watchdog timer generates a system reset unless an exception handler updates the watchdog timer status bit before the timer has completed two of the selected timer intervals.

#### JTAG Port

The JTAG port has been enhanced to allow it to be used as a debug port. Through the JTAG test access port, debug software on a workstation can single-step the processor and interrogate internal processor state to facilitate software

| Table 2. | 403GB Exce | ption Priorities, | Types | and Classes |

|----------|------------|-------------------|-------|-------------|

|----------|------------|-------------------|-------|-------------|

| Priority | Exception Type                                            | Exception Class                          |

|----------|-----------------------------------------------------------|------------------------------------------|

| 1        | System Reset                                              | Asynchronous imprecise                   |

| 2        | Machine Check                                             | Asynchronous imprecise                   |

| 3        | Debug                                                     | Synchronous precise (except UDE and EXC) |

| 4        | Critical Interrupt                                        | Asynchronous precise                     |

| 5        | WatchdogTimer Time-out                                    | Asynchronous precise                     |

| 6        | Program Exception, Protection Violation, and System Calls | Synchronous precise                      |

| 7        | Alignment Exceptions                                      | Synchronous precise                      |

| 8        | External Interrupts                                       | Asynchronous precise                     |

| 9        | Fixed Interval Timer                                      | Asynchronous precise                     |

| 10       | Programmable Interval Timer                               | Asynchronous precise                     |

### IBM PowerPC 403GB

debugging. The standard JTAG boundary-scan register allows testing of circuitry external to the chip, primarily the board interconnect. Alternatively, the JTAG bypass register can be selected when no other test data register needs to be accessed during a board-level test operation.

### P/N Code

Table 3. PPC403GB Part Number

| MHz | Part Number      |

|-----|------------------|

| 28  | PPC403GB-KA28C-1 |

- 1. The dash number indicates the speed version.

- The characters in the dash number indicate package type (K), revision level (A), commercial version (C).

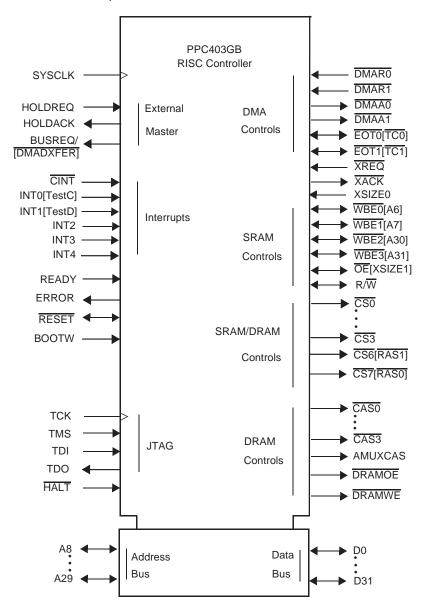

# **Logic Symbol**

Signals in brackets are multiplexed..

# **Pin Functional Descriptions**

Active-low signals are shown with overbars: DMARO. Multiplexed signals are alphabetized under the first (unmultiplexed) signal names on the same pins. The logic symbol on the preceding page shows all 403GB signals arranged by functional groups.

Table 4. 403GB Signal Descriptions

| Signal<br>Name | Pin | I/O<br>Type | Function                                                                                                                                                                                                              |

|----------------|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A8             | 79  | I/O         | Address Bus Bit 8. When the 403GB is bus master, this is an address output from the 403GB. When the 403GB is not bus master, this is an address input from the external bus master, to determine bank register usage. |

| A9             | 80  | I/O         | Address Bus Bit 9. See description of A8                                                                                                                                                                              |

| A10            | 81  | I/O         | Address Bus Bit 10. See description of A8                                                                                                                                                                             |

| A11            | 82  | I/O         | Address Bus Bit 11. See description of A8                                                                                                                                                                             |

| A12            | 83  | 0           | Address Bus Bit 12. When the 403GB is bus master, this is an address output from the 403GB.                                                                                                                           |

| A13            | 86  | 0           | Address Bus Bit 13. See description of A12.                                                                                                                                                                           |

| A14            | 87  | 0           | Address Bus Bit 14. See description of A12.                                                                                                                                                                           |

| A15            | 88  | 0           | Address Bus Bit 15. See description of A12.                                                                                                                                                                           |

| A16            | 89  | 0           | Address Bus Bit 16. See description of A12.                                                                                                                                                                           |

| A17            | 90  | 0           | Address Bus Bit 17. See description of A12.                                                                                                                                                                           |

| A18            | 92  | 0           | Address Bus Bit 18. See description of A12.                                                                                                                                                                           |

| A19            | 93  | 0           | Address Bus Bit 19. See description of A12.                                                                                                                                                                           |

| A20            | 94  | 0           | Address Bus Bit 20. See description of A12.                                                                                                                                                                           |

| A21            | 95  | 0           | Address Bus Bit 21. See description of A12.                                                                                                                                                                           |

| A22            | 96  | I/O         | Address Bus Bit 22. When the 403GB is bus master, this is an address output from the 403GB. When the 403GB is not bus master, this is an address input from the external bus master, to determine page crossings.     |

| A23            | 97  | I/O         | Address Bus Bit 23. See description of A8                                                                                                                                                                             |

Table 4. 403GB Signal Descriptions (Continued)

| Signal<br>Name      | Pin | I/O<br>Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A24                 | 98  | I/O         | Address Bus Bit 24. See description of A8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A25                 | 99  | I/O         | Address Bus Bit 25. See description of A8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A26                 | 101 | I/O         | Address Bus Bit 26. See description of A8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A27                 | 102 | I/O         | Address Bus Bit 27. See description of A8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A28                 | 103 | I/O         | Address Bus Bit 28. See description of A8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A29                 | 104 | I/O         | Address Bus Bit 29. See description of A8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AMuxCAS             | 127 | 0           | DRAM External Address Multiplexer Select. AMuxCAS controls the select logic on an external multiplexer. If AMuxCAS is low, the multiplexer should select the row address for the DRAM and when AMuxCAS is 1, the multiplexer should select the column address.                                                                                                                                                                                                                                                                                                                                                                                                             |

| BootW               | 23  | I           | Boot-up ROM Width Select. BootW is sampled before and after the RESET pin is active to determine the width of the boot-up ROM. If this pin is tied to logic 0 when sampled on reset, an 8-bit boot width is assumed. If BootW is tied to 1, a 32-bit boot width is assumed. For 16-bit boot widths, this pin should be tied to the RESET pin.                                                                                                                                                                                                                                                                                                                              |

| BusReq/<br>DMADXFER | 123 | 0           | Bus Request. While HoldAck is active, BusReq is active when the 403GB has a bus operation pending and needs to regain control of the bus.  DMA Data Transfer. When HoldAck is not active, DMADXFER indicates a valid data transfer cycle. For DMA use, DMADXFER controls burst-mode fly-by DMA transfers between memory and peripherals. DMADXFER is not meaningful unless a DMA Acknowledge signal (DMAA0:DMAA1) is active. For transfer rates slower than one transfer per cycle, DMADXFER is active for one cycle when one transfer is complete and the next one starts. For transfer rates of one transfer per cycle, DMADXFER remains active throughout the transfer. |

| CAS0                | 116 | 0           | DRAM Column Address Select 0.  CAS0 is used with byte 0 of all DRAM banks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CAS1                | 117 | 0           | DRAM Column Address Select 1. CAS1 is used with byte 1 of all DRAM banks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CAS2                | 118 | 0           | DRAM Column Address Select 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Table 4. 403GB Signal Descriptions (Continued)

| Signal<br>Name | Pin | I/O<br>Type | Function                                                                                                                                                                                                                                                    |

|----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAS3           | 119 | 0           | DRAM Column Address Select 3. CAS3 is used with byte 3 of all DRAM banks.                                                                                                                                                                                   |

| CINT           | 34  | I           | Critical Interrupt. To initiate a critical interrupt, the user must maintain a logic 0 on the $\overline{\text{CINT}}$ pin for a minimum of one SysClk clock cycle followed by a logic 1 on the $\overline{\text{CINT}}$ pin for at least one SysClk cycle. |

| <del>CS0</del> | 8   | 0           | SRAM Chip Select 0. Bank register 0 controls an SRAM bank, CS0 is the chip select for that bank.                                                                                                                                                            |

| CS1            | 5   | 0           | SRAM Chip Select 1. Same function as $\overline{\text{CS0}}$ but controls bank 1.                                                                                                                                                                           |

| CS2            | 4   | 0           | SRAM Chip Select 2. Same function as $\overline{\text{CS0}}$ but controls bank 2.                                                                                                                                                                           |

| CS3            | 3   | 0           | SRAM Chip Select 3. Same function as $\overline{\text{CS0}}$ but controls bank 3.                                                                                                                                                                           |

| CS6/RAS1       | 2   | 0           | Chip Select 6/ DRAM Row Address Select 1. When bank register 6 is configured to control an SRAM bank, CS6/RAS1 functions as a chip select. When bank register 6 is configured to control a DRAM bank, CS6/RAS1 is the row address select for that bank.     |

| CS7/RAS0       | 128 | 0           | Chip Select 7/ DRAM Row Address Select 0. Same function as CS6/RAS1 but controls bank 7.                                                                                                                                                                    |

| D0             | 36  | I/O         | Data bus bit 0 (Most significant bit)                                                                                                                                                                                                                       |

| D1             | 37  | I/O         | Data bus bit1                                                                                                                                                                                                                                               |

| D2             | 39  | I/O         | Data bus bit 2                                                                                                                                                                                                                                              |

| D3             | 40  | I/O         | Data bus bit 3                                                                                                                                                                                                                                              |

| D4             | 41  | I/O         | Data bus bit 4                                                                                                                                                                                                                                              |

| D5             | 43  | I/O         | Data bus bit 5                                                                                                                                                                                                                                              |

| D6             | 44  | I/O         | Data bus bit 6                                                                                                                                                                                                                                              |

| D7             | 45  | I/O         | Data bus bit 7                                                                                                                                                                                                                                              |

| D8             | 46  | I/O         | Data bus bit 8                                                                                                                                                                                                                                              |

| D9             | 47  | I/O         | Data bus bit 9                                                                                                                                                                                                                                              |

| D10            | 48  | I/O         | Data bus bit 10                                                                                                                                                                                                                                             |

Table 4. 403GB Signal Descriptions (Continued)

| Signal<br>Name | Pin | I/O<br>Type | Function                                                                                                                    |

|----------------|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------|

| D11            | 49  | I/O         | Data bus bit 11                                                                                                             |

| D12            | 50  | I/O         | Data bus bit 12                                                                                                             |

| D13            | 53  | I/O         | Data bus bit 13                                                                                                             |

| D14            | 54  | I/O         | Data bus bit 14                                                                                                             |

| D15            | 57  | I/O         | Data bus bit 15                                                                                                             |

| D16            | 58  | I/O         | Data bus bit 16                                                                                                             |

| D17            | 59  | I/O         | Data bus bit 17                                                                                                             |

| D18            | 60  | I/O         | Data bus bit 18                                                                                                             |

| D19            | 61  | I/O         | Data bus bit 19                                                                                                             |

| D20            | 62  | I/O         | Data bus bit 20                                                                                                             |

| D21            | 63  | I/O         | Data bus bit 21                                                                                                             |

| D22            | 64  | I/O         | Data bus bit 22                                                                                                             |

| D23            | 67  | I/O         | Data bus bit 23                                                                                                             |

| D24            | 68  | I/O         | Data bus bit 24                                                                                                             |

| D25            | 69  | I/O         | Data bus bit 25                                                                                                             |

| D26            | 70  | I/O         | Data bus bit 26                                                                                                             |

| D27            | 71  | I/O         | Data bus bit 27                                                                                                             |

| D28            | 72  | I/O         | Data bus bit 28                                                                                                             |

| D29            | 73  | I/O         | Data bus bit 29                                                                                                             |

| D30            | 74  | I/O         | Data bus bit 30                                                                                                             |

| D31            | 75  | I/O         | Data bus bit 31                                                                                                             |

| DMAA0          | 9   | 0           | DMA Channel 0 Acknowledge. DMAA0 has an active level when a transaction is taking place between the 403GB and a peripheral. |

| DMAA1          | 10  | 0           | DMA Channel 1 Acknowledge. See description of DMAA0                                                                         |

Table 4. 403GB Signal Descriptions (Continued)

| Signal<br>Name | Pin | I/O<br>Type | Function                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMAR0          | 15  | I           | DMA Channel 0 Request. When the 403GB is the bus master, external devices request a DMA transfer on channel 0 by putting a logic 0 on DMARO.  When the 403GB HoldAck output is active and the 403GB is not the bus master, active requests on DMARO are ignored until the 403GB becomes the bus master.                                                                                                        |

| DMAR1          | 16  | I           | DMA Channel 1 Request. See description of DMAR0                                                                                                                                                                                                                                                                                                                                                                |

| DRAMOE         | 125 | 0           | DRAM Output Enable. DRAMOE has an active level when either the 403GB or an external bus master is reading from a DRAM bank. This signal enables the selected DRAM bank to drive the data bus.                                                                                                                                                                                                                  |

| DRAMWE         | 126 | 0           | DRAM Write Enable. DRAMWE has an active level when either the 403GB or an external bus master is writing to a DRAM bank.                                                                                                                                                                                                                                                                                       |

| EOTO/TCO       | 112 | I/O         | End of Transfer 0 / Terminal Count 0. The function of the EOT0/TC0 is controlled via the EOT/TC bit in the DMA Channel 0 Control Register. When EOT0/TC0 is configured as an End of Transfer pin, external users may stop a DMA transfer by placing a logic 0 on this input pin. When configured as a Terminal Count pin, the 403GB signals the completion of a DMA transfer by placing a logic 0 on this pin. |

| EOT1/TC1       | 113 | I/O         | End of Transfer1 / Terminal Count 1. See description of EOT0/TC0                                                                                                                                                                                                                                                                                                                                               |

| Error          | 124 | 0           | System Error. Error goes to a logic 1 whenever a machine check error is detected in the 403GB. The Error pin then remains a logic 1 until the machine check error is cleared in the Exception Syndrome Register and/or Bus Error Syndrome Register.                                                                                                                                                            |

|                | 1   |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6   |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                          |

|                | 20  |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                          |

| GND            | 38  |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                          |

|                | 51  |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                          |

|                | 55  |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                          |

|                | 66  |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                          |

Table 4. 403GB Signal Descriptions (Continued)

| Signal<br>Name | Pin | I/O<br>Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | 76  |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | 84  |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GND            | 100 |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | 115 |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | 120 |             | Ground. All ground pins must be used.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Halt           | 22  | 1           | Halt from external debugger, active low.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HoldAck        | 122 | 0           | Hold Acknowledge. HoldAck outputs a logic 1 when the 403GB relinquishes its external buses to an external bus master. The external bus master uses the HoldReq pin to request use of the 403GB buses.                                                                                                                                                                                                                                                         |

| HoldReq        | 25  | 1           | Hold Request. External bus masters can request the 403GB bus by placing a logic1 on this pin. When the 403GB HoldAck pin is logic 1, the 403GB has relinquished its address, data and control buses to the external master. The external bus master relinquishes the buses to the 403GB by deasserting HoldReq. The 403GB then deasserts HoldAck during the following cycle.                                                                                  |

| INT0/TestC     | 29  | I           | Interrupt 0. While Reset is not active, INT0 is an interrupt input to the 403GB and users may program the pin to be either edge-triggered or level triggered and may also program the polarity to be active high or active low. The IOCR contains the bits necessary to program the trigger type and polarity.  TestC. Reserved for manufacturing test during the reset interval. While Reset is active, this signal should be tied low for normal operation. |

| INT1/TestD     | 30  | I           | Interrupt 1 / TestD. See description of INT0/TestC.                                                                                                                                                                                                                                                                                                                                                                                                           |

| INT2           | 31  | I           | Interrupt 2. INT2 is an interrupt input to the 403GB and users may program the pin to be either edge-triggered or level triggered and may also program the polarity to be active high or active low. The IOCR contains the bits necessary to program the trigger type and polarity.                                                                                                                                                                           |

| INT3           | 32  | 1           | Interrupt 3. See description of INT2                                                                                                                                                                                                                                                                                                                                                                                                                          |

| INT4           | 33  | I           | Interrupt 4. See description of INT2                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 4. 403GB Signal Descriptions (Continued)

| Signal<br>Name | Pin | I/O<br>Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IVR            | 35  |             | Interface voltage reference. When connected to 3.3V supply, allows the device to interface to an exclusively 3V system. When connected to 5V supply, allows the device to interface to 5V or mixed 3V/5V system. If any input or output connects to 5V system, this pin must be connected to 5V supply.                                                                                                                       |

| OE / XSize1    | 110 | O/I         | Output Enable / External Master Transfer Size 1. When the 403GB is bus master, $\overline{OE}$ enables the selected SRAMs to drive the data bus. The timing parameters of $\overline{OE}$ relative to the chip select, $\overline{CS}$ , are programmable via bits in the 403GB bank registers. When the 403GB is not bus master, $\overline{OE}$ / XSize1 is used as one of two external transfer size input bits, XSize0:1. |

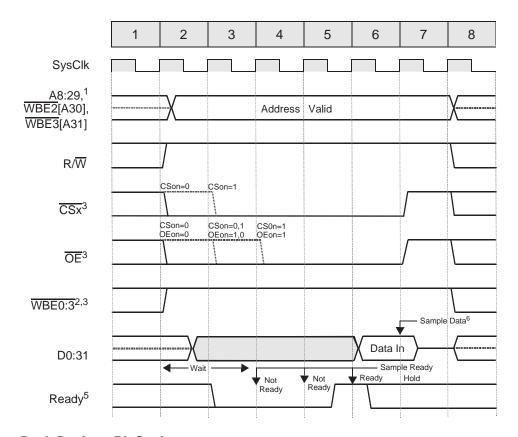

| Ready          | 24  | I           | Ready. Ready is used to insert externally generated (device-paced) wait states into bus transactions. The Ready pin is enabled via the Ready Enable bit in 403GB bank registers.                                                                                                                                                                                                                                              |

| Reset          | 78  | I/O         | Reset. A logic 0 input placed on this pin for eight SysClk cycles causes the 403GB to begin a system reset. When a system reset is internally invoked, the Reset pin becomes a logic 0 output for three SysClk cycles, and the system must maintain Reset active for a total of eight cycles minimum.                                                                                                                         |

| R/W            | 111 | I/O         | Read / Write. When the 403GB is bus master, R/\overline{W} is an output which is high when data is read from memory and low when data is written to memory. R/\overline{W} is driven with the same timings as the address bus.  When the 403GB is not bus master, R/\overline{W} is an input from the external bus master which indicates the direction of data transfer.                                                     |

| SysClk         | 26  | I           | SysClk is the processor system clock input. SysClk supports a 50/50 duty cycle clock input at the rated chip frequency.                                                                                                                                                                                                                                                                                                       |

| тск            | 18  | I           | JTAG Test Clock Input. TCK is the clock source for the 403GB test access port (TAP). The maximum clock rate into the TCK pin is one half of the processor SysClk clock rate.                                                                                                                                                                                                                                                  |

| TDI            | 13  | I           | Test Data In. The TDI is used to input serial data into the TAP. When the TAP enables the use of the TDI pin, the TDI pin is sampled on the rising edge of TCK and this data is input to the selected TAP shift register.                                                                                                                                                                                                     |

| TDO            | 12  | 0           | Test Data Output. TDO is used to transmit data from the 403GB TAP. Data from the selected TAP shift register is shifted out on TDO.                                                                                                                                                                                                                                                                                           |

| TestA          | 27  | I           | Reserved for manufacturing test. Tied low for normal operation.                                                                                                                                                                                                                                                                                                                                                               |

Table 4. 403GB Signal Descriptions (Continued)

| Signal<br>Name  | Pin | I/O<br>Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TestB           | 28  | I           | Reserved for manufacturing test. Tied high for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TMS             | 21  | I           | Test Mode Select. The TMS pin is sampled by the TAP on the rising edge of TCK. The TAP state machine uses the TMS pin to determine the mode in which the TAP operates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 | 7   |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 19  |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 42  |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 52  |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 56  |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V               | 65  |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>DD</sub> | 77  |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 85  |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 91  |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 105 |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 114 |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 121 |             | Power. All power pins must be connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

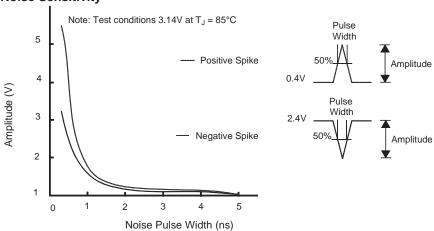

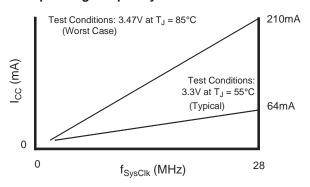

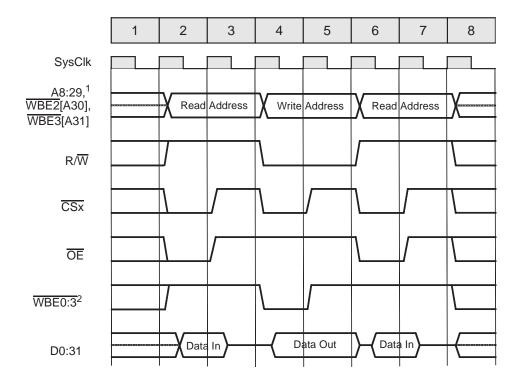

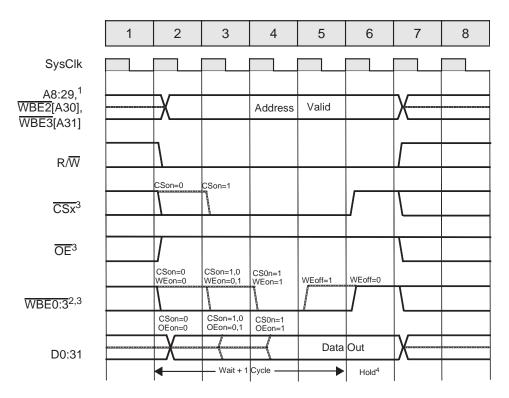

| WBEO / A6       | 106 | O/I         | Write Byte Enable 0 / Address Bus Bit 6. When the 403GB is bus master, the write byte enable outputs, \overline{WBE0:3}, select the active byte(s) in a memory write access. For 8-bit memory regions, \overline{WBE2} and \overline{WBE3} become address bits 30 and 31 and \overline{WBE0} is the write-enable line. For 16-bit memory regions, \overline{WBE2:WBE3} are address bits A30:A31 and \overline{WBE0} and \overline{WBE1} are the high byte and low write enables, respectively. For 32-bit memory regions, \overline{WBE0:3} are write byte enables for bytes 0-3 on the data bus, respectively. When the 403GB is not bus master, \overline{WBE0:1} are used as the A6:7 inputs (for bank register selection) and \overline{WBE2:3} are used as the A30:31 inputs (for byte selection and page crossing detection). |