## **Advance Information**

## **High Resolution Frequency Generator**

### **General Description**

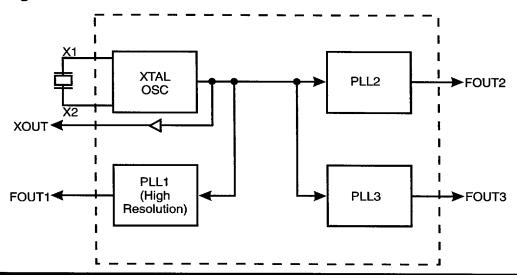

The ICS9123 is a multiple output frequency generator utilizing PLL (Phase-Lock Loop) frequency synthesis. It contains three PLL frequency synthesizers and an internal crystal oscillator reference circuit. Thus, with only an external crystal and the necessary power supply decoupling capacitors, four different output clock frequencies can be provided.

PLL1 of the device has the ability to provide high output frequency resolution (±50 ppm). This makes it suitable for providing clocks for system functions such as modems, ethernet, and sound synthesis. PLL2 and PLL3 provide output clocks for other system applications such as microprocessors and DSP chips. For example, in modem applications, the ICS9123 generates the high resolution clock generator for the A/D converter and two lower resolution clocks for the microprocessor and DSP.

Each of the PLL clock generators has a ROM based frequency selection table which is addressed through device input pins. PLL1 has eight frequency select locations; PLL2 and PLL3 each has four. The ROM based tables are preprogrammed. However, they can be customized for the user specific applications.

#### **Features**

- Cost effective solution for MODEM, ETHERNET and AD1848 applications

- Three independent PLLs

- Four clock frequencies generated from one crystal

- One high resolution PLL provides ±50 ppm accuracy

- Eight ROM based frequency selections for the high resolution PLL1

- Four ROM based frequency selections each for PLL2 and PLL3

- 3.3V or 5V power supply

- On-chip loop filter components

- Low power CMOS technology

- 20- or 16-pin PDIP or SOIC package

#### **Block Diagram**

ICS9123RevA111095

**■** 4825758 0002350 640 **■**

## **ICS9123**

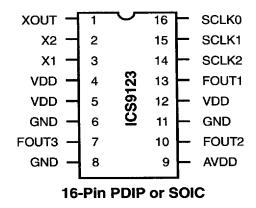

### **Pin Configuration**

## **Decoding Table for Clock Frequency** (Using 14.318 MHz Input Frequency)

| SCLK2                           | SCLK1                      | SCLK0                           | FOUT1*<br>(MHz)                                                                            | FOUT2<br>(MHz)                                               | FOUT3<br>(MHz)                                               |

|---------------------------------|----------------------------|---------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|

| 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | 8.06400<br>19.66080<br>29.49120<br>11.05920<br>13.82400<br>3.68640<br>14.74560<br>16.00031 | 19.7<br>29.5<br>8.06<br>14.6<br>19.7<br>29.5<br>8.06<br>14.6 | 29.5<br>8.06<br>19.7<br>16.5<br>29.5<br>8.06<br>19.7<br>16.5 |

\*FOUT1 frequencies shown are accurate to within 2 PPM.

### **Pin Descriptions**

| PIN NUMBER | PIN NAME | TYPE     | DESCRIPTION                                  |  |

|------------|----------|----------|----------------------------------------------|--|

| 1          | XOUT     | Output   | Crystal buffered output.                     |  |

| 2          | X2       | Output   | Connect crystal.                             |  |

| 3          | X1       | Input    | Connect crystal.                             |  |

| 4          | VDD      | -        | 3V or 5V power supply.                       |  |

| 5          | VDD      | -        | 3V or 5V power supply.                       |  |

| 6          | GND      | <u>-</u> | GROUND.                                      |  |

| 7          | FOUT3    | Output   | Output frequency of one of 3 PLLs.           |  |

| 8          | GND      | _        | GROUND.                                      |  |

| 9          | VDD      | -        | 3V or 5V power supply.                       |  |

| 10         | FOUT2    | Output   | Output frequency of one of 3 PLLs.           |  |

| 11         | GND      | -        | GROUND.                                      |  |

| 12         | VDD      | -        | 3V or 5V power supply.                       |  |

| 13         | FOUT1    | Output   | Output frequency of the high resolution PLL. |  |

| 14         | SCLK2    | Input    | CPU clock frequency SELECT2 (has pull-up).   |  |

| 15         | SCLK1    | Input    | CPU clock frequency SELECT1 (has pull-up).   |  |

| 16         | SCLK0    | Input    | CPU clock frequency SELECTO (has pull-up).   |  |

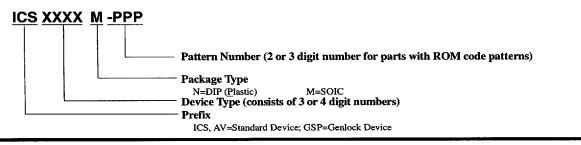

# Ordering Information ICS9123N-01 or ICS9123M-01

ADVANCE INFORMATION documents contain information on new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

Example:

2