# **TMC2255**

# CMOS 3 x 3, 5 x 5 Image Convolver

### 8 x 8 Bits, 12 MHz Data Rate

#### **Features**

- 8-bit data and coefficient input precision

- Triple 3x1 matrix-vector multiplication mode

- 3x3 and 5x5 two-dimensional convolution modes

- TTL-compatible I/O with three-state output bus

- Offered in 68-contact plastic chip carrier (PLCC)

- Built-in 8-, 9-, and 12-bit arithmetic limiter

- · Two's complement, unsigned, or mixed data formats

## **Applications**

- RGB to/from YUV/YIQ color space conversion

- 3x3 or 5x5 two-dimensional FIR filtering

- · Edge enhancement and general image processing

- · Robotics and image recognition

- Electronic darkroom

- · Desktop publishing

## **Description**

Like the faster TMC2250, the low-cost TMC2255 can perform a triple 3x1 matrix-vector multiplication or a 3x3 convolution. It can also perform a 5x5 convolution with bidimensionally symmetrical coefficients. The on-chip coefficient memory stores four sets of nine 8-bit two's complement coefficients. The device accepts unsigned and/or two's complement data at 1/3 of the applied clock rate.

The 3 (3x1) matrix multiply mode supports various 3-space numerical operations, such as video standards conversion (e.g. YIQ to RGB) or three-dimensional perspective transformation. Three input ports accept the 8-bit two's complement and/or unsigned magnitude data. The two remaining input ports can be loaded with coefficients and/or device control parameters "on-the-fly." In this mode, an output is generated on every clock cycle.

The 3x3 and 5x5 pixel image convolver modes support numerous functions, including static filtering and edge detection. On every third clock cycle, the TMC2255 accepts three (3x3 mode) or five (5x5 mode) data inputs. In the 5x5 mode, the coefficient kernel must be symmetric both horizontally and vertically. Outputs from the device are generated on every third clock cycle, matching the input pixel data rate, and can be limited ("clipped") to 8, 9, or 12 bits.

The TMC2255 will operate at clock rates of 0 to 36 MHz over the full commercial temperature (0°C to 70°C) and supply voltage ranges.

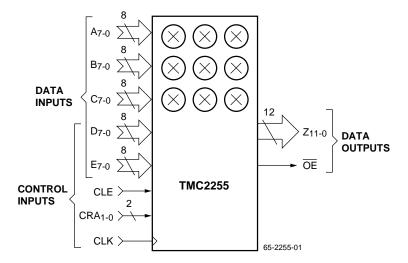

## **Logic Symbol**

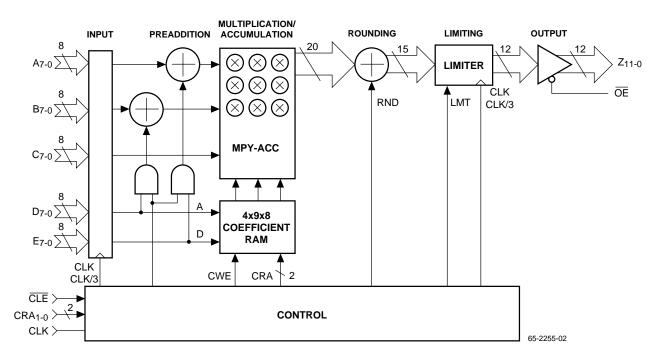

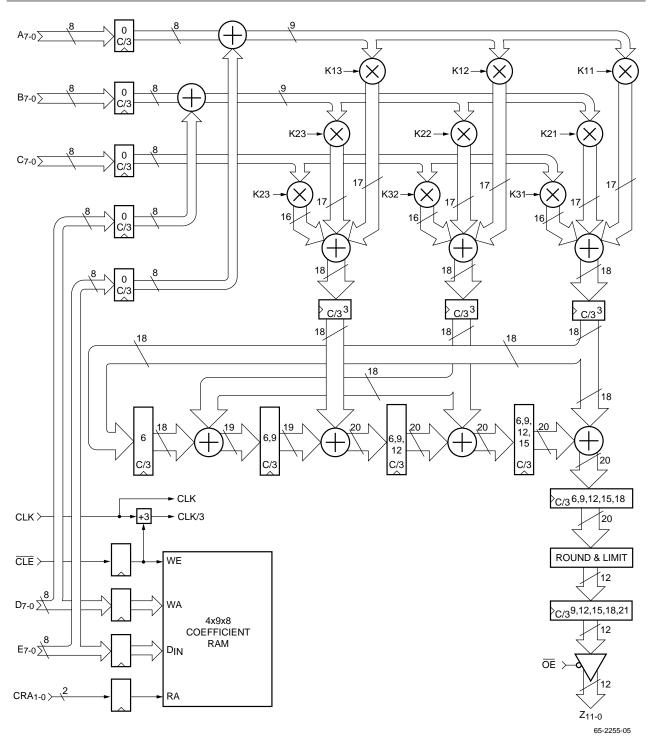

## **Structural Block Diagram**

## **Functional Description**

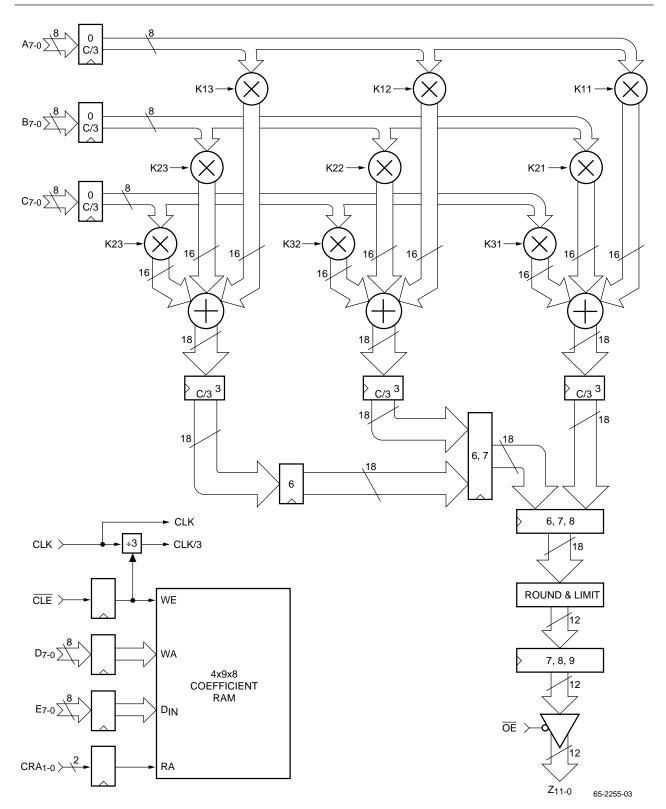

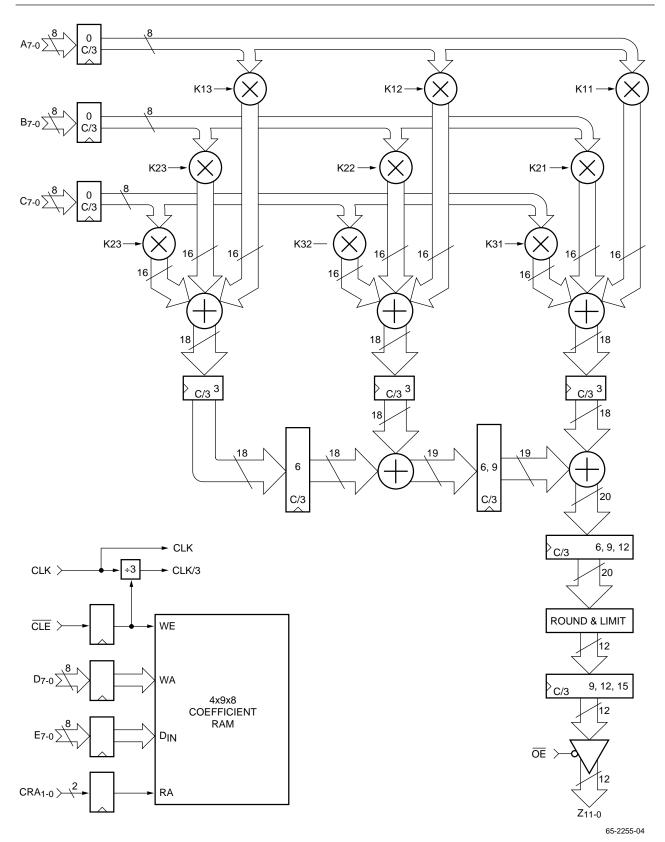

The TMC2255 contains an array of multipliers and adders, four 9x8-bit coefficient "pages" and a global control block, all of which can be initialized or reconfigured through ports D and E when  $\overline{\text{CLE}}$  is LOW. Device parameters include matrix coefficient, internal device configuration (mode), rounding precision, and input/output data formats (two's complement, unsigned, or mixed). After the control parameters have been loaded, device operation commences with the next clock rising edge on which  $\overline{\text{CLE}}$  returns HIGH. Depending on the mode selected, three or five data are input in parallel and proceed through a sequence of operations: Input, Preaddition, Multiply-Accumulation, Rounding, Limiting, and Output. See Figures 1–3 and the Structural Block Diagram.

#### Input Stage

Inputs are supplied to ports A through C in all operating modes on every third clock cycle, beginning with the clock rising edge that contains the most recent  $\overline{\text{CLE}}$  LOW-to-HIGH transition. Control and/or coefficient parameters can be input through ports D and E during any of the three mas-

ter clock cycles that make up each data cycle. In the 5x5 convolution mode, data enter the device through ports A–E. Control and/or coefficients may be updated through ports D and E on the remaining two cycles of each clock triplet.

Input data formats may be unsigned and/or two's complement, as identified in the mode select field of port E.

#### Preaddition

In and only in 5x5 convolution, the horizontal and vertical symmetry of the coefficient permits nine multipliers to do the work of 25. To facilitate this, the data input into ports A and E are pre-added before multiplication, as are the B and D inputs. See Figure 3, the 5x5 Block Diagram.

#### **Coefficient Memory**

The TMC2255 contains enough memory to store four "pages" of nine 8-bit two's complement coefficients each. When  $\overline{\text{CLE}}$  is LOW, a new coefficient is written through port E to the page and location address identified on port D. On

every third clock cycle, the coefficient page to be read and used in the immediate 3-cycle computation set is selected by  $CRA_0$  and  $CRA_1$ . Of the nine coefficients per page, K1, i (i = 1 to 3) process the port A (and E) data; K2, i, the port B and (D) data; and K3, i, the port C data.

#### **Multiplication and Accumulation**

The device computes nine products during every three clock cycles, accumulating them internally to full precision.

#### Rounding

Accumulated sums of products are rounded before the last 5 or 6 bits are truncated. Rounding is performed by adding "010000" or "100000" to the emerging data stream, according to the desired precision of the output results. When  $\overline{CLE}=0$  and D=0XXX1111, pin  $E_6$  sets the chip's rounding position, viz:  $E_6=0$ : add .010000 and use  $Z_0$  as least significant bit;  $E_6=1$ : add .100000 and use  $Z_1$  as least significant bit, ignoring  $Z_0$ .

#### **Output Limiting**

The device provides programmable output limiting in unsigned (UN) and/or two's complement (TC) format and for 8, 9, or 12 bits of output precision (including  $Z_0$ ). In 3 (3x1) mode, for an RGB-to-YIQ transformation, the device can limit  $Z_1$  (Y) to 9 bits unsigned while limiting  $Z_3$  (I) and  $Z_3$  (Q) to 9 bits two's complement.

#### **Outputs**

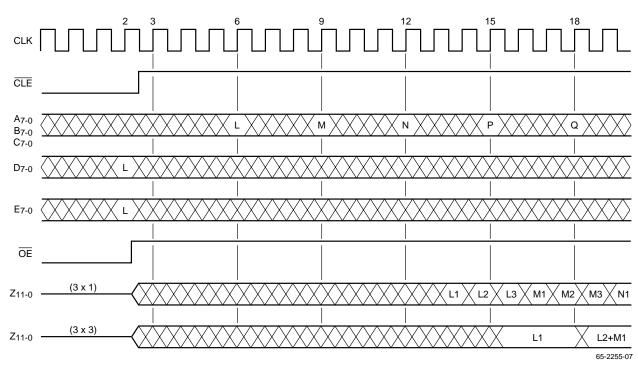

Output is through the 12-bit Z port, which provides 1/2 or 1 LSB precision, relative to the input format. In the 3 (3x1) mode, three outputs will appear consecutively at the Z port during each triple clock cycle; for data input on clock rising edge 0, these results will emerge tDO after clock rising edges 7, 8, and 9. In both convolution modes the results are output at 1/3 the device master clock rate, with the first point of the impulse response emerging after clock rising edge 9. To facilitate connection to a bus, the output buffers are enabled and disabled (placed in high-impedance state) by asynchronous control  $\overline{\rm OE}$ .

Figure 1. Functional Block Diagram, 3 (3x1) Mode

Figure 2. Functional Block Diagram, 3x3 Mode

Figure 3. Functional Block Diagram, 5x5 Mode

# **Pin Assignments**

| Pin | Name            | Pin | Name           | Pin | Name           | Pin | Name             |

|-----|-----------------|-----|----------------|-----|----------------|-----|------------------|

| 1   | GND             | 18  | GND            | 35  | GND            | 52  | GND              |

| 2   | V <sub>DD</sub> | 19  | Z <sub>6</sub> | 36  | D <sub>7</sub> | 53  | V <sub>DD</sub>  |

| 3   | A <sub>2</sub>  | 20  | Z <sub>5</sub> | 37  | D <sub>6</sub> | 54  | В7               |

| 4   | A <sub>1</sub>  | 21  | Z <sub>4</sub> | 38  | D <sub>5</sub> | 55  | B <sub>6</sub>   |

| 5   | A <sub>0</sub>  | 22  | Z <sub>3</sub> | 39  | D <sub>4</sub> | 56  | B <sub>5</sub>   |

| 6   | CLE             | 23  | Z <sub>2</sub> | 40  | D <sub>3</sub> | 57  | B <sub>4</sub>   |

| 7   | ŌĒ              | 24  | Z <sub>1</sub> | 41  | D <sub>2</sub> | 58  | B <sub>3</sub>   |

| 8   | CLK             | 25  | Z <sub>0</sub> | 42  | D <sub>1</sub> | 59  | B <sub>2</sub>   |

| 9   | GND             | 26  | GND            | 43  | D <sub>0</sub> | 60  | B <sub>1</sub>   |

| 10  | V <sub>DD</sub> | 27  | E <sub>7</sub> | 44  | C <sub>7</sub> | 61  | B <sub>0</sub>   |

| 11  | Z <sub>11</sub> | 28  | E <sub>6</sub> | 45  | C <sub>6</sub> | 62  | CRA <sub>1</sub> |

| 12  | Z <sub>10</sub> | 29  | E <sub>5</sub> | 46  | C <sub>5</sub> | 63  | CRA <sub>0</sub> |

| 13  | GND             | 30  | E4             | 47  | C4             | 64  | A <sub>7</sub>   |

| 14  | Z9              | 31  | E3             | 48  | C <sub>3</sub> | 65  | A <sub>6</sub>   |

| 15  | Z <sub>8</sub>  | 32  | E <sub>2</sub> | 49  | C <sub>2</sub> | 66  | A <sub>5</sub>   |

| 16  | Z <sub>7</sub>  | 33  | E <sub>1</sub> | 50  | C <sub>1</sub> | 67  | A <sub>4</sub>   |

| 17  | V <sub>DD</sub> | 34  | E <sub>0</sub> | 51  | C <sub>0</sub> | 68  | A3               |

# **Pin Descriptions**

| Pin Name                           | Pin Number                                   | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inputs                             | ,                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CLK                                | 8                                            | <b>Master chip clock</b> , <b>0 to 30MHz</b> . All operations are referenced to the rising edges of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A0-7, B0-7,<br>C0-7, D0-7,<br>E0-7 | 5-3, 68-64;<br>61-54; 51-44;<br>43-36; 34-27 | <b>Data inputs.</b> Of the device's five 8-bit data input ports, A, B, and C are used exclusively as data inputs, whereas D and E are also used to program the device (see description of $\overline{\text{CLE}}$ pin). For 5x5 convolution, all five ports accept incoming data. In the other modes, only ports A-C accept incoming data, leaving D and E dedicated to control and coefficient values, which may be updated at any time. In all modes, data are loaded on every third rising edge for which $\overline{\text{CLE}}$ makes a 0-to-1 transition. Bits A7, B7, are the two's complement sign bits or most significant unsigned bitsl bits A0, B0, are the least significant bits (LSBs).                                                                                                                                                                                                 |

| CLE                                | 6                                            | Active-LOW coefficient and control load enable. When $\overline{\text{CLE}}$ is LOW, E becomes the input port for the coefficients, and D becomes the coefficient write address and control port. When $\overline{\text{CLE}}$ is HIGH, all coefficients are held unchanged. A LOW-to-HIGH transition at $\overline{\text{CLE}}$ also synchronizes the TMC2255, ushering in a new data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CRA <sub>1-0</sub>                 | 62-63                                        | Coefficient read address. The chip can hold four "pages" of nine coefficients each. These two pins determine which of the four coefficient sets is to be used with the data entering during that cycle.  The timing of coefficient selection by CRA is mode dependent. In the 3 (3x1) mode, CRA influences all coefficients simultaneously. In the 3x3 and 5x5 convolution modes, however, CRA selects the coefficients for each multiplier column individually, i.e. three per clock cycle from left to right (see Figure 3). CRA should be changed only on "data input" clock cycles to avoid corrupting 3x3 or 3 (3x1) work in progress. CRA should not be updated during a 5x5 operation whose result is needed.  When updating coefficients on-the-fly, the user should not set CRA <sub>1-0</sub> and D <sub>5-4</sub> to the same page, but should read from one page while writing to another. |

## Pin Descriptions (continued)

| Pin Name          | Pin Number              | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ŌĒ                | 7                       | Asynchronous, active-LOW output enable. When $\overline{OE}$ is LOW, the output drivers are enabled. When $\overline{OE}$ is HIGH, they are disabled (high-impedance).                                                                                                                                                                                                                                                                                                                                                                                         |

| Outputs           |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Z <sub>11-0</sub> | 25-19, 16-14,<br>12-11  | <b>Data outputs.</b> Outputs available on the Z port are enabled by $\overline{\text{OE}}$ . Z <sub>11</sub> is the unsigned MSB or two's complement MSB/sign bit; Z <sub>1</sub> is the integer LSB ("ones' digit"). Z <sub>0</sub> is the 1/2 fractional digit. In the 3 (3x1) mode (E = XXXXX0XX), a new valid result will emerge tDO after every rising edge of CLK. In the other modes (E = XXXXX1XX), a result emerges after every third rising edge of CLK. Then 9-bit limiting is used, bits Z <sub>11</sub> through Z <sub>8</sub> will be identical. |

| Power             |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GND               | 1, 9, 13, 26,<br>35, 52 | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDD               | 2, 10, 17, 53           | Supply Voltage (+5).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## **Operation and Timing**

Before operation, the TMC2255 must be initalized, i.e. loaded with coefficients and set to the desired operating mode, data format, and rounding precision. The chip is programmed via ports D and E, which double as data input ports in 5x5 mode.

### Initialization

#### **Chip Select**

This control is accessed through bit 7 of port D. When  $\overline{\text{CLE}}$  is LOW, D7 must be LOW to allow the coefficient/control information to be updated. If D7 is HIGH when  $\overline{\text{CLE}}$  is force LOW, the device will not allow the coefficient or control information to be updated, and device execution will begin or continue as commanded on the previous LOW-to-HIGH transition of  $\overline{\text{CLE}}$ . Holding D7 HIGH (at least when  $\overline{\text{CLE}}$  is LOW) permits the system to resynchronize the chip without changing any coefficients or configuration parameters.

### **Coefficient Loading**

When  $\overline{\text{CLE}}$  and D7 are LOW, the coefficient values presented to port 6 are loaded into the coefficient position and page registers selected by port D, as shown in Table 1.

Each of the four "pages" YY comprises a full set of nine coefficients (one per filter tap).

**Table 1. Coefficient Loading**

| When D7-0 = | Update from E <sub>7-0</sub> : Coef | Page |

|-------------|-------------------------------------|------|

| 0XYY0000    | 1,1                                 | YY   |

| 0XYY0001    | 1,2                                 | YY   |

| 0XYY0010    | 1,3                                 | YY   |

| 0XYY0100    | 2,1                                 | YY   |

| 0XYY0101    | 2,2                                 | YY   |

| 0XYY0110    | 2,3                                 | YY   |

| 0XYY1000    | 3,1                                 | YY   |

| 0XYY1001    | 3,2                                 | YY   |

| 0XYY1010    | 3,3                                 | YY   |

| 0XXX0X11    | Hold all coefficients               |      |

| 0XXXX011    | Hold all coefficients               |      |

| 0XXX110X    | Hold all coefficients               |      |

| 0XXX11X0    | Hold all coefficients               |      |

| 0XXX1111    | Control information                 |      |

| 1XXXXXXX    | Hold all coefficients               |      |

X = Don't Care

#### **Mode Selection**

When  $\overline{\text{CLE}} = 0$  and D = 0XXX1111, pins  $E_{2-0}$  select the chip's operating MODE and input data formats, as shown in Table 2.

**Table 2. Mode Selection**

|                                                                                                                                                                                                                                                             |                                 | Data Formats   |            |       |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------|------------|-------|--|

| When E7-0 =                                                                                                                                                                                                                                                 | Mode =                          | Α              | В          | С     |  |

| 0XXXX000                                                                                                                                                                                                                                                    | 3 (3x1) mat mpy                 | TC             | TC         | TC    |  |

| 0XXXX001                                                                                                                                                                                                                                                    | 3 (3x1) mat mpy                 | UN             | TC         | TC    |  |

| 0XXXX010                                                                                                                                                                                                                                                    | RESERVED—Do not use             |                |            |       |  |

| 0XXXX011                                                                                                                                                                                                                                                    | 3 (3x1) mat mpy                 | UN             | UN         | UN    |  |

| Z1 = A*K1,1 + B*K2,1 + C*K3,1                                                                                                                                                                                                                               |                                 | Firs           | t of 3 res | sults |  |

| Z2 = A*K1,2 + B*K2,2 + C*K3,2                                                                                                                                                                                                                               |                                 |                |            |       |  |

| Z3 = A*K1,3 + B*K2,3 + C*K3,3                                                                                                                                                                                                                               |                                 | Last of 3 resu |            | sults |  |

| 0XXXX100                                                                                                                                                                                                                                                    | 3x3 convolution                 | TC             | TC         | TC    |  |

| 0XXXX101                                                                                                                                                                                                                                                    | 3x3 convolution                 | UN             | UN         | UN    |  |

| Z = A1*K1,1 + B1*K2,1 + C1*K3,1 +<br>A2*K1,2 + B2*K2,2 + C2*K3,2 +<br>A3*K1,3 + B3*K2,3 + C3*K3,3                                                                                                                                                           |                                 |                |            |       |  |

| 0XXXX110                                                                                                                                                                                                                                                    | 5x5 convolution                 | TC             | TC         | TC    |  |

| 0XXXX111                                                                                                                                                                                                                                                    | 5x5 convolution                 | UN             | UN         | UN    |  |

| Z = A1*K1,3 + B1*K2,3 + C1*K3,3 + D1*K2,3 + E1*K1,3 + A2*K1,2 + B2*K2,2 + C2*K3,2 + D2*K2,2 + E2*K1,2 + A3*K1,1 + B3*K2,1 + C3*K3,1 + D3*K2,1 + E3*K1,1 + A4*K1,2 + B4*K2,2 + C4*K3,2 + D4*K2,2 + E4*K1,2 + A5*K1,3 + B5*K2,3 + C5*K3,3 + D5*K2,3 + E5*K1,3 |                                 |                |            |       |  |

| 1XXXXXXX                                                                                                                                                                                                                                                    | Unchanged from previous setting |                |            |       |  |

Coefficients are always 8-bit two's complement.

#### Rounding

All computations are rounded internally following the final accumulation of products. Rounding position depends on the output format. If the user desires outputs with 1/2 LSB precision (relative to the inputs) then rounding is performed into  $Z_{-1}$ , just to the right of the LSB of the output port,  $Z_{0}$ . For 1 LSB precision, rounding is into  $Z_{0}$ , and the output is on pins  $Z_{11-1}$  only.

Table 3. Rounding

| When E <sub>7-0</sub> = | Outputs are                               | Rounded at      |

|-------------------------|-------------------------------------------|-----------------|

| 00XXXXXX                | Z <sub>11</sub> –Z <sub>0</sub> (12 bits) | Z <sub>-1</sub> |

| 01XXXXXX                | Z <sub>11</sub> –Z <sub>1</sub> (11 bits) | Z-0             |

| 1XXXXXXX                | Unchanged from previous setting           |                 |

### **Output Limiting**

When  $\overline{\text{CLE}} = 0$  and D = 0XXX1111, pins E<sub>5-3</sub> tell the chip to which numerical format(s) to limit the emerging results. Unsigned (UN), two's complement (TC), and mixed data formats of 8, 9, or 12 bits (including Z0) are supported, as shown in Table 4. Limit "Z" applies to 3x3 and 5x5 convolutional modes; limits Z1, Z2, Z3 apply to 3(3x1) mode.

Prior to output, the limiter (if enabled) tests the leading bits of the emerging result. In the unsigned limit modes, if the MSB = 1, denoting a negative value, the output is forced to 0; if the MSB = 0 but any other bit above the 8, 9, or 12 bit output field = 1, the output is forced to 11111111111.1. In the TC9 limit mode, values above 127.5 (00001111111.1) are forced to 00001111111.1 and values below -128 become 11100000000.0. In the TC12 limit mode, values above 1023.5 (01111111111.1) are forced to 01111111111.1, and values below -1024 become 10000000000.0. If full LSB rounding (E6 = 1) is used, output bit Z0 is ignored, each data format is correspondingly 1 bit narrower than shown in Table 4, and the .5 fractions disappear from the range limits.

| Table 4. C | Dutput L | _imitina |

|------------|----------|----------|

|------------|----------|----------|

| E <sub>7-0</sub> = | Limit Z1 or Z                   | Limit Z2 | Limit Z3 | Range (RND = 0) |  |

|--------------------|---------------------------------|----------|----------|-----------------|--|

| 0X000XXX           | Limiter disabled                |          |          |                 |  |

| 0X001XXX           | UN9                             | UN9      | UN9      | 0, 255.5        |  |

| 0X010XXX           | TC12                            | TC12     | TC12     | -1024, 1023.5   |  |

| 0X011XXX           | UN12                            | UN12     | UN12     | 0, 2047.5       |  |

| 0X100XXX           | TC9                             | TC9      | TC9      | -128, 127.5     |  |

| 0X101XXX           | UN9                             | TC9      | TC9      | (Mixed)         |  |

| 0X110XXX           | Reserved—Do not use             |          |          | ·               |  |

| 0X111XXX           | UN8                             | UN8      | UN8      | 0, 127.5        |  |

| 1XXXXXXX           | Unchanged from previous setting |          |          |                 |  |

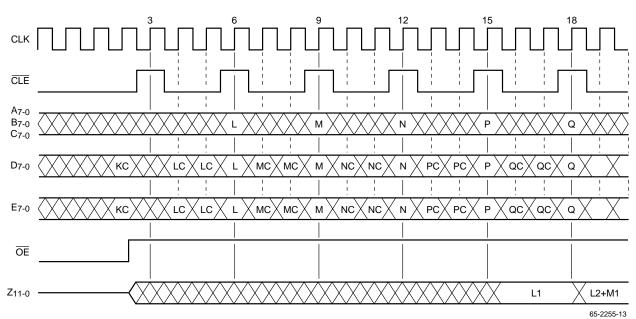

### **Timing**

### **Result Latency**

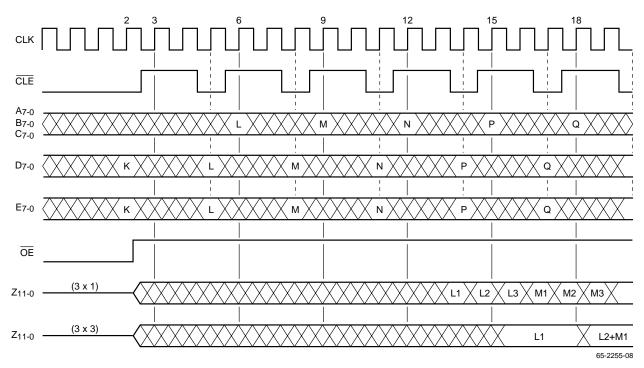

Device operating mode affects when valid results are available at the output port  $Z_{11-0}$ . The three results of a 3x1 triple dot product whose inputs enter on clock rising edge 0 will be available t<sub>DO</sub> after clock rising edges 7, 8, and 9. In a 3x3 and 5x5 convolution, the first three impulse response points will emerge after clock rising edges 9, 12, and 15. The last two points of a 5-point response (5x5 mode) will follow after rising edges 18 and 21.

#### Instructions, Inputs, and Synchronization

Each rising edge of CLK which bears a  $\overline{\text{CLE}}$  LOW-to-HIGH transition resynchronizes the device. If  $\overline{\text{CLE}}$  goes from LOW to HIGH on clock rising edge N, then the chip will resynchronize, starting a new 3-cycle sequence on that edge. It will look for incoming data at clock rising edges N+3i, where i = 1, 2, ... (see Figures 4 through 10). If  $\overline{\text{CLE}}$  is brought LOW while an operation is already in progress (e.g., to update coefficients), it should be brought HIGH only on a regular data input clock cycle (N+3i), to avoid corrupting pending results.

IF  $\overline{\text{CLE}}$  is LOW, control and/or coefficient information enetering on a rising edge of CLK will affect all subsequent data inputs until the control parameters are again updated. Internal pipelining of the controls ensures that "in progress" operations on data previously input into the device will continue unaffected, as long as  $\overline{\text{CLE}}$  is brought HIGH only on data input clock edges.

### System Timing

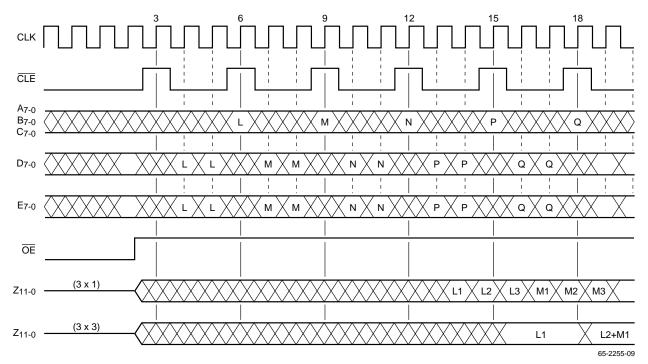

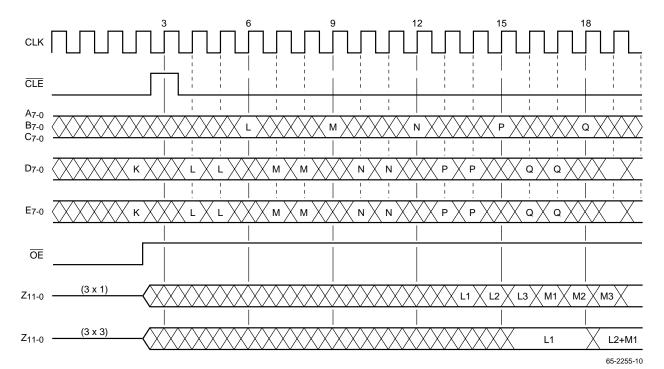

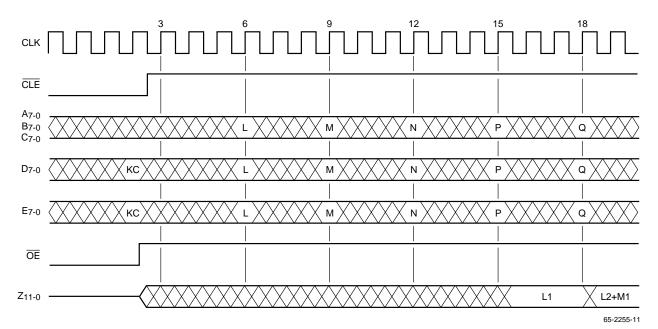

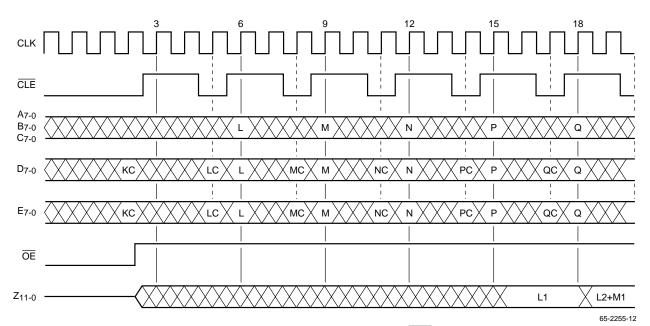

Because the TMC2255's data throughput rate is 1/3 of its incoming clock rate, the user must synchronize the data inputs with the chip's control inputs and internal operation. Figures 4 through 7 illustrate four ways to use rising edges of  $\overline{\text{CLE}}$  to align data inputs in the 3 (3x1) and 3x3 modes, whereas Figures 8 through 10 show how to use  $\overline{\text{CLE}}$  in the 5x5 mode.

In Figure 4, the  $\overline{\text{CLE}}$  0-to-1 transition on CLK rising edge 3 (t = 3) initialized the chip. The final configuration and coefficient values are loaded through ports D and E at t = 2 and the first incoming data enter ports A, B, and C on rising edge 6. In 3 (3x1) mode, the three results from the t = 6 input data emerge after t = 13, 14, and 15. In 3x3 mode, the first result from the edge 6 input data appears after edge 15 and remains until t = 18, when the second result using t = 6 inputs (which is the first result using t = 9 inputs) emerges. After t = 18, the convolution of the t = 6, t = 9, and t = 12 inputs, the last output involving the t = 6 input, appears. The part operates continuously, with inputs read on every third rising clock edge and a new output available tDO after each rising clock edge (3 (3x1) mode) or every third rising edge (3x3 mode).

In Figure 5, CLK rising edges at  $t = 3, 6, 9, \ldots$  resynchronize the chip, with configuration or coefficient updates at  $t = 2, 5, 8, \ldots$ . Data input/output timing is unchanged from Figure 3.

Figure 4. 3 (3x1), 3x3 Timing Diagram, Single CLE Rising Edge

Figure 5. 3xX Modes, Periodic Long CLE Pulses

In Figure 6, CLK rising edges at  $t = 3, 6, 9, \dots$  again resynchronize the chip, but configuration and coefficients my be changed twice as often, at  $t = 1, 2, 4, 5, 7, 8, \dots$

In Figure 7, data timing is the sames as that of Figure 4. However, since  $\overline{\text{CLE}}$  is left LOW after the one-cycle initial-

ization pulse, instructions and coefficients may be updates on every clock cycle, or three times per data input. Instructions entering between data values, e.g. at t=4 or t=5, affect the next data value (i.e., that entering at t=6). Instructions entering with a given data value (e.g., t=6) affect the next data input (i.e., at t=9).

Figure 6. 3xX Modes, Periodic Short CLE Pulses

Figure 7. 3xX Modes, Single CLE Rising Edge

In Figure 8, the CLK rising edge at t=3 synchronizes the operation. The final configuration and coefficient values are loaded through ports D and E at t=2, and the first incoming data enter ports A through E at t=6. The first results using the t=6 input appears after t=15 and remains until t=18. The last result using the t=6 input emerge after t=27 and remains until t=30. The part operates continuously, with

data inputs read on every third rising edge of CLK and a new output available tDO after every third rising edge of CLK.

In Figure 9, one new coefficient or configuration value can be input for every data input, at  $t = 5, 8, 11, \dots$

In Figure 10, two new coefficients or configuration values can be loaded for every incoming data point, at  $t = 4, 5, 7, 8, 10, 11, \ldots$

Figure 8. 5x5 Convolution, Single CLE Rising Edge

Figure 9. 5x5 Convolution, Periodic Long CLE Pulse

Figure 10. 5x5 Convolution, Periodic Short CLE Pulse

Power-Up Sequence

In 5x5 mode,  $\overline{\text{CLE}}$  should not be left LOW continuously, since ports D and E must serve as data inputs on every third clock cycle. If  $\overline{\text{CLE}}$  is LOW on a data input cycle, the chip will interpret the current D and E inputs as both data and instructions/coefficients.

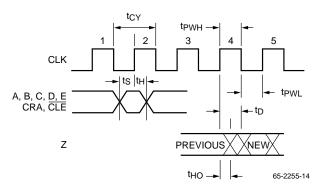

Figure 11. I/O Timing Diagram

To ensure proper operation, the TMC2255 should receive at least two clock rising edges soon after power-up, with  $\overline{\text{CLE}}$  making a 0-to-1 transition on edge 4, 5, or 6. Otherwise, some of the internal multiplexers will power up in disallowed states and draw excessive power.

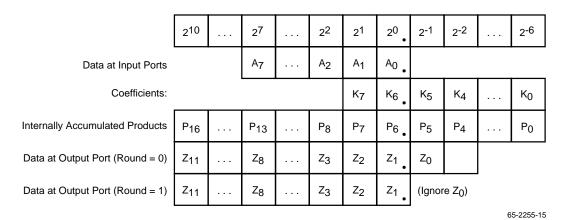

#### **Data Formats**

Figure 12 summarizes the TMC2255's data and coefficient formats for all operating modes. Although integer weighting of input data is shown, the binary point may be moved anywhere to the left, as long as the binary point of the output is moved the same distance. Likewise, the coefficient binary point can be moved, as long as the output binary point is moved equally or the data input binary point is moved in the opposite direction. In all coefficients and in all two's complement data, the most significant bit carries a negative weighting.

Figure 12. Data Formats and Bit Alignment

# Absolute Maximum Ratings (beyond which the device may be damaged)<sup>1</sup>

| Parameter                                                      | Min  | Тур | Max                   | Unit |

|----------------------------------------------------------------|------|-----|-----------------------|------|

| Supply Voltage                                                 | -0.5 |     | 7.0                   | V    |

| Input Voltage                                                  | -0.5 |     | V <sub>DD</sub> + 0.5 | V    |

| Output Applied Voltage <sup>2</sup>                            | -0.5 |     | V <sub>DD</sub> + 0.5 | V    |

| Output Forced Current <sup>3,4</sup>                           | -6.0 |     | 6.0                   | mA   |

| Short Circuit Duration (single output in HIGH state to ground) |      |     | 1                     | sec  |

| Operating Case Temperature                                     | -60  |     | 130                   | °C   |

| Junction Temperature                                           |      |     | 175                   | °C   |

| Storage Temperature                                            | -65  |     | 150                   | °C   |

| Lead Soldering Temperature (10 seconds)                        |      |     | 300                   | °C   |

### Notes:

- 1. Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied.

- 2. Applied voltage must be current limited to specified range, and measured with respect to GND.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

# **Operating Conditions**

| Param | eter                   | Package   | Min  | Nom | Max  | Unit |

|-------|------------------------|-----------|------|-----|------|------|

| VDD   | Supply Voltage         |           | 4.75 | 5.0 | 5.25 | V    |

| VIL   | Input Voltage LOW      |           |      |     | 0.8  | V    |

| VIH   | Input Voltage HIGH     |           | 2.0  |     |      | V    |

| IOL   | Output Current LOW     |           |      |     | 4.0  | mA   |

| Іон   | Output Current HIGH    |           |      |     | -2.0 | mA   |

| tCY   | Cycle Time             | TMC2255   | 33   |     |      | ns   |

|       |                        | TMC2255-1 | 27   |     |      |      |

| tpWL  | Clock Pulse Width LOW  | TMC2255   | 16   |     |      | ns   |

|       |                        | TMC2255-1 | 14   |     |      |      |

| tpWH  | Clock Pulse Width HIGH | TMC2255   | 13   |     |      | ns   |

|       |                        | TMC2255-1 | 10   |     |      |      |

| ts    | Input Setup Time       | TMC2255   | 8    |     |      | ns   |

|       |                        | TMC2255-1 | 6    |     |      |      |

| tH    | Input Hold Time        |           | 0    |     |      | ns   |

| tA    | Ambient Temperature    |           | 0    | 25  | 70   | °C   |

## **Electrical Characteristics**

| Parame | eter                         | Test Conditions                             | Min | Max  | Unit |

|--------|------------------------------|---------------------------------------------|-----|------|------|

| IDDQ   | Supply Current, Quiescent    | V <sub>DD</sub> = Max., V <sub>IN</sub> = 0 |     | 15   | mA   |

| IDDU   | Supply Current, No Load      | VDD = Max., tCY = 50ns                      |     | 100  | mA   |

| IIL    | Input Current LOW            |                                             |     | -10  | μΑ   |

| lін    | Input Current, HIGH          |                                             |     | 10   | μΑ   |

| VoL    | Output Voltage, LOW          |                                             |     | 0.4  | V    |

| Voн    | Output Voltage, HIGH         |                                             | 2.0 |      | V    |

| los    | Short-Circuit Output Current |                                             |     | -100 | μΑ   |

| Cı     | Input Capacitance            |                                             |     | 10   | pF   |

| Co     | Output Capacitance           |                                             |     | 10   | pF   |

**Note:** Actual test conditions may vary from those shown, but guarantee operation as specified.

# **Switching Characteristics**

| Parameter |                | Test Conditions                               | Package   | Min | Max | Unit |

|-----------|----------------|-----------------------------------------------|-----------|-----|-----|------|

| tD        | Output Delay   | V <sub>DD</sub> = Min., C <sub>L</sub> = 25pF | TMC2255   |     | 22  | ns   |

|           |                |                                               | TMC2255-1 |     | 19  |      |

| tHO       | Output Hold    | V <sub>DD</sub> = Max., C <sub>L</sub> = 25pF |           |     | 6   | ns   |

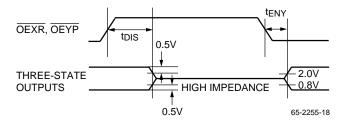

| tENA      | Output Enable  | V <sub>DD</sub> = Min., C <sub>L</sub> = 25pF | TMC2255   |     | 18  | ns   |

|           |                |                                               | TMC2255-1 |     | 15  |      |

| tDIS      | Output Disable | V <sub>DD</sub> = Min., C <sub>L</sub> = 25pF | TMC2255   |     | 21  | ns   |

|           |                |                                               | TMC2255-1 |     | 20  |      |

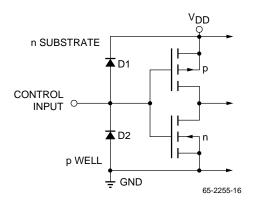

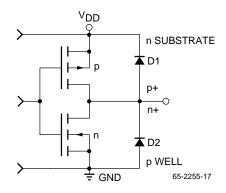

# **Equivalent Circuits and Transition Levels**

Figure 13. Equivalent Input Circuit

Figure 14. Equivalent Output Circuit

Figure 15. Transition Levels for Three-State Measurements

## **Related Products**

- TMC2011 Variable Length Shift Resistor

- TMC2302 Image Manipulation Sequencer

## **Notes:**

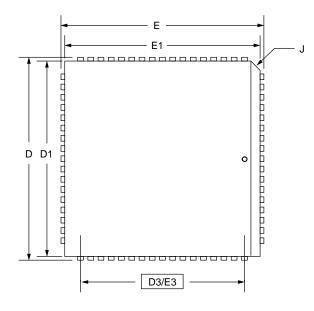

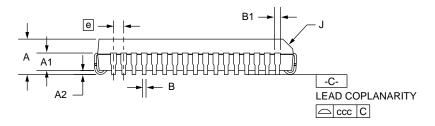

# **Mechanical Dimensions – 68-Lead PLCC Package**

| Symbol | Inches   |      | Millimeters |       | Notes |

|--------|----------|------|-------------|-------|-------|

|        | Min.     | Max. | Min.        | Max.  | Notes |

| Α      | .165     | .200 | 4.19        | 5.08  |       |

| A1     | .090     | .130 | 2.29        | 3.30  |       |

| A2     | .020     | _    | .51         | _     |       |

| В      | .013     | .021 | .33         | .53   |       |

| B1     | .026     | .032 | .66         | .81   |       |

| D/E    | .985     | .995 | 25.02       | 25.27 |       |

| D1/E1  | .950     | .958 | 24.13       | 24.33 | 3     |

| D3/E3  | .800 BSC |      | 20.32 BSC   |       |       |

| е      | .050 BSC |      | 1.27 BSC    |       |       |

| J      | .042     | .056 | 1.07        | 1.42  | 2     |

| ND/NE  | 17       |      | 17          |       |       |

| N      | 68       |      | 68          |       |       |

| CCC    | _        | .004 | _           | 0.10  |       |

#### Notes:

- 1. All dimensions and tolerances conform to ANSI Y14.5M-1982

- 2. Corner and edge chamfer (J) =  $45^{\circ}$

- 3. Dimension D1 and E1 do not include mold protrusion. Allowable protrusion is .101" (.25mm)

## **Ordering Information**

| Product Number | Data Rate (MHz) | Temperature Range | Screening  | Package     | Package Marking |

|----------------|-----------------|-------------------|------------|-------------|-----------------|

| TMC2255R1C     | 10              | 0°C to 70°C       | Commercial | 68 Pin PLCC | 2255R1C         |

| TMC2255R1C1    | 12.5            | 0°C to 70°C       | Commercial | 68 Pin PLCC | 2255R1C1        |

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com