September 1992

#### DESCRIPTION

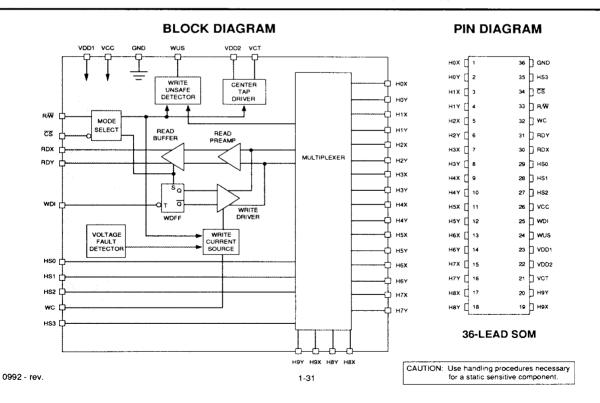

The SSI 32R5161R is a bipolar monolithic integrated circuit designed for use with a center-tapped ferrite or MIG recording heads. The SSI 32R5161R offers the performance upgrades of the SSI 32R511 along with improved head port characteristics and increased read gain. It provides a low noise read path, write current control, and data protection circuitry for as many as 10 channels. The SSI 32R5161R requires +5V and +12V power supplies and is available in a variety of packages.

### **FEATURES**

- High performance

- Read mode gain = 150 V/V

Input noise = 1.3 nV/√Hz maximum

Input capacitance = 18 pF

Write current range = 10 mA to 60 mA

- Enhanced system write to read recovery time

- Power supply fault protection

- Designed for center-tapped ferrite or MIG heads

- Programmable write current source

- Easily multiplexed for larger systems

- Includes write unsafe detection

- TTL compatible control signals

- +5V, +12V power supplies

#### CIRCUIT OPERATION

The SSI 32R5161R gives the user the ability to address up to 10 center-tapped ferrite heads and provide write drive or read amplification. Head selection and mode control is accomplished using the HSn, CS and R/W inputs as shown in tables 1 & 2. Internal pullups are provided for the  $\overline{CS}$  & R/ $\overline{W}$  inputs to force the device into a non-writing condition if either control line is opened accidentally.

TABLE 1: Mode Select

| टड | R/W | MODE  |

|----|-----|-------|

| 0  | 0   | Write |

| 0  | 1   | Read  |

| 1  | X   | ldle  |

**TABLE 2: Head Select**

| HS3 | HS2 | HS1 | HS0 | HEAD |

|-----|-----|-----|-----|------|

| 0   | 0   | 0   | 0   | 0    |

| 0   | 0   | 0   | 11  | 1    |

| 0   | 0   | 1   | 0   | 2    |

| 0   | 0   | 1   | 1   | 3    |

| 0   | 1   | 0   | 0   | 4    |

| 0   | 1   | 0   | 1   | 5    |

| 0   | 1   | 1   | 0   | 6    |

| 0   | 1   | 1   | 1   | 7    |

| 1   | 0   | 0   | 0   | 8    |

| 1   | 0   | 0   | 1   | 9    |

0 = Low level 1 = High level

#### WRITE MODE

Taking both  $\overline{CS}$  and R/W low selects write mode which configures the SSI 32R5161R as a current switch and activates the Write Unsafe (WUS) detector circuitry. Write current is toggled between the X and Y side of the selected head on each high to low transition of the Write Data Input (WDI). Note that a preceding read mode selection initializes the Write Data Flip-Flop. WDFF, to pass write current through the "X" side of the head. The zero-peak write current magnitude is programmed by an external resistor Rwc from pin WC to GND and is given by:

Iw = K/Rwc, where K = Write Current Constant

The Write Unsafe detection circuitry monitors voltage transitions at the selected head connections and flags any of the following conditions as a high level on the Write Unsafe open collector output:

- · Head open

- · Head center tap open

- · WDI frequency too low · Device in read mode

- Device not selected

- · No write current

Two negative transitions on WDI, after the fault is corrected, will clear the WUS flag.

To further assure data security a voltage fault detection circuit prevents application of write current during power loss or power sequencing.

To enhance write to read recovery time the change in RDX, RDY common mode voltage is minimized by biasing these outputs to a level within the read mode range when in write mode.

Power dissipation in write mode may be reduced by placing a resistor (RCT) between VDD1 & VDD2. The optimum resistor value is  $82\Omega \times 60$ /lw (lw in mA). At low write currents (<15 mA) read mode dissipation is higher than write mode and RCT, though recommended, may not be considered necessary. In this case VDD2 is connected directly to VDD1.

#### **READ MODE**

Taking CS low and R/W high selects read mode which configures the SSI 32R5161R as a low noise differential amplifier for the selected head. The RDX and RDY outputs are driven by emitter followers and are in phase with the "X" and "Y" head ports. These outputs should be AC coupled to the load. The internal write current source is gated off in read mode eliminating the need for any external gating.

Read mode selection also initializes the Write Data Flip-Flop (WDFF) to pass write current through the "X" side of the head at a subsequent write mode selection.

#### **IDLE MODE**

Taking CS high selects the idle mode which switches the RDX, RDY outputs into a high impedance state and deactivates the internal write current source. This facilitates multi-device installations by allowing the read outputs to be wire OR'ed and the write current programming resistor to be common to all devices.

### PIN DESCRIPTION

| NAME               | I/O | DESCRIPTION                                                          |

|--------------------|-----|----------------------------------------------------------------------|

| HS0-HS2            | 1   | Head Select                                                          |

| <u>cs</u>          | ı   | Chip Select: a low level enables device                              |

| R/W                | l   | Read/Write: a high level selects read mode                           |

| wus                | O*  | Write Unsafe: a high level indicates an unsafe writing condition     |

| WDI                | I   | Write Data In: negative transition toggles direction of head current |

| H0X-H7X<br>H0Y-H7Y | 1/0 | X,Y head connections                                                 |

| RDX, RDY           | O*  | X, Y Read Data: differential read signal out                         |

| wc                 | *   | Write Current: used to set the magnitude of the write current        |

| VCT                | -   | Voltage Center Tap: voltage source for head center tap               |

| vcc                | -   | +5V                                                                  |

| VDD1               | -   | +12V                                                                 |

| VDD2               | -   | Positive power supply for the center tap voltage source              |

| GND                | -   | Ground                                                               |

<sup>\*</sup>When more than one R/W device is used, these signals can be wire OR'ed.

### **ELECTRICAL SPECIFICATIONS**

ABSOLUTE MAXIMUM RATINGS (All voltages referenced to GND. Currents into device are positive.)

| PARAMETER                                        |      | VALUE              | UNITS |

|--------------------------------------------------|------|--------------------|-------|

| DC Supply Voltage                                | VDD1 | -0.3 to +14        | VDC   |

| DC Supply Voltage                                | VDD2 | -0.3 to +14        | VDC   |

| DC Supply Voltage                                | VCC  | -0.3 to +6         | VDC   |

| Digital Input Voltage Range                      | VIN  | -0.3 to VCC + 0.3  | VDC   |

| Head Port Voltage Range                          | VH   | -0.3 to VDD1 + 0.3 | VDC   |

| WUS Pin Voltage Range                            | Vwus | -0.3 to +14        | VDC   |

| Write Current Zero Peak                          | IW   | 90                 | mA    |

| RDX, RDy Output Current                          | lo   | -10                | mA    |

| VCT Output Current                               | lvct | -90                | mA    |

| WUS Output Current                               | lwus | +12                | mA    |

| Storage Temperature Range                        | Tstg | -65 to 150         | °C    |

| Lead Temperature PDIP, Flat P (10 sec Soldering) | ack  | 260                | °C    |

| Package Temperature PLCC, S (20 sec Reflow)      | 80   | 215                | °C    |

### **RECOMMENDED OPERATION CONDITIONS**

| PARAMETER                  |      | CONDITIONS | MIN  | МОМ  | MAX  | UNITS |

|----------------------------|------|------------|------|------|------|-------|

| DC Supply Voltage          | VDD1 |            | 10.8 | 12.0 | 13.2 | VDC   |

| DC Supply Voltage          | VCC  |            | 4.5  | 5.0  | 5.5  | VDC   |

| Head Inductance            | Lh   |            | 5    |      | 10   | μН    |

| RCT Resistor               | RCT* | lw = 60 mA |      | 82   |      | Ω     |

| Write Current              | IW   |            | 10   |      | 60   | mA    |

| Junction Temperature Range | Tj   |            | +25  |      | +135 | °C    |

<sup>\*</sup>For Iw = 60 mA. At other Iw levels refer to Applications Information that follows this specification.

### **DC CHARACTERISTICS**

(Unless otherwise specified, recommended operating conditions apply.)

### **POWER SUPPLY**

| PARAMETER                       | CONDITIONS                                | MIN | NOM | MAX     | UNITS |

|---------------------------------|-------------------------------------------|-----|-----|---------|-------|

| VCC Supply Current              | Read/Idle Mode                            |     |     | 30      | mA    |

|                                 | Write Mode                                |     |     | 30      | mA    |

| VDD Supply Current              | Idle Mode                                 |     |     | 20      | mA    |

| (sum of VDD1 and VDD2)          | Read Mode                                 |     |     | 40      | mA    |

|                                 | Write Mode                                |     |     | 20 + tw | mA    |

| Power Dissipation (Tj = +125°C) | Idle Mode                                 |     |     | 400     | mW    |

|                                 | Read Mode                                 |     |     | 620     | mW    |

|                                 | Write Mode, IW = 45 mA, RCT = $0\Omega$   |     |     | 800     | mW    |

|                                 | Write Mode, IW = 45 mA, RCT = $110\Omega$ |     |     | 610     | mW    |

|                                 | Write Mode, IW = 60 mA RCT = $82\Omega$   |     |     | 680     | mW    |

## **DC CHARACTERISTICS** (continued)

### DIGITAL I/O

| PARA | METER                   | CONDITIONS | MIN  | МОМ | MAX          | UNITS |

|------|-------------------------|------------|------|-----|--------------|-------|

| VIL  | Input Low Voltage       |            |      |     | 0.8          | VDC   |

| VIH  | Input High Voltage      |            | 2.0  |     | VCC<br>+ 0.3 | VDC   |

| IIL  | Input Low Current       | VIL = 0.8V | -0.4 |     |              | mA    |

| IIH  | Input High Current      | VIH = 2.0V |      |     | 100          | μА    |

| VOL  | WUS Output Low Voltage  | IOL = 8 mA |      |     | 0.5          | VDC   |

| IOH  | WUS Output High Current | VOH = 5.0V |      |     | 100          | μА    |

### **WRITE MODE**

| Center Tap Voltage VCT              | Write Mode                                        |       | 6.9  |      | VDC   |

|-------------------------------------|---------------------------------------------------|-------|------|------|-------|

| Head Current (per side)             | Write Mode,<br>0 ≤ VCC ≤ 3.7V,<br>0 ≤ VDD1 ≤ 8.7V | -200  |      | 200  | μА    |

| Write Current Range                 |                                                   | 10    |      | 60   | mA    |

| Write Current Constant "K"          | IW = 10 -60 mA                                    | 2.375 |      | 2.80 | V     |

| lwc to Head Current Gain            |                                                   |       | 0.99 |      | mA/mA |

| Unselected Head Leakage Current     |                                                   |       |      | 85   | μА    |

| RDX, RDY Output Offset Voltage      | Write/Idle Mode                                   | -20   |      | +20  | mV    |

| RDX, RDY Common Mode Output Voltage | Write/Idle Mode                                   |       | 5.5  |      | VDC   |

| RDX, RDY Leakage                    | RDX, RDY = 6V<br>Write/Idle Mode                  | -100  |      | 100  | μА    |

### **READ MODE**

| Center Tap Voltage            | Read Mode                                               |      | 4.2 |     | VDC |

|-------------------------------|---------------------------------------------------------|------|-----|-----|-----|

| Head Current (per side)       | Read or Idle Mode<br>0 ≤ VCC ≤ 5.5V<br>0 ≤ VDD1 ≤ 13.2V | -200 |     | 200 | μА  |

| Input Bias Current (per side) |                                                         |      |     | 45  | μΑ  |

| Input Offset Voltage          | Read Mode                                               | -4   |     | +4  | mV  |

| Common Mode Output Voltage    | Read Mode                                               | 4.5  | 5.5 | 6.5 | VDC |

### **DYNAMIC CHARACTERISTICS AND TIMING**

(Unless otherwise specified, recommended operating conditions apply and IW = 35 mA, Lh = 5  $\mu$ H, f(WDI) = 5 MHz, CL(RDX, RDY)  $\leq$  35 pF.)

### WRITE MODE

| PARAMETER                         | CONDITIONS | MIN | МОМ | MAX | UNITS  |

|-----------------------------------|------------|-----|-----|-----|--------|

| Differential Head Voltage Swing   |            | 7.0 |     |     | V(pk)  |

| Unselected Head Transient Current |            | ·   |     | 2   | mA(pk) |

| Differential Output Capacitance   |            |     |     | 15  | pF     |

| Differential Output Resistance    |            | 430 | 650 | 870 | Ω      |

| WDI Transition Frequency          | WUS = low  | 125 |     |     | kHz    |

#### **READ MODE**

| Differential Voltage Gain      | Vin = 1 mVpp @ 300 kHz,<br>RL(RDX), RL(RDY)<br>= 1 K $\Omega$                      | 120  | 150 | 180 | V/V    |

|--------------------------------|------------------------------------------------------------------------------------|------|-----|-----|--------|

| Dynamic Range                  | AC Input Voltage, Vi,<br>Where Gain Falls<br>by 10%. V + f = 300 KHz               | -3   |     |     | m∨pp   |

| Bandwidth (-3dB)               | $ Zs  < 5\Omega$ , Vin = 1 mVpp                                                    | 30   |     |     | MHz    |

| Input Noise Voltage            | BW = 15 MHz,<br>Lh = 0, Rh = 0                                                     |      | 1.0 | 1.3 | nV/√Hz |

| Differential Input Capacitance | f = 5 MHz                                                                          |      | 14  | 18  | pF     |

| Differential Input Resistance  | 32R5161R, f = 5 MHz                                                                | 350  |     | 800 | Ω      |

| Common Mode Rejection Ratio    | Vcm = VCT + 100 mVpp<br>@ 5 MHz                                                    | 50   |     |     | dB     |

| Power Supply Rejection Ratio   | 100 mVpp @ 5 MHz on<br>VDD1, VDD2 or VCC                                           | 45   |     |     | dB     |

| Channel Separation             | Unselected Channels:<br>Vin=100 mVpp @ 5 MHz;<br>Selected Channel:<br>Vin = 0 mVpp | 45   |     |     | dB     |

| Single Ended Output Resistance | f = 5 MHz                                                                          |      |     | 30  | Ω      |

| Output Current                 | AC Coupled Load,<br>RDX to RDY                                                     | ±2.1 |     |     | mA     |

### **DYNAMIC CHARACTERISTICS AND TIMING (continued)**

### **SWITCHING CHARACTERISTICS**

| PARAMETER                                     | CONDITIONS                                                                                       | MIN | МОМ | MAX | UNITS |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| R/₩ To Write                                  | Delay to 90% of<br>Write Current                                                                 |     | .15 | .7  | μs    |

| R/₩ to Read                                   | Delay to 90% of<br>100 mV, 10 MHz Read<br>Signal Envelope or<br>to 90% decay of<br>Write Current |     | .25 | .7  | μs    |

| CS to Select                                  | Delay to 90% of Write<br>Current or to 90% of<br>100 mV, 10 MHz Read<br>Signal Envelope          |     | .2  | 1.0 | μѕ    |

| CS to Unselect                                | Delay to 90% Decay of Write Current                                                              |     | .1  | 1.0 | μS    |

| HS0 - HS2 to any head                         | Delay to 90% of 100 mV,<br>10 MHz Read Signal<br>Envelope                                        |     | .25 | 1.0 | μѕ    |

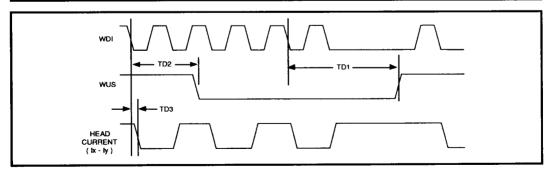

| WUS, Safe to Unsafe - TD1                     | lw = 35 mA                                                                                       | 1.6 |     | 8.0 | μs    |

| WUS, Unsafe to Safe - TD2                     | lw = 35 mA                                                                                       |     |     | 1.0 | μs    |

| Head Current (Lh = 0 $\mu$ H, Rh = 0 $\Omega$ | 2)                                                                                               |     |     |     |       |

| Prop. Delay - TD3                             | From 50% Points                                                                                  |     |     | 25  | ns    |

| Asymmetry                                     | WDI has 50% Duty Cycle and 1ns Rise/Fall Time                                                    |     |     | 1   | ns    |

| Rise/Fall Time                                | 10% - 90% Points                                                                                 |     |     | 20  | ns    |

FIGURE 1: Write Mode Timing Diagram

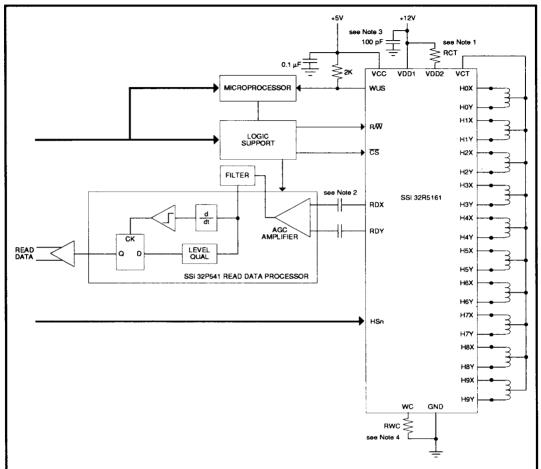

### **NOTES**

- An external resistor, RCT, given by; RCT = 82 (60/lw) where lw is the zero-peak write current in mA, can be used to limit internal power dissipation. Otherwise connect VDD2 to VDD1.

- Limit DC current from RDX and RDY to 100 μA and load capacitance to 20 pF. In multi-chip application these outputs can be wire-OR'ed.

- 3. The power bypassing capacitor must be located close to the 32R5161R with its ground returned directly to device ground, with as short a path as possible.

- 4. To reduce ringing due to stray capacitance this resistor should be located close to the 32R5161R. Where this is not desirable a series resistor can be used to buffer a long WC line. In multi-chip applications a single resistor common to all chips may be used.

FIGURE 2: Applications Information

### **PACKAGE PIN DESIGNATIONS**

(Top View)

36-lead

| нох [ | 1  | 36 | GND   |

|-------|----|----|-------|

| ноч [ | 2  | 35 | ] нѕз |

| н1х [ | 3  | 34 | ] cs  |

| н1Ү [ | 4  | 33 | ] ₽∕₩ |

| н2х [ | 5  | 32 | wc    |

| H2Y [ | 6  | 31 | RDY   |

| нзх [ | 7  | 30 | RDX   |

| нэү [ | 8  | 29 | ] HSO |

| H4X [ | 9  | 28 | ] нѕ1 |

| H4Y [ | 10 | 27 | ] HS2 |

| н5х [ | 11 | 26 | vcc   |

| H5Y [ | 12 | 25 | wo.   |

| нех [ | 13 | 24 | wus   |

| Н6Ү [ | 14 | 23 | VDD1  |

| H7X [ | 15 | 22 | NDD2  |

| H7Y [ | 16 | 21 | VCT   |

| нвх [ | 17 | 50 | нэү   |

| нву [ | 18 | 19 | ] нэх |

THERMAL CHARACTERISTICS: θja

SOM

50°C/W

36-Lead SOM

### **ORDERING INFORMATION**

| PART DESCRIPTION               | ORDERING NO.  | PKG. MARK     |

|--------------------------------|---------------|---------------|

| SSI 32R5161R Read/Write Device |               |               |

| 10-Channel SOM                 | 32R5161R-10CM | 32R5161R-10CM |

No responsibility is assumed by Silicon Systems for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Silicon Systems. Silicon Systems reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680 (714) 573-6000, FAX (714) 573-6914