## CL-MD1414UXX

Data Book

### **FEATURES**

#### ■ International telephony support

- Call progress and black listing

- CCITT V.23 and V.21 data modes

#### ■ Flash memory interface

- Firmware-upgradeable microcontroller

- Programmable manufacturer-specific parameters

- Caller ID and distinctive ringing

- Telephone-Emulation mode (speakerphone)

- Three DTE (data terminal) interfaces available

- PC card (PCMCIA) bus interface

- Direct connection to a PC card bus

- 16C550A/16C450 register-compatible UART

- Manufacturer-programmable internal CIS

- DMA for Voice playback and record modes

- Parallel bus interface

- Direct connection to PC ISA bus

- Direct connection to PC ISA bus plug-and-play interface with pin-compatibility

- 16C550A/16C450 register-compatible UART

- Built-in COM 1–4 address decoding and bus drivers

- DMA for Voice playback and record modes

- Serial RS-232 (V.24)

#### Voice mode

- Embedded voice mode AT command set

- Sample Rates: 4800, 7200, 8000, 9600, 11025, and 22050 bps

- Compression: ADPCM, Linear, and CL1

- Radish<sup>®</sup> VoiceView<sup>™</sup>

Universal 14,400-bps

Data/Fax/Voice

Modem Device Set Family

(Two-Chip Set)

#### **OVERVIEW**

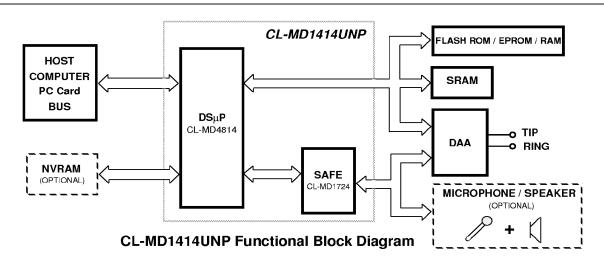

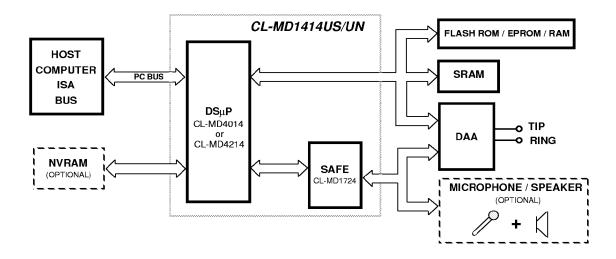

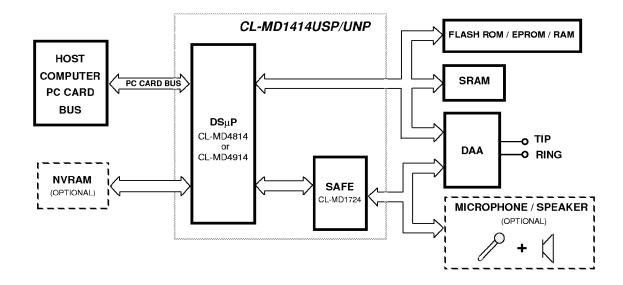

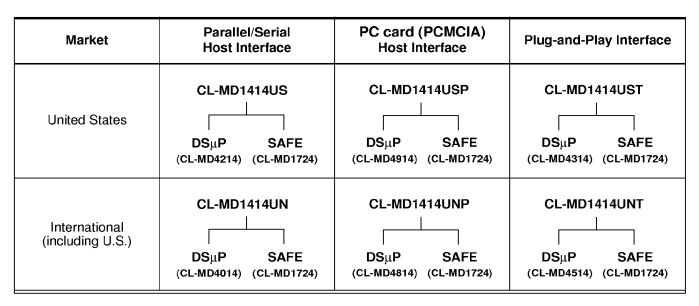

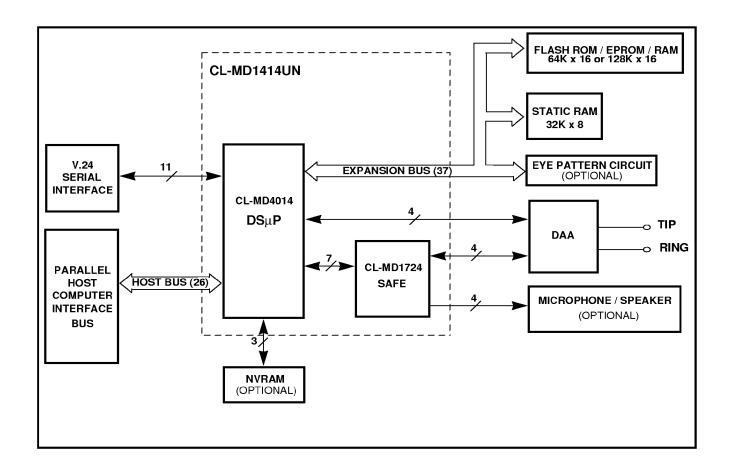

The CL-MD1414UXX, the Cirrus Logic Universal, is a complete, intelligent, multi-mode modem combining data, fax, and voice features in only two devices, a DS $\mu$ P (Digital Signal Microprocessor) and a SAFE (Sigma-Delta Analog Front End).

The CL-MD1414UXX operates up to 14,400 bps as a data and fax (transmit and receive) modem, and is intended for stand-alone, ISA bus card, and PC card (PCMCIA) applications. No additional firmware development is required for this complete solution.

The Universal provides the standard data, EIA/TIA-578 Class 1 and EIA/TIA-592 Class 2 fax AT commands. In addition, the Universal includes a voice and V.42/MNP® 2–4 error correction and V.42 bis/MNP 5 data compression command set to ensure fast error-free data transfer during data modem connections. The Universal implements a voice mode AT command set, that enables a host computer and the CL-MD1414UXX to emulate a telephone answering machine and telephone.

(cont. next page)

(cont. next page)

Version 1.2 November 1995

### FEATURES (cont.)

#### ■ Data modem modes

- CCITT: V.32 bis, V.32, V.23, V.22 bis, V.22, and V.21

- Bell<sup>®</sup>: 212A and 103

- Speeds: 14400, 12000, 9600, 7200, 4800, 2400, 1200, and 300 bps

- Industry-standard AT command set

#### ■ Fax Modem Send and Receive modes

- CCITT: V.17, V.29, V.27 ter, and V.21 ch2

- Speeds: 14400, 12000, 9600, 7200, 4800, 2400, and 300 bps

- Supports Group 3 fax

- EIA/TIA-578 Class 1 Fax AT command set

- EIA/TIA-592 Class 2 Fax AT command set

#### ■ V.42/MNP® protocols

- Error correction: V.42 and MNP® 2–4

- Data compression: V.42 bis and MNP® 5

#### ■ Microphone interface

#### ■ Low power requirement

- Automatic sleep (power-down) and wake-up

- Operates from a single +5-V power supply

- Typical power requirements for CL-MD1414US/UN:

- Operating power: 450 mW

- Sleep mode: 40 mW

- Stop mode: 50 μW

- Typical power requirements for CL-MD1414USP/UNP:

- Operating power: 450 mW

- Sleep mode: 40 mW

#### ■ Small package dimensions

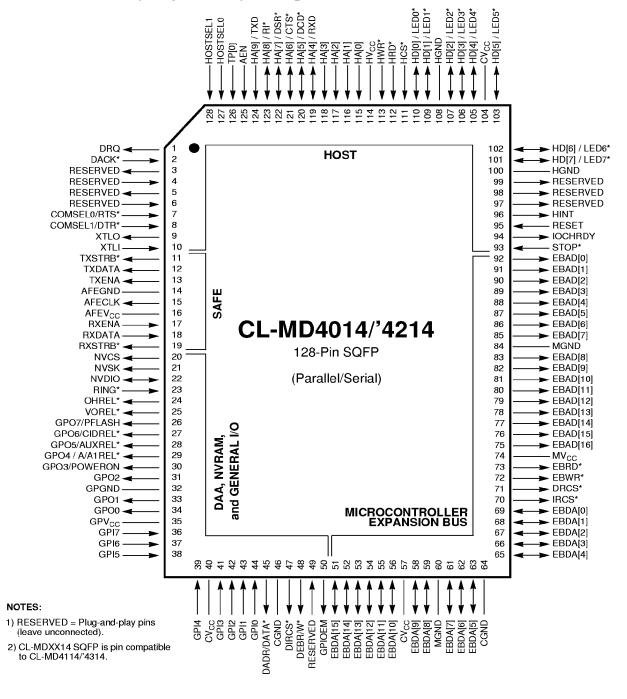

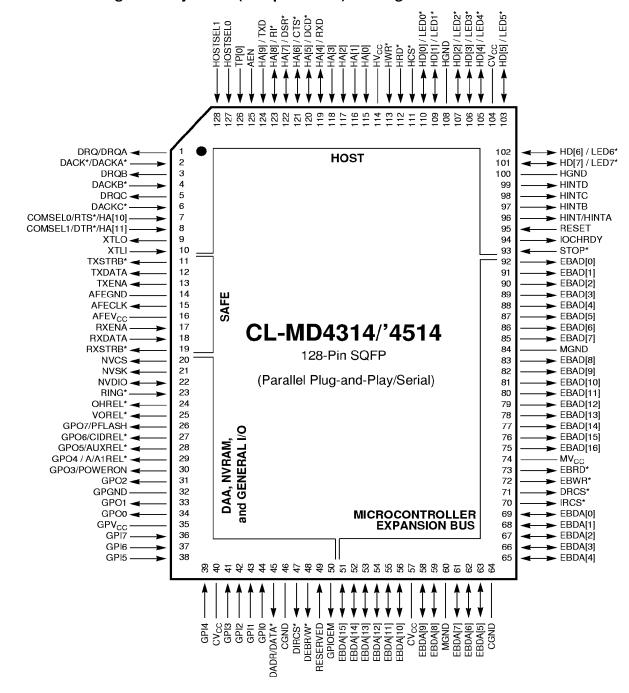

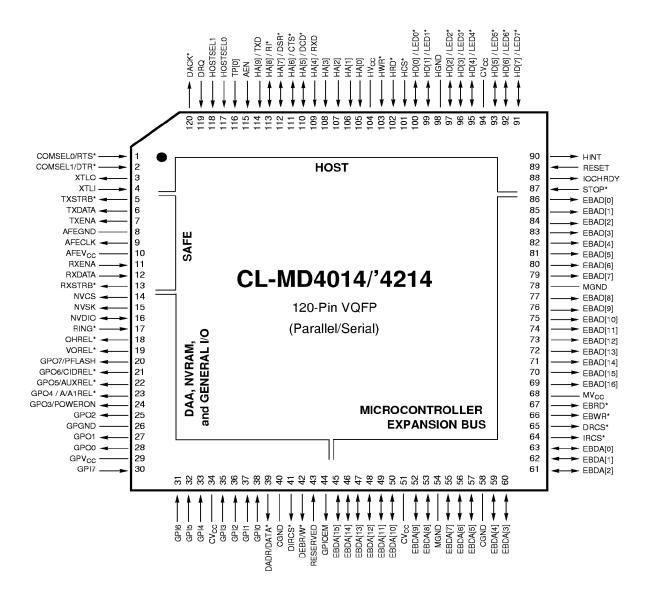

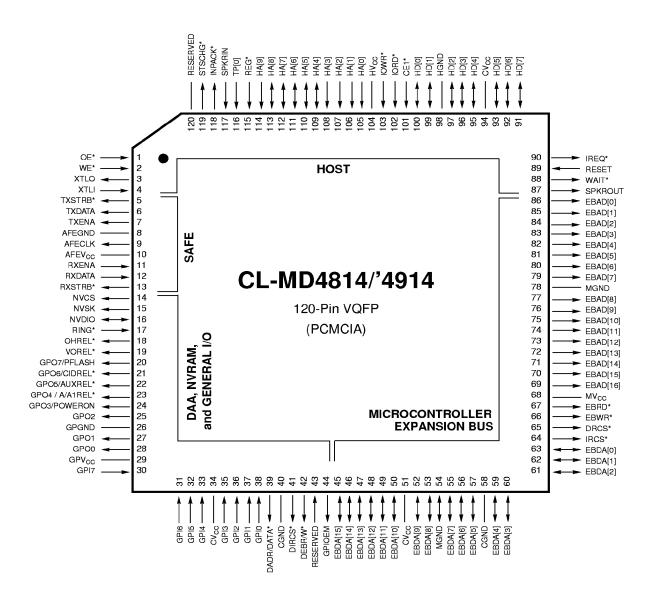

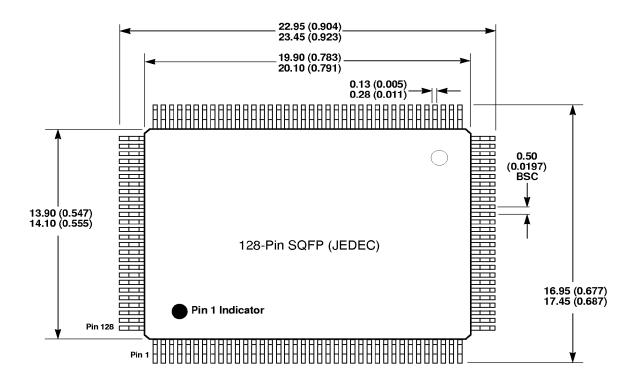

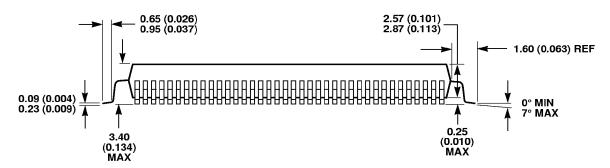

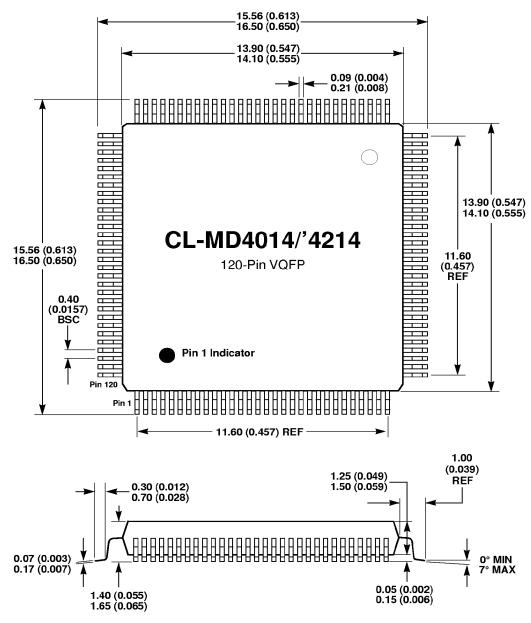

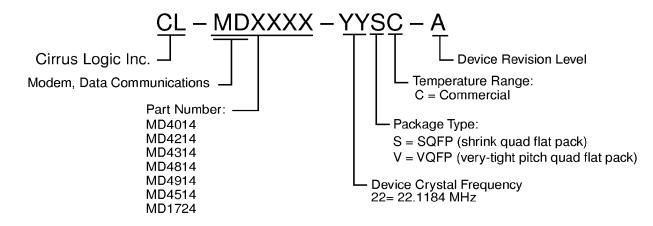

- DSμP (CL-MDXX14): 128-pin SQFP or 120-pin VQFP

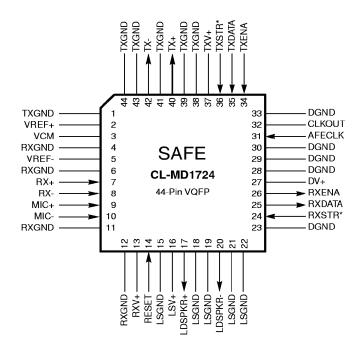

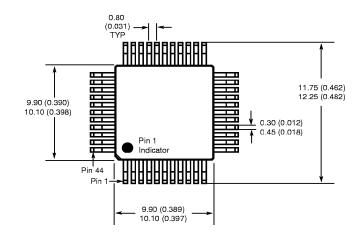

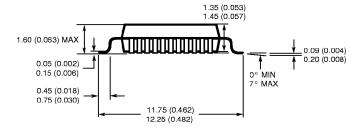

- SAFE (CL-MD1724): 44-pin VQFP

## **OVERVIEW** (cont.)

New voice features in the Universal include higher sampling rates (4800, 7200, 8000, 9600, 11025, and 22050 samples/sec.), speakerphone, and Radish<sup>®</sup> VoiceView™.

The Universal also offers an extended data, EIA/TIA-578 Class 1 and EIA/TIA-592 Class 2 fax, and voice AT command set interpreter, which is embedded in the device sets. This allows system designers to develop a Hayes<sup>®</sup> compatible modem with minimal effort.

The CL-MD1414UXX offers several hardware interfaces. The Universal can host interface in serial RS232, parallel bus, plug-and-play, and PC card modes. Additionally, the CL-MD1414UXX supports expansion bus, NVRAM, DAA, speaker, microphone, and flash memory interfaces.

The flash memory interface is a new feature to the Cirrus Logic modem devices. It allows end-users and modem designers to download new firmware easily and quickly. It works by downloading the new firmware through the UART interface to a flash ROM or RAM.

#### **APPLICATIONS**

- Notebook computers

- PDA applications

- ISA bus modems

- Box modems

- Pocket modems

- PC cards

#### **ADVANTAGES**

#### **Unique Features**

- Downloadable flash memory interface

- .wave-compatible sample rates and compression (with DTMF detection)

- Direct connection to PC ISA bus or PC card bus

- 14400-bps fax transmission and reception

- 16C550A register-compatible UART

- Small package sizes

- Power-management modes

- Requires a single +5-V power supply

#### **Benefits**

Allows end-users to download firmware upgrades

Allows playing or recording of .wave files without a file translation program

Eliminates the need for bus drivers, address decoding logic, PC card interface chip, and CIS ROM

Latest fax standard reduces telephone connect time

Supports enhanced communication software for improved data throughput

Minimizes board area

Reduces power consumption over 92 percent

Simplifies board design

November 1995

2 FEATURES/OVERVIEW

DATA BOOK

## **Table of Contents**

| 1. | FU                                                                             | NCTIONAL BLOCK DIAGRAMS                                                                                                                                                                                                                                                              | 5                                |

|----|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2. | DE                                                                             | VICE SET DESCRIPTION                                                                                                                                                                                                                                                                 | 6                                |

|    | 2.1                                                                            | DSμP (Digital Signal Microprocessor)                                                                                                                                                                                                                                                 | 6                                |

|    | 2.2                                                                            | SAFE (Sigma-Delta Analog Front End) Device                                                                                                                                                                                                                                           |                                  |

| 3. | MC                                                                             | DDES OF OPERATION                                                                                                                                                                                                                                                                    | 7                                |

|    | 3.1                                                                            | Data Mode                                                                                                                                                                                                                                                                            | 7                                |

|    | 3.2                                                                            | Fax Mode                                                                                                                                                                                                                                                                             |                                  |

|    | 3.3                                                                            | Voice Mode                                                                                                                                                                                                                                                                           |                                  |

|    | 3.4                                                                            | V.42/MNP, 2-4 and V.42 bis/MNP, 5 Modes                                                                                                                                                                                                                                              | 7                                |

|    | 3.5                                                                            | Radish, VoiceView™ Mode                                                                                                                                                                                                                                                              | 7                                |

|    | 3.6                                                                            | Power Management Modes                                                                                                                                                                                                                                                               |                                  |

|    | 3.7                                                                            | Loopback Test Modes                                                                                                                                                                                                                                                                  |                                  |

|    | 3.8                                                                            | Transmit Levels                                                                                                                                                                                                                                                                      |                                  |

|    | 3.9                                                                            | Transmit Tone Levels                                                                                                                                                                                                                                                                 |                                  |

|    | 3.10                                                                           | Receive Level                                                                                                                                                                                                                                                                        |                                  |

|    |                                                                                | 3.10.1 Receiver Tracking                                                                                                                                                                                                                                                             |                                  |

|    |                                                                                | 3.10.2 Equalizers                                                                                                                                                                                                                                                                    |                                  |

|    |                                                                                | 3.10.4 Caller ID                                                                                                                                                                                                                                                                     |                                  |

|    |                                                                                | 3.10.5 International Support                                                                                                                                                                                                                                                         |                                  |

| _  |                                                                                | •                                                                                                                                                                                                                                                                                    |                                  |

| 4. |                                                                                | RDWARE INTERFACES                                                                                                                                                                                                                                                                    |                                  |

|    | 4.1                                                                            | Host Interfaces                                                                                                                                                                                                                                                                      |                                  |

|    |                                                                                | 4.1.1 Serial RS-232 Interface                                                                                                                                                                                                                                                        |                                  |

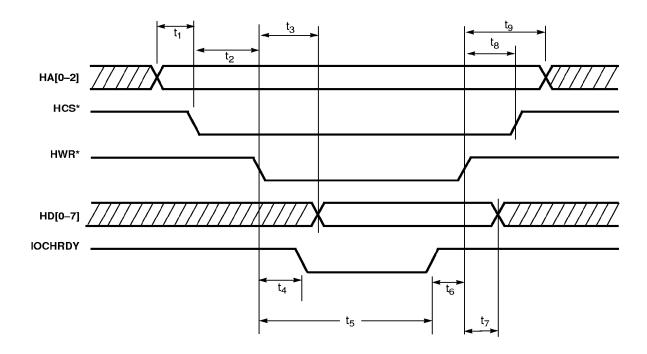

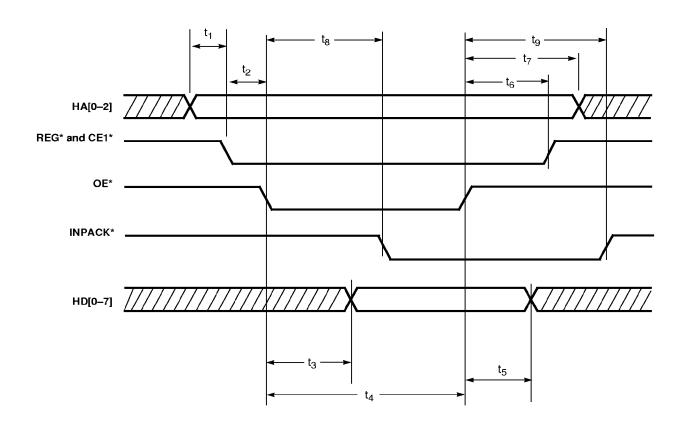

|    |                                                                                | 4.1.2 Parallel Bus Interface                                                                                                                                                                                                                                                         |                                  |

|    |                                                                                | 4.1.4 PC Card Interface                                                                                                                                                                                                                                                              |                                  |

|    |                                                                                |                                                                                                                                                                                                                                                                                      | 10                               |

|    | 12                                                                             |                                                                                                                                                                                                                                                                                      |                                  |

|    | 4.2<br>4.3                                                                     | Flash Interface                                                                                                                                                                                                                                                                      | 12                               |

|    | 4.3                                                                            | Flash Interface                                                                                                                                                                                                                                                                      | 12<br>12                         |

|    | 4.3<br>4.4                                                                     | Flash Interface                                                                                                                                                                                                                                                                      | 12<br>12<br>12                   |

|    | 4.3                                                                            | Flash Interface                                                                                                                                                                                                                                                                      | 12<br>12<br>12<br>13             |

|    | 4.3<br>4.4<br>4.5                                                              | Flash Interface                                                                                                                                                                                                                                                                      | 12<br>12<br>12<br>13             |

|    | 4.3<br>4.4<br>4.5<br>4.6                                                       | Flash Interface                                                                                                                                                                                                                                                                      | 12<br>12<br>13<br>13<br>13       |

| 5. | 4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                                         | Flash Interface The Expansion Bus Interface  NVRAM Interface  DAA Interface  Speaker Interface  Microphone Interface  General-Purpose I/O Interface                                                                                                                                  | 12<br>12<br>13<br>13<br>13       |

| 5. | 4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                                         | Flash Interface The Expansion Bus Interface  NVRAM Interface  DAA Interface  Speaker Interface  Microphone Interface  General-Purpose I/O Interface  COMMAND SET                                                                                                                     | 12<br>12<br>13<br>13<br>13       |

| 5. | 4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br><b>AT</b><br>5.1                     | Flash Interface The Expansion Bus Interface  NVRAM Interface  DAA Interface  Speaker Interface  Microphone Interface  General-Purpose I/O Interface  COMMAND SET                                                                                                                     | 12 12 13 13 13 15                |

|    | 4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br><b>AT</b><br>5.1<br>5.2              | Flash Interface The Expansion Bus Interface NVRAM Interface DAA Interface Speaker Interface Microphone Interface General-Purpose I/O Interface  COMMAND SET AT Command Description AT Escape Sequence                                                                                | 12 12 13 13 13 15 15             |

|    | 4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br><b>AT</b><br>5.1<br>5.2              | Flash Interface The Expansion Bus Interface NVRAM Interface DAA Interface Speaker Interface Microphone Interface General-Purpose I/O Interface  AT Command Description AT Escape Sequence  RDWARE SIGNALS                                                                            | 12 12 13 13 13 15 15             |

|    | 4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br><b>AT</b><br>5.1<br>5.2<br><b>HA</b> | Flash Interface The Expansion Bus Interface NVRAM Interface DAA Interface Speaker Interface Microphone Interface General-Purpose I/O Interface  COMMAND SET  AT Command Description AT Escape Sequence  RDWARE SIGNALS  DSµP Pin Diagram                                             | 12 12 13 13 13 15 15 22          |

|    | 4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br><b>AT</b><br>5.1<br>5.2<br><b>HA</b> | Flash Interface The Expansion Bus Interface NVRAM Interface DAA Interface Speaker Interface Microphone Interface General-Purpose I/O Interface  COMMAND SET AT Command Description AT Escape Sequence  RDWARE SIGNALS  DSµP Pin Diagram 6.1.1 Parallel/Serial (128-pin SQFP) Package | 12 12 13 13 13 15 15 15 22 22    |

|    | 4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br><b>AT</b><br>5.1<br>5.2<br><b>HA</b> | Flash Interface The Expansion Bus Interface NVRAM Interface DAA Interface Speaker Interface Microphone Interface General-Purpose I/O Interface  COMMAND SET AT Command Description AT Escape Sequence  RDWARE SIGNALS  DSµP Pin Diagram 6.1.1 Parallel/Serial (128-pin SQFP) Package | 12 12 12 13 13 15 15 15 22 22 23 |

November 1995

DATA BOOK v1.2

Table of Contents

|    | 6.3                                                                             | SAFE                                                                                   | Pin Diagram — 44-pin VQFP Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                                                         |

|----|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

|    | 6.4                                                                             | DSμP                                                                                   | Pin Descriptions (CL-MDXX14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                                         |

|    |                                                                                 |                                                                                        | $DS\mu P$ Parallel/Serial (RS-232) Host Interface Pin Descriptions (CL-MDXX127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14)                                                        |

|    |                                                                                 | 6.4.2                                                                                  | DSµP PC Card (PCMCIA) Host Interface Pin Descriptions (CL-MD4814/'4914)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33                                                         |

|    |                                                                                 | 6.4.3                                                                                  | DSµP NVRAM, DAA and General-Purpose I/O Interface Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35                                                         |

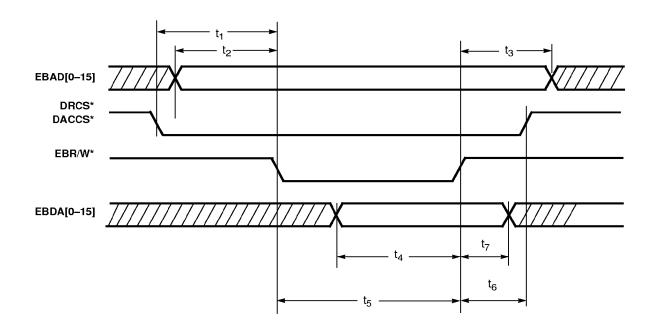

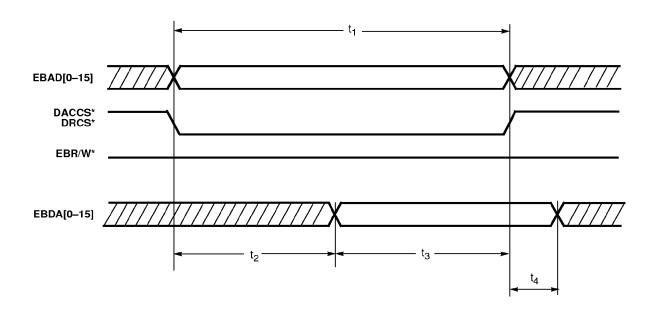

|    |                                                                                 | 6.4.4                                                                                  | DSµP Microcontroller Expansion Bus Interface Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                                                         |

|    |                                                                                 | 6.4.5                                                                                  | DSμP-SAFE Interface Pin Descriptions (128-pin SQFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39                                                         |

|    |                                                                                 | 6.4.6                                                                                  | DSµP CORE Power Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                                         |

|    | 6.5                                                                             |                                                                                        | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                            |

|    |                                                                                 |                                                                                        | SAFE General Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                            |

|    |                                                                                 |                                                                                        | SAFE Power Supply Pin Descriptions (CL-MD1724)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |

|    |                                                                                 |                                                                                        | SAFE—DSµP Interface Pin Descriptions (CL-MD1724)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                            |

|    |                                                                                 | 6.5.4                                                                                  | SAFE DAA Interface Pin Descriptions (CL-MD1724)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42                                                         |

|    |                                                                                 |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                            |

| 7. | ELE                                                                             | ECTRI                                                                                  | CAL SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43                                                         |

| 7. | <b>ELE</b> 7.1                                                                  |                                                                                        | CAL SPECIFICATIONSte Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                            |

| 7. |                                                                                 | Absolu                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43                                                         |

| 7. | 7.1                                                                             | Absolu<br>Recom                                                                        | te Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43<br>43                                                   |

| 7. | 7.1<br>7.2                                                                      | Absolu<br>Recom<br>DC Ele                                                              | te Maximum Ratingsmended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43<br>43<br>43                                             |

| 7. | 7.1<br>7.2<br>7.3                                                               | Absolu<br>Recom<br>DC Ele<br>AC/DC                                                     | te Maximum Ratings<br>mended Operating Conditions<br>ctrical Characteristics — DSµP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43<br>43<br>43<br>44                                       |

|    | 7.1<br>7.2<br>7.3<br>7.4<br>7.5                                                 | Absolu<br>Recom<br>DC Ele<br>AC/DC<br>Index o                                          | te Maximum Ratings Imended Operating Conditions Extrical Characteristics — DSµP Electrical Characteristics — CL-MD1724 (SAFE)  If Timing Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43<br>43<br>43<br>44<br>44                                 |

|    | 7.1<br>7.2<br>7.3<br>7.4<br>7.5                                                 | Absolu<br>Recom<br>DC Ele<br>AC/DC<br>Index o                                          | te Maximum Ratings Imended Operating Conditions Interctrical Characteristics — DSµP Electrical Characteristics — CL-MD1724 (SAFE) Interctrical Information  PACKAGE INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43<br>43<br>44<br>44<br><b>59</b>                          |

|    | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br><b>SAI</b><br>8.1                            | Absolu<br>Recom<br>DC Ele<br>AC/DC<br>Index of<br>MPLE<br>128-Pii                      | te Maximum Ratings Imended Operating Conditions Intercept Characteristics — DSµP Electrical Characteristics — CL-MD1724 (SAFE) Intercept Information Intercept Characteristics — CL-MD1724 (SAFE) Intercept Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43<br>43<br>44<br>44<br><b>59</b><br>59                    |