# **FEATURES**

condition codes

□ Serial μ-coded Monolithic Multi-mode Intelligent Terminal (SμMMIT)

□ Comprehensive MIL-STD-1553 dual redundant Bus Controller (BC), Remote Terminal (RT), and Monitor Terminal (MT)

□ Compliant MIL-STD-1553B Notice II Remote Terminal

□ Simultaneous Remote Terminal/Monitor mode of operation

□ Autonomous operation in all three modes of operation

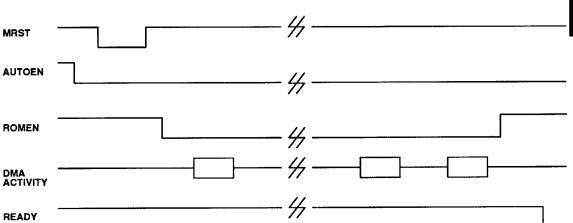

- Initialization via external ROM

Powerful BC instruction set with 15 opcodes and 7

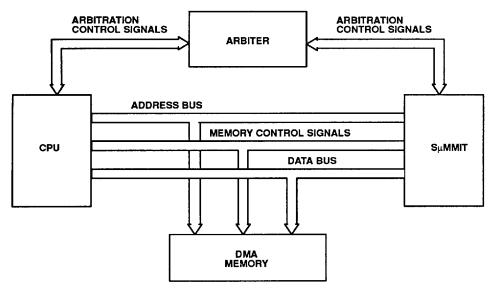

- □ Flexible host interface with complete DMA architecture

□ Internal illegalization in the RT mode of operation

- ☐ Programmable interrupt scheme with internally generated interrupt history list available

- $\hfill \Box$  Full 16-bit (R/W) time-tag with user-defined resolution

SHMMIT

Overview

- ☐ Built-In-Test capability

- ☐ Supports IEEE Standard 1149.1 (JTAG)

- ☐ Assembler available to ease programming

- ☐ Built on a low-power, 1.2μ CMOS process

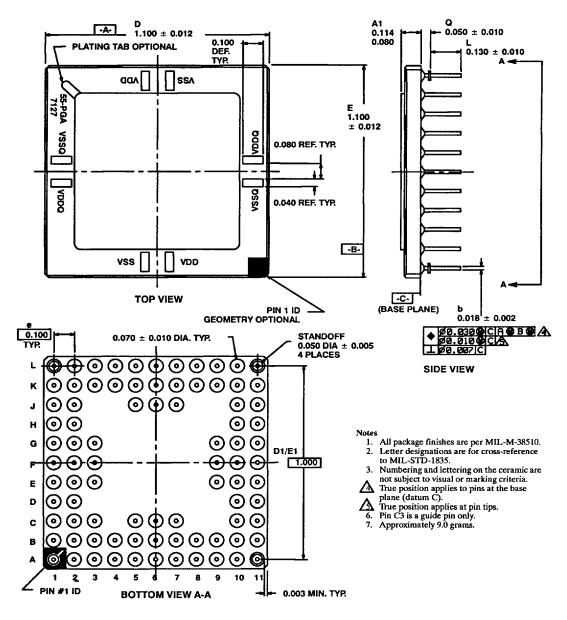

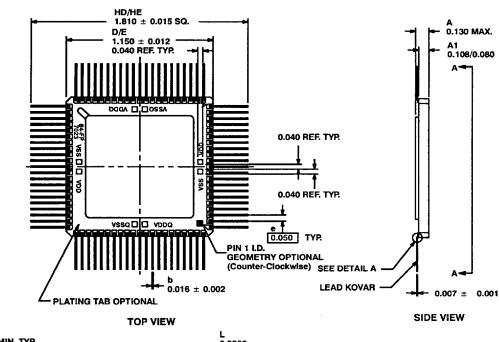

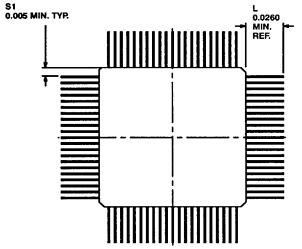

- ☐ Packaged in a 84-pin PGA or 84-lead flatpack

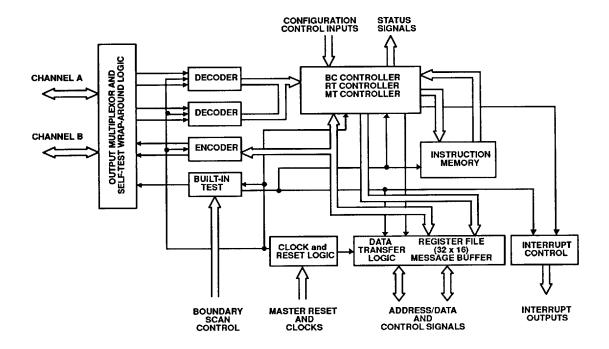

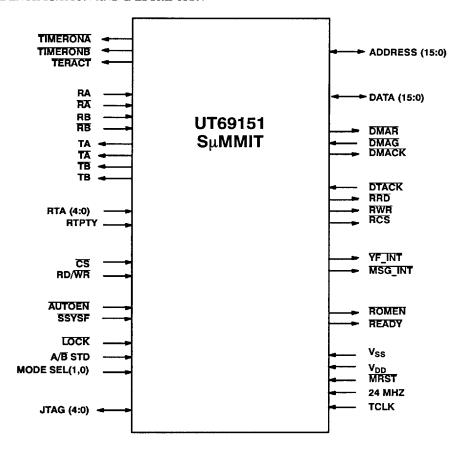

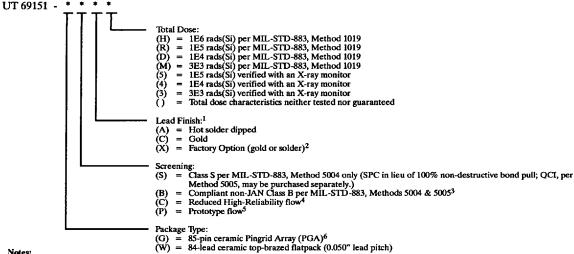

Figure 1. UT69151 SµMMIT Block Diagram

**SµMMIT**

**■** 9343947 0003861 999 ■

#### 1.0 Introduction

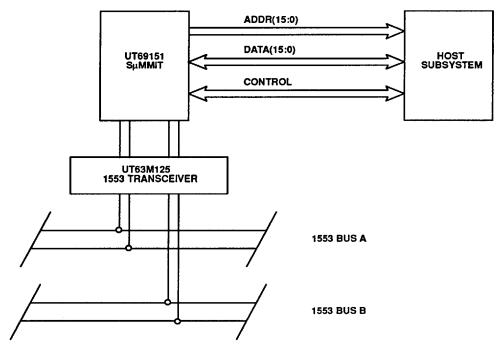

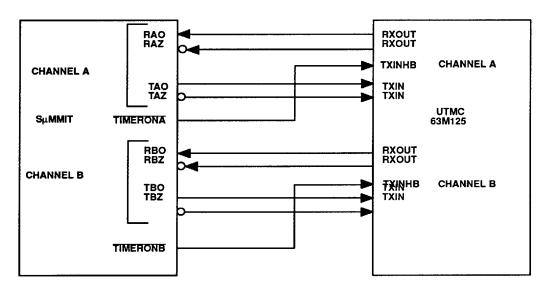

The monolithic CMOS UT69151 SµMMIT provides the system designer with an intelligent solution to MIL-STD-1553 multiplexed serial data bus design problems. The SµMMIT is a single-chip device that implements all three of the defined MIL-STD-1553 functions - Remote Terminal, Bus Controller, and Monitor. Operating either autonomously or with a tightly coupled host, the SµMMIT will solve a wide range of MIL-STD-1553 interface problems. A powerful RISC processing unit provides automatic message handling, message status, general status, and interrupt information. The register-based interface architecture provides many programmable functions as well as extensive information pertinent to device maintenance. In either of the three operating modes, the SµMMIT can access up to 64K x 16 of external memory (65,536 x 16).

The S $\mu$ MMIT (which derives its name from serial,  $\mu$ -coded, monolithic, multimode, intelligent, terminal) is a powerful asset to a system designer solving the MIL-STD-1553 problem.

#### 1.1 Remote Terminal Features

The SµMMIT Remote Terminal (SRT) conforms to the requirements of MIL-STD-1553B, Notice II. In addition to meeting the requirements of the Standard, the SRT has an extensive list of flexible features to meet any MIL-STD-1553B interface requirement.

# Indexing

The SRT can buffer up to 256 receive messages on a subaddress-by-subaddress basis. Upon reception of the specified number of messages, the SRT can generate an interrupt by signaling either the host or subsystem that data is ready for processing. The indexing feature is commonly used to implement bulk data transfer algorithms.

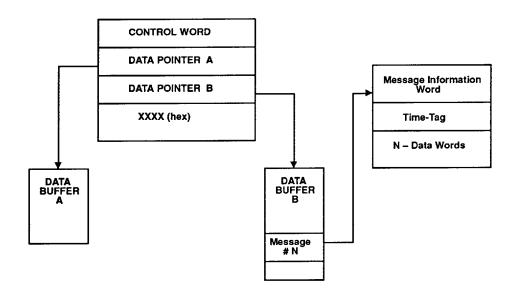

## Buffer Ping-Pong

To support the transfer of periodic data, double buffering schemes are often incorporated into remote terminal designs. Periodic data transfer incorporates the use of two data buffers per subaddress. The remote terminal processes messages (receive or transmit) via the designated primary buffer. The host or subsystem uses the secondary buffer to collect new data for transmission or process data received during the defined time interval. Upon completion of the defined interval, the remote terminal will switch the primary

and secondary data buffers (i.e., ping-pong). The SRT supports ping-pong buffering via a user-selected ping-pong architecture consisting of dual subaddress data pointers.

## Internal Illegalization

An internal 256-bit (16 x 16) RAM allows for the illegalization of all mode codes and subaddresses. The illegalization RAM is accessed at the beginning of message processing to determine if the valid command is prohibited. To eliminate host or subsystem overhead, the S $\mu$ MMIT can initialize the 256-bit illegalization RAM during the auto-initialization sequence.

#### Broadcast

Designed to meet the requirements of MIL-STD-1553B Notice II, the SRT can store all data associated with a broadcast command in separate memory from non-broadcast commands. This feature is user-selected via the Descriptor Control word and internal Control Register.

#### Interrupt History

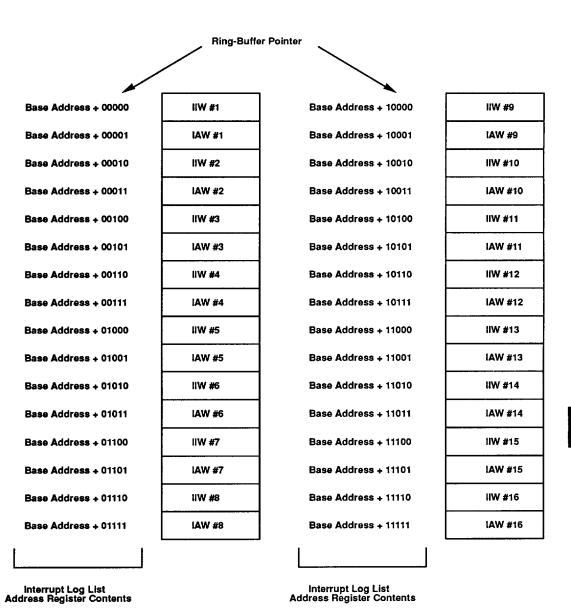

A programmable interrupt structure allows the host or subsystem the flexibility to enter 16 interrupts into a 32-word buffer before service. This feature allows the logging of multiple interrupts if immediate service is restricted. The interrupt structure enters an Interrupt Information word (IFW) and an Interrupt Address word (IAW) indicating what subaddress or command block generated the interrupt. All modes of operation support interrupt logging. For more details on the interrupt structure, refer to section 5.0.

#### Message Information

The SRT generates a Message Information word and time-tag (16-bit) for all transacted messages. This information is written into memory along with message data words. The Message Information word contains word count, message errors, and message type information.

#### 1.2 Bus Controller Features

The SµMMIT Bus Controller (SBC) is a powerful MIL-STD-1553 bus controller developed to meet the requirements of multi-frame processing with low host overhead. User-defined decision making allows the SBC to operate autonomously from the host until a designated event or series of events has taken place.

8 SμMMIT

■ 9343947 0003862 825 ■

#### Multiple Message Processing

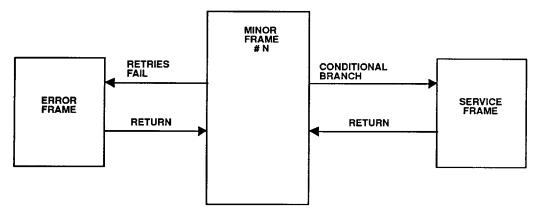

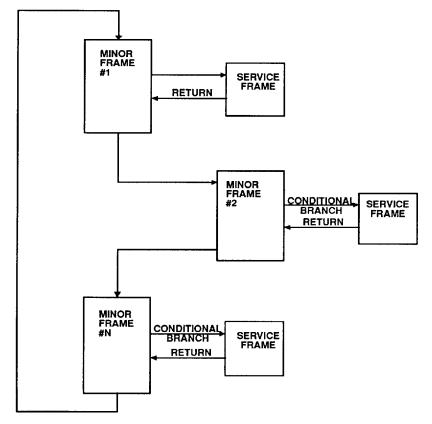

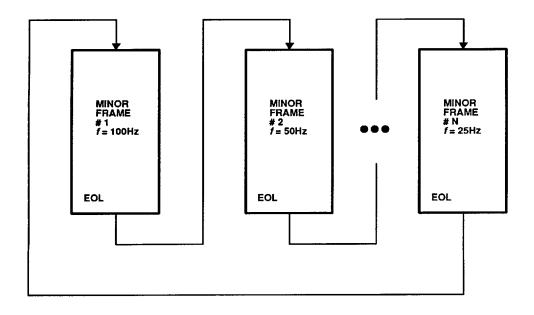

The SBC architecture allows the chaining of multiple MIL-STD-1553 commands into major and minor frames depending on the application. This feature allows the host to structure message frames that perform independent tasks such as periodic data transfer, service requests, and bus diagnostics (initiate BIT). The SBC uses a simple opcode scheme to control the command block flow.

# Message Scheduling

The SBC allows host entry of data to control the time between messages. This feature is useful when the BC has to perform periodic message transactions with multiple remote terminals.

#### Polling

The host instructs the SBC to interrogate the status word response of remote terminals to determine if any SBC action is required. The SBC can detect the assertion of status word bits and generate interrupts or branch to a new message frame. Polling is useful if the application requires control of message frame flow as a function of remote terminal response.

#### Automatic Retry

The SBC can automatically retry a message on busy, message error, or other status word bit response. If enabled, the SBC can retry up to four times on the primary bus or alternate bus.

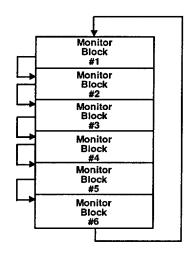

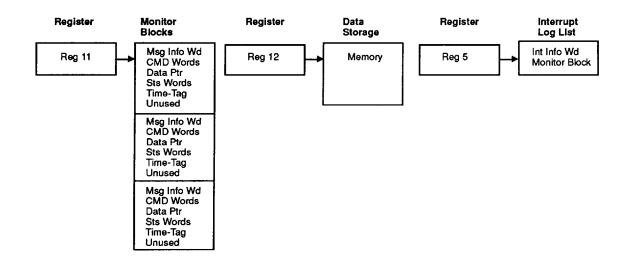

#### 1.3 Monitor Terminal Features

The SµMMIT Monitor Terminal (SMT) is a full-featured MIL-STD-1553B bus monitor designed to monitor all or selected remote terminals on the bus. Requiring little host intervention, the SMT will monitor selected remote terminals until a pre-defined message count is reached. Generation of an interrupt alerts the host that SMT service is required.

# Message Information

Each message transaction generates a message information word. This information helps determine message validity and remote terminal health. The message information word is stored in external memory along with message data words.

#### 1.4 Remote Terminal/Monitor Terminal Features

#### Monitor and Remote Terminal

For those applications that require the SMT to transfer or receive information, the S $\mu$ MMIT is configured as both a remote terminal (SRT) and monitor (SMT). This feature allows the SMT to communicate on the bus as an RT, and monitor bus activity. Configuration as both SMT and SRT precludes the SMT from monitoring its own remote terminal address.

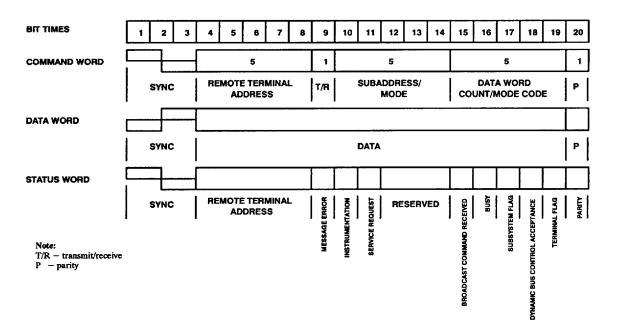

#### 1.5 Protocol Definition

For maximum flexibility, the SµMMIT has been designed to operate in many different systems which use various protocols. Specifically, two of the protocols that the SµMMIT may interface is MIL-STD-1553A and MIL-STD-1553B. To meet these protocols, the SµMMIT may be configured through an external pin or through control register bits.

# 2.0 REMOTE TERMINAL ARCHITECTURE

The SRT is an interface device linking a MIL-STD-1553 serial data bus to a host microprocessor and/or subsystem. The SRT's MIL-STD-1553 interface includes encoding/decoding logic, error detection, command recognition, DMA interface, control/configuration registers, clock, and reset logic. The following sections review the architecture and use. Each section supplies information on the SRT's configuration and operation.

## 2.1 Register Descriptions

The following list provides the bit descriptions of the 32 internal registers that control SRT operation. All register bits are active high and reflect a logic zero condition (0000 hex) after Master Reset (except those reflecting input pins).

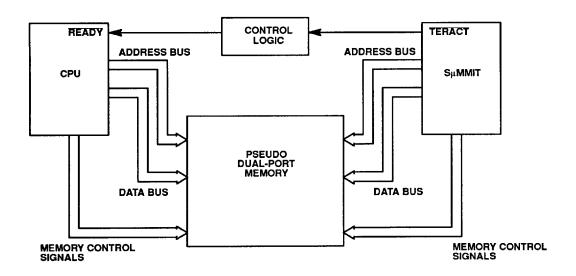

Note: Do not write internal registers while output pin TERACT is active.

| Register<br>Number | Name                                | Register Address   |

|--------------------|-------------------------------------|--------------------|

| 0                  | Control Register                    | 0000 (hex)         |

| 1                  | Operational Status Register         | 0001 (hex)         |

| 2                  | Current Command Register            | 0002 (hex)         |

| 3                  | Interrupt Mask Register             | 0003 (hex)         |

| 4                  | Pending Interrupt Register          | 0004 (hex)         |

| 5                  | Interrupt Log List Pointer Register | 0005 (hex)         |

| 6                  | BIT Word Register                   | 0006 (hex)         |

| 7                  | Time-Tag Register                   | 0007 (hex)         |

| 8                  | SRT Descriptor Pointer Register     | 0008 (hex)         |

| 9                  | 1553 Status Word Bits Register      | 0009 (hex)         |

| 10-15              | Not Applicable                      | 000A to 000F (hex) |

| 16-31              | Illegalization Registers            | 0010 to 001F (hex) |

# 2.1.1 Control Register (Read/Write) - Register 0

This 16-bit register controls SRT configuration. To make changes to the SRT and this register, the STEX bit (Bit 15 of the Control Register) must be logic zero.

Note: The user has 5µs after TERACT active to stop execution.

| Bit<br>Number | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                             |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15            | STEX     | Start Execution. Assertion of this bit initiates SµMMIT operation. A Control Register write negating this bit inhibits SµMMIT operation. A remote terminal address parity error prevents SRT operation regardless of the logical state of this bit. If an RT address parity error exists, bit 3 of Register 1 will be set low and bit 2 of Register 1 will be set high. |

| 14            | SBIT     | Start BIT. Assertion of this bit places the S $\mu$ MMIT into the Built-In Test routine. The BIT test takes 1ms to execute and has a fault coverage of 93.4%. If the S $\mu$ MMIT has been started, the host must halt the device in order to place the S $\mu$ MMIT into the Built-In Test routine (STEX = 0).                                                         |

|               |          | Note: If Start BIT (SBIT) and Start Execution (STEX) are both set on one register write, BIT has priority.                                                                                                                                                                                                                                                              |

| 13            | SRST     | Start Software Reset. Assertion of this bit immediately places the SµMMIT into a software reset. The software reset (which takes 5µs to execute), like MRST, clears all internal logic.                                                                                                                                                                                 |

|               |          | Note: During auto-initialization this bit should not be loaded with a logic one. SRST will only function after READYB is asserted.                                                                                                                                                                                                                                      |

| 12            | CHAEN    | Channel A Enable. Setting this bit enables Channel A operation. If negated, the SRT does not recognize commands received over Channel A.                                                                                                                                                                                                                                |

| 11            | CHBEN    | Channel B Enable. Setting this bit enables Channel B operation. If negated, the SRT does not recognize commands received over Channel B.                                                                                                                                                                                                                                |

| Bit<br>Number | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10            | ETCE     | External Timer Clock Enable. Assertion of this bit to a logic one allows the external timer clock input to supply stimulus to the internal time-tag counter. Refer to section 2.1.8.                                                                                                                                                                       |

|               |          | Note: The user can only change the clock frequency before starting the device (i.e., setting bit 15 of Register 0 to a logic one).                                                                                                                                                                                                                         |

| 9-7           | N/A      | Not Applicable.                                                                                                                                                                                                                                                                                                                                            |

| 6             | BUFR     | Buffer Mode Enable. Assertion of this bit enables the buffer mode of operation. For more detailed information on this feature refer to section 8.6.                                                                                                                                                                                                        |

| 5             | N/A      | Not Applicable.                                                                                                                                                                                                                                                                                                                                            |

| 4             | BCEN     | Broadcast Enable. Assertion of this bit enables the SRT broadcast option. Negation of this bit enables remote terminal address 31 as a unique remote terminal address.                                                                                                                                                                                     |

| 3             | DYNBC    | Dynamic Bus Control Acceptance. This bit controls the SRT's ability to accept the dynamic bus control mode code. Assertion of this bit allows the SRT to respond to a dynamic bus control mode code with status word bit 18 set to a logic one. Negation of this bit prevents the assertion of status word bit 18 upon reception of the dynamic mode code. |

| 2             | PPEN     | Ping-Pong Enable. Assertion of this bit enables the ping-pong buffer feature of the SRT and disables the message indexing feature. Negation of this bit disables the ping-pong feature and enables the message indexing feature.                                                                                                                           |

| 1             | INTEN    | Interrupt Log Enable. Assertion of this bit enables the SµMMIT interrupt logging feature. Negation of this bit prevents the logging of interrupts.                                                                                                                                                                                                         |

| 0             | XMTSW    | Transmit Last Status Word. Assertion of this bit allows the SRT to automatically execute the TRANSMIT LAST STATUS WORD mode code when configured for MIL-STD-1553A mode operation. Refer to section 2.9 of this document for further definition.                                                                                                           |

SµMMIT

11

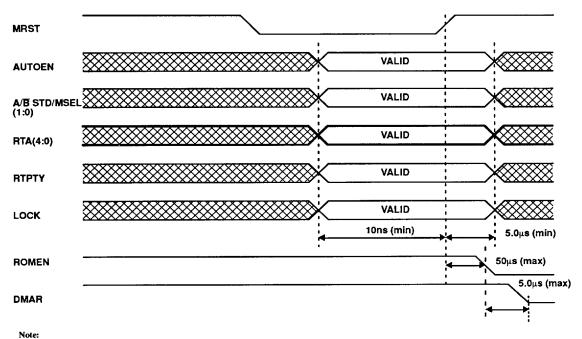

# 2.1.2 Operational Status Register (Read/Write) - Register 1

This register reflects pertinent status information for the SRT and is not reset to 0000 (hex) on MRST. Instead, the register reflects the actual stimulus applied to input pins RTA(4:0), RTAPTY, MSEL1:0, A/B STD, and LOCK. Assertion of the LOCK input prevents the modification of the remote terminal address, mode selects, and A or B Standard. In this case, a write to this register's most significant nine bits is meaningless. If LOCK is negated, a read of this register reflects the information written into this register's most significant nine bits.

Note: To make changes to the SRT and this register, the STEX bit (Bit 15 in Register 0) must be logic zero.

| Bit<br>Number | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15            | RTA4     | Terminal Address Bit 4. This bit is the most significant bit of the remote terminal address. This bit is latched on the rising edge of $\overline{MRST}$ and is a read only bit if the $\overline{LOCK}$ pin is active.                                                                                                                                                                                                                                         |  |

| 14            | RTA3     | Terminal Address Bit 3. This bit is Bit 3 of the remote terminal address. This bit is latched on the rising edge of $\overline{MRST}$ and is a read only bit if the $\overline{LOCK}$ pin is active.                                                                                                                                                                                                                                                            |  |

| 13            | RTA2     | Terminal Address Bit 2. This bit is Bit 2 of the remote terminal address. This bit is latched on the rising edge of $\overline{MRST}$ and is a read only bit if the $\overline{LOCK}$ pin is active.                                                                                                                                                                                                                                                            |  |

| 12            | RTA1     | Terminal Address Bit 1. This bit is Bit 1 of the remote terminal address. This bit is latched on the rising edge of $\overline{MRST}$ and is a read only bit if the $\overline{LOCK}$ pin is active.                                                                                                                                                                                                                                                            |  |

| 11            | RTA0     | Terminal Address Bit 0. This bit is the least significant bit of the remote terminal address. This bit is latched on the rising edge of MRST and is a read only bit if the LOCK pin is active.                                                                                                                                                                                                                                                                  |  |

| 10            | RTAPTY   | Terminal Address Parity Bit. This bit is appended to the remote terminal address bus (RTA(4:0)) to supply odd parity. The SRT requires odd parity for proper operation. This bit is latched on the rising edge of MRST and is a read only bit if the LOCK pin is active.                                                                                                                                                                                        |  |

| 9             | MSEL1    | Mode Select 1. In conjunction with MSEL0, this bit determines the SµMMIT mode of operation. This bit is latched on the rising edge of MRST and is a read only bit if the LOCK pin is active.                                                                                                                                                                                                                                                                    |  |

| 8             | MSEL0    | Mode Select 0. In conjunction with MSEL1, this bit determines the SµMMIT mode of operation. This bit is latched on the rising edge of MRST and is a read only bit if the LOCK pin is active.  MSEL1 MSEL0 Mode of Operation  0 0 SBC  0 1 SRT  1 0 SMT/SRT                                                                                                                                                                                                      |  |

| 7             |          | 1 SMT/SRT  Military Standard 1553A or 1553B Standard. This bit determines whether the SRT will be set to operate under MIL-STD-1553A or B. Assertion of this bit enables the XMTSW bit (Bit 0 of the Control Register). Negation of this bit automatically allows the SRT to operate under the MIL-STD-1553B protocol. This bit is latched on the rising edge of MRST and is a read only bit if the LOCK pin is active. See section 2.9 for further definition. |  |

| 6             | LOCK     | LOCK Pin. This read-only bit reflects the inverted state of input pin LOCK and is latched on the rising edge of MRST.                                                                                                                                                                                                                                                                                                                                           |  |

| Bit<br>Number | Mnemonic | Description                                                                                                                                                                                                                                             |

|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5             | AUTOEN   | AUTOEN Pin. This read-only bit reflects the inverted state of input pin AUTOEN. Assertion of this input enables SRT auto-initialization.                                                                                                                |

| 4             | SSYSF    | SSYSF Pin. This read-only bit reflects the inverted state of the input pin SSYSF.                                                                                                                                                                       |

| 3             | EX       | SμMMIT Executing. This read-only bit indicates whether the SRT is presently executing or whether it is idle. A logic one indicates that the SμMMIT is executing; logic zero indicates that the SμMMIT is idle.                                          |

| 2             | TPARF    | Terminal Parity Fail. This bit indicates the observance of a terminal address parity error. The SRT checks for odd parity. This read only bit reflects the parity of Operational Status Register bits 15-10, and is latched on the rising edge of MRST. |

| 1             | READY    | READY Pin. This read-only bit reflects the inverted state of the output pin READY and is cleared on reset.                                                                                                                                              |

| 0             | TERACT   | TERACT Pin. Assertion of this bit indicates that the SRT is presently processing a message. This read only bit reflects the inverted state of output pin TERACT and is cleared on reset.                                                                |

Note: Remote Terminal Address and Parity checked on start of execution.

# 2.1.3 Current Command Register (Read-only) - Register 2

This 16-bit register contains the last valid command processed by the SRT.

| Bit<br>Number | Mnemonic | Description                                                                                                                                                             |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 0       | CC15-CC0 | Current Command Bits. This register contains the last valid command received by the SRT. This register is valid 13µs after TERACT is negated. (Bit 15 MSB - Bit 0 LSB). |

# 2.1.4 Interrupt Mask Register (Read/Write) - Register 3

The SRT interrupt architecture allows for the masking of all interrupts. An interrupt is masked if the corresponding bit of this register is set to logic zero. This feature allows the host or subsystem to temporarily disable the service of interrupts. While masked, interrupt activity does not occur. The unmasking of an interrupt after the event occurs does not generate an interrupt for that event.

| Bit<br>Number | Mnemonic | Description                            |

|---------------|----------|----------------------------------------|

| 15            | DMAF     | DMA Fail Interrupt                     |

| 14            | WRAPF    | Wrap Fail Interrupt                    |

| 13            | TAPF     | Terminal Address Parity Fail Interrupt |

| 12            | BITF     | BIT Fail Interrupt                     |

| 11            | MERR     | Message Error Interrupt                |

| 10            | SUBAD    | Subaddress Accessed Interrupt          |

| 9             | BDRCV    | Broadcast Command Received Interrupt   |

| 8             | IXEQ0    | Index Equal Zero Interrupt             |

| 7             | ILLCMD   | Illegal Command Interrupt              |

| 6-0           | N/A      | Not Applicable                         |

# 2.1.5 Pending Interrupt Register (Read-only) - Register 4

The Pending Interrupt Register contains information that identifies events that generate interrupts. The assertion of any bit in this register asserts an output pin,  $\overline{MSG\_INT}$  or  $\overline{YF\_INT}$  (three clock cycles). A register read of the Pending Interrupt Register will clear all bits. Writing to the most significant 4 bits of this register generates a  $\overline{YF\_INT}$ .

| Bit<br>Number | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15            | DMAF     | DMA Fail Interrupt. Once the SµMMIT issues the DMAR signal, an internal timer starts. If all DMA activity (which includes DMAR to DMAG, and all wait states) is not completed by the time the counter decrements to zero, the interrupt is generated. In the SRT mode, the YF_INT interrupt is generated (if not masked), current command processing ends, and the SRT will remain on-line. Current cycle terminated, bus released. |

| 14            | WRAPF    | Wrap Fail Interrupt. The SRT automatically compares the transmitted word (encoder word) to the reflected decoder word via the continuous loop-back feature. If the encoder word and reflected word do not match, the WRAPF bit is asserted in the BIT Word Register and a YF_INT interrupt is generated (if not masked). The loop-back path is via the MIL-STD-1553 bus transceiver.                                                |

| 13            | TAPF     | Terminal Address Parity Fail Interrupt. This bit reflects the outcome of the remote terminal address parity check. A logic one indicates a parity failure. When a parity error occurs, the SRT does not begin operation (STEX bit forced to logic zero), channel A and B do not enable, the TAPF bit is asserted here and in the BIT Word Register, and a YF_INT interrupt is generated (if not masked).                            |

14 S<sub>M</sub>MMIT

| 12  | BITF  | BIT Fail Interrupt. Assertion of this bit indicates a BIT failure. Status word bit 19 is automatically set to a logic one when a BIT failure occurs. If a BIT fails, the BITF bit is asserted here and in the BIT Word Register, and a YF_INT interrupt is generated (if not masked). Operation continues.                                                                                                                                                  |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | MERR  | Message Error Interrupt. Assertion of this bit indicates that a message error condition exists. The SRT can detect Manchester errors, syncfield, word count errors (too many or too few), MIL-STD-1553 word parity errors, bit count errors (too many or too few), and protocol errors. If not masked, this bit is always set when the SRT asserts bit 9 of the status word (e.g., illegal commands, invalid data word, etc.). MSG_INT interrupt generated. |

| 10  | SUBAD | Subaddress Accessed Interrupt. Assertion of this bit indicates a pre-se-<br>lected subaddress has transacted a message. To determine the exact sub-<br>address, the host interrogates the interrupt log IAW. MSG_INT interrupt<br>generated.                                                                                                                                                                                                                |

| 9   | BDRCV | Broadcast Command Received Interrupt. This bit is set to a logic one to indicate the SRT's receipt of a valid broadcast command. The SRT suppresses status word transmission. MSG_INT interrupt generated.                                                                                                                                                                                                                                                  |

| 8   | IXEQ0 | Index Equal Zero Interrupt. The SRT asserts this bit to indicate the completion of a pre-defined number of commands by the SRT. Upon assertion of this interrupt, the host or subsystem updates the subaddress descriptor to prevent the potential loss of data. MSG_INT interrupt generated.                                                                                                                                                               |

| 7   | ILCMD | Illegal Command Interrupt, This bit is set to a logic one to indicate the reception of an illegal command by the SRT. Upon receipt of this command, the SRT responds with a status word only; Bit 9 of the status word is set to a logic one. MSG_INT interrupt generated.                                                                                                                                                                                  |

| 6-0 | N/A   | Not Applicable.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

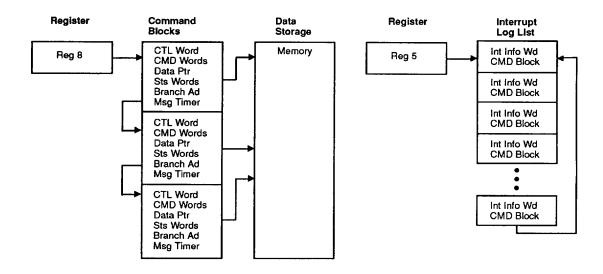

# 2.1.6 Interrupt Log List Pointer Register (Read/Write) - Register 5

The Interrupt Log List Pointer indicates the starting address of the Interrupt Log List. The Interrupt Log List is a 32 word ring-buffer that contains information pertinent to the service of interrupts. The SµMMIT architecture requires the location of the Interrupt Log List on a 32-word boundary. The most significant 11 bits of this register designate the location of the Interrupt Log List within a 64K memory space. The lower 5 bits of this register should be initialized to a logic zero. The SµMMIT controls the lower 5 bits to implement the ring-buffer architecture. The host or subsystem reads this register to determine the location and number of interrupts within the Interrupt Log List (least significant 5 bits).

Note: Bits 15-5 indicate the starting Base address while bits 4-0 indicate the ring location of the Interrupt Log List. See sections 5.0-5.3 for a description of the Interrupt Architecture.

| Bit<br>Number | Mnemonic   | Description                                                |

|---------------|------------|------------------------------------------------------------|

| 15-0          | INTA(15:0) | Interrupt Log List Pointer Bits. (Bit 15 MSB - Bit 0 LSB). |

# 2.1.7 BIT Word Register (Read/Write) - Register 6

This register contains information on the SRT's current health. The SRT transmits the contents of this register upon reception of a Transmit Bit Word Mode Code. The lower 10 bits of this register are user-defined.

| Bit<br>Number | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                          |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15            | DMAF     | DMA Fail. This bit is set if all DMA activity is not completed between the time $\overline{DMAR}$ asserts and when the timer decrements to zero (i.e., 7 $\mu$ s). The DMA activity includes $\overline{DMAR}$ to $\overline{DMAG}$ , and all wait states.                                                                                           |

| 14            | WRAPF    | Wrap Fail. The SRT automatically compares the transmitted word (encoder word) to the reflected decoder word via the continuous loop-back feature. If the encoder word and reflected word do not match, the WRAPF bit asserts and a <u>YF_INT</u> interrupt is generated (if not masked). The loop-back path is via the MIL-STD-1553 bus transceiver. |

| 13            | TAPF     | Terminal Address Parity Fail. This bit reflects the outcome of the remote terminal address parity check. A logic one indicates a parity failure. When a parity error occurs the SRT does not begin operation (STEX bit forced to a logic zero), channel A and B do not enable, and a $\overline{YF\_INT}$ interrupt is generated (if not masked).    |

| 12            | BITF     | BIT Fail. Assertion of this bit indicates a BIT failure. Bits 11 and 10 should be interrogated to determine the specific channel that failed. Status word bit 19 is automatically set to a logic one when a BIT failure occurs. If a BIT fails, the BITF bit is asserted, and a YF_INT interrupt is generated (if not masked).                       |

| 11            | CHAF     | Channel A Fail. Assertion of this bit indicates a BIT test failure in Channel A.                                                                                                                                                                                                                                                                     |

| 10            | СНВF     | Channel B Fail. Assertion of this bit indicates a BIT test failure in Channel B.                                                                                                                                                                                                                                                                     |

| 9-0           | UDB(9:0) | User-Defined Bits.                                                                                                                                                                                                                                                                                                                                   |

## 2.1.8 Time-Tag Register (Read/Write) - Register 7

The Time-Tag Register reflects the state of a 16-bit free running counter. The resolution of this counter is user-defined via input TCLK or fixed at  $64\mu$ s/bit. The Time-Tag counter is automatically reset when the SRT receives a valid synchronize without data mode code. The SRT automatically loads the Time-Tag counter with the data associated with reception of a valid synchronize with data mode code. The Time-Tag counter begins operation on the rising edge of  $\overline{MRST}$  or within  $64\mu$ s; after the receipt of a valid mode code, reset remote terminal, or sync with/without data. When the SRT is halted (STEX = 0), the Time-Tag continues to run.

| Bit<br>Number | Mnemonic | Description                                     |

|---------------|----------|-------------------------------------------------|

| 15-0          | TT(15:0) | Time-Tag Counter Bits. (Bit 15 MSB - Bit 0 LSB) |

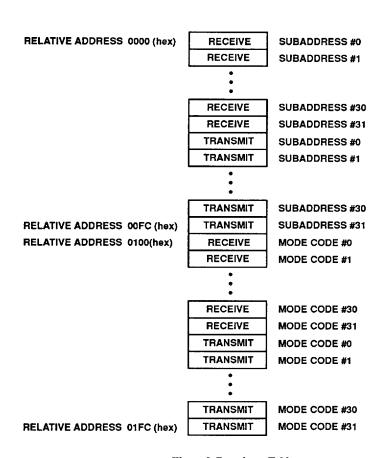

# 2.1.9 Remote Terminal Descriptor Pointer Register (Read/Write) - Register 8

The SRT accesses a block of external memory to gain information on how to process a valid command. Each subaddress and mode code has a block of memory reserved for this task. Located contiguously in memory, these reserved memory locations are called a descriptor space. The Remote Terminal Descriptor Pointer Register contains an address that points to the top of this memory space. The SRT uses the T/R bit, subaddress/mode code field, and mode code to select one block within the descriptor table for message processing. The Remote Terminal Descriptor Pointer Register is static during message processing.

| Bit<br>Number | Mnemonic   | Description                                                       |

|---------------|------------|-------------------------------------------------------------------|

| 15-0          | RTDA(15:0) | Remote Terminal Descriptor Address Bits. (Bit 15 MSB - Bit 0 LSB) |

# 2.1.10 1553 Status Word Bits Register (Read/Write) - Register 9

The host or subsystem accesses this register to control the outgoing MIL-STD-1553 status word. The host or subsystem controls the Instrumentation, Busy, Terminal Flag, Service Request, and Subsystem Flag by writing to bits 9 through 0 of this register. The SRT's status word response reflects assertion of these bit(s) until negated by the host or subsystem unless the Immediate Clear Function is enabled. The Immediate Clear Function automatically clears these bits after being transmitted in a status word.

The Immediate Clear Function does not affect the operation of the Transmit Last Status word and Transmit Last Command word Mode Codes. Transaction of a legal valid command with the INS bit set to a logic one and the Immediate Clear Function enabled, results in the transmission of a status word with Bit 10 asserted. If the ensuing command is a Transmit Last Status word or Last Command mode code, Bit 10 of the outgoing status word remains a logic one. For MIL-STD-1553B applications, the register is as follows:

| Bit Number | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15         | IMCLR    | Immediate Clear Function. Assertion of this bit enables the Immediate Clear Function (IMF) of the SRT. Enabling the IMF results in the clearing of the INS, BUSY, TF, SRQ, and/or SUBF bit immediately after a message is completed. This function is enabled by asserting this bit when asserting bit(s) INS, BUSY, TF, SRQ, and/or SSYSF. This bit should be used consistently since once set, it will remain set, and once cleared, it will remain cleared. |

| 14-10      | N/A      | Not Applicable.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9          | INS      | Instrumentation Bit. This bit asserts the Instrumentation bit of the MIL-STD-1553B status word. (Bit 10 of the Status Word).                                                                                                                                                                                                                                                                                                                                   |

| 8          | SRQ      | Service Request Bit. This bit asserts the Service Request bit of the MIL-STD-1553B status word. (Bit 11 of the Status Word).                                                                                                                                                                                                                                                                                                                                   |

| 7-4        | N/A      | Not Applicable.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3          | BUSY     | Busy Bit. Assertion of this bit is reflected in the outgoing MIL-STD-1553B status word. Assertion of this bit prevents memory accesses. (Bit 16 of the Status Word).                                                                                                                                                                                                                                                                                           |

| 2          | SSYSF    | Subsystem Flag Bit. This bit asserts the Subsystem Flag bit of the MIL-STD-1553B status word and may also be set with the SSYSF input pin. (Bit 17 of the Status Word).                                                                                                                                                                                                                                                                                        |

| 1          | N/A      | Not Applicable.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0          | TF       | Terminal Flag. Assertion of this bit is reflected in the outgoing MIL-STD-1553B status word. The SRT automatically asserts this bit if a BIT failure occurs. Inhibit Terminal Flag mode code prevents the assertion by the host or subsystem. Override Inhibit Terminal Flag Mode Code re-establishes the Terminal Flag option. (Bit 19 of the Status Word).                                                                                                   |

# For MIL-STD-1553A applications, the register is as follows:

**SB19**

0

| Bit Number | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15         | IMCLR    | Immediate Clear Function. Assertion of this bit enables the Immediate Clear Function (IMF) of the SRT. Enabling the IMF results in the clearing of the bit times 10-19 immediately after a status word is transmitted. This function is enabled by asserting this bit when asserting bit times 10-19. This bit should be used consistently since once set, it will remain set, and once cleared, it will remain cleared. |

| 14-10      | N/A      | Not Applicable.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9          | SB10     | Status bit time 10.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8          | SB11     | Status bit time 11.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7          | SB12     | Status bit time 12.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6          | \$B13    | Status bit time 13.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5          | SB14     | Status bit time 14.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4          | SB15     | Status bit time 15.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3          | SB16     | Status bit time 16.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2          | SB17     | Status bit time 17.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1          | SB18     | Status bit time 18.                                                                                                                                                                                                                                                                                                                                                                                                      |

Status bit time 19.

#### 2.1.11 Illegalization Registers

The 16 registers are divided into 8 blocks, 2 registers per block (see table 1).

Table 1. Illegalization Register Blocks

| Block Name                                     | Address (hex) |

|------------------------------------------------|---------------|

| Receive                                        | 0010 and 0011 |

| Transmit                                       | 0012 and 0013 |

| Broadcast Receive                              | 0014 and 0015 |

| Broadcast Transmit (Automatically Illegalized) | 0016 and 0017 |

| Mode Code Receive                              | 0018 and 0019 |

| Mode Code Transmit                             | 001A and 001B |

| Broadcast Mode Code Receive                    | 001C and 001D |

| Broadcast Mode Code Transmit                   | 001E and 001F |

The blocks correspond to the following types of commands. Register address 0010 (hex) and 0011 (hex) illegalize receive commands to 32 subaddresses. The most significant bit of register 0010 (hex) controls the illegalization of subaddress 01111. The least significant bit controls subaddress 00000. Register 0011 (hex) controls illegalization of subaddresses 10000 through 11111. The least significant bit relates to subaddress 10000; the most significant bit relates to subaddress 11111. Transmit commands and broadcast commands (both receive and transmit) use the same encoding scheme as receive subaddress illegalization.

Registers 18 (hex) through 1F (hex) control the illegalization of mode codes. Register 18 governs the illegalization of receive mode codes (T/R bit = 0) 00000 through 01111 and register 19 mode codes 10000 through 11111. Register blocks Transmit Mode Code (T/R bit = 1), Broadcast Receive Mode Codes, and Broadcast Transmit Mode Codes use the same decode scheme as receive mode codes.

Table 2 shows the illegalization register map. For each block, the numbers shown in the column under each bit number identifies the specific subaddress or mode code (in hex) that the register bit illegalizes. (Logical 0 = legal, Logical 1 = illegal)

20 SμMMIT

9343947 0003874 547 ■

Table 2. Illegalization Register Map

| Name              | Register<br>Number |                        |                        |                        |            |            |                        |                        |                        |                        |                        |                        |    |    |    |    |    |

|-------------------|--------------------|------------------------|------------------------|------------------------|------------|------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|----|----|----|----|----|

| Bit Number        |                    | 15                     | 14                     | 13                     | 12         | 11         | 10                     | 9                      | 8                      | 7                      | 6                      | 5                      | 4  | 3  | 2  | 1  | 0  |

| Receive           | 16                 | 0F                     | 0E                     | 0D                     | 0C         | 0B         | 0A                     | 09                     | 08                     | 07                     | 06                     | 05                     | 04 | 03 | 02 | 01 | 00 |

|                   | 17                 | 1F                     | 1E                     | 1D                     | 1C         | 1B         | 1A                     | 19                     | 18                     | 17                     | 16                     | 15                     | 14 | 13 | 12 | 11 | 10 |

| Transmit          | 18                 | 0F                     | 0E                     | 0 <b>D</b>             | 0C         | ОВ         | 0A                     | 09                     | 08                     | 07                     | 06                     | 05                     | 04 | 03 | 02 | 01 | 00 |

| ı                 | 19                 | 1F                     | 1E                     | 1D                     | 1C         | 1B         | 1A                     | 19                     | 18                     | 17                     | 16                     | 15                     | 14 | 13 | 12 | 11 | 10 |

| Brd Receive       | 20                 | 0F                     | 0E                     | 0 <b>D</b>             | 0C         | 0 <b>B</b> | 0 <b>A</b>             | 09                     | 08                     | 07                     | 06                     | 05                     | 04 | 03 | 02 | 01 | 00 |

|                   | 21                 | iF                     | 1E                     | 1D                     | 1C         | 1B         | 1A                     | 19                     | 18                     | 17                     | 16                     | 15                     | 14 | 13 | 12 | 11 | 10 |

| Brd Transmit      | 22                 | XX                     | XX                     | XX                     | XX         | XX         | XX                     | XX                     | XX                     | XX                     | XX                     | XX                     | XX | XX | XX | XX | XX |

|                   | 23                 | $\mathbf{x}\mathbf{x}$ | $\mathbf{X}\mathbf{X}$ | $\mathbf{X}\mathbf{X}$ | XX         | XX         | $\mathbf{X}\mathbf{X}$ | $\mathbf{x}\mathbf{x}$ | $\mathbf{X}\mathbf{X}$ | $\mathbf{x}\mathbf{x}$ | $\mathbf{X}\mathbf{X}$ | $\mathbf{X}\mathbf{X}$ | XX | XX | XX | XX | XX |

| Mode Receive      | 24                 | 0F                     | 0E                     | 0D                     | 0C         | 0B         | 0A                     | 09                     | 08                     | 07                     | 06                     | 05                     | 04 | 03 | 02 | 01 | 00 |

|                   | 25                 | 1F                     | 1E                     | 1D                     | 1C         | 1B         | 1A                     | 19                     | 18                     | 17                     | 16                     | 15                     | 14 | 13 | 12 | 11 | 10 |

| Mode Transmit     | 26                 | 0F                     | 0E                     | 0D                     | 0C         | 0B         | 0A                     | 09                     | 08                     | 07                     | 06                     | 05                     | 04 | 03 | 02 | 01 | 00 |

|                   | 27                 | 1F                     | 1E                     | 1D                     | 1C         | 1B         | 1A                     | 19                     | 18                     | 17                     | 16                     | 15                     | 14 | 13 | 12 | 11 | 10 |

| Mode Brd Receive  | 28                 | 0F                     | 0E                     | 0D                     | 0C         | 0B         | 0A                     | 09                     | 08                     | 07                     | 06                     | 05                     | 04 | 03 | UU | 01 | ww |

|                   | 29                 | 1F                     | 1E                     | 1D                     | 1 <b>C</b> | 1B         | 1A                     | 19                     | 18                     | 17                     | 16                     | 15                     | 14 | 13 | 12 | 11 | 10 |

| Mode Brd Transmit | 30                 | 0F                     | 0E                     | 0D                     | 0C         | 0B         | 0 <b>A</b>             | 09                     | 08                     | 07                     | 06                     | 05                     | 04 | 03 | ZZ | 01 | XX |

|                   | 31                 | YY                     | YY                     | YY                     | ΥY         | YY         | ΥY                     | ΥY                     | YY                     | YY                     | YY                     | YY                     | ΥΥ | YY | YY | YY | YY |

- Notes: 1. Brd = Broadcast

- 1. Bit = Broadcast

2. Mode = Mode code

3. XX = Automatically illegalized by SRT.

4. YY = Automatically illegalized by SRT in 1553B only.

5. ZZ = Automatically illegalized by SRT in 1553B and 1553A if XMTSW is enabled.

6. WW = Automatically illegalized in 1558A.

7. UU = Automatically illegalized in 1553A if XMTSW enabled.

## 2.2 Descriptor Block

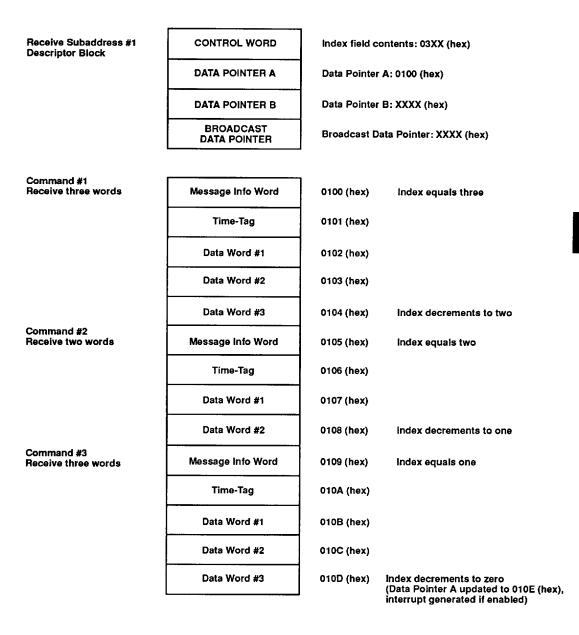

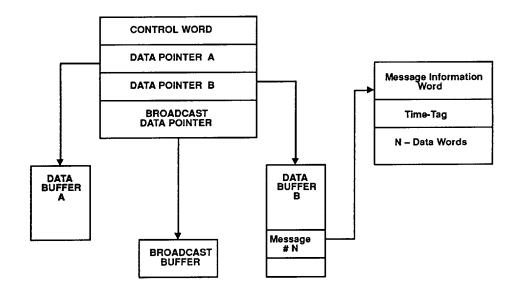

To process messages, the SRT uses data supplied in the internal registers with data stored in external memory. The SRT accesses a four word descriptor block stored in external memory. The descriptor block is accessed at the beginning and end of command processing. Multiple descriptor blocks are sequentially entered into memory to form a descriptor table. The following paragraphs discuss the descriptor block in detail.

The host or subsystem controlling the SRT allocates 512 consecutive memory spaces for the subaddress and mode code descriptor table (see figure 2). The top of the descriptor table can reside at any address location. Defined and entered into memory by the host, the SRT is linked to the descriptor table via the Descriptor Address Register contents. Each descriptor block contains a Control Word, Data Pointer A, Data Pointer B, and Broadcast Data Pointer. Each subaddress and mode code is assigned a descriptor for receive and transmit commands (T/R bit equal zero or one).

Control word information allows the SRT to generate interrupts, buffer messages, and control message processing. For a receive command, the Data List Pointer is read to determine the top of the data buffer. The SRT stores data sequentially from the top of data buffer plus two locations (e.g., 0100, 0101, 0102, 0103, etc.). When processing a transmit command, the Data List Pointer is read to determine where data words are retrieved. The SRT retrieves data words sequentially from the address the Data List Pointer designates plus two address locations.

The Broadcast Data Pointer allows for separate storage of non-broadcast data from broadcast data per MIL-STD-1553B Notice II. The host or subsystem enables or disables this feature via the Control Word's least significant bit. When disabled, the non-broadcast and broadcast data is stored via Data List Pointer A or B. For transmit commands, the Broadcast Data Pointer is not used. The SRT does not transmit any information on the receipt of a broadcast transmit command.

The SRT reads the descriptor block during command processing (i.e., after assertion of TERACT). The SRT arbitrates for the memory bus. After receiving control of the bus, the SRT reads the control word and three Data Pointers. The SRT then surrenders control of the bus back to the bus master (i.e., negates DMACK). The SRT then begins the acquisition of data words for either transmission or storage.

After transmission or reception, the SRT begins post-processing. Command post-processing begins with arbitration for the memory bus. The SRT performs a DMA burst during post-processing. An optional interrupt log entry is performed after a descriptor update. During the descriptor update, the SRT modifies the Control Word index field and bits 4, 2, and 1, if required. The SRT updates Data Pointer A if no message errors occurred during the message transaction. Reception of a broadcast command, with no message errors, results in the update of the Broadcast Data Pointer. Neither Data Pointer A, B or Broadcast is updated if the SRT has the ping-pong mode of operation enabled.

Figure 2. Descriptor Table

$S\mu MMIT \\$

23

## 2.2.1 Receive Control Word

The following bits describe the receive subaddress descriptor Control word. Information contained in this word assists the SRT in message processing. The descriptor control word is initialized by the host or subsystem and updated by the SRT during command post-processing.

| Bit<br>Number | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-8          | INDX     | Index Field. These bits define multiple message buffer length. The host or subsystem uses this field to instruct the SRT to buffer "N" messages. "N" can range from 0 (00 hex) to 256 (FF hex). If buffer ping-ponging is enabled, the INDX field is "don't care" (i.e., does not contain applicable information). During ping-pong mode operation, initialize the index field to 00 (hex). The SRT does not perform multiple message buffering in the ping-pong mode of operation. The index decrements each time a complete message is transacted (no message errors). The index does not decrement if the subaddress is illegalized. The SRT can generate an interrupt when the index field transitions from one to zero (see bit 7). |

| 7             | INTX     | Interrupt Index Equals Zero. Assertion of this bit enables the generation of an interrupt when the index field transitions from one to zero. The interrupt is entered into the Pending Interrupt Register if not masked in the Mask Register. Output pin MSG_INT asserts after message processing.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6             | IWA      | Interrupt When Accessed. Assertion of this bit enables the generation of an interrupt when the subaddress receives a valid command. The interrupt is entered into the Pending Interrupt Register if not masked in the Mask Register. Output pin MSG_INT asserts after message processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5             | IBRD     | Interrupt Broadcast Received. Assertion of this bit enables the generation of an interrupt when the subaddress receives a valid broadcast command. The interrupt is entered into the Pending Interrupt Register if not masked in the Mask Register. Output pin MSG_INT asserts after message processing.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4             | BAC      | Block Accessed. The subsystem or host initializes this bit to zero; the SRT overwrites the zero with a logic one upon completion of message processing. After interrogating this bit, the host resets this bit to zero to observe further accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3             | N/A      | Not Applicable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2             | А/В      | Buffer A/B. Indicates the last buffer accessed when buffer ping-pong is enabled. During initialization, the host designates the first buffer used by asserting or negating this bit. A logic one indicates buffer A; a logic zero indicates buffer B. This bit is a "don't care" if buffer ping-ponging is not enabled.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1             | BRD      | Broadcast Received. Assertion of this bit indicates the reception of a valid broadcast command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0             | NII      | Notice II. Assertion of this bit enables the use of the Broadcast Data Pointer as a buffer for broadcast command information. When negated, broadcast information is stored in the same buffer as non-broadcast information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# 2.2.2 Transmit Control Word

The following bits describe the transmit subaddress descriptor Control word. Information contained in this word assists the SRT in message processing. The descriptor control word is initialized by the host or subsystem and updated by the SRT during command post-processing.

| Bit<br>Number | Mnemonic | Description                                                                                                                                                                                                                                                                                                               |

|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-7          | N/A      | Not Applicable.                                                                                                                                                                                                                                                                                                           |

| 6             | IWA      | Interrupt When Accessed. Assertion of this bit enables the generation of an interrupt when the subaddress receives a valid command. The interrupt is entered into the Pending Interrupt Register if not masked in the Mask Register. Output pin MSG_INT asserts after message processing.                                 |

| 5             | N/A      | Not Applicable.                                                                                                                                                                                                                                                                                                           |

| 4             | BAC      | Block Accessed. The subsystem or host initializes this bit to zero, the SRT overwrites the zero with a logic one upon completion of message processing. After interrogation, the host should reset this bit to zero to observe further accesses.                                                                          |

| 3             | N/A      | Not Applicable.                                                                                                                                                                                                                                                                                                           |

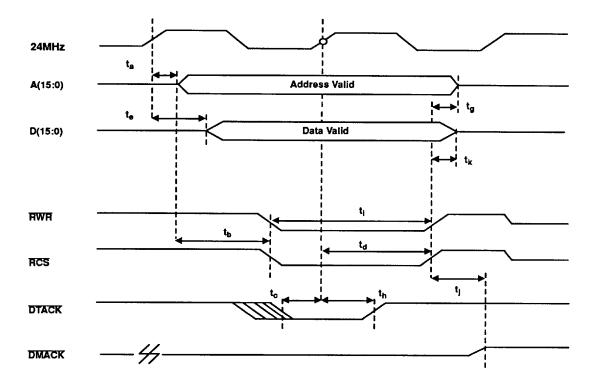

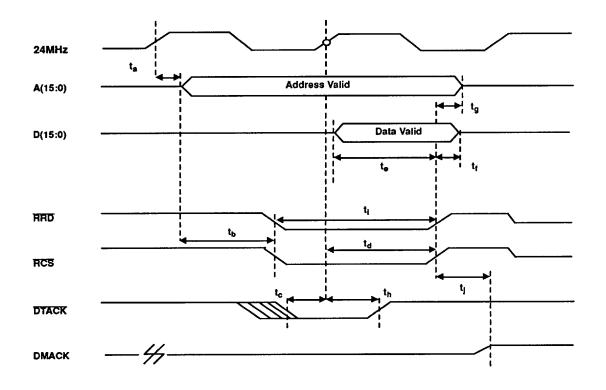

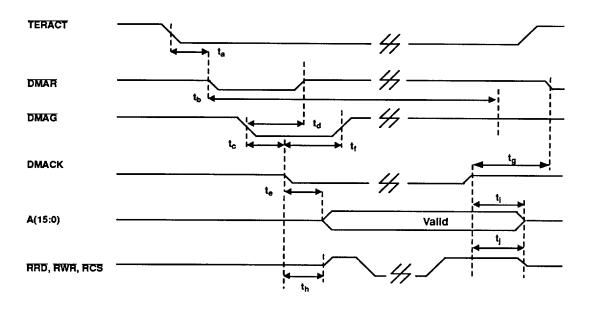

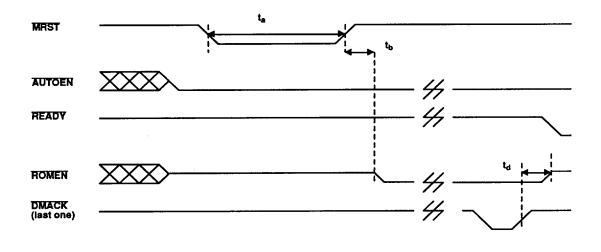

| 2             | A/B      | Buffer A/B. Indicates the data pointer to access when buffer ping-pong is enabled. During initialization, the host designates the first buffer used by asserting or negating this bit. A logic one indicates buffer A; a logic zero indicates buffer B. This bit is a "don't care" if buffer ping-ponging is not enabled. |