Inc.

## PUMA 2U2000

## PUMA 2U2000-12/15/17/20

Issue 1.2: February 1990

## ADVANCE PRODUCT INFORMATION

# 1,048,576 bit CMOS High Speed UV EPROM Features

User Configurable as 8,16 or 32 bit wide.

Very Fast access times of 120/150/170/200 ns.

Operating Power 1000mW (typ), 32 bit mode.

530mW (typ), 16 bit mode.

295mW (typ), 8 bit mode.

Low Power Standby 4mW (typ). Vpp Program Voltage of 12.5V.

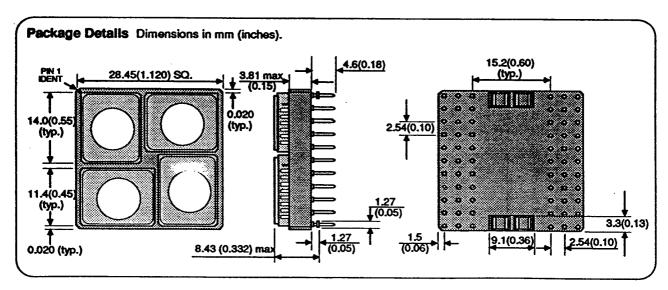

Pin grid array gives 2:1 improvement over DIL.

Package Suitable for Thermal Ladder Applications.

On board decoupling capacitors.

May be screened as BS9400 & MIL-STD-883C.

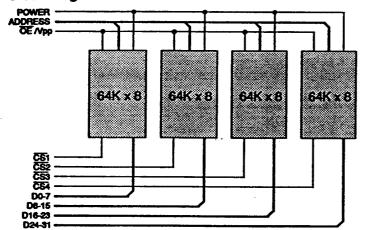

### **Block Dlagram**

| Pin | De | efini | tion       |               |    |    |    |

|-----|----|-------|------------|---------------|----|----|----|

|     | 1  | 12    | 23         |               | 34 | 45 | 56 |

|     | 0  | 0     | 0          |               | 0  | 0  | 0  |

|     | 0  | 0     | 0          |               | 0  | 0  | 0  |

|     | 0  | 0     | 0          |               | 0  | Ö  | 0  |

|     | 0  | 0     | 0          |               | 0  | 0  |    |

|     | 0  | 0     | 0          | VIEW          | 0  | 0  | 0  |

| i   | 0  | 0     | 0          | FROM<br>ABOVE | 0  | 0  |    |

|     | 0  | 0     | 0          |               | 0  | 0  | 0  |

| l   | 0  | 0     | 0          |               | 0  | 0  |    |

|     | 0  | 0     | 0          |               | 0  | 0  | 0  |

| I   | 0  | 0     | 0          |               | 0  | 0  | 0  |

| l   | 0  | 0     | 0          |               | 0  | 0  | 0  |

|     | 11 | 22    | <b>3</b> 3 |               | 44 | 55 | 66 |

For pinout see page 7

#### **Pin Functions**

A0-15 Address Inputs

D0-D32 Data Inputs/Outputs

CS1-4 Chip Select

OE/V<sub>PP</sub> Output Enable/Programming

Voltage

NC No Connect

V<sub>C</sub> Power (+5V)

GND Ground

## Absolute Maximum Ratings (1)

| Supply Voltage (2)    | V <sub>cc</sub>  | -0.6 to +6.25 | V  |

|-----------------------|------------------|---------------|----|

| Programming Voltage   | V <sub>PP</sub>  | -0.6 to +14   | V  |

| Input Voltage (2),(3) | V <sub>IN</sub>  | -0.6 to +6.25 | V  |

| Operating Temperature | Topa             | -60 to +140   |    |

| Storage Temperature   | T <sub>stg</sub> | -65 to +150   | °C |

Notes: (1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

(2) Pulse Width: -2.0V for less than 20ns.

(3) With Respect to GND.

#### **Recommended Operating Conditions**

|                                      |                 | <b>m</b> in | typ | max                |               |

|--------------------------------------|-----------------|-------------|-----|--------------------|---------------|

| DC Logic Supply Voltage              | $V_{\infty}$    | 4.75        | 5.0 | 6.3                | V             |

| DC EPROM Program Voltage             | VPP             | 12.2        | -   | 12.5               | V             |

| Input High Voltage                   | V <sub>aH</sub> | 2.0         | -   | V <sub>cc</sub> +1 | V             |

| Input Low Voltage                    | <b>V</b> ,,     | 0.3         | -   | 0.8                | V             |

| Operating Temperature <sup>(1)</sup> | T <sub>A</sub>  | 0           | •   | 70                 | <b>℃</b>      |

| •                                    | TAI             | -40         | -   | <b>8</b> 5         | °C (2000I)    |

|                                      | TAM             | -55         | -   | 125                | °C (2000M,MB) |

Note: (1) Programming would normally take place at 25°C

(2) When programming a 0.1μF high frequency by-pass capacitor is required across V<sub>pp</sub> and GND to suppress noise transients

#### **Operating Modes**

The Table below show the logic inputs required to control the operating modes of each EPROM on the PUMA2U2000.

| Mode            | cs | OE/VPP | V <sub>cc</sub> | Outputs  |

|-----------------|----|--------|-----------------|----------|

| Read            | 0  | 0      | 5V              | Data out |

| Output Disable  | 0  | 1      | 5V              | Floating |

| Standby         | 1  | X      | 5V              | Floating |

| Program         | 0  | 12.5V  | 6V              | Data in  |

| Program Verify  | 0  | 0      | 6V              | Data out |

| Program Inhibit | 1  | 12.5V  | 6V              | Floating |

$$1 = V_{iH}

0 = V_{iL}

X = V_{iH} \text{ or } V_{i}$$

#### **Device Identifier Mode**

The Identifier Mode allows the reading out of binary codes, which identify manufacturer and type of device, from the outputs of each EPROM. By this mode, the device can be automatically matched to the correct programming algorithm using a suitable EPROM Programmer. The table below shows the outputs of a single EPROM with the PUMA 2U2000 in 8 bit Mode.

| PINS              | <b>A9</b> | AO | D7 | D6 | D5 | D4 | D3       | D2 | D1 | D0 | HEX  |

|-------------------|-----------|----|----|----|----|----|----------|----|----|----|------|

| IDENTIFIER        |           |    |    |    |    |    | <b> </b> |    |    |    | DATA |

| Manufacturer Code | 12.0V     | V, | 0  | 0  | 0  | 1  | 1        | 1  | 1  | 1  | 1F   |

| Device Code       | 12.04     | V  | 1  | 0  | 0  | 0  | 1        | 1  | 0  | 1  | 0D   |

Notes (1) A1 - A8, A10 - A15, CS1 and OE are all held at VIL

## **READ OPERATION**

|  | DC Electric | al Characteristics | $(T_2 = -55)$ | °C to +125 | °C,V~=5V±5% |

|--|-------------|--------------------|---------------|------------|-------------|

|--|-------------|--------------------|---------------|------------|-------------|

| Parameter                         | Symbol            | Test Condition                                       | min        | typ | тах               | Unit |

|-----------------------------------|-------------------|------------------------------------------------------|------------|-----|-------------------|------|

| Input Leakage Current             | I <sub>IN1</sub>  | V <sub>IN</sub> =5.25V, Address & OE/V <sub>PP</sub> | -          | •   | 40                | μΑ   |

|                                   | L <sub>IN2</sub>  | CË1 - CE4                                            | -          | -   | 10                | μA   |

| Output Leakage Current            | lout              | V <sub>ouт</sub> =5.25V/0.45V                        | -          | -   | 40                | μA   |

| V <sub>PP</sub> Leakage Current   | I <sub>PP</sub>   | V <sub>PP</sub> =5.5V                                | -          | -   | 40                | μA   |

| Standby Power                     | I <sub>SB1</sub>  | CS = V <sub>sH</sub>                                 | -          | -   | 12                | mA   |

| Supply Current                    | l <sub>sts2</sub> | CS=V <sub>cc</sub> ±0.3V, L <sub>out</sub> =0mA      | -          | -   | 800               | μΑ   |

| Operating Power<br>Supply Current | l∞                | f=5MHz, l <sub>out</sub> =0mA (3)                    | <b>5</b> 9 | 106 | 200               | mA   |

| nput Low Voltage                  | V <sub>L</sub>    | Note (1)                                             | -0.6       | -   | 8.0               | V    |

| Input High Voltage                | V.                | Note (2)                                             | 2.0        | -   | V <sub>∞</sub> +1 | V    |

| Output LowVoltage                 | V <sub>a</sub>    | l <sub>ot</sub> =2.1mA                               | -          | -   | 0.45              | V    |

| Output HighVoltage                | V <sub>OH</sub>   | l <sub>oн</sub> =-400μΑ                              | 2.4        | -   | -                 | V    |

Notes (1) -1.0V for pulse width ≤ 50 ns

(2) Vcc+1.5V for pulse width ≤20 ns. If V<sub>M</sub> is over the specified max. value, READ operation cannot be guaranteed.

(3) For these currents min, typ and max values are given for 8, 16 and 32 bit mode operation respectively. Values are min.

| Capacitance : | (T <sub>4</sub> =25°C,f=1MHz | :) |

|---------------|------------------------------|----|

|---------------|------------------------------|----|

| Parameter           | Symbol          | Test Condition                  | typ | max | Unit |

|---------------------|-----------------|---------------------------------|-----|-----|------|

| Input Capacitance:  | C <sub>IN</sub> | V <sub>n</sub> =0V,8 bit mode   | 16  | 24  | pF   |

| Output Capacitance: | Cout            | V <sub>ouτ</sub> =0V,8 bit mode | 32  | 48  | рF   |

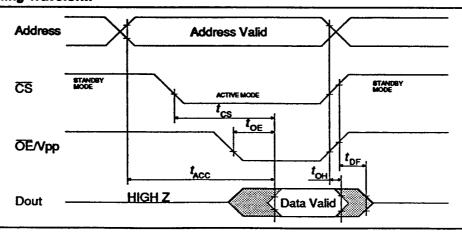

#### **AC Characteristics**

|                                               |                  | -   | 12         | -   | 15  | -   | 17  | -2  | 20         |      |

|-----------------------------------------------|------------------|-----|------------|-----|-----|-----|-----|-----|------------|------|

| Parameter                                     | Symbol           | min | max        | min | max | min | max | min | max        | Unit |

| Address to Output Delay                       | t <sub>ACC</sub> | -   | 120        | -   | 150 | -   | 170 | _   | 200        | ns   |

| CS to Output Delay                            | tcs              | -   | 120        | -   | 150 | -   | 170 | -   | 200        | ns   |

| OE/V <sub>pp</sub> to Output Delay            | to∈              | -   | <b>6</b> 5 | -   | 70  | -   | 70  | -   | <b>7</b> 5 | ns   |

| DE/V <sub>pp</sub> or CS High to Output Float | tne              | -   | 50         | -   | 50  | -   | 50  | -   | <b>5</b> 5 | ns   |

| O/P Hold from Address, CS or OE/V             | pe tou           | -   | 0          | -   | 0   | -   | 0   | -   | 0          | ns   |

| NOTE: $T_{ m DF}$ not measured but guarantee  |                  |     |            |     |     |     |     |     |            |      |

#### **AC Test Conditions**

- \* Input pulse levels: 0.45V to 2.4V

- \* Input rise and fall times: ≤ 20ns

- \* Input and Output timing reference levels: 0.8V and 2.0V

- \* Output load: 1 TTL gate plus 100pF.

## **Read Cycle Timing Waveform**

#### PROGRAMMING OPERATION

| DC Electrical Characteristics (T = 25°C ±5°C, V = 6V±0.25V, | $V_{\rm pp} = 12.5V \pm 0.5V$ |

|-------------------------------------------------------------|-------------------------------|

|-------------------------------------------------------------|-------------------------------|

| Parameter                      | Symbol                       | Test Condition              | min  | typ | max               | Unit |

|--------------------------------|------------------------------|-----------------------------|------|-----|-------------------|------|

| Input Leakage Current          | I <sub>N</sub>               | V <sub>IH</sub> =5.25V      | -    | -   | 40                | μΑ   |

| Operating Power                | •••                          | •••                         |      |     |                   |      |

| Supply Current                 | l <sub>cc</sub>              | Note (7)                    | 46   | 84  | 160               | mA   |

| V <sub>PP</sub> Supply Current | 1                            | Single Byte Programming (7) | 25   | 50  | 100               | mA   |

| Input Low Voltage              | <sup>1</sup> РР1<br><b>V</b> | Note (5)                    | -0.6 | -   | 0.8               | V    |

| Input High Voltage             | V <sub>H</sub>               | Note (6)                    | 2.0  | -   | V <sub>∞</sub> +1 | V    |

| Output LowVoltage (Verify      | /) Val                       | l <sub>oL</sub> =2.1mA      |      | _   | 0.45              | V    |

| Output HighVoltage (Verif      | v) V~.                       | ι <sub>οн</sub> =-400μΑ     | 2.4  | -   | •                 | V    |

- Notes (1)  $V_{cc}$  must be applied before  $V_{pp}$  and removed after  $V_{pp}$ . (2)  $V_{pp}$  must not exceed 13V including overshoot.

- (3) Device reliability may be affected if device is installed or removed while V<sub>pp</sub>= 12.5V

- (4) The transitions Vii to 12.5V or 12.5V to  $V_{ii}$  are not allowed while CS = Low.

- (5) -0.6V for pulse width ≤ 20 ns.

- (6) If V<sub>ih</sub> is over the specified maximum value, programming operation cannot be guaranteed.

- (7) For Vcc and Vpp Supply Currents, min, typ and max values are given for 8, 16 and 32 bit mode operation respectively. Each individual value shown is a maximum.

- (8) When programming a 0.1μF high frequency by-pass capacitor is required across V<sub>pp</sub> and GND to suppress noise transients

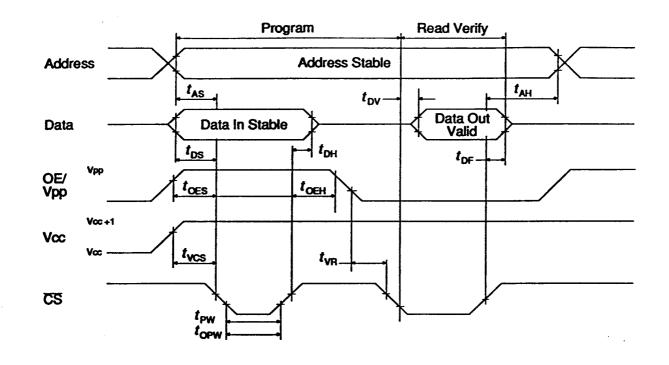

## AC Characteristics (T<sub>a</sub>=25±5°C, V<sub>cc</sub>=6.0±0.25V,OE/V<sub>pp</sub>=12.5±0.5V)

| Parameter                                             | Symbol           | min  | max   | Unit | Notes |

|-------------------------------------------------------|------------------|------|-------|------|-------|

| Address Setup Time                                    | t <sub>AS</sub>  | 2    | -     | μs   |       |

| OE/V <sub>PP</sub> Setup Time                         | t <sub>oes</sub> | 2    | -     | μs   | 1     |

| OE/V <sub>PP</sub> Hold Time                          | t <sub>OEH</sub> | 2    | -     | μs   | 1     |

| Data Setup Time                                       | tos              | 2    | -     | μs   |       |

| Address Hold Time                                     | tan              | 0    | -     | μs   |       |

| Data Hold Time                                        | t <sub>DH</sub>  | 2    | -     | μs   |       |

| CS High to Output Float Delay                         | t <sub>DFP</sub> | 0    | 130   | ns   | 2     |

| V <sub>∞</sub> Setup Time                             | t <sub>vcs</sub> | 2    | -     | μs   | 1     |

| CS Initial Program Pulse Width                        | t <sub>PW</sub>  | 0.95 | 1.05  | ms   | 3     |

| CS Overprogram Pulse Width                            | topw             | 2.85 | 78.75 | ms   | 4     |

| Data Valid from CS                                    | t <sub>DV</sub>  | •    | 1     | μs   | 2     |

| OE/V <sub>PP</sub> Recovery Time                      | t <sub>vR</sub>  | 2    | -     | μs   | 1     |

| OE/V <sub>PP</sub> Pulse Rise time during Programming | t <sub>PRT</sub> | 50   | •     | ns   |       |

#### Notes

- (1) V<sub>cc</sub> must be applied simultaneously or before  $\overline{\text{OE}}/\text{V}_{pp}$  and removed simultaneously or after  $\overline{\text{OE}}/\text{V}_{pp}$

- (2) Defines the time at which the output achieves the open circuit condition and is no longer driven. This parameter is not measured but guaranteed by design.

- (3) Initial program pulse width tolerance is 1 ms ± 5%.

- (4) Length of this pulse may vary as a function of the iteration counter value n.

## **AC Test Conditions**

- \* Input pulse levels: 0.45V to 2.4V

- \* Input rise and fall times: ≤ 20ns

- \* Input and Output timing reference levels: 0.8V and 2.0V

## **Programming Cycle Timing Waveform**

## Single Byte Programming

# HIGH PERFORMANCE PROGRAMMING ALGORITHM

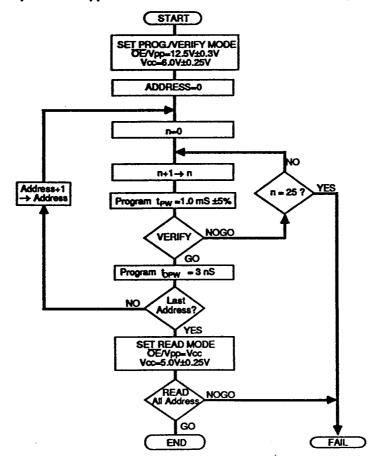

The PUMA2U2000 can be programmed using the alogorithm shown below. This allows faster programming times without stressing the device or causing deterioration in Data Retention Time.

Although the flow chart specifically refers to a single EPROM, all four devices on the PUMA tile can be programmed simultaneously in 32 bit mode, in pairs in 16 bit mode or singly in 8 bit mode. Obviously 32 bit mode is potentially the fastest programming time, but this makes greater demands on the Vpp Supply Current.

#### **Programming Algorithm**

Two  $\overline{\text{CS}}$  pulse widths are used to program, initial and overprogram. The address inputs are set to address the desired byte.  $V_{\text{CC}}$  is raised to 6.0V and  $\overline{\text{OE}}$ /Vpp is raised to 12.5v. The first  $\overline{\text{CS}}$  pulse is 1ms. The programmed byte is then verified. If the byte is programmed successfully, then an overprogram  $\overline{\text{CS}}$  pulse is applied for 3ms.

If the byte fails to program after the first 1ms pulse, then up to 25 successive 1ms pulses are applied with a verification after each pulse. When the byte passes verification, the overprogram pulse width is 3X (times) the number of 1ms pulses required earlier (75ms max).

If the part fails to verify after 25 1ms pulses have been applied, it is considered as failed. After the first byte is programmed, the address inputs are set to the next address repeating the algorithm until all required addresses are programmed. Then  $V_{\rm cc}$  and  $\overline{\rm OE}/V_{\rm pp}$  are lowered to 5.0V All bytes subsequently are read to compare with the original data to determine if the device passes or fails.

#### Notes:

1.V $_{\rm CC}$  must be applied simultaneously or before  $\overline{\rm OE}/V_{\rm PP}$  and removed simultaneously or after  $\overline{\rm OE}/V_{\rm PP}$ .

#### **ERASE**

Erasure of the PUMA 2U2000 is performed by exposure to ultraviolet light of 2537 Å at a minimum intensity of 15WS/cm², for approximately 15 - 20 minutes.

Note that sunlight and flourescent light may contain sufficient ultraviolet light to erase the programmed information. For this reason, and anyway for any operation in the READ mode, the transparent lids on this device should be covered with an opaque label.

## **Connection Table**

| PGA<br>Pin No. | Signal<br>Name |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1              | D8             | 2              | D9             | 3              | D10            | 4              | A13            | 5              | A15            |

| 6              | NC             | 7              | NC             | 8              | NC             | 9              | D0             | 10             | D1             |

| 11             | D2             | 12             | A14            | 13             | CS2            | 14             | GND            | 15             | D11            |

| 16             | A10            | 17             | A11            | 18             | A12            | 19             | Vcc            | 20             | CS1            |

| 21             | NC             | 22             | D3             | 23             | D15            | 24             | D14            | 25             | D13            |

| 26             | D12            | 27             | OE/Vpp         | 28             | NC             | 29             | A14            | 30             | D7             |

| 31             | D6             | 32             | D5             | 33             | D4             | 34             | D24            | 35             | D25            |

| 36             | D26            | 37             | A6             | 38             | A7             | 39             | NC             | 40             | <b>A8</b>      |

| 41             | A9             | 42             | D16            | 43             | D17            | 44             | D18            | 45             | Vcc            |

| 46             | CS4            | 47             | A14            | 48             | D27            | 49             | <b>A</b> 3     | 50             | A4             |

| 51             | A5             | 52             | A14            | 53             | CS3            | 54             | GND            | 55             | D19            |

| 56             | D31            | 57             | D30            | 58             | D29            | 59             | D28            | 60             | <b>A</b> 0     |

| 61             | A1             | 62             | A2             | 63             | D23            | 64             | D22            | 65             | D21            |

| 66             | D20            |                |                |                |                |                |                |                |                |

## Note:

Pins 12, 29, 47 and 52 (A14) are not connected together on the PUMA substrate - they must be connected externally.

#### **Military Screening Procedure**

Module Screening Flow for high reliability product is in accordance with MIL-STD-883C method 5004 Level B and is detailed below:

| MB MODULE SCREENING FLOW             |                                                                                                                            |              |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|

| SCREEN                               | TEST METHOD                                                                                                                |              |  |  |  |

| Visual and Mechanical                |                                                                                                                            |              |  |  |  |

| External visual<br>Temperature cycle | 2017 Condition B (or manufacturers equivalent)<br>1010 Condition C (10 Cycles,-65°C to +150°C)                             | 100%<br>100% |  |  |  |

| Burn-in                              |                                                                                                                            |              |  |  |  |

| Pre Bum-in Electrical<br>Bum-In      | Per Applicable device Specifications at $T_A = +25$ °C (optional)<br>Method 1015, Codition D, $T_A = +125$ °C              | 100%<br>100% |  |  |  |

| Final Electrical Tests               | Per applicable Device Specification                                                                                        |              |  |  |  |

| Static (dc)                          | <ul> <li>a) @ T<sub>A</sub>=+25°C and power supply extremes</li> <li>b) @ temperature and power supply extremes</li> </ul> | 100%<br>100% |  |  |  |

| Functional                           | <ul> <li>a) @ T<sub>A</sub>=+25°C and power supply extremes</li> <li>b) @ temperature and power supply extremes</li> </ul> | 100%<br>100% |  |  |  |

| Switching (ac)                       | <ul> <li>a) @ T<sub>A</sub>=+25°C and power supply extremes</li> <li>b) @ temperature and power supply extremes</li> </ul> | 100%<br>100% |  |  |  |

| Percent Defective Allowable (PDA)    | Calculated at Post Burn-in at T <sub>A</sub> =+25°C                                                                        | 10%          |  |  |  |

| Quality Conformance                  | Per applicable Device Specification                                                                                        | Sample       |  |  |  |

| External Visual                      | 2009 Per HMP or customer specification                                                                                     |              |  |  |  |

#### **Ordering Information**

## PUMA 2U2000MB-20

= 120 ns Speed 12 15 = 150 ns17 = 170 ns= 200 ns Blank = Commercial Temp. Temp. range/screening = Industrial Temp. M = Military Temp. MB = Screened in accordance with MIL STD 883C **Memory Type** U = UV EPROM

The policy of the company is one of continuous development and while the information presented in this data sheet is believed to be accurate, no liability is assumed for any data contained within. The company reserves the right to make changes without notice at any time.

© 1988 This design is the property of Mosaic Semiconductor, Inc.

019982 🗸 🕻

7420 Carroll Road San Diego, CA 92121 Tel: (619) 271 4565 FAX: (619) 271 6058

Semiconductor Inc.