PM7340 S/UNI-IMA-8

ISSUE 3

INVERSE MULTIPLEXING OVER ATM

## **PM7340**

## S/UNI-IMA-8

# S/UNI INVERSE MULTIPLEXING FOR ATM, 8 LINKS

# DATA SHEET

PROPRIETARY AND CONFIDENTIAL PRELIMINARY ISSUE 3: FEBUARY, 2001

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE i

PMC-2001723

PM7340 S/UNI-IMA-8

ISSUE 3

#### **CONTENTS**

| 1 | DEF   | NITIONS 1                                                    |

|---|-------|--------------------------------------------------------------|

| 2 | FEAT  | TURES                                                        |

| 3 | APPI  | LICATIONS                                                    |

| 4 | REFI  | ERENCES                                                      |

| 5 | APPI  | LICATION EXAMPLES 10                                         |

|   | 5.1   | MULTI-SERVICE ACCESS – IADS, ACCESS CONCENTRATORS<br>        |

|   | 5.2   | REMOTE DSLAM WAN UPLINK 10                                   |

| 6 | BLO   | CK DIAGRAM 12                                                |

| 7 | DES   | CRIPTION                                                     |

| 8 | PIN I | DIAGRAM 15                                                   |

| 9 | PIN I | DESCRIPTION 16                                               |

|   | 9.1   | RECEIVE SLAVE ATM INTERFACE (UTOPIA L2 MODE) (26<br>SIGNALS) |

|   | 9.2   | TRANSMIT SLAVE INTERFACE (ANY-PHY MODE) (30 SIGNALS)21       |

|   | 9.3   | TRANSMIT SLAVE INTERFACE (UTOPIA L2 MODE) (26<br>SIGNALS)    |

|   | 9.4   | MICROPROCESSOR INTERFACE (31 SIGNALS)                        |

|   | 9.5   | SDRAM I/F (35 SIGNALS)                                       |

|   | 9.6   | CLK/DATA (33 SIGNALS)                                        |

|   | 9.7   | GENERAL (5 SIGNALS)                                          |

|   | 9.8   | JTAG & SCAN INTERFACE (7 SIGNALS)                            |

**ISSUE 3**

PM7340 S/UNI-IMA-8

PMC-2001723

|    | 9.9  | POWER (120 SIGNALS)                                       |

|----|------|-----------------------------------------------------------|

| 10 | FUNC | CTIONAL DESCRIPTION                                       |

|    | 10.1 | ANY-PHY/UTOPIA INTERFACE 41                               |

|    |      | 10.1.1 TRANSMIT ANY-PHY/UTOPIA SLAVE (TXAPS) 41           |

|    |      | 10.1.2 RECEIVE ANY-PHY/UTOPIA SLAVE (RXAPS)               |

|    |      | 10.1.3 SUMMARY OF ANY-PHY/UTOPIA MODES 49                 |

|    |      | 10.1.4 ANY-PHY/UTOPIA LOOPBACK 50                         |

|    | 10.2 | IMA SUB-LAYER                                             |

|    |      | 10.2.1 OVERVIEW                                           |

|    |      | 10.2.2 IDCC SCHEDULER                                     |

|    |      | 10.2.3 TRANSMIT IMA PROCESSOR (TIMA) 52                   |

|    |      | 10.2.4 RECEIVE IMA DATA PROCESSOR (RDAT) 56               |

|    |      | 10.2.5 LINK/GROUP STATE MACHINES 69                       |

|    |      | 10.2.6 SUPPORT OF IMA TEST PATTERN PROCEDURE 80           |

|    |      | 10.2.7 SUPPORT OF SYMMETRIC/ASYMMETRIC OPERATION<br>MODES |

|    |      | 10.2.8 SUPPORT OF DIFFERENT IMA VERSIONS                  |

|    |      | 10.2.9 SDRAM INTERFACE 81                                 |

|    | 10.3 | LINK FIFOS                                                |

|    | 10.4 | TC LAYER 85                                               |

|    |      | 10.4.1 TX TC LAYER (TTTC) 85                              |

|    |      | 10.4.2 RX TC LAYER (RTTC) 85                              |

|    | 10.5 | LINE SIDE PHYSICAL LAYER 87                               |

PM7340 S/UNI-IMA-8

ISSUE 3

|    |       | 10.5.1 TX CLOCK/DATA (TCAS)                       |

|----|-------|---------------------------------------------------|

|    |       | 10.5.2 RX CLOCK/DATA (RCAS)                       |

|    | 10.6  | MICROPROCESSOR INTERFACE                          |

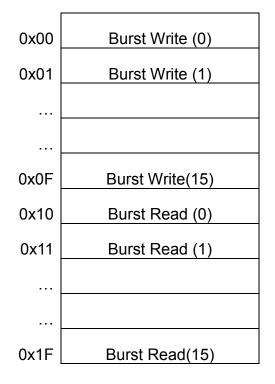

|    |       | 10.6.1 MAPPING AND LINK IDENTIFICATION            |

|    |       | 10.6.2 INTERRUPT DRIVEN ERROR/STATUS REPORTING 90 |

|    |       | 10.6.3 REGISTERS                                  |

| 11 | NOR   | MAL MODE REGISTER DESCRIPTION                     |

|    | 11.1  | GLOBAL AND INTERRUPT REGISTERS                    |

|    | 11.2  | MASTER INTERRUPT INTERFACE                        |

|    | 11.3  | UTOPIA INTERFACE REGISTERS 111                    |

|    | 11.4  | SDRAM CONFIGURATION AND DIAGNOSTIC ACCESS 118     |

|    | 11.5  | TC LAYER REGISTERS 125                            |

|    | 11.6  | LINE CLOCK/DATA INTERFACE 135                     |

|    | 11.7  | RIPP REGISTERS 149                                |

|    | 11.8  | RDAT REGISTERS 215                                |

|    | 11.9  | TIMA REGISTERS                                    |

|    | 11.10 | TX IDCC REGISTERS                                 |

|    | 11.11 | RX IDCC REGISTERS                                 |

| 12 | OPEF  | RATION                                            |

|    | 12.1  | HARDWARE CONFIGURATION                            |

|    | 12.2  | START-UP                                          |

|    | 12.3  | CONFIGURING THE S/UNI-IMA-8                       |

PMC-2001723

PM7340 S/UNI-IMA-8

ISSUE 3

|      | 12.3.1 CONFIGURING CLOCK/DATA INTERFACE                             | 259 |

|------|---------------------------------------------------------------------|-----|

|      | 12.3.2 CONFIGURING TC LAYER OPTIONS                                 | 261 |

|      | 12.3.3 UTOPIA INTERFACE CONFIGURATION                               | 261 |

| 12.4 | IMA_LAYER CONFIGURATION                                             | 262 |

|      | 12.4.1 INDIRECT ACCESS TO INTERNAL MEMORY TABLES                    | 262 |

|      | 12.4.2 CONFIGURING LINKS FOR TRANSMISSION<br>CONVERGENCE OPERATIONS | 263 |

|      | 12.4.3 CONFIGURING FOR IMA OPERATIONS                               | 264 |

| 12.5 | IMA OPERATIONS                                                      | 267 |

|      | 12.5.1 ISSUING A RIPP COMMAND                                       | 268 |

|      | 12.5.2 SUMMARY OF RIPP COMMANDS                                     | 269 |

|      | 12.5.3 ADDING A GROUP                                               | 275 |

|      | 12.5.4 DELETING A GROUP                                             | 276 |

|      | 12.5.5 RESTART GROUP                                                | 276 |

|      | 12.5.6 INHIBIT GROUP/NOT INHIBIT GROUP                              | 277 |

|      | 12.5.7 ADDING A LINK OR LINKS TO AN EXISTING GROUP<br>(START LASR)  | 277 |

|      | 12.5.8 REPORTING LINK DEFECTS IN THE ICP CELL                       | 278 |

|      | 12.5.9 FAULTING/INHIBITING LINKS                                    | 278 |

|      | 12.5.10 CHANGE TRL                                                  | 278 |

|      | 12.5.11 DELETING A LINK FROM A GROUP                                | 279 |

|      | 12.5.12 TEST PATTERN PROCEDURES                                     | 279 |

|      | 12.5.13 IMA EVENTS                                                  | 279 |

**ISSUE 3**

PM7340 S/UNI-IMA-8

PMC-2001723

| INVERSE         | MULTIPLE | XING OVE | RATM |

|-----------------|----------|----------|------|

| <b>INTERCOL</b> |          |          |      |

|    |       | 12.5.14 END-TO-END CHANNEL COMMUNICATION                 |

|----|-------|----------------------------------------------------------|

|    | 12.6  | DIAGNOSTIC FEATURES                                      |

|    |       | 12.6.1 ICP CELL TRACE                                    |

|    |       | 12.6.2 SDRAM DIAGNOSTIC ACCESS                           |

|    | 12.7  | IMA PERFORMANCE PARAMETERS AND FAILURE ALARMS<br>SUPPORT |

| 13 | FUNC  | CTIONAL TIMING                                           |

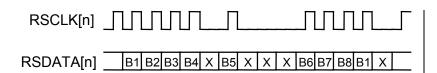

|    | 13.1  | RECEIVE LINK INPUT TIMING                                |

|    | 13.2  | TRANSMIT LINK OUTPUT TIMING                              |

|    | 13.3  | ANY-PHY/UTOPIA L2 INTERFACES                             |

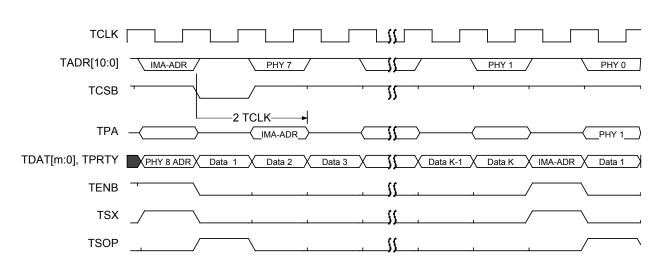

|    |       | 13.3.1 UTOPIA L2 TRANSMIT SLAVE INTERFACE                |

|    |       | 13.3.2 ANY-PHY TRANSMIT SLAVE INTERFACE                  |

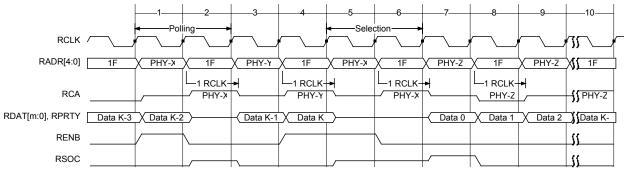

|    |       | 13.3.3 UTOPIA L2 MULTI-PHY RECEIVE SLAVE INTERFACE 292   |

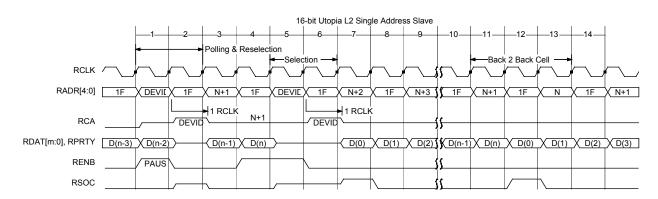

|    |       | 13.3.4 UTOPIA L2 SINGLE-PHY RECEIVE SLAVE INTERFACE      |

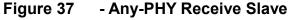

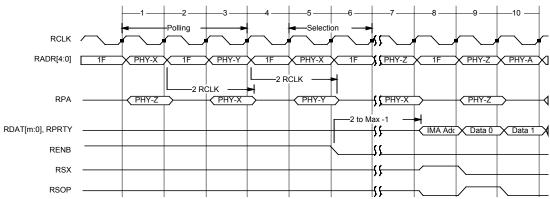

|    |       | 13.3.5 ANY-PHY RECEIVE SLAVE INTERFACE                   |

|    | 13.4  | SDRAM INTERFACE                                          |

| 14 | ABSC  | DLUTE MAXIMUM RATINGS                                    |

| 15 | D. C. | CHARACTERISTICS                                          |

| 16 | A.C   | TIMING CHARACTERISTICS                                   |

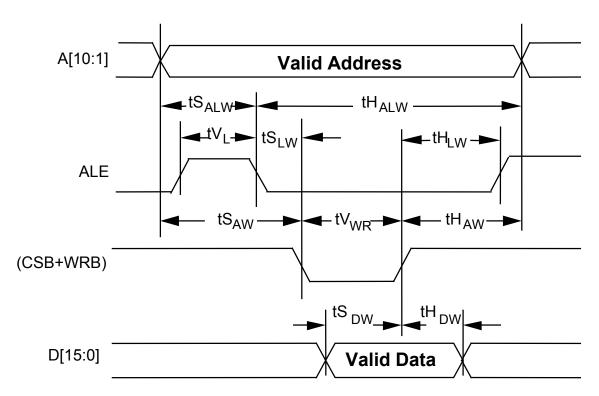

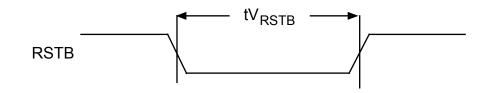

|    | 16.1  | MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS          |

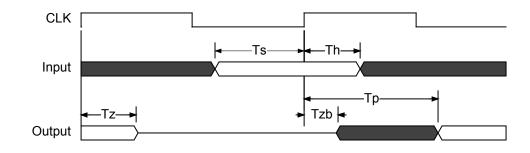

|    | 16.2  | SYNCHRONOUS I/O TIMING                                   |

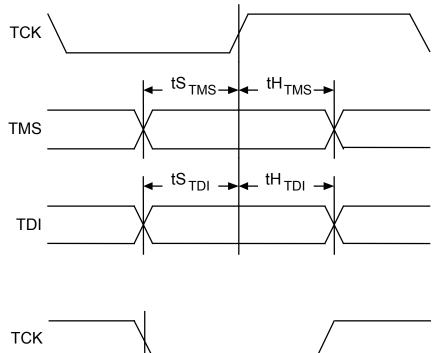

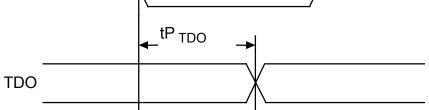

|    | 16.3  | JTAG TIMING                                              |

PRELIMINARY INVERSE MULTIPLEXING OVER ATM DATA SHEET

PMC-2001723

PMC-2001723

PMC-2001723

INVERSE MULTIPLEXING OVER ATM

17

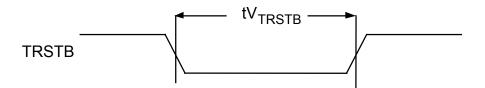

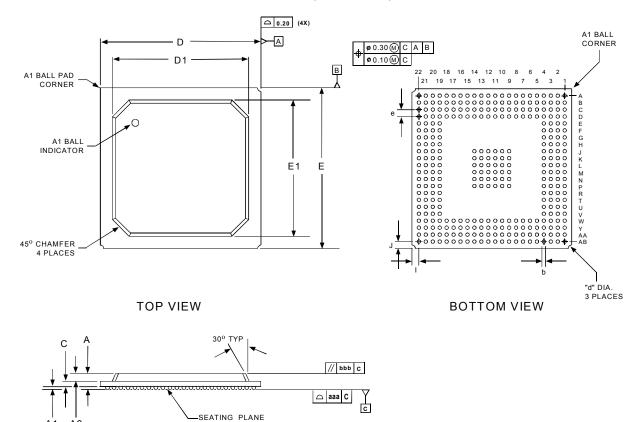

ORDERING AND THERMAL INFORMATION

313

18

MECHANICAL INFORMATION

314

PMC-Sierra, Inc.

PM7340 S/UNI-IMA-8

PMC-2001723

ISSUE 3

#### LIST OF FIGURES

| FIGURE 1 - MULTI-SERVICE ACCESS – IADS AND ACCESS<br>CONCENTRATORS                        |

|-------------------------------------------------------------------------------------------|

| FIGURE 2 -S/UNI-IMA-8 IN A REMOTE DSLAM WAN UPLINK APPLICATION.11                         |

| FIGURE 3 - S/UNI-IMA-8 BLOCK DIAGRAM 12                                                   |

| FIGURE 4 - S/UNI-IMA PRELIMINARY PINOUT (BOTTOM VIEW) 15                                  |

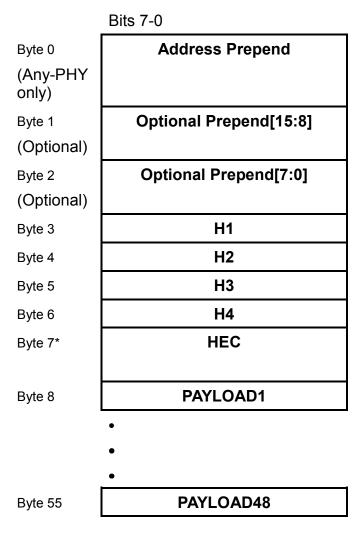

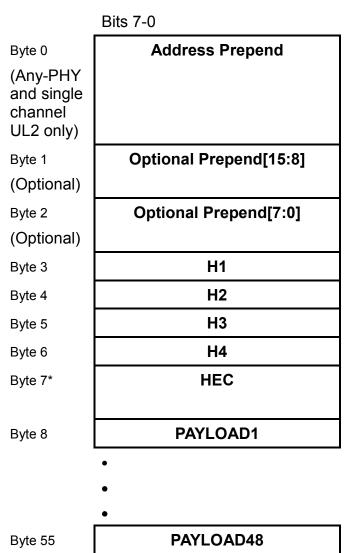

| FIGURE 5 - 16-BIT TRANSMIT CELL TRANSFER FORMAT                                           |

| FIGURE 6 - 8-BIT TRANSMIT CELL TRANSFER FORMAT                                            |

| FIGURE 7 - 16-BIT RECEIVE CELL TRANSFER FORMAT                                            |

| FIGURE 8 - 8-BIT RECEIVE CELL TRANSFER FORMAT                                             |

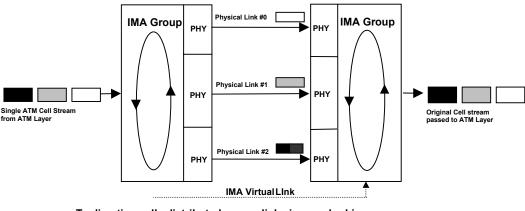

| FIGURE 9 - INVERSE MULTIPLEXING                                                           |

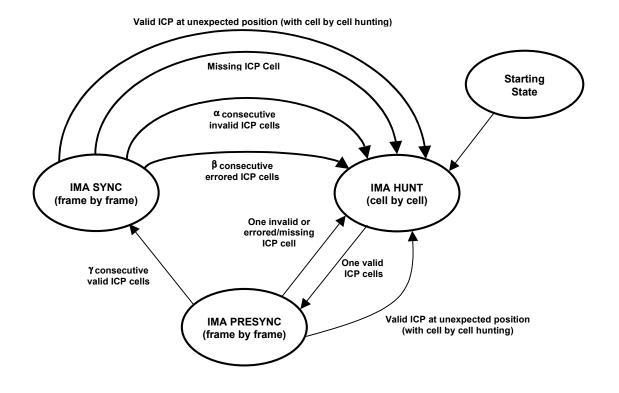

| FIGURE 10- IFSM STATE MACHINE                                                             |

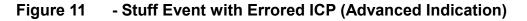

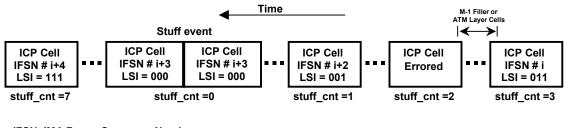

| FIGURE 11 - STUFF EVENT WITH ERRORED ICP (ADVANCED INDICATION)<br>60                      |

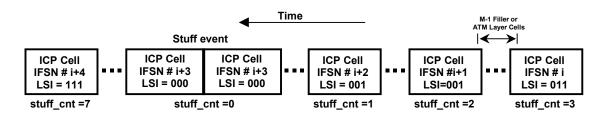

| FIGURE 12- INVALID STUFF SEQUENCE (ADVANCED INDICATION) 60                                |

| FIGURE 13 - ERRORED/INVALID ICP CELLS IN PROXIMITY TO A STUFF<br>EVENT                    |

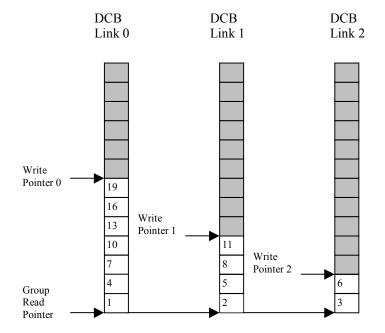

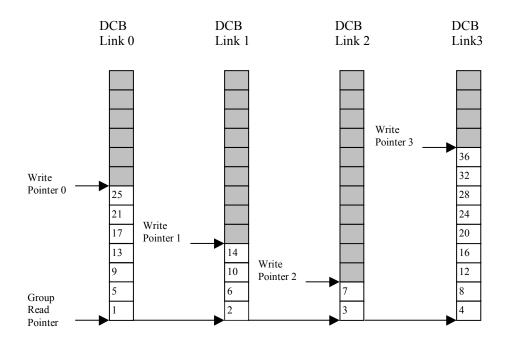

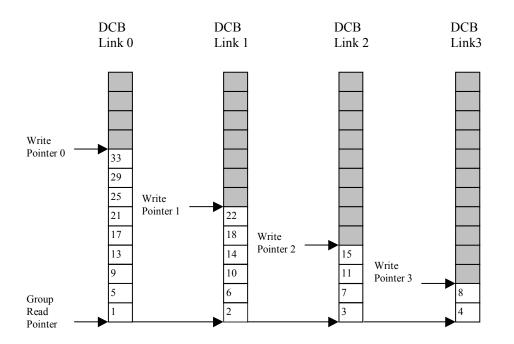

| FIGURE 14- SNAPSHOT OF DCB BUFFERS                                                        |

| FIGURE 15- SNAPSHOT OF DCB BUFFERS AFTER ADDITION OF LINK WITH<br>SMALLER TRANSPORT DELAY |

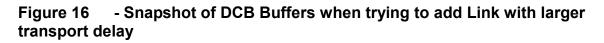

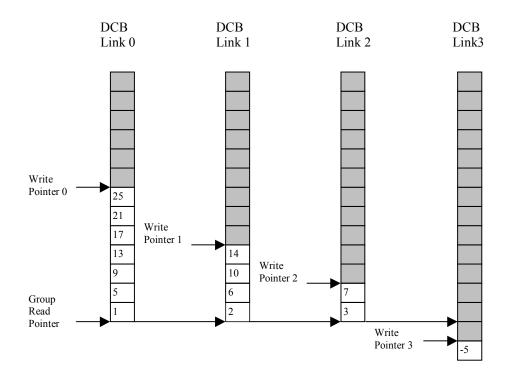

| FIGURE 16- SNAPSHOT OF DCB BUFFERS WHEN TRYING TO ADD LINK<br>WITH LARGER TRANSPORT DELAY |

| FIGURE 17 - SNAPSHOT OF DCB BUFFERS AFTER DELAY ADJUSTMENT 65                             |

**ISSUE 3**

PM7340 S/UNI-IMA-8

PMC-2001723

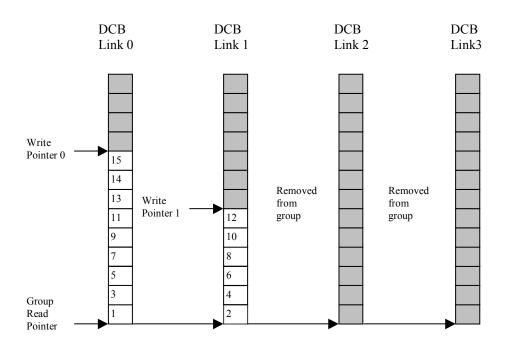

| FIGURE 18- SNAPSHOT OF DCB BUFFERS AFTER DELETION OF LINKS<br>FROM GROUP |

|--------------------------------------------------------------------------|

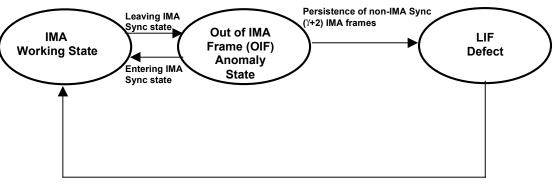

| FIGURE 19- IMA ERROR/MAINTENANCE STATE DIAGRAM                           |

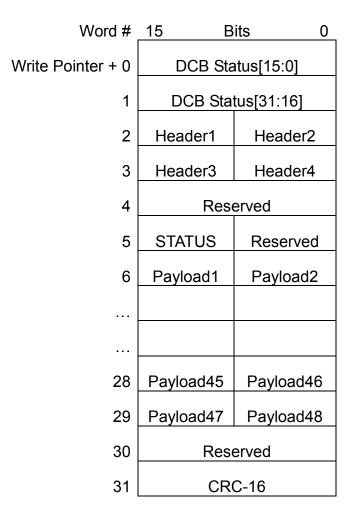

| FIGURE 20 - CELL STORAGE MAP 82                                          |

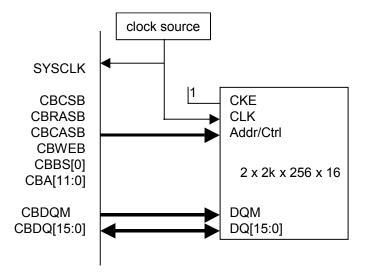

| FIGURE 21 - 2 MBYTE 83                                                   |

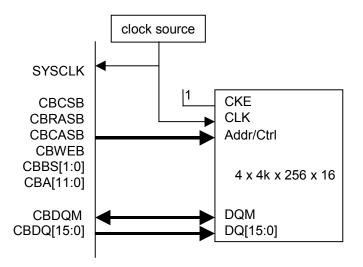

| FIGURE 22 - 8 MBYTE 83                                                   |

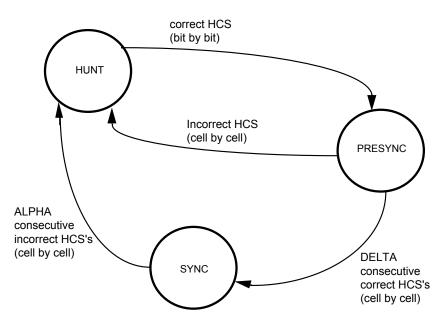

| FIGURE 23- CELL DELINEATION STATE DIAGRAM                                |

| FIGURE 24-BURST RAM FORMAT 121                                           |

| FIGURE 25- UNCHANNELIZED RECEIVE LINK TIMING                             |

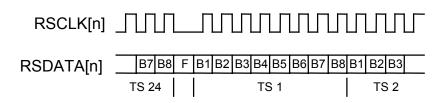

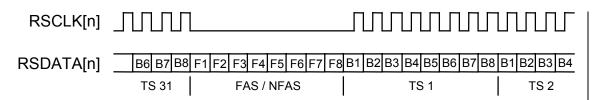

| FIGURE 26- CHANNELIZED T1 RECEIVE LINK TIMING 287                        |

| FIGURE 27 - CHANNELIZED E1 RECEIVE LINK TIMING                           |

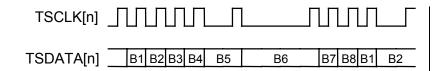

| FIGURE 28- UNCHANNELIZED TRANSMIT LINK TIMING 288                        |

| FIGURE 29- CHANNELIZED T1 TRANSMIT LINK TIMING W/ CLOCK GAPPED<br>LOW    |

| FIGURE 30- CHANNELIZED T1 TRANSMIT LINK TIMING W/ CLOCK GAPPED<br>HIGH   |

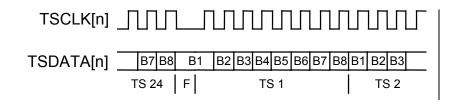

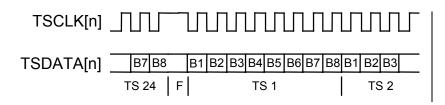

| FIGURE 31- CHANNELIZED E1 TRANSMIT LINK TIMING W/ CLOCK GAPPED<br>LOW    |

| FIGURE 32- CHANNELIZED E1 TRANSMIT LINK TIMING W/ CLOCK GAPPED<br>HOW    |

| FIGURE 33- UTOPIA L2 TRANSMIT SLAVE                                      |

| FIGURE 34 - ANY-PHY TRANSMIT SLAVE                                       |

| FIGURE 35- UTOPIA L2 MULTI-PHY RECEIVE SLAVE                             |

| FIGURE 36- UTOPIA L2 SINGLE-PHY RECEIVE SLAVE                            |

| FIGURE 37 - ANY-PHY RECEIVE SLAVE                                        |

**ISSUE 3**

PM7340 S/UNI-IMA-8

DATA SHEET PMC-2001723

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

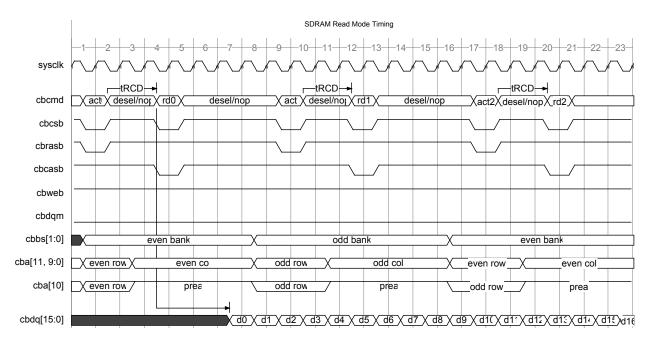

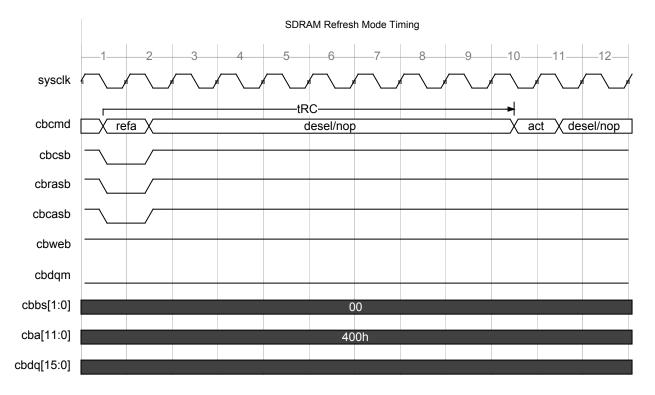

| FIGURE 38- SDRAM READ TIMING                     | 295   |

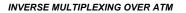

|--------------------------------------------------|-------|

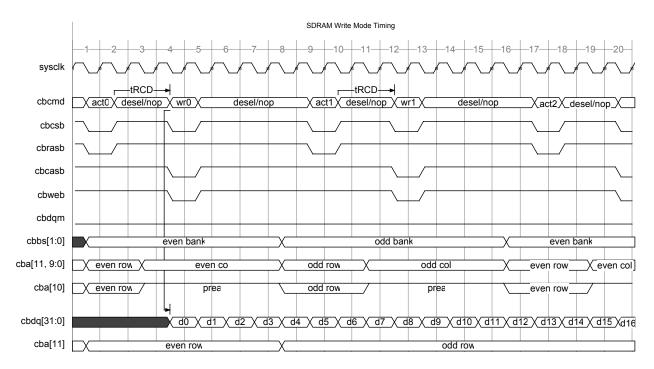

| FIGURE 39- SDRAM WRITE TIMING                    | 296   |

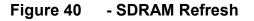

| FIGURE 40- SDRAM REFRESH                         | 297   |

| FIGURE 41- POWER UP AND INITIALIZATION SEQUENCE  | 298   |

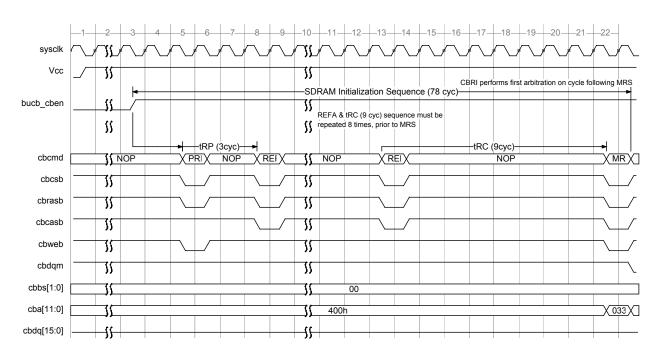

| FIGURE 42- MICROPROCESSOR INTERFACE READ TIMING  | 304   |

| FIGURE 43- MICROPROCESSOR INTERFACE WRITE TIMING | 306   |

| FIGURE 44- RSTB TIMING                           | 307   |

| FIGURE 45- SYNCHRONOUS I/O TIMING                | 307   |

| FIGURE 46- JTAG PORT INTERFACE TIMING            | . 312 |

PMC-2001723

PM7340 S/UNI-IMA-8

ISSUE 3

#### LIST OF TABLES

| TABLE 1  | REVISION HISTORY                                |

|----------|-------------------------------------------------|

| TABLE 2  | TERMINOLOGY 1                                   |

| TABLE 3  | UTOPIA L2 AND ANY-PHY COMPARISON                |

| TABLE 4  | PM COMMAND DESCRIPTION                          |

| TABLE 5  | REGISTER MEMORY MAP                             |

| TABLE 6  | CONFIGURATION MEMORY ADDRESS SPACE 150          |

| TABLE 7  | CONTEXT MEMORY ADDRESS SPACE                    |

| TABLE 8  | RIPP GROUP CONFIGURATION RECORD STRUCTURE 152   |

| TABLE 9  | RX PHYSICAL LINK TABLE 159                      |

| TABLE 10 | RIPP TX LINK CONFIGURATION RECORD STRUCTURE 160 |

| TABLE 11 | RIPP RX LINK CONFIGURATION RECORD STRUCTURE 162 |

| TABLE 12 | RIPP GROUP CONTEXT RECORD STRUCTURE 163         |

| TABLE 13 | RIPP TX LINK CONTEXT RECORD STRUCTURE 175       |

| TABLE 14 | RIPP RX LINK CONTEXT RECORD STRUCTURE 178       |

| TABLE 15 | COMMAND REGISTER ENCODING 195                   |

| TABLE 16 | COMMAND DATA REGISTER ARRAY FORMAT 203          |

| TABLE 17 | GROUP ERROR/STATUS BIT MAPPING 204              |

| TABLE 18 | LINK EVENT INTERRUPT BIT MAPPING 207            |

| TABLE 19 | LINK STATUS BIT MAPPING 209                     |

| TABLE 20 | RECEIVE ICP CELL BUFFER STRUCTURE               |

| TABLE 21 | RDAT LINK STATISTICS RECORD (IMA) 219           |

**ISSUE 3**

PM7340 S/UNI-IMA-8

PMC-2001723

| TABLE 22       RDAT LINK STATISTICS RECORD (TC)            | )           |

|------------------------------------------------------------|-------------|

| TABLE 23       RDAT IMA GROUP STATISTICS RECORD            | l           |

| TABLE 24       RDAT TC GROUP STATISTICS RECORD       222   | <u>&gt;</u> |

| TABLE 25 RDAT VALIDATION RECORD                            | 2           |

| TABLE 26    RDAT LINK CONTEXT RECORD    225                | 5           |

| TABLE 27       RECEIVE ICP CELL BUFFER STRUCTURE       230 | )           |

| TABLE 28       RDAT IMA GROUP CONTEXT RECORD               | <u>&gt;</u> |

| TABLE 29    RDAT TC CONTEXT RECORD    233                  | 3           |

| TABLE 30 RECEIVE ATM CONGESTION COUNT REGISTER             | 3           |

| TABLE 31 TRANSMIT IMA GROUP CONTEXT RECORD                 | ł           |

| TABLE 32 TRANSMIT GROUP CONFIGURATION TABLE RECORD         | 7           |

| TABLE 33 TRANSMIT LID TO PHYSICAL LINK MAPPING TABLE       | 3           |

| TABLE 34 TIMA PHYSICAL LINK CONTEXT RECORD                 | 3           |

| TABLE 35 260                                               |             |

| TABLE 36 IMA PERFORMANCE PARAMETER SUPPORT       282       | <u>&gt;</u> |

| TABLE 37 IMA FAILURE ALARM SUPPORT       284               | ł           |

| TABLE 38 ABSOLUTE MAXIMUM RATINGS                          | )           |

| TABLE 39 D.C. CHARACTERISTICS                              | )           |

| TABLE 40       MICROPROCESSOR INTERFACE READ ACCESS        | 3           |

| TABLE 41 MICROPROCESSOR INTERFACE WRITE ACCESS             | 5           |

| TABLE 42 RTSB TIMING                                       | 3           |

| TABLE 43 SYSCLK AND REFCLK TIMING                          | ,           |

|                                                            |             |

PMC-Sierra, Inc.

**ISSUE 3**

PM7340 S/UNI-IMA-8

DATA SHEET PMC-2001723

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

| TABLE 44 | CELL BUFFER SDRAM INTERFACE                | 307  |

|----------|--------------------------------------------|------|

| TABLE 45 | ANY-PHY/UTOPIA TRANSMIT INTERFACE          | 308  |

| TABLE 46 | ANY-PHY/UTOPIA RECEIVE INTERFACE           | 308  |

| TABLE 47 | SERIAL LINK INPUT                          | 309  |

| TABLE 48 | SERIAL LINK OUTPUT                         | 310  |

| TABLE 49 | JTAG PORT INTERFACE                        | .311 |

| TABLE 50 | ORDERING AND THERMAL INFORMATION           | 313  |

| TABLE 51 | THERMAL INFORMATION - THETA JA VS. AIRFLOW | 313  |

PM7340 S/UNI-IMA-8

PMC-2001723

ISSUE 3

## LIST OF REGISTERS

| REGISTER | 0X000: GLOBAL RESET                                              | 98      |

|----------|------------------------------------------------------------------|---------|

| REGISTER | 0X002: GLOBAL CONFIGURATION                                      | 99      |

| REGISTER | 0X004: JTAG ID (MSB)                                             | . 101   |

| REGISTER | 0X006: JTAG ID (LSB)                                             | . 101   |

| REGISTER | 0X008: MASTER INTERRUPT REGISTER                                 | . 102   |

| REGISTER | 0X00A: MISCELLANEOUS INTERRUPT REGISTER                          | . 104   |

| REGISTER | 0X00C: TC INTERRUPT FIFO                                         | . 106   |

| REGISTER | 0X010: MASTER INTERRUPT ENABLE REGISTER                          | . 108   |

| REGISTER | 0X012: MISCELLANEOUS INTERRUPT ENABLE REGISTER.                  | . 109   |

| REGISTER | 0X014: TC INTERRUPT ENABLE REGISTER                              | 110     |

|          | 0X020: TRANSMIT ANY-PHY/UTOPIA CELL AVAILABLE ENAB<br>111        | BLE     |

| REGISTER | 0X022: RECEIVE UTOPIA CELL AVAILABLE ENABLE                      | 112     |

|          | 0X024: RECEIVE ANY-PHY/UTOPIA CONFIG REG (RXAPS_C<br>113         | FG)     |

| REGISTER | 0X026: TRANSMIT ANY-PHY/UTOPIA CONFIG REG (TXAPS_                | CFG)115 |

|          | 0X028: TRANSMIT ANY-PHY ADDRESS CONFIG REGISTER<br>XAPS_ADD_CFG) | 117     |

| REGISTER | 0X040: SDRAM CONFIGURATION                                       | 118     |

| REGISTER | 0X042 SDRAM DIAGNOSTICS                                          | 119     |

| REGISTER | 0X044: SDRAM DIAG BURST RAM INDIRECT ACCESS                      | . 120   |

| REGISTER | 0X046: SDRAM DIAG INDIRECT BURST RAM DATA LSB                    | . 121   |

|          |                                                                  |         |

PM7340 S/UNI-IMA-8

ISSUE 3

| REGISTER 0X048: SDRAM DIAG INDIRECT BURST RAM DATA MSB 121        |

|-------------------------------------------------------------------|

| REGISTER 0X04A: SDRAM DIAG WRITE CMD 1 123                        |

| REGISTER 0X04C: SDRAM DIAG WRITE CMD 2 123                        |

| REGISTER 0X04E: SDRAM DIAG READ CMD 1 124                         |

| REGISTER 0X050: SDRAM DIAG READ CMD 2 124                         |

| REGISTER 0X060: TTTC INDIRECT STATUS 125                          |

| REGISTER 0X062: TTTC INDIRECT LINK DATA REGISTER #1 126           |

| REGISTER 0X070: RTTC INDIRECT LINK STATUS 127                     |

| REGISTER 0X072: RTTC INDIRECT LINK DATA REGISTER #1 129           |

| REGISTER 0X074: RTTC INDIRECT LINK DATA REGISTER #2 132           |

| REGISTER 0X076: RTTC INDIRECT LINK DATA REGISTER #3 134           |

| REGISTER 0X078: LCD COUNT THRESHOLD 135                           |

| REGISTER 0X100: RCAS INDIRECT LINK AND TIME-SLOT SELECT 135       |

| REGISTER 0X102: RCAS INDIRECT LINK DATA                           |

| REGISTER 0X104: RCAS FRAMING BIT THRESHOLD 139                    |

| REGISTER 0X106: RCAS LINK DISABLE                                 |

| REGISTER 0X140- 0X14E: RCAS LINK #0 TO LINK #7 CONFIGURATION. 141 |

| REGISTER 0X180: TCAS INDIRECT LINK AND TIME-SLOT SELECT 142       |

| REGISTER 0X182: TCAS INDIRECT CHANNEL DATA 144                    |

| REGISTER 0X184: FRAMING BIT THRESHOLD 145                         |

| REGISTER 0X186: TCAS IDLE TIME-SLOT FILL DATA                     |

| REGISTER 0X188: TCAS CHANNEL DISABLE REGISTER 147                 |

|                                                                   |

PMC-Sierra, Inc.

PM7340 S/UNI-IMA-8

DATA SHEET PMC-2001723

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

ISSUE 3

| REGISTER 0X1C0 – 0X1CE: TCAS LINK #0 TO LINK #7 CONFIGURATION148   |

|--------------------------------------------------------------------|

| REGISTER 0X200:RIPP CONTROL 149                                    |

| REGISTER 0X202:RIPP INDIRECT MEMORY ACCESS CONTROL 150             |

| REGISTER 0X204 – 0X206:RIPP INDIRECT MEMORY DATA REGISTER<br>ARRAY |

| REGISTER 0X20C: RIPP TIMER TICK CONFIGURATION REGISTER 185         |

| REGISTER 0X20E: GROUP TIMEOUT REGISTER # 1 186                     |

| REGISTER 0X210: GROUP TIMEOUT REGISTER # 2 187                     |

| REGISTER 0X212: TX LINK TIMEOUT REGISTER 188                       |

| REGISTER 0X214: RX LINK TIMEOUT REGISTER                           |

| REGISTER 0X216: RIPP INTERRUPT STATUS REGISTER                     |

| REGISTER 0X218:RIPP GROUP INTERRUPT ENABLE REGISTER                |

| REGISTER 0X21A:RIPP TX LINK INTERRUPT ENABLE REGISTER              |

| REGISTER 0X21C:RIPP RX LINK INTERRUPT ENABLE REGISTER              |

| REGISTER 0X220-22C: RIPP COMMAND REGISTER 194                      |

| REGISTER 0X22E: COMMAND READ DATA CONTROL REGISTER                 |

| REGISTER 0X230: ICP CELL FORWARDING STATUS REGISTER                |

| REGISTER 0X232: ICP CELL FORWARDING CONTROL REGISTER               |

| REGISTER 0X240- 0X29E:RIPP COMMAND DATA REGISTER ARRAY 201         |

| REGISTER 0X2C0- 0X2FE: FORWARDING ICP CELL BUFFER 212              |

| REGISTER 0X300: RDAT INDIRECT MEMORY COMMAND 215                   |

| REGISTER 0X302: RDAT INDIRECT MEMORY ADDRESS                       |

| REGISTER 0X304: RDAT INDIRECT MEMORY DATA LSB 218                  |

|                                                                    |

PM7340 S/UNI-IMA-8

DATA SHEET PMC-2001723

PRELIMINARY

**ISSUE 3**

| REGISTER 0X306: RDAT INDIRECT MEMORY DATA MSB 219           |

|-------------------------------------------------------------|

| REGISTER 0X308: RDAT CONFIGURATION                          |

| REGISTER 0X30A: RECEIVE ATM CONGESTION STATUS 236           |

| REGISTER 0X30E: RECEIVE TC OVERRUN STATUS                   |

| REGISTER 0X310: RDAT MASTER INTERRUPT STATUS                |

| REGISTER 0X312: RECEIVE ATM CONGESTION INTERRUPT ENABLE 239 |

| REGISTER 0X316: RDAT MASTER INTERRUPT ENABLE                |

| REGISTER 0X320: TIMA INDIRECT MEMORY COMMAND 241            |

| REGISTER 0X322: TIMA INDIRECT MEMORY ADDRESS                |

| REGISTER 0X324: TIMA INDIRECT MEMORY DATA LSB 243           |

| REGISTER 0X326: TIMA INDIRECT MEMORY DATA MSB 244           |

| REGISTER 0X328 TX LINK FIFO OVERFLOW STATUS                 |

| REGISTER 0X336 INTERRUPT ENABLE                             |

| REGISTER 0X340: TXIDCC INDIRECT LINK ACCESS                 |

| REGISTER 0X342: TXIDCC INDIRECT LINK DATA REGISTER 1 254    |

| REGISTER 0X350: RXIDCC INDIRECT LINK ACCESS                 |

| REGISTER 0X352: RXIDCC INDIRECT LINK DATA REGISTER 1 256    |

| REGISTER 0X366: DLL CONTROL STATUS                          |

|                                                             |

ISSUE 3

INVERSE MULTIPLEXING OVER ATM

#### 1 DEFINITIONS

#### Table 2Terminology

| Term    | Definition                                                              |

|---------|-------------------------------------------------------------------------|

| Any-PHY | Interoperable version of UTOPIA and UTOPIA L2, with inband addressing.  |

| ATM     | Asynchronous Transfer Mode                                              |

| CDV     | Cell Delay Variation                                                    |

| СТС     | Common Transmit Clock                                                   |

| DLL     | Delay Locked Loop                                                       |

| ECBI    | Enhanced Common Bus Interface (asynchronous register bus and interface) |

| FIFO    | First-In-First-Out                                                      |

| Framed  | Framing information available – may be channelized or unchannelized.    |

| HEC     | Header Error Check                                                      |

| HCS     | Header Check Sequence                                                   |

| ICP     | IMA Control Protocol Cell                                               |

| IDCC    | IMA Data Cell Clock                                                     |

| IDCR    | IMA Data Cell Rate                                                      |

| IFSN    | IMA Frame Sequence Number                                               |

| IMA     | Inverse Multiplexing for ATM                                            |

| ITC     | Independent Transmit Clock                                              |

| LCD     | Loss of Cell Delineation                                                |

| LID     | Link ID                                                                 |

| LSI     | Link Stuff Indication                                                   |

| MIB     | Management Information Base                                             |

| MCFD    | Multi-Channel Cell Based FIFO                                           |

| OAM     | Operation, Administration and Maintenance                               |

PM7340 S/UNI-IMA-8

PMC-2001723

ISSUE 3

|          | 1                                                 |

|----------|---------------------------------------------------|

| OCD      | Out of Cell Delineation                           |

| PISO     | Parallel in Serial Out                            |

| PM       | Plane Management                                  |

| RCAS     | Receive Channel Assigner                          |

| RDAT     | RX IMA Data Processor                             |

| RIPP     | RX IMA Protocol Processor                         |

| RMTS     | RX Master TX Slave                                |

| SIPO     | Serial in Parallel Out                            |

| SPE      | Synchronous Payload Envelope                      |

| ТС       | Transmission Convergence                          |

| TCAS     | Transmit Channel Assigner                         |

| TDM      | Time Division Multiplexing                        |

| TRL      | Timing Reference Link                             |

| TRLCR    | TRL Cell Rate                                     |

| TSB      | Telecom Systems Block                             |

| ТС       | Transmission Convergence                          |

| ΤΙΜΑ     | TX IMA Processor                                  |

| Unframed | No framing information available                  |

| UTOPIA   | Universal Test & Operations PHY Interface for ATM |

DATA SHEET PMC-2001723

PRELIMINARY

ISSUE 3

INVERSE MULTIPLEXING OVER ATM

#### 2 FEATURES

**INVERSE MULTIPLEXING OVER ATM**

The PM7340 S/UNI-IMA-8 is a monolithic integrated circuit that implements the Inverse Multiplexing for ATM (IMA 1.1) protocol with backward compatibility to IMA 1.0 and the Transmission Convergence (TC) layer function. The S/UNI-IMA-8 supports 8 T1, E1 or unchannelized links where each link is dynamically configurable to support either IMA 1.1, backward compatible IMA 1.0, ATM over T1/E1, ATM over fractional T1/E1 or ATM HEC cell delination for unchannelized links Unchannelized links may be used to support applications such as ADSL.

#### **Standards Supported**

- ATM Forum Inverse Multiplexing for ATM Specification Version 1.1, March 1999

- ATM Forum Inverse Multiplexing for ATM Specification Version 1.0 supports the method of reporting Rx cell information as in Appendix C.8 of the ATM Forum Inverse Multiplexing for ATM Specification Version 1.1 for symmetrical configurations with M=128.

- I.432-1 B-ISDN user network interface Physical Layer specification: General characteristics

- I.432-3 B-ISDN user network interface Physical Layer specification: 1544 kbps and 2048 kbps operation

- ATM on Fractional E1/T1, af-phy-0130.00 October, 1999

#### **IMA Features**

- IMA 1.1 protocol including group and link state machines implemented by onchip hardware.

- Supports up to 4 simultaneous IMA groups.

- Each IMA group can support any number of supported links.

- Each link can be programmed for either IMA processing or cell delineation.

- Supports all IMA Group Symmetry modes:

- Symmetrical configuration with symmetrical operation

PMC-Sierra, Inc.

DATA SHEET PMC-2001723

PRELIMINARY

**INVERSE MULTIPLEXING OVER ATM**

ISSUE 3

- Symmetrical configuration with asymmetrical operation.

- Asymmetrical configuration with asymmetrical operation.

- Performs IMA differential delay calculation and synchronization.

- Provides programmable limit on allowable differential delay and minimum number of links per group.

- Supports up to 279 ms (for T1 links) and 226 ms (for E1 links) link-differential delay between links in an IMA group.

- Performs ICP and stuff-cell insertion and removal.

- Supports both Common Transmit Clock (CTC) and Independent Transmit Clock (ITC) transmit ICP stuffing modes.

- Supports IMA frame length (M) equal to 32, 64, 128, or 256.

- Optionally supports the IMA 1.0 method of reporting Rx cell information as defined in appendix C.8 of the ATM Forum Inverse Multiplexing for ATM Specification Version 1.1 for symmetrical configurations with M=128.

- Provides IMA layer statistic counts and alarms for support of IMA Performance and Failure Alarm Monitoring and MIB support.

- Provides per link counters for statistics and performance monitoring:

- ICP Violations

- OIF anomalies

- Rx Link stuff events

- Tx Link stuff events

- User cells

- Filler cells

- Provides per group counters for statistics and performance monitoring:

- User cells received

PMC-2001723

ISSUE 3

- Filler cells received

- User cells transmitted

- Filler cells transmitted

#### TC Features

- Performs cell delineation on all links.

- Performs receive cell Header Error Check (HEC) checking and transmit cell HEC generation.

- Optionally supports receive cell payload unscrambling and transmit cell payload scrambling.

- Provides TC layer statistics counts and alarms for MIB support.

#### Interface Support

- Supports 8 individual serial T1, E1 or unchannelized links via a 2-pin clock and data interface.

- Supports ATM over fractional T1/E1 by providing the capability to select any DS0 timeslots that are active in a link.

- Serial link interface supports both independent transmit clock (ITC) and common transmit clock (CTC) options.

- Interfaces to a 1M x 16 SDRAM for 279 msec of T1, 226 msec of E1 differential delay tolerance through a 16-bit SDRAM interface.

- Provides a 16-bit microprocessor bus interface for configuration and Link and Unit Management.

- ATM receive interface supports 8- and 16-bit UTOPIA L2 or Any-PHY cell interfaces at clock rates up to 52 MHz.

- Any-PHY receive slave appears as a single device. The PHY-ID of each cell is identified in the in-band address.

- UTOPIA L2 receive slave appears as a 31 port multi-PHY.

PMC-Sierra, Inc.

DATA SHEET PMC-2001723

PRELIMINARY

**INVERSE MULTIPLEXING OVER ATM**

ISSUE 3

- UTOPIA L2 receive slave can also appear as a single port with the logical port provided as a prepend or in the HEC/UDF field.

- ATM transmit interface supports 8- and 16-bit UTOPIA L2 and Any-PHY cell interfaces at clock rates up to 52 MHz.

- Each link configured for cell delineation or each IMA group appears as a PHY port on the Any-PHY and UTOPIA L2 bus.

- Any-PHY transmit slave appears as an 8-port multi-PHY. The PHY-ID of each cell is identified in the in-band address.

- UTOPIA L2 transmit slave appears as an 8-port multi-PHY.

- Seamlessly interconnects to PMC-Sierra's PM7326 S/UNI-APEX ATM/Packet Traffic Manager and Switch and PM7324 S/UNI-ATLAS ATM layer device.

#### Loopback and Diagnostic Features

- Supports UTOPIA L2/Any-PHY Loopback (global loopback– where all cells received on the UTOPIA L2 / Any-PHY interface are looped back out)

- Supports Line Side Loopback (global loopback

where all data received on the line side is looped back out)

- Supports the capability to trace ICP cells for any group

#### Software

The S/UNI-IMA device driver, written in ANSI C, provides a well-defined Application Programming Interface (API) for use by application software. Low level utility functions are also provided for diagnostics and debugging purposes. Software wrappers are used for RTOS-related functions making the S/UNI-IMA device driver portable to any Real Time Operating System (RTOS) and hardware environment. The S/UNI-IMA device driver is compatible across the S/UNI-IMA family of devices.

#### Packaging

• Implemented in low power, 0.18 micron, 1.8V CMOS technology with TTL compatible inputs and outputs.

PMC-2001723

ISSUE 3

- Provides a standard 5-pin P1149 JTAG port.

- 324 ball PBGA, 23mm x 23mm

ISSUE 3

INVERSE MULTIPLEXING OVER ATM

#### **3** APPLICATIONS

- Digital Subscriber Line Access Multiplexers (DSLAMs)

- Access Concentrators

- Integrated Access Devices (IAD)

- Wireless Base Transceiver Stations

PMC-2001723

ISSUE 3

INVERSE MULTIPLEXING OVER ATM

#### 4 REFERENCES

- AF-PHY-0086.001 "Inverse Multiplexing for ATM (IMA) Specification Version 1.1", March 1999

- I.432-1 B-ISDN User Network Interface Physical Layer specification: General characteristics

- I.432-3 B-ISDN User Network Interface Physical Layer specification: 1544 kbps and 2048 kbps operation

- G.804 "ATM Cell Mapping into Plesiochronous Digital Hierarchy (PDH)"

- AF-PHY-0016.000 "ATM Forum DS1 Physical Layer Specification"

- AF-PHY-0064.000 "ATM Forum E1 Physical Interface"

- ATM Forum, UTOPIA, an ATM-PHY Layer Specification, Level 2, V. 1.0, Foster City, CA USA, June 1995.

PMC PMC-Sierra, Inc.

DATA SHEET PMC-2001723

PRELIMINARY

**INVERSE MULTIPLEXING OVER ATM**

ISSUE 3

#### 5 APPLICATION EXAMPLES

#### 5.1 Multi-Service Access – IADs, Access Concentrators

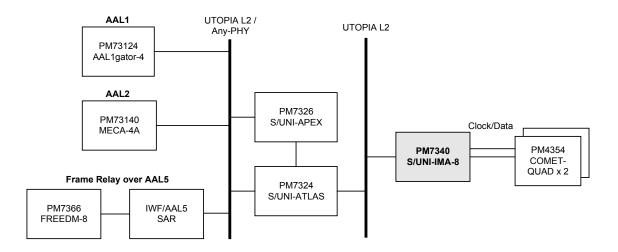

Multi-Service access equipment such as Integrated Access Devices (IADs) and Access Concentrators consolidate voice, data, Internet, and video wide-area network services over ATM unifying the functions of many different types of equipment including CSUs, DSUs, multiplexers and FRADs. Figure 1 illustrates an example of a multi-service access box using IMA over multiple T1/E1 lines for WAN access.

#### Figure 1 - Multi-Service Access – IADs and Access Concentrators.

On the lineside, the S/UNI-IMA-8 interfaces seamlessly to standard devices such as the PM4354 COMET-QUAD T1/E1 Framer plus LIU.

#### 5.2 Remote DSLAM WAN Uplink

IMA is ideally suited for remote DSLAM applications for several reasons. Firstly, remote DSLAMs are physically located at remote sites of which many are served by T1 or E1 lines. Secondly, the benefits of ATM have resulted in its almost exclusive use in DSLAMs. Coupled with ATM, DSLAMs enable service providers to utilize the bandwidth of the T1/E1 infrastructure for delivering integrated services such as high-speed Internet access and real-time voice and video. ATM over T1/E1 is a suitable DSLAM WAN uplink technology and IMA, due to its

PRELIMINARY INVERSE MULTIPLEXING OVER ATM DATA SHEET PMC-2001723 ISSUE 3 INVERSE MULTIPLEXING OVER ATM

benefits of higher bandwidth, statistical gain and fault tolerance, is even more suitable.

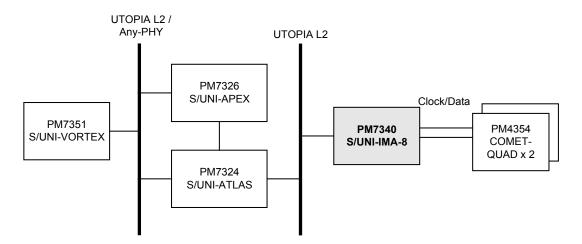

Figure 2 illustrates an example of the S/UNI-IMA-8 in a remote DSLAM WAN uplink application.

## Figure 2 -S/UNI-IMA-8 in a Remote DSLAM WAN Uplink Application.

ISSUE 3

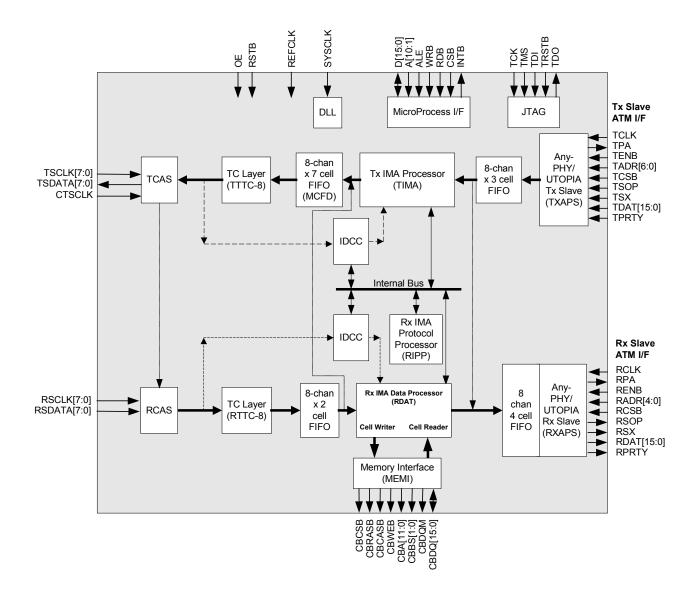

#### 6 BLOCK DIAGRAM

IMA-8 Block Diagram

#### Figure 3 - S/UNI-IMA-8 Block Diagram

PM7340 S/UNI-IMA-8

PRELIMINARY INVERSE MULTIPLEXING OVER ATM DATA SHEET

PMC-2001723

ISSUE 3

INVERSE MULTIPLEXING OVER ATM

#### 7 DESCRIPTION

The PM7340 S/UNI-IMA-8 is a monolithic integrated circuit that implements the Inverse Multiplexing for ATM (IMA 1.1) protocol with backward compatibility to IMA 1.0 and the Transmission Convergence (TC) layer function.

PMC PMC-Sierra, Inc.

IMA is a protocol designed to combine the transport bandwidth of multiple links into a single logical link. The logical link is called a group. The S/UNI-IMA-8 can support up to 4 independent groups with each group capable of supporting from 1 to 8 links. All links within an IMA group must be at the same nominal rate, however the link rates within a group can be different across groups. The S/UNI-IMA-8 can be programmed on a per link basis for cell delination or IMA.

The S/UNI-IMA-8 supports 8 T1, E1 or unchannelized links where each link is dynamically configurable to support either IMA 1.1, backward compatible IMA 1.0, ATM over T1/E1, ATM over fractional T1/E1 or ATM HEC cell delination for unchannelized links. Unchannelized links may be used to support applications such as ADSL.

The S/UNI-IMA-8 supports a clock and data interface where eight 2-pin serial clock and data interfaces are provided. Each clock and data interface can be configured to simultaneously support combinations of either T1, E1, or unchannelized links. Unchannelized links may be used to support applications such as ADSL. Additionally, for cell delineation only, ATM over fractional T1/E1 is supported by allowing individual DS0 timeslots to be configured as active or inactive.

In the transmit direction, the S/UNI-IMA-8 accepts cells from the Any-PHY/UTOPIA interface. As per the IMA specification, the cells, destined for a group, are distributed in a round-robin fashion to the links within the group, adding IMA Control Protocol (ICP) cells, filler cells, and stuff cells as needed. The ICP cells convey state information to the far end and are used to format an IMA Frame. The IMA Frame is used as a mechanism to synchronize the links at the far end. Cell rate decoupling is performed at the IMA sub-layer via filler cells. Filler cells are used instead of physical layer cells for cell rate decoupling, thus a continuous stream of cells is sent to the TC layer. The stuff cells are used to maintain synchronization between links in a group by absorbing the rate differential that exists when links are running at slightly different rates.

The data from the IMA sub-layer is passed on to the TC layer. In the TC layer, the HEC is calculated and inserted into the cell headers; optional scrambling of the

PMC-Sierra, Inc.

PM7340 S/UNI-IMA-8

PRELIMINARY INVERSE MULTIPLEXING OVER ATM DATA SHEET

PMC-2001723

ISSUE 3

INVERSE MULTIPLEXING OVER ATM

payload is performed. The cell stream is then mapped into a T1 or E1 payload with zeros inserted for the framing and overhead bits or bytes. If using an unchannelized clock and data interface, the data is not mapped into the T1/E1 payload but instead is transmitted one bit for each provided clock pulse.

The links are then transmitted via the serial interfaces. The clock is provided from each serial clock pin. An optional common-clock mode is provided to enable all links to run from the same clock. If using an unchannelized clock and data interface, the data is received one bit for each provided clock pulse.

On the receive side, data is received from the clock/data interface. The timeslots are mapped to logical channels called links. The TC layer searches for cell delineation as per the procedures outlined in ITU-T Recommendation I.432.1. Once cell delineation is obtained, the payload is optionally descrambled and the cells are passed to the IMA sub-layer. The TC layer provides counts of errored headers as well as OCD and LCD error interrupts.

The receive IMA sublayer performs IMA-frame delineation and stuff-cell removal. Based upon the ICP cell information, the S/UNI-IMA-8 determines the differential delay between the links within a group and applies the link and group state machine logic to coordinate the activation and deactivation of groups and links with the far end. As cells are received, they are stored in an external FIFO structure. This structure is based upon the IMA frame boundaries and the IMA frame sequence number. When links or groups are determined to be active by the link and group state machines, the data is played out to the Any-PHY/UTOPIA interface at a constant rate to mimic the existence of a single higher bandwidth physical link.

Once a group of links is established, links can be dynamically added or deleted from the group. Under management control, the S/UNI-IMA-8 will perform all necessary steps to add or delete links from previously established groups.

In order to aid with diagnostics, a line side loopback and a UTOPIA side loopback are provided. Also, an ICP cell trace feature is provided. When the ICP cell trace has been enabled for a group, the S/UNI-IMA-8 will place those ICP cells where a SCCI field change is detected into a buffer that is accessible to the microprocessor.

DATA SHEET PMC-2001723

PRELIMINARY

ISSUE 3

#### 8 PIN DIAGRAM

**INVERSE MULTIPLEXING OVER ATM**

The S/UNI-IMA-8 is packaged in a 324-pin PBGA package that has a body size of 23mm by 23mm and a ball pitch of 1mm.

Figure 4 - S/UNI-IMA Preliminary Pinout (Bottom View)

|    | 22               | 21               | 20               | 19               | 18      | 17      | 16      | 15      | 14       | 13       | 12      | 11     | 10     | 9      | 8       | 7             | 6      | 5   | 4             | 3             | 2             | 1             |    |

|----|------------------|------------------|------------------|------------------|---------|---------|---------|---------|----------|----------|---------|--------|--------|--------|---------|---------------|--------|-----|---------------|---------------|---------------|---------------|----|

| A  | VDD              | TMS              | NC               | NC               | VDD     | D[11]   | D[7]    | D[5]    | D[3]     | A[10]    | VSS     | A[5]   | A[2]   | RDB    | SCANENB | VDDI          | NC     | NC  | NC            | NC            | NC            | NC            | А  |

| в  | TDAT[0]          | тск              | TDI              | TDO              | D[15]   | D[14]   | D[10]   | D[6]    | D[4]     | D[0]     | A[7]    | A[4]   | A[1]   | CSB    | NC      | NC            | NC     | NC  | vss           | NC            | NC            | NC            | в  |

| с  | TDAT[4]          | TDAT[1]          | TDAT[6]          | VSS              | TRSTB   | VSS     | D[12]   | D[9]    | VDDI     | D[1]     | A[8]    | VSS    | ALE    | INTB   | NC      | NC            | NC     | NC  | NC            | VSS           | NC            | NC            | с  |

| D  | VSS              | TDAT[2]          | TPRTY            | VSS              | D[13]   | D[8]    | VDD     | VSS     | D[2]     | A[9]     | A[6]    | VDD    | A[3]   | WRB    | VSS     | SCANMO<br>DEB | NC     | VSS | VDD           | TSCLK[6]      | NC            | NC            | D  |

| E  | TDAT[7]          | TDAT[5]          | TDAT[3]          | TCLK             |         |         |         |         |          |          |         |        |        |        |         |               |        |     | VDDI          | NC            | NC            | VDD           | E  |

| F  | TDAT[10]         | TDAT[8]          | VDD              | TDAT[13]         |         |         |         |         |          |          |         |        |        |        |         |               |        |     | TSCLK[2]      | NC            | TSCLK[7]      | VSS           | F  |

| G  | TDAT[12]         | TDAT[11]         | TDAT[9]          | vss              |         |         |         |         |          |          |         |        |        |        |         |               |        |     | vss           | TSCLK[5]      | TSCLK[4]      | TSCLK[3]      | G  |

| н  | тѕх              | TDAT[15]         | TDAT[14]         | TSOP             |         |         |         |         |          |          |         |        |        |        |         |               |        |     | TSDATA[<br>7] | TSCLK[0]      | CTSCLK        | TSCLK[1]      | н  |

| J  | TADR_SC<br>AN[1] | TADR_SC<br>AN[0] | TCSB             | TADR_SC<br>AN[2] |         |         |         |         | VSS      | VSS      | VSS     | VSS    | VSS    | VSS    |         |               |        |     | TSDATA[<br>3] | TSDATA[<br>6] | TSDATA[<br>5] | TSDATA[<br>4] | J  |

| к  | TADR_SC<br>AN[5] | TADR_SC<br>AN[4] | TADR_SC<br>AN[3] | TADR_SC<br>AN[6] |         |         |         |         | VSS      | VSS      | VSS     | VSS    | VSS    | VSS    |         |               |        |     | TSDATA[<br>0] | VSS           | TSDATA[<br>2] | TSDATA[<br>1] | к  |

| L  | TPA              | VSS              | TENB             | VDD              |         |         |         |         | VSS      | VSS      | VSS     | VSS    | VSS    | VSS    |         |               |        |     | NC            | NC            | NC            | VDD           | L  |

| м  | RPRTY            | VDDI             | RDAT[0]          | vss              |         |         |         |         | VSS      | VSS      | VSS     | VSS    | VSS    | VSS    |         |               |        |     | vss           | NC            | NC            | NC            | м  |

| N  | RDAT[2]          | RDAT[3]          | RDAT[4]          | RDAT[1]          |         |         |         |         | VSS      | VSS      | VSS     | VSS    | VSS    | VSS    |         |               |        |     | NC            | NC            | REFCLK        | NC            | N  |

| Ρ  | RDAT[6]          | RDAT[7]          | RDAT[8]          | RDAT[5]          |         |         |         |         | VSS      | VSS      | VSS     | VSS    | VSS    | VSS    |         |               |        |     | NC            | RSCLK[1]      | RSCLK[0]      | NC            | Р  |

| R  | RDAT[11]         | VDD              | RDAT[12]         | RDAT[9]          |         |         |         |         |          |          |         |        |        |        |         |               |        |     | VDD           | RSDATA[<br>1] | RSDATA[<br>0] | RSCLK[3]      | R  |

| т  | RDAT[14]         | RCLK             | RSX              | RDAT[10]         |         |         |         |         |          |          |         |        |        |        |         |               |        |     | RSCLK[2]      | RSCLK[4]      | VSS           | RSDATA[<br>2] | т  |

| U  | RDAT[15]         | RCSB             | VDDI             | RDAT[13]         |         |         |         |         |          |          |         |        |        |        |         |               |        |     | VDDI          | RSDATA[<br>4] | RSCLK[6]      | RSDATA[<br>3] | U  |

| v  | vss              | vss              | RADR[2]          | RSOP             |         |         |         |         |          |          |         |        |        |        |         |               |        |     | RSCLK[5]      | RSDATA[<br>7] | VDD           | RSCLK[7]      | v  |

| w  | RADR[0]          | VSS              | RENB             | NC               | CBDQ[2] | VDDI    | VDD     | CBDQ[8] | CBDQ[11] | CBDQ[15] | CBBS[1] | CBA[0] | CBA[2] | CBA[6] | VDD     | CBA[10]       | CBCASB | NC  | VDD           | NC            | NC            | RSDATA[<br>5] | w  |

| Y  | RADR[1]          | RADR[3]          | VDD              | NC               | VDD     | VSS     | CBDQ[3] | CBDQ[6] | VSS      | CBDQ(12) | CBDQM   | VSS    | CBA[5] | CBA[9] | CBIVEB  | SYSCLK        | NC     | VDD | NC            | NC            | NC            | RSDATA[<br>6] | Y  |

| AA | RADR[4]          | NC               | NC               | NC               | RSTB    | CBDQ[1] | CBDQ[4] | CBDQ[7] | CBDQ(9)  | CBDQ[13] | CBBS[0] | VDDI   | CBA[4] | CBA[8] | CBA[11] | VSS           | NC     | NC  | NC            | VSS           | VSS           | NC            | АА |

| AB | RPA              | VSS              | NC               | OE               | CBDQ(0) | VDD     | CBDQ[5] | VSS     | CBDQ(10) | CBDQ(14) | vss     | CBA[1] | CBA[3] | CBA[7] | vss     | CBRASB        | CBCSB  | NC  | NC            | NC            | NC            | NC            | AB |

|    | 22               | 21               | 20               | 19               | 18      | 17      | 16      | 15      | 14       | 13       | 12      | 11     | 10     | 9      | 8       | 7             | 6      | 5   | 4             | 3             | 2             | 1             |    |

DATA SHEET PMC-2001723

PRELIMINARY

ISSUE 3

INVERSE MULTIPLEXING OVER ATM

#### 9 PIN DESCRIPTION

**INVERSE MULTIPLEXING OVER ATM**

## Receive Slave ATM Interface (Any-PHY mode) (28 Signals)

| Pin Name | Туре               | Pin<br>No. | Function                                                                                                                                                                                                      |

|----------|--------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK     | Input              | T21        | The <b>Receive Clock</b> (RCLK) signal is used to transfer data blocks from the S/UNI-IMA-8 across the receive Any-PHY interface.                                                                             |

|          |                    |            | The RPA, RSOP, RSX, RDAT[15:0], and RPRTY outputs are updated on the rising edge of RCLK. The RENB, RADR[4:0], and RCSB inputs are sampled on the rising edge of RCLK.                                        |

|          |                    |            | The RCLK input must cycle at a 52 MHz or lower instantaneous rate.                                                                                                                                            |

| RPA      | Tristate<br>Output | AB22       | The <b>Receive Packet Available</b> (RPA) is an active high signal that indicates whether at least one cell is queued for transfer.                                                                           |

|          |                    |            | The S/UNI-IMA-8 device drives the RPA with the cell<br>availability status two RCLK cycles after RADR[4:0]<br>matches the S/UNI IMA's device address. The RPA<br>output is high-impedance at all other times. |

|          |                    |            | The RPA output is updated on the rising edge of RCLK.                                                                                                                                                         |

| RENB     | Input              | W20        | The <b>Receive Enable Bar</b> (RENB) is an active low signal used to initiate the transfer of cells from the S/UNI-IMA-8 to an ATM layer component, such as a traffic management device.                      |

|          |                    |            | The RENB input is sampled on the rising edge of RCLK.                                                                                                                                                         |

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM DATA SHEET

PMC-2001723

PM7340 S/UNI-IMA-8

ISSUE 3

| Pin Name                                            | Туре   | Pin<br>No.                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------|--------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RADR[4]<br>RADR[3]<br>RADR[2]<br>RADR[1]<br>RADR[0] | Input  | AA22<br>Y21<br>V20<br>Y22<br>W22 | The <b>Receive Address</b> (RADR[4:0]) signals are<br>used to address the S/UNI-IMA-8 device for the<br>purposes of polling and selection for cell transfer.<br>The RADR[4:0] signals are valid only when the<br>RCSB signal is sampled active in the following<br>RCLK cycle.                                                                                                                                                                                                                                                    |

|                                                     |        |                                  | The RADR[4:0] input bus is sampled on the rising edge of RCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RCSB                                                | Input  | U21                              | The <b>Receive Chip Select</b> (RCSB) is an active low<br>signal that is used to select the S/UNI-IMA-8 receive<br>interface. When the RCSB is sampled low, it<br>indicates that the RADR[4:0] sampled at the<br>previous clock is a valid address. If the RCSB is<br>sampled high, the device is not selected and the<br>RADR[4:0] sampled on the previous cycle is not a<br>valid address and is ignored. When sufficient<br>address space is provided by RADR[4:0] for all<br>devices on the bus, this signal may be tied low. |

|                                                     |        |                                  | The RCSB input is sampled on the rising edge of RCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RSOP                                                | Output | V19                              | The <b>Receive Start of Packet</b> (RSOP) is an active<br>high signal that marks the start of the cell on the<br>RDAT[15:0] bus. When RSOP is active, the first<br>word of the cell is present on the RDAT[15:0] bus.                                                                                                                                                                                                                                                                                                             |

|                                                     |        |                                  | The RSOP output is updated on the rising edge of RCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RSX                                                 | Output | T20                              | The <b>Receive Start of Transfer</b> (RSX) signal is an active high signal that marks the first cycle of a data block transfer on the RDAT[15:0] bus. When the RSX signal is active, the coinciding data on the RDAT[15:0] bus represents the in-band PHY address.                                                                                                                                                                                                                                                                |

|                                                     |        |                                  | The RSX output is updated on the rising edge of RCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM DATA SHEET

PM7340 S/UNI-IMA-8

ISSUE 3

INVERSE MULTIPLEXING OVER ATM

| Pin Name                                                                                                                                                                                       | Туре   | Pin<br>No.                                                                                                   | Function                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDAT[15]<br>RDAT[14]<br>RDAT[13]<br>RDAT[12]<br>RDAT[12]<br>RDAT[10]<br>RDAT[10]<br>RDAT[9]<br>RDAT[9]<br>RDAT[8]<br>RDAT[7]<br>RDAT[6]<br>RDAT[6]<br>RDAT[4]<br>RDAT[1]<br>RDAT[1]<br>RDAT[0] | Output | U22<br>T22<br>U19<br>R20<br>R22<br>T19<br>R19<br>P20<br>P21<br>P22<br>P19<br>N20<br>N21<br>N22<br>N19<br>M20 | The <b>Receive Cell Data</b> (RDAT[15:0]) signals carry<br>the ATM cell words that have been read from the<br>S/UNI-IMA-8 internal cell buffers. When this<br>interface is operating in 8-bit mode, the data is<br>carried on RDAT[7:0].<br>The RDAT[15:0] output bus is updated on the rising<br>edge of RCLK. |

| RPRTY                                                                                                                                                                                          | Output | M22                                                                                                          | The <b>Receive Parity</b> (RPRTY) signal provides the parity (programmable for odd or even parity) of the RDAT[15:0] bus. When the interface is operating in 8-bit mode, the parity is calculated over RDAT[7:0]                                                                                                |

|                                                                                                                                                                                                |        |                                                                                                              | The RPRTY output is updated on the rising edge of RCLK.                                                                                                                                                                                                                                                         |

## 9.1 Receive Slave ATM Interface (UTOPIA L2 mode) (26 Signals)

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                   |

|----------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK     | Input | T21        | The <b>Receive Clock</b> (RCLK) signal is used to transfer data blocks from the S/UNI-IMA-8 across the receive UTOPIA L2 interface.                        |

|          |       |            | The RCA, RSOC, RDAT[15:0], and RPRTY outputs are updated on the rising edge of RCLK. The RENB and RADR[4:0] inputs are sampled on the rising edge of RCLK. |

|          |       |            | The RCLK input must cycle at a 52 MHz or lower instantaneous rate.                                                                                         |

PM7340 S/UNI-IMA-8

PMC-2001723

ISSUE 3

| Pin Name                      | Туре               | Pin<br>No.         | Function                                                                                                                                                                                                         |

|-------------------------------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCA                           | Tristate<br>Output | AB22               | The <b>Receive Cell Available</b> (RCA) is an active high signal that, when polled using the RADR[4:0] signals, indicates if at least one cell is queued for transfer on the selected logical channel FIFO.      |

|                               |                    |                    | The S/UNI-IMA-8 device drives RCA with the cell<br>availability status for the polled port one RCLK cycle<br>after a valid RADR[4:0] address is sampled. The<br>RCA output is high-impedance at all other times. |

|                               |                    |                    | The RCA output is updated on the rising edge of RCLK.                                                                                                                                                            |

| RENB                          | Input              | W20                | The <b>Receive Enable Bar</b> (RENB) is an active low signal used to initiate the transfer of cells from the S/UNI-IMA-8 to an ATM-layer component, such as a traffic management device.                         |

|                               |                    |                    | The RENB input is sampled on the rising edge of RCLK.                                                                                                                                                            |

| RADR[4]<br>RADR[3]<br>RADR[2] | Input              | AA22<br>Y21<br>V20 | The <b>Receive Address</b> (RADR[4:0]) signals are used to address the S/UNI-IMA-8 device for the purposes of polling and selecting for cell transfer.                                                           |

| RADR[1]<br>RADR[0]            |                    | Y22<br>W22         | The RADR[4:0] input bus is sampled on the rising edge of RCLK.                                                                                                                                                   |

| RSOC                          | Output             | V19                | The <b>Receive Start of Cell</b> (RSOC) is an active high signal that marks the first word of the cell on the RDAT[15:0] bus.                                                                                    |

|                               |                    |                    | The RSOC output is updated on the rising edge of RCLK.                                                                                                                                                           |

INVERSE MULTIPLEXING OVER ATM DATA SHEET

PM7340 S/UNI-IMA-8

ISSUE 3

| Pin Name                                                                                                                                                                                       | Туре   | Pin<br>No.                                                                                                   | Function                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDAT[15]<br>RDAT[14]<br>RDAT[13]<br>RDAT[12]<br>RDAT[12]<br>RDAT[10]<br>RDAT[10]<br>RDAT[9]<br>RDAT[9]<br>RDAT[8]<br>RDAT[7]<br>RDAT[6]<br>RDAT[6]<br>RDAT[4]<br>RDAT[1]<br>RDAT[1]<br>RDAT[0] | Output | U22<br>T22<br>U19<br>R20<br>R22<br>T19<br>R19<br>P20<br>P21<br>P22<br>P19<br>N20<br>N21<br>N22<br>N19<br>M20 | The <b>Receive Cell Data</b> (RDAT[15:0]) signals carry<br>the ATM cell words that have been read from the<br>S/UNI-IMA-8 internal cell buffers. When this<br>interface is operating in 8-bit mode, the data is<br>carried on RDAT[7:0].<br>The RDAT[15:0] output bus is updated on the rising<br>edge of RCLK. |

| RPRTY                                                                                                                                                                                          | Output | M22                                                                                                          | The <b>Receive Parity</b> (RPRTY) signal provides the parity (programmable for odd or even parity) of the RDAT[15:0] bus. When the interface is operating in 8-bit mode, the parity is calculated over RDAT[7:0]                                                                                                |

|                                                                                                                                                                                                |        |                                                                                                              | The RPRTY output is updated on the rising edge of RCLK.                                                                                                                                                                                                                                                         |

PMC-2001723

**INVERSE MULTIPLEXING OVER ATM**

#### Pin Name Type Pin Function No. TCLK E19 Input The **Transmit Clock** (TCLK) signal is used to transfer cells across the ANY-PHY interface to the internal downstream cell buffers. The TPA output is updated on the rising edge of TCLK. The TENB. TSX, TSOP, TDAT[15:0], TPRTY, TADR[6:0], and TCSB inputs are sampled on the rising edge of TCLK. The TCLK input must cycle at a 52 MHz or lower instantaneous rate. TPA Tristate 122 The **Transmit Packet Available** (TPA) is an active high signal that indicates the availability of space in Output the selected logical channel FIFO when polled using the TADR[6:0] signals. The S/UNI-IMA-8 device drives TPA with the cell availability status of the polled port two TCLK cycles after TADR[6:0] matches the S/UNI IMA's device address. The TPA output is high-impedance at all other times. The TPA output is updated on the rising edge of TCLK. TENB Input L20 The **Transmit enable bar** (TENB) is an active low signal that is used to indicate cell transfers to the internal cell buffers. The TENB input is sampled on the rising edge of TCLK.

# 9.2 Transmit Slave Interface (ANY-PHY mode) (30 Signals)

**ISSUE 3**

INVERSE MULTIPLEXING OVER ATM DATA SHEET

PMC-Sierra, Inc.

PM7340 S/UNI-IMA-8

ISSUE 3

| Pin Name                                            | Туре  | Pin<br>No.                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------|-------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TADR[6]<br>TADR[5]<br>TADR[4]<br>TADR[3]<br>TADR[2] | Input | Input K19<br>K22<br>K21<br>K20<br>J19 | The <b>Transmit Address</b> (TADR[6:0]) signals are<br>used to address logical channels for the purpose of<br>polling and device selection. The TADR[6:0] signals<br>are valid only when the TCSB signal is sampled<br>active in the following TCLK cycle.                                                                                                                                                                                                                                                                          |

| TADR[1]<br>TADR[0]                                  |       | J22<br>J21                            | The TADR[6:0] input bus is sampled on the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TCSB                                                | Input | J20                                   | The <b>Transmit Chip Select</b> (TCSB) is an active low<br>signal that is used to select the S/UNI-IMA-8<br>transmit interface. When the TCSB is sampled low, it<br>indicates that the TADR[6:0] sampled at the<br>previous clock is a valid address. If the TCSB is<br>sampled high, the device is not selected and the<br>TADR[6:0] sampled on the previous cycle is not a<br>valid address and is ignored. When sufficient<br>address space is provided by TADR[6:0] for all<br>devices on the bus, this signal may be tied low. |

|                                                     |       |                                       | The TCSB is asserted low one cycle after a valid address is present on the TADR[6:0] signals.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                     |       |                                       | The TCSB input is sampled on the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TSOP                                                | Input | H19                                   | The <b>Transmit Start of Packet</b> (TSOP) is an active<br>high signal that marks the start of the cell on the<br>TDAT[15:0] bus. When TSOP is active, the first word<br>of the cell is present on the TDAT[15:0] bus.                                                                                                                                                                                                                                                                                                              |

|                                                     |       |                                       | The TSOP output is sampled on the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |