T-77-29

## **DSPG7001**

Advance Information

December 1989, Rev. 1.1

## Variable Speed & IC Repeat Speech Processor

## (Low Power Applications)

#### **GENERAL DESCRIPTION**

The DSPG7001 Variable Speed & IC Repeat Speech Processor chip set performs the following functions:

- Time Scale Modification of speech signals for variable speed speech playback applications.

- High quality digital speech compression for IC repeat applications.

- Voice activated recording.

This chip set is ideal for dictation, transcription and other speech reproduction applications. The DSPG7001 utilizes the proprietary FLEXISPEECH digital signal processing Time Scale Modification (TSM) technology to increase (up to 200%) or decrease (down to 50%) the playback speed of speech signals. This processing does not affect the quality of the reproduced speech, nor its natural sound, intonation or the speaker identity. When used in conjunction with variable speed tape recorders, the chip set derives synchronization signals from the recorder mechanism.

The DSPG7001 incorporates a high quality speech compression technique, capable of digitally coding speech signals at rates of 13 kbps. This allows efficient storage of a speech segment for the 'IC repeat' function.

The DSPG7001 incorporates also a highly reliable 'speech specific' speech detector that supports voice activated recording for tape recorders.

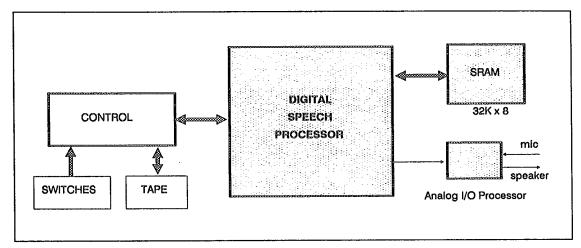

The DSPG7001 is specially designed for low power, low voltage applications. The chip set comprises of a digital speech processor, a CODEC and a 32K\*8 SRAM.

#### **FEATURES**

- High quality real-time speech restoration for variable-speed speech playback (0.5 to 2.0)

- High resolution control of time scale factor (not limited to multiples of the pitch period)

- Natural sounding speech output for any speaker: male, female, children

- Voice activated recording

- High quality, low rate digital speech compression

- Robust operation under noisy conditions

- Simple host interface

- Low power, CMOS technology

The DSP Group, Inc., 1900 Powell Street, Suite 1120, Emeryville, CA 94608 Tel: (415) 655-7311 Fax: (415) 655-7537

## **DSPG7001**

DSPG7001 Block Diagram.

# **Specifications**

AUDIO BANDWIDTH: 0-3200 Hz

AUDIO LEVELS: 100mV-2V PTP

TIME SCALE MODIFICATION FACTORS (default):

Compression ... 0.5, 0.625, 0.75, 0.875

Original ... 1

Expansion ... 1.125, 1.25, 1.5, 1.75, 2

TAPE SPEED CONTROL: Automatic (pulse rate modulated) or via host command

THROUGHPUT DELAY: 16 milliseconds

INTERFACE LEVEL: TTL

LOW POWER: +3VDC operation

IC Repeat length:

up to 16 seconds

# Physical Description

- DSPG7001-11 Digital Signal Processor (68 pin PLCC) 1ea.

- DSPG7000-25 Analog I/O Processor (24 pin PLCC) 1 ea.

- DSPG7001-12 256 Kbit SRAM (28 pin FlatPack) 1 ea.

Note: Specifications are subject to change without prior notice.

December 1989