Issued March 1983 4333

# High speed opto-isolators 6N137 and Dual 6N137

T-41-83

Stock numbers 304 – 273 and 302 – 104

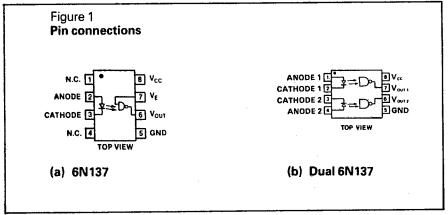

The 6N137 consists of a Ga As P input diode optically coupled to a unique integrated detector comprising a photodiode, high gain linear amplifier and Schottky clamped open collector output transistor. The circuit is temperature, current and voltage compensated.

The internal isolator design provides maximum DC and AC circuit isolation between input and output whilst achieving LSTTL/TTL circuit compatibility. The isolator operational parameters are guaranteed from 0°C to 70°C, such that a minimum input current of 5mA will sink an eight gate fan-out (13mA) at the output with 5 volt V∞ applied to the detector. The isolation and coupling is achieved with a typical propagation delay of 45ns. The enable input provides gating of the detector with input sinking and sourcing requirements compatible with LSTTL/TTL interfacing and a propagation delay of 25ns typical (single version only).

The 6N137 can be used in high speed digital interfacing applications where common mode signals must be rejected, such as for a line receiver and digital programming of floating power supplies, motors, and other machine control systems. The elimination of ground loops can be accomplished in system interfaces such as between a computer and a peripheral memory, printer, controller, etc.

The Dual 6N137 is equivalent to the HCPL-2630.

#### **Features**

- ◆LSTTL/TTL compatible: 5V supply

- Ultra high speed typically 10M bit/s (NRZ)

- Low input current required

- High common mode rejection

- Guaranteed performance over temperature range

- •3000 Vdc withstand test voltage

- Enable input available (single type only)

#### Absolute maximum ratings

(No derating required up to 70°C). Where two figures are given (e.g. 20/15) the first is for single version, the second for dual version.

| Operating Voltage          |                   |                      |

|----------------------------|-------------------|----------------------|

| Range                      | 4.5 to 5.5V (7V   | 1 Minute Maximum)    |

|                            |                   | 55°C to + 125°C      |

| <b>Operating Tempera</b>   | iture             | 0°C to + 70°C        |

| Lead Solder Tempe          | rature            | 260°C for 10s        |

| (1.6mm below se            | ating plane)      |                      |

| <b>Peak Forward Input</b>  | Current _40/30m   | A (≤ 1msec duration) |

| Average Forward In         | put Current       | 20/15mA              |

| Reverse Input Volta        | ge                | 5V                   |

|                            |                   | 5.5V                 |

| (Not to exceed Vo          |                   |                      |

| Output Current             | ·                 | 50/16mA              |

| <b>Output Collector Po</b> | wer Dissipation _ | 85/60mW              |

| Output Voltage             |                   | 7V                   |

## Electrical characteristics T<sub>A</sub> = 0 to + 70°C, V<sub>cc</sub> = 4.5 to 5.5V unless otherwise stated

| Parameter                                  | Symbol           | Test Conditions                                                                        | Min. | Тур. | Max.            | Units | Not |

|--------------------------------------------|------------------|----------------------------------------------------------------------------------------|------|------|-----------------|-------|-----|

| Input Current, Low Level                   | IFL              |                                                                                        | 0    |      | 250             | μΑ    |     |

| Input Current, High Level                  | I <sub>FH</sub>  |                                                                                        | 6.3  |      | 15              | mA    | 5   |

| High Level Output Current                  | Юн               | $V_{CC} = 5.5V, V_{O} = 5.5V,$ $I_{F} = 250\mu A, V_{E} = 2.0V$                        |      | 50   | 250             | μΑ    |     |

| Low Level Output Voltage                   | V <sub>OL</sub>  | $V_{CC} = 5.5V, I_F = 5mA, V_{EH} = 2.0V I_{OL}(Sinking) = 13mA$                       |      | 0.5  | 0.6             | V     |     |

| High Level Enable Voltage                  | V <sub>EH</sub>  |                                                                                        | 2.0  |      | V <sub>CC</sub> | V     |     |

| High Level Enable Current                  | I <sub>EH</sub>  | $V_{CC} = 5.5V, V_{E} = 2.0V$                                                          |      | -1.0 |                 | mA    |     |

| Low Level Enable Voltage<br>(Output High)  | V <sub>EL</sub>  |                                                                                        | 0    |      | 0.8             | V     |     |

| Low Level Enable Current                   | I <sub>EL</sub>  | $V_{CC} = 5.5V, V_{E} = 0.5V$                                                          |      | -1.6 | -2.0            | mA    |     |

| Hìgh Level Supply Current<br>(per channel) | ССН              | $V_{CC} = 5.5V, I_F = 0$<br>$V_E = 0.5V$                                               |      | 7    | 15              | mA    |     |

| Low Level Supply Current (per channel)     | CCL              | $V_{CC} = 5.5V, I_F = 10mA$<br>$V_E = 0.5V$                                            |      | 13   | 18              | mA    |     |

| Input-Output Insulation<br>Leakage Current | I <sub>1-0</sub> | Relative Humidity = 45%<br>T <sub>A</sub> = 25°C, t = 5s<br>V <sub>I-0</sub> = 3000Vdc |      |      | 1.0             | μΑ    | 1   |

| Resistance (Input-Output)                  | R <sub>I-0</sub> | V <sub>I-0</sub> = 500V, T <sub>A</sub> = 25°C                                         |      | 1012 |                 | Ω     | 1   |

| Capacitance (Input-Output)                 | C <sub>I-0</sub> | f = 1MHz, T <sub>A</sub> = 25°C                                                        |      | 0.6  |                 | рF    | 1   |

| Input Forward Voltage                      | V <sub>F</sub>   | I <sub>F</sub> = 10mA, T <sub>A</sub> =25°C                                            |      | 1.5  | 1.75            | V     | 2   |

| Input Reverse Breakdown<br>Voltage         | BV <sub>R</sub>  | $I_R = 10\mu A, T_A = 25^{\circ}C$                                                     | 5    |      |                 | V     |     |

| Input Capacitance                          | C <sub>IN</sub>  | $V_F = 0, f = 1MHz$                                                                    |      | 60   |                 | pF    |     |

| Current Transfer Ratio                     | CTR              | $I_F = 5.0 \text{mA}, R_L = 100 \Omega$                                                |      | 700  |                 | %     | 3   |

| Fan Out (TTL Load)                         | N                | V <sub>CC</sub> = 5.5V                                                                 |      |      | 8               |       |     |

<sup>\*\*</sup>All typical values are at  $V_{cc} = 5V$ ,  $T_A = 25^{\circ}C$

### 4333

# **Switching characteristics** at $T_A = 25^{\circ}C$ , $V_{CC} = 5V$

| Parameter                                                                   | Symbol                         | Test Conditions                                                                      | Min. | Тур.  | Max. | Units | Note |

|-----------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------|------|-------|------|-------|------|

| Propagation Delay Time to<br>High Output Level                              | t <sub>PLH</sub>               | $R_L = 350\Omega$ , $C_L = 15pF$ , $I_F = 7.5mA$                                     |      | 45    | 75   | ns    |      |

| Propagation Delay Time to<br>Low Output Level                               | t <sub>PHL</sub>               | $R_L = 350\Omega$ , $C_L = 15pF$ , $I_F = 7.5mA$                                     |      |       | 75   | ns    |      |

| Output Rise-Fall Time<br>(10-90%)                                           | t <sub>r</sub> ,t <sub>f</sub> | $R_L = 350\Omega$ , $C_L = 15pF$ , $I_F = 7.5mA$                                     |      | 25    |      | ns    |      |

| Propagation Delay Time of<br>Enable from V <sub>EH</sub> to V <sub>EL</sub> | t <sub>ELH</sub>               | $R_L = 350\Omega$ , $C_L = 15pF$ , $I_F = 7.5mA$ , $V_{EH} = 3.0V$ , $V_{EL} = 0.5V$ |      | 25    |      | ns    |      |

| Propagation Delay Time of<br>Enable from V <sub>EL</sub> to V <sub>EH</sub> | t <sub>EHL</sub>               | $R_L = 350\Omega$ , $C_L = 15pF$ , $I_F = 7.5mA$ , $V_{EH} = 3.0V$ , $V_{EL} = 0.5V$ |      | 15    |      | ns    |      |

| Common Mode Transient<br>Immunity at Logic High<br>Output Level             | CM <sub>H</sub>                | $V_{CM} = 10V, R_L = 350\Omega, V_{O}min.) = 2V, I_F = 0mA,$ 50                      |      | 50    |      | V/μs  | 4    |

| Common Mode Transient<br>Immunity at Logic Low<br>Output Level              | CML                            | $V_{CM} = 10V, R_L = 350\Omega, V_{O}(max.) = 0.8V, I_F = 5mA,$                      |      | - 150 |      | V/μs  | 4    |

- 1. Device considered a two terminal device: pins 1, 2, 3 and 4 shorted together, and pins 5,6,7 and 8 shorted together.

- 2. At 10mA V<sub>F</sub> decreases with increasing temperature at the rate of 1.6mV/°C.

- 3. DC Current Transfer Ratio is defined as the ratio of the output collector current to the forward bias input current

- 4. Common mode transient immunity in Logic High Level is the maximum tolerable (positive)  ${\rm d}V_{\mbox{CM}}/{\rm d}t$  on the leading

- edge of the common mode pulse, V<sub>CM</sub>, to assure that the output will remain in a Logic High state (i.e., V<sub>O</sub>>2.0V). Common mode transient immunity in Logic Low Level is the maximum tolerable (negative) dV<sub>CM</sub>/dt on the trailing edge of the common mode pulse signal, V<sub>CM</sub>, to assure that the output will remain in a Logic Low state (i.e., VO<0.8V).

- 6.3mA condition permits at least 20% CTR degradation guardband. Initial switching threshold is 5mA or less.

# Typical Characteristics

Figure 5 Figure 3 Figure 4 Output Current, IOH vs. Opto-isolator Collector Input Diode Forward **Temperature** characteristics characteristics MA STE TA - TEMPERATURE - "C Figure 8 Propagation Delay, tpHL and tpLH vs. Pulse Input Current, I<sub>FH</sub>. - COLLECTOR VOLTAGE - V Figure 7 Output Voltage, Vol vs. Figure 6 Input-Output Temperature and Fan-Out. characteristics lo = 9.6 m/ TA - TEMPERATURE - \*C

#### **Definitions**

Logic Convention. The 6N137 is defined in terms of positive logic.

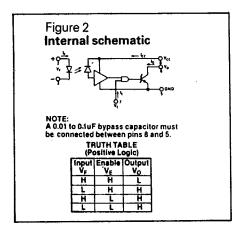

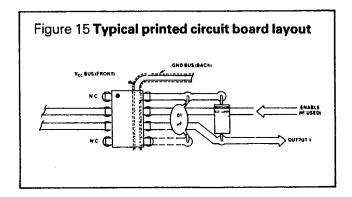

Bypassing. A ceramic capacitor (.01 to  $0.1\mu$ F) should be connected from pin 8 to pin 5 (Figure 15). Its purpose is to stabilize the operation of the high gain linear amplifier. Failure to provide the bypassing may impair the switching properties. The total lead length between capacitor and coupler should not exceed 20mm.

Polarities. All voltages are referenced to network ground (pin 5). Current flowing toward a terminal is considered positive.

Enable Input. No external pull-up required for a logic 1, i.e., can be open circuit.

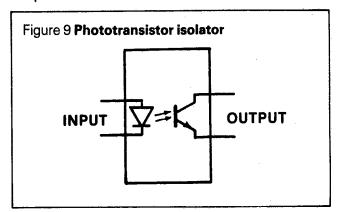

## **Phototransistor vs Integrated Detector**

A common type of optically coupled isolator (Figure 9) uses a phototransistor for a detector where the transistor provides the gain necessary to interface with logic circuits. The major problem with this phototransistor isolator is bandwidth. This is due to the fact that both the detection of the photons and the amplification of the resulting photo current occur in the same physical structure in the phototransistor. The large feedback capacitance between the collector and the base is what essentially limits the phototransistor bandwidth.

The 6N137 design greatly reduces this bandwidth limitation by proper optimization of the detector. The detector element is a monolithic structure, consisting of a photodiode, which collects the light; and a linear high speed amplifier (Fig. 2), which amplifies the resultant photo current. Functional separation of the photodiode from the amplifier reduces feedback capacitance to less than 1pF, thus making possible bandwidths up to 20MHz. The device, in detail, consists of a gallium arsenide phosphide input diode and a monolithically integrated detector at the output. The detector comprises a photodiode followed by a linear amplifier which drives a Schottky clamped output transistor. This output circuit is temperature, voltage, and current compensated to be truly compatible with standard TTL and DTL circuits. It also has a DTL/TTL compatible strobing input; with logic 'O' at the strobe input, the output is held at logic '1', regardless of input conditions at the gallium arsenide phosphide diode. The basic features of the 6N137 are compared to phototransistor types in Table 1.

| TABLE 1                                              |                 |        |                             |

|------------------------------------------------------|-----------------|--------|-----------------------------|

| Isolator<br>Types                                    | Bandwidth<br>BW | gation | Common<br>Mode<br>Rejection |

| 6N137<br>(IC Compatible<br>Optical Isolated<br>Gate) |                 | 60ns   | 10V/10MHz                   |

| Phototransistor<br>Types                             | 100 kHz         | 6μs    | 3V/1MHz                     |

#### TTL interfacing

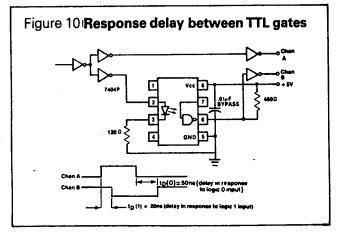

The 6N137 is TTL (also DTL) compatible at both input and output requiring only 5mA input current to sink 13mA at the output — that is, it has 8-gate fan-out capability at 5mA input. The device interfacing with TTL inverters is demonstrated in Figure 10, the circuit for testing response delays. The inverting mode achieves the best speed performance, with typical delays of 20ns and 50ns. The current limiting resistor in series with the input diode is  $120\Omega$ , allowing approximately 10 mA of current to flow in on the 'on' state. The output load resistor is only 450 $\Omega$ - due to the greater sinking capability of the output transistor.

The input diode turn-on delay time of the 6N137 is a function of the input charging time. This delay time is most easily improved by simply adding a capacitor in parallel with the input current limiting resistor and operating from a low impedance source. In general, the capacitor should be a low inductance type with a value for a time constant of 15 to 30ns with the current limiting resistor. If the current limiting resistor is  $100\Omega$ , the capacitor should be 150 to 300pF.

On the output side of the isolator, speed is enhanced by using the lowest possible value of pull-up resistance which is consistent with the current sinking capability of the isolator collector. The stray capacitance to ground should also be minimized. An output pull-up resistor is recommended to improve noise immunity and speed of response in moving to logic '1' output.

#### Line receivers

When digital data is transmitted over an appreciable length of transmission line (even less than a metre), there arises a possibility of ground shift, ground looping, etc. Opto-isolators can reduce the amount of ground loop current and the effects of the resulting common mode voltage. They are, therefore, very useful as line receivers.

55E D

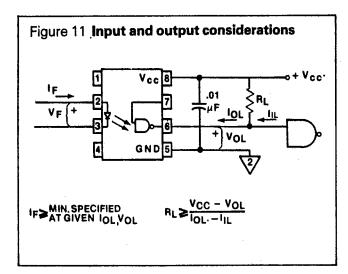

Most line drivers are capable of sourcing a line voltage higher than the minimum (≈ 1.5V) needed to turn "on" an opto-isolator. They usually also deliver a line current greater than the value of IF as determined with reference to Figure 11. It is possible, of course, to design a line driver that will source the proper current and no more, but that is usually not good practice. Good practice is to drive the line with all the voltage and current available, then deal with the excess in the design of the termination of the line.

In the design of the termination, the "off" state is usually ignored unless pre-bias is used. There are usually three objectives in the design of the termination:

- (A) proper "on" state IF

- (B) threshold level, IFth (to switch the output)

- (C) reflections due to impedance mismatch.

#### **Resistive Terminations**

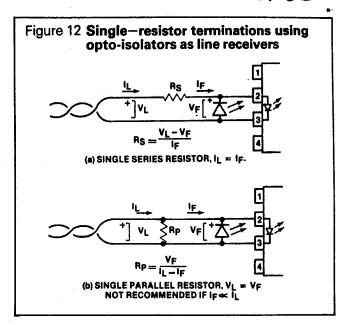

Objective (A) is mandatory; objectives (B) and (C) are discretionary. If discretion allows (B) and (C) to be neglected, the termination may be as simple as in Figure 12 requiring only a single resistor. In most cases, the series resistor termination of Figure 12 (a) would be used because it will accomodate a broader range of driver and line resistance variables. It is slower than the single parallel resistor termination of figure 12 (b) because the input diode is driven from a higher impedance. Slowness can be remedied with a peaking capacitor in parallel with Rs as previously explained; if peaking capacitance is applied, the anti-parallel diode should be used (even if the driver is polarity non-reversing) to allow the peaking capacitor to charge and discharge the maximum amount.

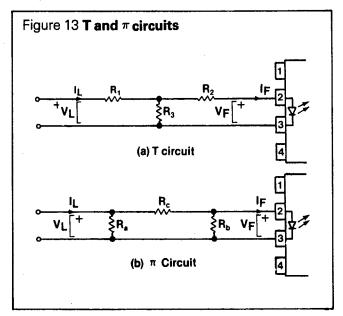

When, in addition to proper I<sub>F</sub>, consideration must be given to either threshold current. I<sub>Fth</sub>, or to line reflections, an additional resistor provides one additional degree of freedom. A two-resistor termination can accommodate the additional objective of either setting the I<sub>Fth</sub> level or of approximate impedance matching but not both. To satisfy all three of the design objectives requires a three resistor termination in either " $\pi$ " or "T" configuration.

The 6N137 may be used as line receivers in either single-ended or balanced line applications. The turn-on voltage of the input diode establishes a threshold for the flow of current, thereby making the noise immunity higher than it would be for a linear line receiver. In many applications, this noise immunity is high enough that only a single-ended transmission line is required. For transmission over long distances or in very noisy environments, a balanced system should be used.

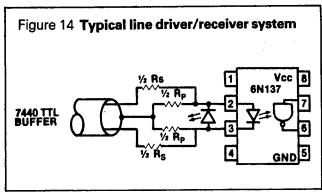

Figure 14 – demonstrates the use of the 6N137 as a balanced line receiver, using 7440 line driver. The resistor values are chosen in each case to match the line driver to the isolator line receiver. The line driver should be designed to supply more current

than the isolator input diode requires; this permits the use of a shunt resistor at the receiving end for better impedance matching and improved noise immunity. To maintain a reasonable impedance match during the negative excursion when the isolator input diode is reversed biased, a diode having about the same turn-on voltage as the input diode should be connected in reverse polarity across the input diode. For this purpose two silicon diodes in series could be used, or one LED, such as the RS standard red 0.2in LED.

Formulas for the terminating resistances are given below.

#### TABLE 2

|    | Basically                       | Given<br>R <sub>O</sub> , I <sub>L</sub> | Given<br>R <sub>O</sub> , V <sub>L</sub> | For best<br>CMR                                                                  |

|----|---------------------------------|------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------|

| Rp | VD<br>IL – ID                   | IL – ID                                  | I Rol ———I                               | Connect ½ RP from each side of isolator input to cable shield.                   |

| Rs | V <sub>L</sub> - V <sub>D</sub> | Ro- VD                                   | $R_O(1-\frac{V_D}{V_D})$                 | Connect ½ Rs<br>in series from<br>each line to<br>input terminal<br>of isolator. |

#### Where:

RO – Line-to-line terminating resistor which gives least reflection.

V<sub>L</sub>, I<sub>L</sub> – line-to-line voltage and line current with R<sub>O</sub> connected.

V<sub>D</sub>, I<sub>D</sub> - isolator input diode forward voltage and current.

## **Circuit board layout**

Careful attention is required for the 6N137 circuit layout due to the high gain employed in its internal amplifier. Power Supply lead lengths (Pins 5 and 8) are particularly important as their inductance provides an impedance across which a positive feedback signal may appear. A socket may be used, but it should be of a type having very short lead lengths. Proper bypassing is also essential. A total of at least 1µF of capacitance from V<sub>CC</sub> to ground should be used on the board. Part of this  $1\mu$ F may come from other bypasses installed to serve other circuits on the same board. In addition to the  $1\mu$ F total, a bypass capacitor of 0.01 µF should be connected directly from Pin 8 to Pin 5 of each 6N137 used on the board. These individual bypass capacitors must be low inductance disc ceramic. It is also

important to have adequate bypassing for those circuits whose response is related to the signals produced in regenerative phase (circuit feedback) with variations in the V<sub>CC</sub> line voltage. If the common practice of having 1µF for each two circuits is adopted, there should be no problem, and much less bypassing will ordinarily suffice.

#### Common mode decoupling

Common mode decoupling can be significantly enhanced by running a ground trace midway between the rows of isolator terminals. This trace is, of course, connected to the output ground (Pin 5) of the 6N137 (see Figure 15). Its purpose is to cause electric potential at the input side to be coupled to ground at the output, rather than to some signal amplifying terminal. If no socket or if in-the-board socket pins are used, this ground lead may be simply a printed trace, but if a socket is used, the ground trace should be paralleled by a piece of grounded wire running up over the socket. When the common mode voltage is very high (>1000V) the ground wire should be insulated to prevent electric discharge from the ground wire to the input terminals.

55E D

# **Typical applications**

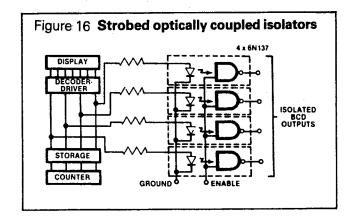

Ground loops involving peripheral equipment are effectively prevented by the use of optically coupled isolators. A typical situation is shown in Figure 16 in which the information on a set of BDC lines is made available at the electrically isolated outputs of the optically coupled isolators.

Although the use of the enable feature of the 6N137 is not always required, strobing of the enable inputs

improves propagation delay times and helps to eliminate the change-of-state glitches that are sometimes present on BCD and other word lines. When the enable inputs are held at logic 'O' (low) the outputs will all be at logic '1' (high). When the enable inputs are high, the outputs will be low on only those isolators whose isolated input is at the logic '1' state; the other outputs will remain high.

Telephone: 0536 201234 ©RS Components Ltd. 1984