EIIINEAAEA

Storage

Technology

# **EMULEX SCSI PROCESSOR**

2400138

ESP Chi

- Reselection sequence, from arbitration through message

- Bus-initiated selection through received command

- Bus-initiated reselection through received message

- Command complete sequences

- Terminate and disconnect sequences

- Interrupts microprocessor only when service is required

- Disconnect or bus reset

- Selection/reselection sequence complete

- Target mode command complete or ATN detected

- Initiator mode command complete or phase change and REQ detected

- Supports clock rates of up to 25 MHz

- Interfaces to eight-bit microprocessor data bus with no support logic

- Low power requirements

#### **FEATURES**

- Supports ANSI X3T9.2 SCSI standard

- Utilizes buffer controller interface for I/O and fast DMA

- Provides on-chip single-ended receivers and 48 mA drivers for SCSI bus

- Contains control logic for differential transceivers

- Generates and checks parity on SCSI bus (checking can be disabled)

- Functions as initiator or target

- Supports asynchronous SCSI bus data transfers up to 6M bytes per second depending on cable characteristics

- Supports synchronous SCSI bus data transfers up to 5M bytes per second

- Programmable synchronous transfer period

- Programmable synchronous transfer offsets up to 15

- Provides sixteen-byte data FIFO between the DMA and SCSI channels

- Utilizes pipelined command structure

- Implements common SCSI sequences without microprocessor intervention

- Selection sequence, from arbitration through command

## **DESCRIPTION**

The Emulex SCSI Processor (ESP) chip is a VLSI device which implements the detailed protocol of the SCSI bus standard. The ESP performs such functions as bus arbitration, selection of a target, or reselection of an initiator. It handles message, command, status, and data transfers between the SCSI bus and its internal FIFO or a buffer memory.

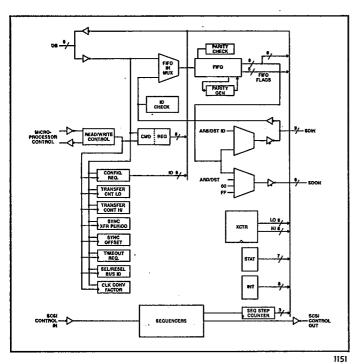

Figure 1 shows the internal architecture of the ESP. The ESP is essentially a sophisticated sequencer. The sequencers are a collection of high- and low-level state machines that perform the various functions required by the SCSI bus and the DMA channel. The high-level state machines manage the disconnect, target, and initiator modes of operation. The low-level state machines perform the actual interface operations.

The main data paths are the buffer controller input and output data buses (BI and BO), and the SCSI input and output data buses (SDI and SDO). All are eight-bit buses. In differential mode, the SDI bus becomes bidirectional and the SDO bus controls the direction of the external differential transceivers.

Storage

Technology

Figure 1. ESP Block Diagram

The ESP replaces existing SCSI interface circuitry, which typically consists of discrete devices, external drivers, and a low performance SCSI interface chip. The ESP contains a fast DMA interface, a sixteen-byte FIFO, and fast asynchronous and synchronous data interface to the SCSI bus, including drivers.

The ESP has been optimized for interaction with the controller microprocessor. Common SCSI bus sequences that would typically require significant amounts of processing and interaction have been reduced to single commands. These include:

| Sequence    | Description                                                                                                     |

|-------------|-----------------------------------------------------------------------------------------------------------------|

| Selection   | Arbitration, target selection, transmission of an optional one-byte message followed by a multiple-byte command |

| Reselection | Arbitration, initiator reselection, and transmission of a one-byte message                                      |

(continued)

# (continued)

| Sequence                      | Description                                                                                                                      |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Bus-Initiated Selection       | Selection detection, receipt of a one-byte message, command length decode and receipt of a command (if the message was IDENTIFY) |

| Bus-Initiated Reselection     | Reselection detection and receipt of a one-byte message                                                                          |

| Target Command<br>Complete    | Transmission of a status byte and a one-byte message                                                                             |

| Target Terminate              | Transmission of a status byte and a one-byte message followed by disconnection from the SCSI bus                                 |

| Target Disconnection          | Transmission of two one-byte messages followed by disconnection from the SCSI bus                                                |

| Initiator Command<br>Complete | Receipt of a status byte and a one-byte message                                                                                  |

To further reduce overhead, the ESP contains a double-ranked Command Register and Transfer Counter which provides a transfer-command pipeline. With Emulex's Buffer Controller 2, which supports buffer setup overlap, the time lost in interbuffer overhead can be reduced to zero.

Using the ESP reduces firmware, part count, board area, and cost while enhancing system performance.

# SYSTEM ORGANIZATION

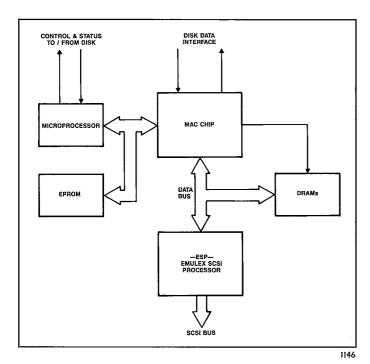

Figure 2 shows a block diagram of a typical SCSI disk controller. The ESP chip provides the controller with a complete SCSI interface. The other major chips in the circuit include the Emulex Merged Architecture Controller (MAC) and a microprocessor.

The MAC chip controls data movement in and out of the buffer memory. It supports up to four DMA channels with a total throughput rate up to 4M bytes per second and provides format control for a wide spectrum of 14-, 8-, 51/4- and 31/2-inch disk drives.

The 8031 microprocessor coordinates the interaction of the VLSI devices on the board. It also implements high level SCSI protocol, such as the message system, SCSI pointers, and command set.

Figure 2. Typical SCSI Controller.

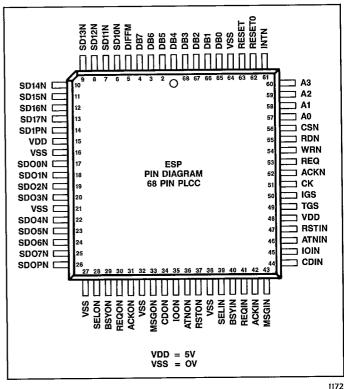

#### **PACKAGING**

The ESP chip is available in a 68-pin PLCC for surface or socket mounting. The Emulex part number is 2400138.

## **REGISTERS**

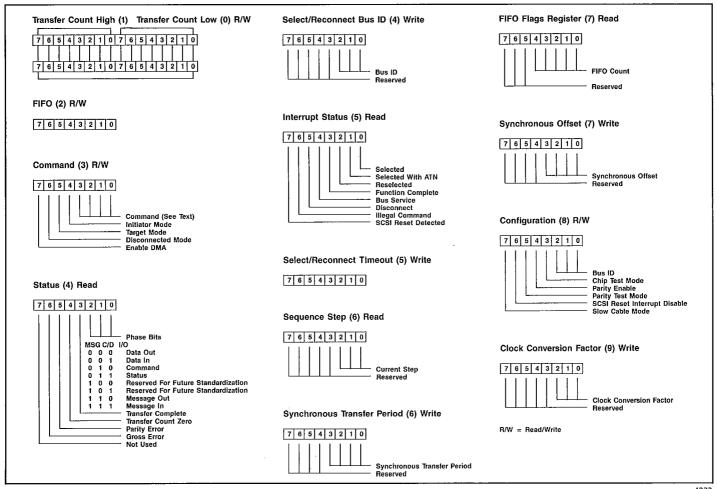

The ESP has 15 registers which are used to configure, command, monitor, and pass data to the chip. These registers are shown in Figure 3 and are more fully described in the paragraphs that follow.

# **Transfer Count Register**

This 16-bit write-only register specifies the number of bytes to be transferred during a DMA operation. Zero specifies the maximum count (65536).

# FIFO Register

The FIFO is a 16-byte deep, first-in-first-out buffer between the SCSI bus and buffer memory. The controller microprocessor can access the FIFO using this register. "Writes" load to the top of the FIFO; "Reads" unload from the bottom.

# **Command Register**

This eight-bit read/write register is used to give commands to the ESP. The register is double ranked, enabling the microprocessor to stack commands to the ESP.

The ESP's command set is listed in the following table.

| Bits                            |                                              |                                                                                                                              |                                        |

|---------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 654                             | 3210                                         | Command                                                                                                                      | Interrupt                              |

| 000<br>000<br>000               | 0000<br>0001<br>0010<br>0011                 | NOP<br>Flush FIFO<br>Reset chip<br>Reset SCSI bus                                                                            | No<br>No<br>No<br>No                   |

| 100<br>100<br>100<br>100        | 0000<br>0001<br>0010<br>0011                 | Reconnect sequence<br>Select without ATN sequence<br>Select with ATN sequence<br>Select with ATN and stop<br>sequence        | Yes<br>Yes<br>Yes<br>Yes               |

| 100                             | 0100<br>0101                                 | Enable selection/reselection Disable selection/reselection                                                                   | No<br>Yes                              |

| 010<br>010<br>010<br>010<br>010 | 0000<br>0001<br>0010<br>0011<br>0100<br>0101 | Send message<br>Send status<br>Send data<br>Disconnect sequence<br>Terminate sequence<br>Target command complete<br>sequence | Yes<br>Yes<br>Yes<br>Yes<br>Yes<br>Yes |

| 010<br>010<br>010<br>010<br>010 | 0111<br>1000<br>1001<br>1010<br>1011         | Disconnect<br>Receive message sequence<br>Receive command<br>Receive data<br>Receive command sequence                        | No<br>Yes<br>Yes<br>Yes<br>Yes         |

| 001<br>001                      | 0000<br>0001                                 | Transfer information<br>Initiator command complete<br>sequence                                                               | Yes<br>Yes                             |

| 001                             | 0010                                         | Accept message                                                                                                               | Yes                                    |

| 001                             | 1000                                         | Transfer pad                                                                                                                 | Yes                                    |

| 001                             | 1010                                         | Set ATN                                                                                                                      | No                                     |

<sup>&</sup>lt;sup>1</sup> External connection of the RSTO pin to the RSTI pin causes an interrupt if the SCSI reset interrupt is not disabled in the Configuration Register.

Storage

Technology

Figure 3. ESP Registers

# **Status Register**

This eight-bit read-only register contains fields to indicate the status of the chip and to qualify the reason for an interrupt.

Bits 2 through 0 indicate the state of the SCSI MSG, C/D, and I/O signals, respectively. These bits define the information phase being asserted by the target (see Figure 3).

## Select/Reconnect Bus ID Register

This three-bit write-only register specifies the destination bus ID for a select or reconnect command.

## **Interrupt Status Register**

This eight-bit read-only register is used in conjunction

with the Status Register and Sequence Counter to determine the cause of an interrupt.

# **Select/Reconnect Timeout Register**

This eight-bit write-only register specifies the number of time units to wait for a response during selection or reselection. The value of a time unit is based on the clock applied to the ESP (CK). At 24 MHz this value is 1.7 msec, which allows an absolute timeout period of from 1.7 msec to 435 msec (1 to 255 units).

#### **Sequence Step**

This eight-bit read-only register indicates the current substep within a command sequence when an interrupt occurs.

# Synchronous Transfer Period Register

This eight-bit write-only register specifies the minimum time between leading edges of successive REQ or ACK pulses during synchronous transfers. At present, only 4 bits are actively used and the remaining four are reserved.

05E D

# FIFO Flags Register

This is a read-only register. The least significant five bits encode the 16 "FIFO full" flags to indicate the number of bytes remaining in the FIFO. The remaining bits are reserved.

## Synchronous Offset Register

This four-bit write-only register specifies the maximum REQIACK offset allowed during synchronous transfers. An offset of zero specifies asynchronous operation.

## **Configuration Register**

This eight-bit read/write register is used to specify different operating options for the ESP, including the ESP's SCSI bus address, parity configuration, and cable speed configuration. Slow cable mode provides longer data setup times on the SCSI bus to compensate for high capacitance on the SCSI cable.

## **Clock Conversion Factor Register**

The microprocessor loads this three-bit write-only register with a clock conversion factor. This factor is required to run the ESP at various clock speeds while maintaining consistent SCSI interface timing. The factor used is one-half the number of clock cycles (CK) required to generate a 400 nsec period clock. For example, at 24 MHz the clock conversion factor is five.

## PROCESSOR OVERHEAD

The following table shows the processor overhead required for the target to change phases during a command. Times are estimated based on using an ESP and an 8031 microprocessor running at 12 MHz.

|                                                                                                                                                                                                                                                     | Change Time<br>(usec)                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Selection to ID message ID message to command * Command to Disconnect message Disconnect message to bus free Reselect to ID message * ID message to data transfer * Data transfer to status Status to Complete message Complete message to bus free | \(\rangle 2\) \(\lambda 2\) \(\lambda 1\) \(\lambda 2\) \(\lambda 2\) \(\lambda 2\) \(\lambda 2\) \(\lambda 2\) \(\lambda 2\) \(\lambda 1\) |

| Total phase change overhead                                                                                                                                                                                                                         | ⟨480                                                                                                                                        |

| Interbuffer time for data transfers                                                                                                                                                                                                                 | 0                                                                                                                                           |

<sup>\*</sup> Associated with the 8031 microprocessor functions.

#### PIN DESCRIPTION

The ESP pins are described below. The pin type is indicated by "I" for input, "O" for output, and "I/O" for bidirectional. Figure 4 shows the ESP's pinouts.

Figure 4. ESP Pinouts

Storage

Technology

| _                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | <del></del>                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pir                                                                                                                                                                                      | Symbo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         | _l                                                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | er Controlle                                                  | r Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 55<br>54<br>55<br>55<br>54<br>55<br>52<br>61                                                                                                                                             | DB6<br>DB5<br>DB4<br>DB3<br>DB2<br>DB1<br>DB0<br>A3<br>A2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         | TTLP/TTL3<br>TTLP/TTL3<br>TTLP/TTL3<br>TTLP/TTL3<br>TTLP/TTL3 | Data Bus Register Address Register Address Register Address Register Address Register Address Register Address Chip Select Read Strobe Write Strobe DMA Request DMA Acknowledge Microprocessor Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | SCSI Bus Int                                                  | <del></del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 25<br>24<br>23<br>22<br>20<br>19<br>18<br>17<br>26<br>13<br>12<br>11<br>10<br>9<br>8<br>7<br>6<br>14<br>28<br>29<br>36<br>31<br>30<br>33<br>34<br>46<br>42<br>41<br>43<br>44<br>45<br>47 | SDO7N<br>SDO6N<br>SDO5N<br>SDO3N<br>SDO3N<br>SDO2N<br>SDO1N<br>SDO9N<br>SDI7N<br>SDI6N<br>SDI5N<br>SDI2N<br>SDI2N<br>SDI2N<br>SDI2N<br>SDIDN<br>SDIPN<br>SELON<br>BSYON<br>ATNON<br>ACKON<br>REQON<br>MSGON<br>CDON<br>IOON<br>RSTON<br>SELIN<br>BSYIN<br>ATNIN<br>ACKIN<br>REQIN<br>MSGIN<br>CDIN<br>SOIN<br>SELIN<br>BSYIN<br>ATNIN<br>SELIN<br>REQON<br>RSTON<br>SELIN<br>BSYIN<br>ATNIN<br>SELIN<br>REGIN<br>ATNIN<br>SELIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGIN<br>REGI | 000000000000000000000000000000000000000 | OD48 OD48 OD48 OD48 OD48 OD48 OD48 OD48                       | SCSI Data Bus Out SCSI Data Bus In SCSI Parity In SCSI Select Out SCSI Request Out SCSI Acknowledge Out SCSI Input/Output Out SCSI Input/Output Out SCSI Reset Out SCSI Select In SCSI Select In SCSI Acknowledge In SCSI Acknowledge In SCSI Request In SCSI Message In SCSI Control Data In SCSI Input/Output In SCSI Input/Output In SCSI Reset In |

(continued)

## (continued)

|                                                    | Miscellaneous Pins                     |     |                                   |                                                                                                        |  |  |  |

|----------------------------------------------------|----------------------------------------|-----|-----------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| 50<br>49<br>5<br>63<br>62                          | IGS<br>TGS<br>DIFFM<br>RESET<br>RESETO | 000 | TTL3<br>TTL3<br>TTL<br>TTL<br>OD4 | Initiator Group Select<br>Target Group Select<br>Differential Mode Enable<br>ESP Reset<br>Reset Output |  |  |  |

| 51<br>15<br>48<br>16<br>21<br>27<br>32<br>38<br>64 | CK VDD VSS VSS VSS VSS VSS VSS VSS VSS |     | ΠL                                | Clock<br>+5Vdc<br>+5Vdc<br>Ground<br>Ground<br>Ground<br>Ground<br>Ground<br>Ground                    |  |  |  |

#### **INTERFACES**

The ESP has two separate interfaces: the buffer data bus and the SCSI bus.

#### **Buffer Data Bus**

The buffer data interface is used for DMA (in conjunction with a buffer controller) and to allow microprocessor access to ESP registers.

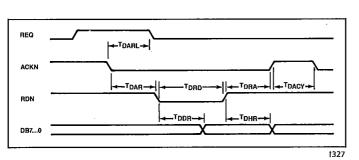

The interface consists of an eight-bit data bus (DB7-DB0), four address lines (A3-A0), a read strobe (RDN), a write strobe (WRN), DMA request (REQ), DMA acknowledge (ACKN), and microprocessor interrupt (INTN) signals.

To access an ESP register, the microprocessor presents an address on A0-A3, drives CSN true, and strobes the data in or out of the register using WRN or RDN.

For DMA operations, the buffer controller manages access timing and generates all buffer memory addresses. When a DMA operation is enabled, the ESP drives REQ true, the buffer controller acknowledges with ACKN and strobes the data into or out of the ESP with WRN or RDN.

#### **SCSI** Interface

The SCSI interface can be configured for operation in either differential mode or single-ended mode using the differential mode enable (DIFFM) pin. When DIFFM is grounded, the ESP operates in single-ended mode; when it is held high, the ESP operates in differential mode.

# Single-Ended Mode

In single-ended mode, all SCSI bus signals have separate input and output pins. That is, the ESP drives data out on SDO7-0N and receives data on SDI7-0N.

## **Differential Mode**

In differential mode, the SDI7N-ON pins carry bidirectional data and the SDO7N-0N pins configure the direction of the external transceivers.

During arbitration, the ESP drives the SDO7-0N lines with the appropriate ID bit set, which sets the desired differential transceiver's direction to out. The other transceivers are configured for input, allowing the ESP to determine whether it has won arbitration. During selection and information transfers, the SDO7-0N lines are driven, either all high or all low, to configure the transceivers for output or input, respectively.

The other SCSI bus signals have separate input and output pins. The direction of the transceivers for ATN, ACK, REQ, MSG, CID, and I/O is selected by the IGS and TGS outputs, which indicate whether the chip is operating in the initiator or the target role. The BSY, SEL, and RST signals are OR-tied on the SCSI bus.

| Absolute Maximum Ratings (Referenced to VSS) |                                                                                                   |                                              |            |  |  |  |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------|------------|--|--|--|--|

| Symbol                                       | Parameter                                                                                         | Limits                                       | Unit       |  |  |  |  |

| V <sub>DD</sub>                              | DC Supply Voltage                                                                                 | 0.5 to +7.0                                  | \<br>\     |  |  |  |  |

| V <sub>I</sub>                               | Input Voltage                                                                                     | V <sub>SS</sub> -0.7 to V <sub>DD</sub> +0.3 | V          |  |  |  |  |

| I <sub>I</sub>                               | DC Input Current                                                                                  | ±10                                          | mA         |  |  |  |  |

| T <sub>STG</sub>                             | Storage Temperature<br>Range (Plastic)                                                            | -40 to +125                                  | ۰c         |  |  |  |  |

| Rec                                          | Recommended Operating Conditions                                                                  |                                              |            |  |  |  |  |

| Symbol                                       | Parameter                                                                                         | Range                                        | Unit       |  |  |  |  |

| V <sub>DD</sub>                              | DC Supply Voltage                                                                                 | 4.75 to 5.25                                 | V          |  |  |  |  |

| TA                                           | Operating Ambient<br>Temperature Range                                                            | 0 to +70                                     | ۰c         |  |  |  |  |

| СК                                           | Rate, Asynchronous<br>Rate, Synchronous                                                           | 10 to 24<br>12 to 24                         | MHz<br>MHz |  |  |  |  |

| IDD                                          | Static (all inputs at V <sub>SS</sub> , all outputs floating, all bidirects configured as inputs) | 10                                           | mA         |  |  |  |  |

| lDD                                          | Dynamic                                                                                           | 70                                           | mΑ         |  |  |  |  |

| ESD/SCR Requirements |                                                                              |        |      |  |  |  |

|----------------------|------------------------------------------------------------------------------|--------|------|--|--|--|

| Symbol               | Parameter                                                                    | Limits | Unit |  |  |  |

| ESP                  | Electrostatic Discharge<br>(100 pF via 1500 ohms)                            | 1500   | V    |  |  |  |

| IMAX                 | Current into or out of any pin (25°C, V <sub>DD</sub> -V <sub>SS</sub> =5 V) | 50     | mA   |  |  |  |

#### **DC Electrical Characteristics**

| Specified at $V_{DD} = 5V \pm 5\%$                            |                                                                                    |                   |                                |                      |                                                                  |  |

|---------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------|--------------------------------|----------------------|------------------------------------------------------------------|--|

| over the temperature of 0 to +70°C                            |                                                                                    |                   |                                |                      |                                                                  |  |

| Symbol                                                        | Parameter                                                                          | Min               | Max                            | Unit                 | Condition                                                        |  |

|                                                               | TTL: TT                                                                            | L Inp             | ut                             |                      |                                                                  |  |

| VIH<br>VIL<br>VIH                                             | Input High Voltage<br>Input Low Voltage<br>Input High Current<br>Input Low Current | 2.0<br>0<br>0     | 0.8<br>20<br>-100              | ∨<br>∨<br>μ^<br>μ^   | V <sub>IN</sub> = V <sub>DD</sub><br>V <sub>IN</sub> = 0 V       |  |

|                                                               | TTLP: TTL Inpu                                                                     | it W              | ith P                          | ullup                |                                                                  |  |

| FĪ수도                                                          | Input High Voltage<br>Input Low Voltage<br>Input High Current<br>Input Low Current | 2.0<br>0<br>0     | 0.8<br>20<br>- <del>4</del> 00 | > > < <              | V <sub>IN</sub> = V <sub>DD</sub><br>V <sub>IN</sub> = 0 V       |  |

|                                                               | TTL3: TTL 3.2                                                                      | 2 mA              | Out                            | put                  |                                                                  |  |

| VOH<br>VOL                                                    | Output High Voltage<br>Output Low Voltage                                          | 2.4               | 0.4                            | V<br>V               | $I_{OH} = -80  \mu A$<br>$I_{OL} = 3.2  \text{mA}$               |  |

|                                                               | OD3: 3.2 mA Op                                                                     | en D              | raln                           | Outp                 | ut                                                               |  |

| V <sub>OL</sub><br>I <sub>ZL</sub>                            | Output Low Voltage<br>High Z Leakage                                               | -20               | 0.4<br>20                      | ν<br><sub>μ</sub> Α  | $I_{OL} = 3.2 \text{ mA}$<br>$V_{O} = 0V \text{ or}$<br>$V_{DD}$ |  |

|                                                               | ST: Schmidt                                                                        | Trigge            | er Inp                         | out                  | •                                                                |  |

| V <sub>T+</sub><br>V <sub>T-</sub><br>VHYS<br>I <sub>IN</sub> | Input High Threshold<br>Input Low Threshold<br>Hysteresis<br>Input Leakage         | 2.1<br>0.2<br>-10 | 0.7<br>10                      | > > > μ <sup>Α</sup> | V <sub>IN</sub> = 0V or<br>VDD                                   |  |

|                                                               | OD48: 48 mA Op                                                                     | en D              | rain                           | Outp                 | ut                                                               |  |

| V <sub>OL</sub><br>I <sub>ZL</sub>                            | Output Low Voltage<br>High Z Leakage                                               | -30               | 0.4<br>30                      | V<br>μA              | $I_{OL} = 48 \text{ mA}$ $V_{O} = 0V \text{ or}$ $V_{DD}$        |  |

| TTL4: 4 mA Output                                             |                                                                                    |                   |                                |                      |                                                                  |  |

| VOH<br>VOL                                                    | Output High Voltage<br>Output Low Voltage                                          | 2.4               | 0.4                            | <b>&gt; &gt;</b>     | I <sub>OH</sub> = -4 mA<br>I <sub>OL</sub> = 4 mA                |  |

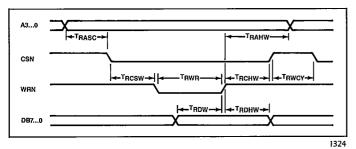

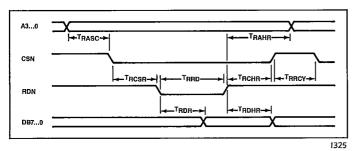

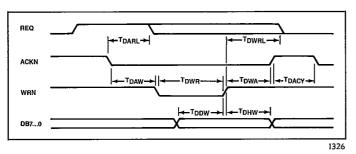

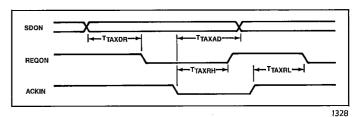

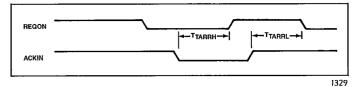

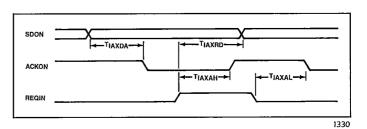

# **AC Timing**

The following figures and the table of values that accompanies them are illustrative of the ESP chip's AC timing characteristics. For definitive values, see the ESP Applications Manual or Specification.

Storage

Technology

Figure 5. Register Write Operation

Figure 6. Register Read Operation

Figure 7. DMA Write Operation

Figure 8. DMA Read Operation

Figure 9. Target Asynchronous Transmit

Figure 10. Target Asynchronous Receive

Figure 11. Initiator Asynchronous Transmit

Figure 12. Initiator Asynchronous Receive

Figure 13. Synchronous Transmit

| Symbol                        | Parameter                | Min | May    | Units |

|-------------------------------|--------------------------|-----|--------|-------|

| <del>-</del>                  |                          |     | IVICIA |       |

| TDACY                         | ACKN High to ACKN Low    | 12  |        | Nsec  |

| TDAR                          | ACKN Low to RDN Low      | 0   |        | Nsec  |

| TDARL                         | ACKN Low to REQ Low      | 0   | 65     | Nsec  |

| TDAW/                         | ACKN Low to WRN Low      | 0   |        | Nsec  |

| TDDR                          | RDN to Data              | l   | 50     | Nsec  |

| TDDW                          | Data to WRN High         | 20  |        | Nsec  |

| TDHR                          | Data Hold Time           | 0   | 50     | Nsec  |

| TDHW                          | Data Hold Time           | 10  |        | Nsec  |

| TDRA                          | RDN High to ACKN High    | 0   |        | Nsec  |

| TDRD                          | RDN Pulse Width          | 40  |        | Nsec  |

| TDWA                          | WRN High to ACKN High    | 12  |        | Nsec  |

| TDWR                          | WRN Pulse Width          | 40  |        | Nsec  |

| TDWRL                         | WRN High to REQ Low      |     | 44     | Nsec  |

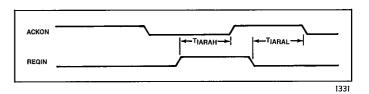

| TIARAH                        | REQIN High to ACKON High |     | 37     | Nsec  |

| TIARAL                        | REQIN Low to ACKON Low   |     | 57     | Nsec  |

| TIAXAH                        |                          |     | 55     | Nsec  |

| TIAXAL                        | REQIN Low to ACKON Low   |     | 33     | Nsec  |

| TIAXDA                        |                          | 55  |        | Nsec  |

| TIAXRD                        | REQIN High to Data       |     | 75     | Nsec  |

| TRAHR                         | Address Hold Time        | 0   |        | Nsec  |

| TRAHW                         | Address Hold Time        | 0   |        | Nsec  |

| TRASC                         | Address Setup to CSN     | 12  |        | Nsec  |

| TRCHR                         | RDN High to CSN High     | 12  |        | Nsec  |

| TRCHW                         | WRN High to CSN High     | 12  |        | Nsec  |

| T <sub>RCSR</sub>             | CSN Setup to RDN         | 12  |        | Nsec  |

| TRCSW                         | CSN Setup to WRN         | 12  |        | Nsec  |

| TROHR                         | Data Hold Time           | 0   | 50     | Nsec  |

| TRDHW                         |                          | 10  |        | Nsec  |

| TRDR                          | RDN to Data              |     | 50     | Nsec  |

| TROW                          | Data to WRN High         | 20  |        | Nsec  |

| TRRCY                         | CSN High to CSN Low      | 30  |        | Nsec  |

| TRRD                          | RDN Pulse Width          | 40  |        | Nsec  |

| T <sub>RWCY</sub>             | CSN High to CSN Low      | 60  |        | Nsec  |

| T <sub>R</sub> W <sub>R</sub> | WRN Pulse Width          | 40  |        | Nsec  |

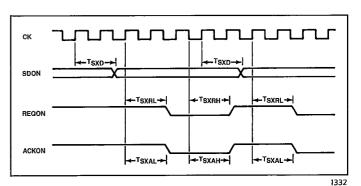

| TSXAH                         | ACKON High from CK Low   | 27  | 50     | Nsec  |

| TSXAL                         | ACKON Low from CK High   | 13  | 39     | Nsec  |

| TSXD                          | Data from CK High        | 30  | 60     | Nsec  |

| TSXRH                         | REQON High from CK Low   | 27  | 50     | Nsec  |

| TSXRL                         | REQON Low from CK High   | 13  | 39     | Nsec  |

| TTARRH                        | ACKIN Low to REQON High  | 40  |        | Nsec  |

| TTARRL                        | ACKIN High to REQON Low  | 47  |        | Nsec  |

| TTAXAD                        | ACKIN Low to Data        |     | 59     | Nsec  |

| TTAXDR                        |                          | 55  | l      | Nsec  |

| TTAXRH                        |                          |     | 40     | Nsec  |

| TTAXRL                        | ACKIN High to REQON Low  |     | 44     | Nsec  |

# **ESP Reference Sheet**

| #                                                                    | ESP Read Re                                                                                                               | gisters                                                                       | #                           | ESI                                                   | Write Registers                                                                                                                                               |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8                            | Transfer counter lo Transfer counter hi FIFO Command Status Interrupt Sequence step FIFO flags Configuration              |                                                                               |                             | Trai<br>FIF<br>Coi<br>S/R<br>S/R<br>Syr<br>Syr<br>Coi | nsfer count lo<br>nsfer count hi<br>O<br>mmand<br>bus ID<br>timeout<br>nc period<br>nc offset<br>nfiguration                                                  |

|                                                                      | COMMAND                                                                                                                   | REGISTER                                                                      | (RV                         | /3) (B                                                | t 7 = DMA)                                                                                                                                                    |

| Mis                                                                  | c Cmds                                                                                                                    | Initiator                                                                     | Cm                          | ds                                                    | Target Cmds                                                                                                                                                   |

| 01 F<br>02 F<br>03 F<br>03 F<br>40 F<br>41 S<br>42 S<br>43 S<br>44 F | NOP Flush FIFO Reset chip Reset SCSI Connected Cmds Reconnect Sel w/o ATN Sel w/ATN Sel w/ATN/stop Enable S/R Disable S/R | 11 Cmd o<br>12 Accep                                                          | nsfer pad                   |                                                       | 20 Send msg 21 Send status 22 Send data 23 Disconnect seq 24 Terminate seq 25 Cmd comp seq 27 Disconnect 28 Rcv msg seq 29 Rcv cmd 2A Rcv data 2B Rcv cmd seq |

| STA                                                                  | TUS (RO4)                                                                                                                 | INTERRUPT (RO5)                                                               |                             | RO5)                                                  | CONFIG (RW8)                                                                                                                                                  |

| 4 X<br>5 P<br>6 G<br>7<br><b>SEC</b><br>0 Se<br>1 Se                 | <i>I</i> D                                                                                                                | O Selecte 1 Selecte 2 Reselec 3 Func c 4 Bus ser 5 Discon 6 Illegal 7 SCSI re | d wated omportice omections | lete                                                  | O Bus ID O 1 Bus ID 1 2 Bus ID 2 3 (O) 4 Parity enable 5 Parity test mode 6 SCSI rst int dis 7 Slow cable                                                     |