8,388,608 bit CMOS FLASH Memory Module

### **Features**

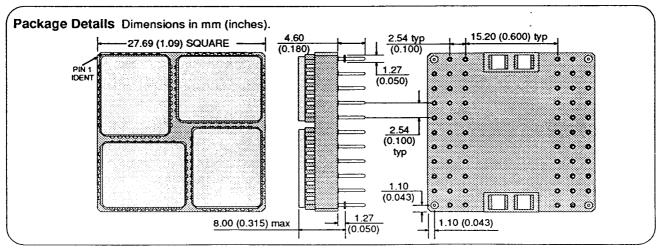

Fast access times of 200/250 ns (170ns in development). User Configurable as 32 / 16 / 8 bit wide output. Operating Power 200 / 110 / 65 mW (typical) Low Power Standby 1 mW (typical) Single High Voltage for Erase/Write: V<sub>pp</sub>=12.0V±5%. Fast Programming - Byte =10µs, Module = 4 sec. (typ). Flash Electrical Erase of Module 10 seconds typ. 10<sup>4</sup> Erase/Write Cycle Endurance min. (10<sup>5</sup> typical) Uses Command Register Architecture for all operations. On board decoupling capacitors.

Module Components May be screened in accordance with MIL-STD-883C.

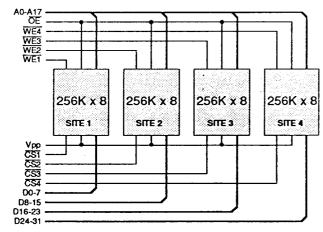

## **Block Diagram**

# PUMA 2F8003

## PUMA 2F8003-17/20/25

Issue 1.0: March 1991

## ADVANCE PRODUCT INFORMATION

| 711 | ı De                                   | ıınıt                                            | ion                                                        |                       |                                                                      |                                         |                           |   |

|-----|----------------------------------------|--------------------------------------------------|------------------------------------------------------------|-----------------------|----------------------------------------------------------------------|-----------------------------------------|---------------------------|---|

|     | 1                                      | 12                                               | 23                                                         |                       | 34                                                                   | 45                                      | 56                        | _ |

|     | O8000000000000000000000000000000000000 | O WE2 O CS O O D O D O D O D O D O D O D O D O D | O D 14 O D 13 O D 12 O D O D O D O D O D O D O D O D O D O | VIEW<br>FROM<br>ABOVE | O24 O 25 O 25 O 27 O 21 O 29 O 23 O 25 | 0 8 0 8 0 8 0 8 0 8 0 8 0 8 0 8 0 8 0 8 | 0208080804040408080808086 |   |

|     |                                        |                                                  | ~                                                          |                       | -7-4                                                                 |                                         |                           |   |

#### **Pin Functions**

| A0-A17   | Address Inputs            |

|----------|---------------------------|

| D0-D31   | Data Input/Output         |

| CS1-4    | Chip Selects              |

| ŌĒ       | Output Enable             |

| WE1-4    | Write Enables             |

| $V_{pp}$ | Write/Erase Input Voltage |

| $V_{cc}$ | Power (+5V)               |

| GND      | Ground                    |

## **GENERAL DESCRIPTION**

The PUMA 2F8003 is a 8,388,608 bit CMOS FLASH Memory which is configurable as 8, 16 or 32 bit wide output using CS1-4, allowing flexibility in a wide range of applications.

FLASH memory combines the functionality of EPROM with on-board electrical Write/Erasure. The PUMA 2F8003 utilizes devices which use a Command Register to manage these functions, allowing fixed power supply during Write/Erase and maximum EPROM

compatibility. During Write cycles, the command register internally latches address and data needed for the Write and Erase operations, thus simplifying the external control circuitry.

FLASH technology reliably stores data even after 10,000 Write/Erase cycles and utilises a single program supply of 12V±5%. Additionally, the interactive program algorithm allows a typical room temperature program time of 4 seconds for the entire module (in 32 bit mode). The typical module erasure time is less than 10 seconds.

## Absolute Maximum Ratings (1)

| Temperature Under Bias                                 | TOPR             | -55 to +125 °C  |

|--------------------------------------------------------|------------------|-----------------|

| Storage Temperature                                    | T <sub>stg</sub> | -65 to +150 °C  |

| Voltage on Any Pin with respect to GND (2)             | $V_{T1}$         | -2.0 to +7.0 V  |

| Voltage on A9 pin with respect to GND (3)              | V <sub>T2</sub>  | -2.0 to 13.5 V  |

| Voltage on V <sub>PP</sub> pin with respect to GND (3) | V <sub>PT</sub>  | -2.0 to +14.0 V |

| V <sub>cc</sub> Supply Voltage <sup>(2)</sup>          | V <sub>cc</sub>  | -2.0 to +7.0 V  |

| Output Short Circuit Current (4)                       | I <sub>sc</sub>  | 100 mA          |

- Notes: (1) Stresses above those listed may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- (2) Minimum DC input voltage is -0.5V. During transitions inputs may undershoot to -2.0V for periods less than 20 ns. Maximum DC voltage on output pins is  $V_{cc}$ +0.5V, which may overshoot to  $V_{cc}$ +2.0V for periods less than 20 ns.

- (3) Minimum DC input voltage is -0.5V. During transitions inputs may undershoot to -2.0V for periods less than 20 ns. Maximum DC input voltage is +13.5V, which may overshoot to +14.0V for periods less than 20 ns.

- (4) Output shorted for no more than one second. No more than one output shorted at any one time.

## **Recommended Operating Conditions**

|                      |          |                  | min                      | typ  | max                 |                    |

|----------------------|----------|------------------|--------------------------|------|---------------------|--------------------|

| Supply Voltage       |          | V <sub>cc</sub>  | 4.5                      | 5.0  | 5.5                 | V                  |

| Programming Voltage  | Read     | V <sub>PPR</sub> | -0.5                     | 5.0  | 12.6                | V                  |

| Write/Eras           | e/Verify | V <sub>PPW</sub> | 11.4                     | 12.0 | 12.6                | V                  |

| Input High Voltage   | TTL      | V <sub>IH</sub>  | 2.0                      |      | V <sub>∞</sub> +0.5 | V                  |

|                      | CMOS     | V <sub>iHC</sub> | $0.7\mathrm{V}_{\infty}$ | -    | V <sub>∞</sub> +0.5 | V                  |

| Input Low Voltage    | TTL      |                  | -0.5                     | -    | 0.8                 | V                  |

|                      | CMOS     | V <sub>ILC</sub> | -0.5                     | -    | 8.0                 | V                  |

| Operating Temperatur | e        | T.               | 0                        | -    | 70                  | °C                 |

| •                    |          | TAI              | -40                      | -    | 85                  | °C (-I suffix)     |

|                      |          | T                | -55                      | -    | 125                 | °C (-M,-MB suffix) |

## Capacitance $(T_A=25^{\circ}C, f=1MHz)$

| Parameter            |                    | Symbol             | Test Condition       | typ | max | Unit |

|----------------------|--------------------|--------------------|----------------------|-----|-----|------|

| Input Capacitance    | Address, OE        | C <sub>IN1</sub>   | V <sub>IN</sub> =0V  | -   | 24  | pF   |

|                      | $V_{pp}$           | C <sub>IN2</sub>   | V <sub>IN</sub> =0V  | -   | 24  | pF   |

|                      | Other pins         | CIN3               | V <sub>IN</sub> =0V  | -   | 6   | рF   |

| Output Capacitance   | 32 bit             | C <sub>OUT32</sub> | $V_{OUT}=0V$         | -   | 12  | pF   |

|                      | 16 bit             | C <sub>OUT16</sub> | V <sub>out</sub> =0V | -   | 24  | pF   |

|                      | 8 bit              | COUTS              | V <sub>OUT</sub> =0V | -   | 48  | pF   |

| Note: These paramete | rs are calculated. | not measure        | d.                   |     |     |      |

PUMA 2F8003-17/20/25 ISSUE 1.0 : MARCH 1991

# DC Electrical Characteristics (T<sub>A</sub>=-55°C to +125°C,V<sub>cc</sub>=5V ± 10%)

| Parameter                            | S        | ymbol              | Test Condition                                                                                                  | min                 | typ(2) | max        | Unit            |

|--------------------------------------|----------|--------------------|-----------------------------------------------------------------------------------------------------------------|---------------------|--------|------------|-----------------|

| I/P Leakage Current Addre            | ess, OE  | l <sub>u1</sub>    | V <sub>cc</sub> =V <sub>cc</sub> max, V <sub>IN</sub> =0V or V <sub>cc</sub> ,V <sub>PP</sub> =V <sub>PPL</sub> | -                   | -      | <u>+</u> 4 | μΑ              |

| Oth                                  | ner Pins | I <sub>L12</sub>   | V <sub>cc</sub> =V <sub>cc</sub> max, V <sub>IN</sub> =0V or V <sub>cc</sub>                                    | -                   | -      | ±1         | μΑ              |

| Output Leakage Current               |          | I <sub>LO</sub>    | $V_{cc} = V_{cc}$ max, $V_{out} = 0V$ or $V_{cc}$ , 8 bit                                                       | -                   | -      | ±40        | μΑ              |

| V <sub>pp</sub> Read Current         |          | I <sub>PP1</sub>   | $V_{pp} = V_{ppH}$                                                                                              | -                   | 270    | 800        | μΑ              |

| Device Identifier Current            |          | IID                | A9=V <sub>ID</sub>                                                                                              | -                   | 270    | 800        | μΑ              |

| V <sub>∞</sub> Operating Current     | 32 bit   | 100032             | $\overline{CS}=V_{iL}^{(1)}$ , $\overline{OE}=V_{iH}$ , $I_{OUT}=0$ mA, $f=6$ MHz                               | <u>-</u>            | 40     | 120        | mΑ              |

|                                      | 16 bit   | I <sub>CCO16</sub> | As above                                                                                                        | -                   | 22     | 62         | mΑ              |

|                                      | 8 bit    | Iccos              | As above                                                                                                        | -                   | 13     | 33         | mΑ              |

| V <sub>cc</sub> Programming Current  | 32 bit   | I <sub>CCP32</sub> | Programming in Progress                                                                                         | -                   | 4      | 40         | mΑ              |

| •                                    | 16 bit   | I <sub>CCP16</sub> | As above                                                                                                        | -                   | 4      | 22         | mΑ              |

|                                      | 8 bit    | I <sub>CCP8</sub>  | As above                                                                                                        | -                   | 4      | 13         | mA              |

| V <sub>cc</sub> Erase/Verify Current | 32 bit   | I <sub>CCE32</sub> | CS=V <sub>it</sub> (1), Write/Erase in progress                                                                 | -                   | 20     | 60         | mA              |

|                                      | 16 bit   | I <sub>CCE16</sub> | As above                                                                                                        | -                   | 12     | 32         | mΑ              |

|                                      | 8 bit    | I <sub>CCE8</sub>  | As above                                                                                                        | -                   | 8      | 18         | <sub>,</sub> mA |

| V <sub>PP</sub> Write/Erase Current  | 32 bit   | I <sub>PP32</sub>  | V <sub>PP</sub> =V <sub>PPH</sub> , Write/Erase in progress                                                     | -                   | 40     | 120        | mΑ              |

| •                                    | 16 bit   | I <sub>PP16</sub>  | As above                                                                                                        | -                   | 22     | 62         | mΑ              |

|                                      | 8 bit    | I <sub>PP8</sub>   | As above                                                                                                        | -                   | 13     | 33         | mA              |

| Standby Supply Current               | TTL      | I <sub>SB1</sub>   | V <sub>cc</sub> =V <sub>cc</sub> max, CS=V <sub>IH</sub> (t)                                                    | -                   | -      | 4          | mΑ              |

|                                      | CMOS     | 1882               | V <sub>cc</sub> =V <sub>cc</sub> max, CS=V <sub>IHC</sub> <sup>(1)</sup>                                        | -                   | 200    | 400        | μΑ              |

| Device Identifier Voltage            |          | V <sub>ID</sub>    | A9=V <sub>ID</sub>                                                                                              | 11.5                | -      | 13.0       | V               |

| V <sub>pp</sub> Voltage During Rea   | ad Only  | V <sub>PPL</sub>   | Write/Erase Inhibited if V <sub>PP</sub> =V <sub>PPL</sub>                                                      | 0                   | -      | 6.5        | ٧               |

| , ,                                  | d/Write  | V <sub>PPH</sub>   |                                                                                                                 | 11.4                | -      | 12.6       | ٧               |

| Output Low Voltage                   |          | V <sub>OL</sub>    | I <sub>ot</sub> =2.1mA.                                                                                         | -                   | -      | 0.45       | V               |

| Output High Voltage TTL              | loading  | V <sub>OH1</sub>   | I <sub>oH</sub> =-2.5mA.                                                                                        | 2.4                 | -      | -          | ٧               |

| CMOS                                 | loading  | V <sub>OH2</sub>   |                                                                                                                 | V <sub>∞</sub> -0.4 |        | -          | V               |

Notes (1)  $\overline{\text{CS}}$  above are accessed through  $\overline{\text{CS1-4}}$ . These inputs must be operated simultaneoulsy for 32 bit operation, in pairs in 16 bit mode and singly for 8 bit mode.

- (2) Typical figures are measured at 25°C and nominal  $\rm V_{cc}$ .

- (3) Maximum active current is the sum of  $I_{cc}(I_{cp})$  and  $I_{pp}$ .

- (4) CAUTION: the PUMA 2F8003 must not be removed from or inserted into a socket when  $V_{cc}$  or  $V_{PP}$  is applied.

## **ERASE AND PROGRAMMING PERFORMANCE**

| Parameter         |        | min | typ | max | Units  | Comments                                              |

|-------------------|--------|-----|-----|-----|--------|-------------------------------------------------------|

| Erase Times       | 32 bit | -   | 10  | 60  | sec    | Excludes 00 <sub>H</sub> Programming Prior to Erasure |

| Program Times     | 32 bit | -   | 4   | 25  | sec    | Excludes System-Level Overhead                        |

| Write/Erase Cycle | es     | 104 | 10⁵ | -   | cycles | Not 100% tested                                       |

## **AC Test Conditions**

- \* Input pulse levels: 0.45V to 2.4V.

- \* Input rise and fall times: ≤ 10ns.

- \* Input and Output timing reference levels: 0.8V and 2.0V

- \* Output load: 1 TTL gate plus 100 pF.

## **READ**

## **AC Characteristics**

|                                                   |                 | -17     | -2  | 20  | -   | 25  |      |

|---------------------------------------------------|-----------------|---------|-----|-----|-----|-----|------|

| Parameter                                         | Symbol          | min max | min | max | min | max | Unit |

| Read Cycle Time                                   | t <sub>BC</sub> | 170 -   | 200 | -   | 250 | -   | ns   |

| Chip Select Access Time                           | t <sub>cs</sub> | - 170   | -   | 200 | -   | 250 | ns   |

| Address Access Time                               | t               | - 170   | -   | 200 | -   | 250 | ns   |

| Output Enable Access Time                         | t <sub>oe</sub> | - 55    | -   | 55  | -   | 55  | ns   |

| Chip Select to Output in Low Z(2)                 | t <sub>uz</sub> | 0 -     | 0   | -   | 0   | -   | ns   |

| Output Enable to Output in Low Z(2)               | toLZ            | 0 -     | 0   | -   | 0   | -   | ns   |

| Output Disable to Output in High Z <sup>(1)</sup> |                 | - 40    | -   | 40  | -   | 45  | ns   |

| Output Hold Time                                  | t <sub>oh</sub> | 0 -     | 0   | -   | 0   | -   | ns   |

| Write Recovery Time                               | twhGL           | 6 -     | 6   | -   | 6   | -   | μs   |

Notes: (1) t<sub>DF</sub> is defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels.

- (2) These parameters are sampled and not 100% tested.

- (3) 170 ns specifications are currently in development and are provided here for information only.

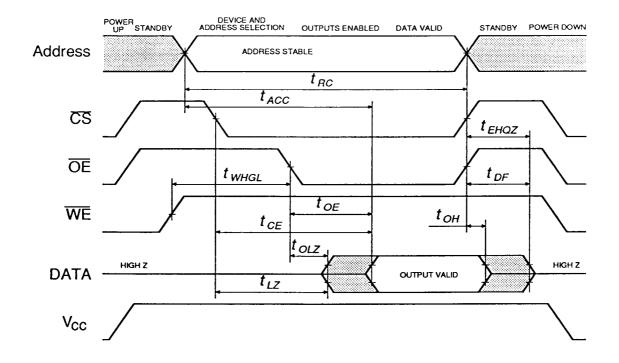

# **Read Cycle Timing Waveform**

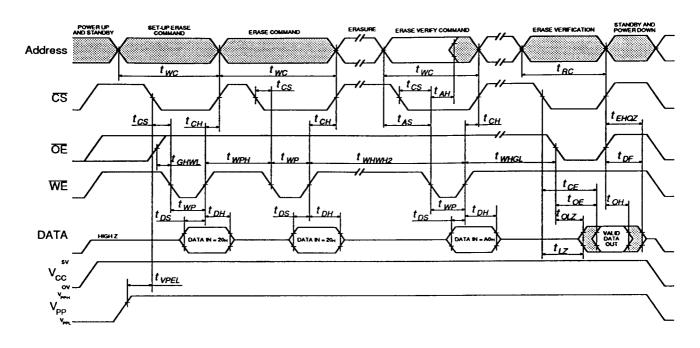

## WRITE/ERASE/PROGRAM (1)

## **AC Characteristics**

|                                               |                    | -17 |          | -2  | 20   | -   | -25  |      |

|-----------------------------------------------|--------------------|-----|----------|-----|------|-----|------|------|

| Parameter                                     | Symbol             | min | max      | min | max  | min | max  | Unit |

| Write Cycle Time                              | t <sub>wc</sub>    | 170 | ÷        | 200 | -    | 250 | -    | ns   |

| Address Setup Time                            | tas                | 0   | -        | 0   | -    | 0   | -    | ns   |

| Address Hold Time                             | t <sub>ah</sub>    | 60  | -        | 60  | -    | 90  | -    | ns   |

| Data Setup Time                               | t <sub>os</sub>    | 50  |          | 50  | -    | 50  | -    | ns   |

| Data Hold Time                                | t <sub>on</sub>    | 10  | •        | 10  | -    | 10  | -    | ns   |

| Write Recovery Time                           | t <sub>whGL</sub>  | 6   | -        | 6   | -    | 6   | -    | μs   |

| Read Recovery Time                            | t <sub>GHWL</sub>  | 0   |          | 0   | -    | 0   | -    | μs   |

| Chip Select Setup Time                        | t <sub>cs</sub>    | 20  | <u>.</u> | 20  | -    | 20  | -    | ns   |

| Chip Select Hold Time                         | t <sub>ch</sub>    | 0   |          | 0   | -    | 0   | -    | ns   |

| Write Pulse Width                             | $t_{wp}$           | 50  |          | 50  | -    | 50  | -    | ns   |

| Write Pulse Width High                        | t <sub>wph</sub>   | 20  |          | 20  | -    | 20  | -    | ns   |

| <b>Duration of Programming Operation</b>      | t <sub>whwh1</sub> | 10  | 25       | 10  | 25   | 10  | 25   | μs   |

| Duration of Erase Operation                   | t <sub>whwh2</sub> | 9.5 | 10.5     | 9.5 | 10.5 | 9.5 | 10.5 | ms   |

| V <sub>PP</sub> Setup Time to Chip Select Low | $t_{vPEL}$         | 100 |          | 100 | -    | 100 | -    | ns   |

| V <sub>∞</sub> Setup Time                     | t <sub>vcs</sub>   | 2   |          | 2   | -    | 2   | -    | μs   |

| V <sub>PP</sub> Rise Time                     | t <sub>vppr</sub>  | 500 |          | 500 | -    | 500 | -    | ns   |

| V <sub>PP</sub> Fall Time                     | t <sub>vppf</sub>  | 500 |          | 500 | -    | 500 | -    | ns   |

Notes (1) Read timing characteristics during read/write operations are the same as during read only operations. Refer to AC Characteristics for read only operations.

(2) 170 ns specifications are currently in development and are provided here for information only.

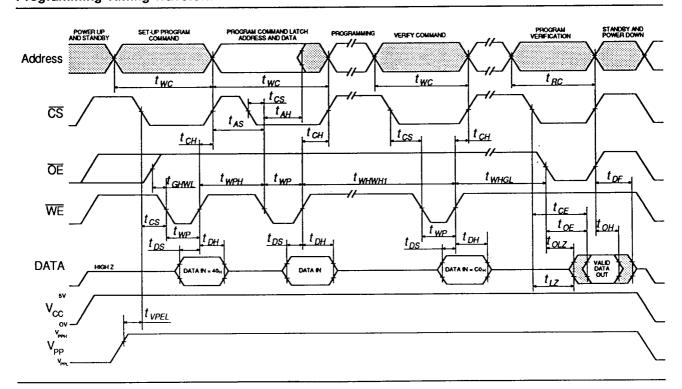

## **Programming Timing Waveform**

# **Erase Timing Waveform**

## MODULE DESCRIPTION

When normal TTL/CMOS logic levels are applied to the  $V_{pp}$  pin, the module displays normal EPROM Read, Standby, Output Disable and Device Identifier operations. However, when high voltage ( $V_{ppH}$ ) is applied to  $V_{pp}$  the Write/Erase options are available as well as the Read.

#### **BUS OPERATIONS**

Read Two control functions are provided, both of which must be logically active to obtain data at the outputs.  $\overline{CS}$  selects the module and controls the power, while  $\overline{OE}$  gates data from the output pins - see the Read Cycle Timing Waveform for details.

**Write** Module Write/Erasure are accessed via the command register while V<sub>PP</sub> is at V<sub>PPH</sub>. Note that the register itself does not occupy an addressable memory location, but is simply a latch used to store the command and address/data information required to excecute the command.

With  $\overline{CE}$  and  $\overline{WE}$  at  $V_{iL}$  the command register is accessed; addresses are latched on the falling edge of

$\overline{\text{WE}}$  and data latched on the rising edge of  $\overline{\text{WE}}$ . The three most significant register bits (D7-D5) encode the command function while all other bits (D4-D0) must be zero. The exception to this is the Reset command when data  $\text{FF}_{\text{H}}$  is written to the register and Identifier mode when  $90_{\text{H}}$  is written to the register.

Output Disable When  $\overline{OE}$  is at  $V_H$  the output pins are placed in a high impedance state and output from the module is disabled.

Standby If  $\overline{\text{CS}}$  is held at  $V_{\mathbb{H}}$  the power consumption of the module is substantially reduced because most of the on-board circuitry is disabled. The outputs are placed in a high impedance state (independent of  $\overline{\text{OE}}$ ).

If the PUMA 2F8003 module is deselected and placed in Standby mode during Write/Erase and Verify cycles, the module will continue to draw normal active current until the operation is terminated.

Device Identifier Placing a high voltage (V<sub>ID</sub>) on pin A9 of the module causes the manufacturer and device codes to be output. This can be used to match the correct Write/Erase algorithms to the module.

## **PUMA 2F8003 Bus Operations**

| <b>OPERATION</b> |                                        | <i>Vpp</i> (1)   | AO              | A9                  | <del>CS</del>   | ŌĒ              | WE              | D0 - D7                |

|------------------|----------------------------------------|------------------|-----------------|---------------------|-----------------|-----------------|-----------------|------------------------|

|                  | Read                                   | $V_{PPL}$        | A0              | A9                  | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Data out               |

|                  | Output Disable                         | V <sub>PPL</sub> | Х               | Х                   | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Tri-State              |

| READ ONLY        | Standby                                | $V_{PPL}$        | Х               | Х                   | V <sub>IH</sub> | Х               | Х               | Tri-State              |

|                  | Manufacturer Identifier <sup>(2)</sup> | $V_{PPL}$        | V <sub>IL</sub> | V <sub>ID</sub> (3) | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Data = 89 <sub>H</sub> |

|                  | Device Identifier <sup>(2)</sup>       | $V_{PPL}$        | V <sub>IH</sub> | V <sub>ID</sub> (3) | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Data = BDH             |

|                  | Read                                   | $V_{PPH}$        | A0              | A9                  | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Data Out (4)           |

| DEADAADITE       | Output Disable                         | $V_{PPH}$        | Х               | Х                   | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Tri-State              |

| READ/WRITE       | Standby                                | $V_{PPH}$        | X               | Х                   | V <sub>IH</sub> | Х               | X               | Tri-State              |

|                  | Write                                  | $V_{PPH}$        | Α0              | A9                  | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Data In (5)            |

- Notes (1) V<sub>PPL</sub> may be GND, a NC with a resistor tied to GND, or ≤V<sub>CC</sub>+2.0V. V<sub>PPH</sub> is the programming voltage specified for the device refer to the DC Characteristics. When V<sub>PP</sub>=V<sub>PPL</sub> memory contents can be read but not Written or Erased

- (2) Manufacturer and Device codes may also be accessed via the command register. In this mode all addresses except A0 and A9 must be at V<sub>II</sub>.

- (3)  $11.5V \le V_{10} \le 13.0V$

- (4) Read operations with V<sub>PP</sub>=V<sub>PPH</sub> may access array data or identifier codes (see page 7).

- (5) Refer to Command Definition table for valid Data In during a Write operation.

- (6) X can be V<sub>IL</sub> or V<sub>IH</sub>.

#### **COMMAND DEFINITIONS**

With the  $V_{pp}$  pin at a low voltage the Command Register contents default to  $00_{\rm H}$ , enabling Read-only operations. A high voltage on  $V_{pp}$  enable Read/Write modes with device operation selected by writing data into the Register - see the Command Definition table for details.

Note that the following descriptions refer to the commands for the PUMA 2F8003 operating in 8 bit mode. The actual data presented to the module will change with the configured word width i.e. for the Erase Verify command of  $AO_{\rm H}$ , if the PUMA is in 16 bit mode  $AOAO_{\rm H}$  will be placed on the data bus and in 32 bit mode the data would be  $AOAOAOAO_{\rm H}$ .

**Read** While  $V_{pp}$  is high the memory contents can be Read by first writing  $00_{\rm H}$  into the Command Register. A delay of  $6\mu s$  is required before reading the first location, but all subsequent Read operations take  $t_{\rm acc}$ . This mode remains enabled until the Command Register contents are altered.

On power up the Register contents will be  $00_{\rm H}$ , ensuring that the memory contents are not changed during the  $V_{\rm pp}/V_{\rm cc}$  power transition. If the  $V_{\rm pp}$  pin is hard wired to a high voltage the memory will power up enabled for Read until the Register contents are altered.

Intelligent Identifier In order to use the correct programming and erase algorithms on PROM devices, these parts usually have built in codes to identify manufacturer and specific device. However, to access these codes address line A9 has to be placed at a high voltage, which is not considered good practise and can lead to complications on PCB design.

The PUMA 2F8003 module uses both of these codes to supplement traditional PROM programming methodology, but the identifiers are accessed through the Command Register without placing a high voltage on A9. Writing 90<sub>H</sub> into the Register starts this process with a subsequent Read from 00000<sub>H</sub> retrieving the manufacturer code of 89<sub>H</sub> and a Read from 00001<sub>H</sub> giving the device code B4<sub>H</sub>. To terminate this sequence another valid command must be written to the Register.

**Set-up Program/Program** Set-up program is a command only operation which prepares the memory for byte programming, initiated by writing  $40_{\rm H}$  into the command register.

Once Set-up program has been performed, the next WE pulse causes data to be latched on the rising edge and the address is latched on the falling edge of this pulse. Internal programming begins on the rising edge and is terminated with the next rising edge of Write Enable used to write the program-verify command.

**Program-Verify** This module is programmed byte by byte, which can occur sequentially or at random, but the byte just written must be verified.

Writing CO<sub>H</sub> to the command register begins this operation, which also terminates the programming operation. The last byte written will be verified; no new address information is required as the previous address is latched. A Read Cycle can now be performed in order to compare the data just written with the byte contents. This process is shown by the Programming Algorithm.

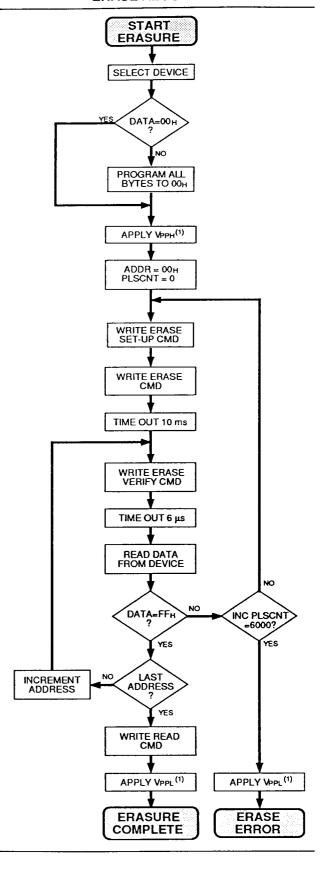

Set-up Erase/Erase Set-up erase is a command only operation which prepares the memory for electrical erasure of all contents, initiated by writing  $20_{\rm H}$  to the Command Register.

In order to start erasure  $20_{\rm H}$  must again be written to the register; this two-step sequence ensures that accidental erasure will not occur. Additionally, if the  $V_{pp}$  pin is not at a high voltage the memory contents are protected against erasure.

Erase-Verify The Erase command erases all the contents of the memory, but after this operation all bytes must be verified. This is accomplished by writing  $A0_H$  to the Command Register, with the address of the byte to be verified supplied as it is latched on the falling edge of the Write-Enable pulse. Reading FF $_H$  from the addressed byte indicates that it is erased. This command must be issued prior to each byte verification to latch its address.

If the data read is not  $FF_{\mu}$  another erase operation must be performed. Verification can then continue from the address of the last verified byte, and once all bytes have been verified the erase procedure is complete. This process is shown by the Erase algorithm.

The verify operation is halted by writing another valid command e.g. Set-up Program, into the command register.

**Reset** This command, which consists of two consecutive writes of FF<sub>H</sub>, will safely abort either Erase or Program operations after the Set-up commands. Memory contents will not be altered, and a valid command must then be written to place the device in the desired state.

## **ALGORITHM NOTES**

It can be seen that the Programming and Erase algorithms both terminate with the Command Register being loaded with a Read command. If devices on the PUMA 2F8003 are being Programmed/Erased sequentially (i.e. it is configured in 8 bit mode) then at the termination of the sequence all devices which have been accessed must be returned to the Read mode before correct operation can resume.

PUMA 2F8003-17/20/25 ISSUE 1.0 : MARCH 1991

#### **PUMA 2F8003 Command Definitions**

|                                       | Bus             | First E       | Bus Cycle | 9               | Second Bus Cycle |          |                 |  |

|---------------------------------------|-----------------|---------------|-----------|-----------------|------------------|----------|-----------------|--|

| COMMAND                               | Cycles<br>Req'd | Operation (1) | Addr (2)  | Data (3)        | Operation (1)    | Addr (2) | Data (3)        |  |

| Read Memory <sup>(8)</sup>            | 1               | Write         | Х         | 00 <sub>H</sub> | Read             | RA       | RD              |  |

| Read Identifier Codes <sup>(4)</sup>  | 2               | Write         | Х         | 90 <sub>H</sub> | Read             | IA       | ID              |  |

| Set-up Erase/Erase <sup>(5)</sup>     | 2               | Write         | Х         | 20 <sub>H</sub> | Write            | Х        | 20 <sub>H</sub> |  |

| Erase Verify (5)                      | 2               | Write         | EA        | A0 <sub>H</sub> | Read             | Х        | EVD             |  |

| Set-up Program/Program <sup>(6)</sup> | 2               | Write         | Х         | 40 <sub>H</sub> | Write            | PA       | PD              |  |

| Program Verify <sup>(6)</sup>         | 2               | Write         | Х         | C0 <sub>H</sub> | Read             | Х        | PVD             |  |

| Reset (7)                             | 2               | Write         | X         | FF <sub>H</sub> | Write            | X        | FF <sub>H</sub> |  |

Notes (1) See Bus Operations Table.

(2) IA = Identifier address. 00 for Manufacturers code and 01 for device code.

EA = Address of memory location to be read during Erase Verify.

PA = Address of memory location to be programmed.

RA = Address of memory location to be Read.

Addresses are latched on the falling edge of Write Enable pulse.

(3) ID = Data read from location IA during device identification. (Manufacturer = 89<sub>H</sub>, Device = BD<sub>H</sub>)

EVD = Data read from location EA during Erase Verify.

PD = Data to be programmed at location PA. Data is latched on the rising edge of Write Enable.

RD = Data to be read from location RA during Read operation.

PVD = Data to be read from location PA during Program Verify. PA is latched on the Program command.

- (4) Following the Read Identifier command, two read operations access the manufacturer and device codes.

- (5) See the Erase Algorithm.

- (6) See the Programming Algorithm.

- (7) The second bus cycle must be followed by the desired command register write.

- (8) Wait 6μs after the first Read command before accessing data. When the second bus command is a Read command, all subsequent Read operations take t<sub>ACC</sub>.

Parallel Erase If the PUMA 2F8003 is used in 16 or 32 bit mode then two or four devices will be accessed simultaneously. This reduces the total Erase time, but because individual devices will erase at different rates care must be taken that each device is verified separately. When a device is completely erased and verified a masking code should be used to prevent further erasure e.g. writing the Read Command to the appropriate device. Any other devices will continue to Erase until verified.

**Timing Delays** Four timing delays are associated with the Program and Erase algorithms described:

- (1) When V<sub>PP</sub> first turns on the capacitors on the V<sub>PP</sub> line cause an RC ramp, the rise time of which is proportional to the number of devices being erased and the capacitance per device. V<sub>PP</sub> must reach its final value 100ns before any commands are excecuted.

- (2) The second timing delay is the erase time pulse width of 10ms, which should be timed by a routine run by the local microprocessor. This operation must be terminated before servicing any system interrupts which may occur during the routine. An Erase/Verify command should be written after each

- erase pulse, otherwise the device(s) may continue to erase until the memory cells are driven into depletion. A symptom of this over erasure is an error attempting to Write the next time; occasionally it may be possible to recover this situation by programming all of the locations with 00<sub>µ</sub>.

- (3) Each Write pulse width is 10µs, and since the algorithm is interactive each byte is verified after a Write pulse. The program operation must be terminated at the conclusion of the timing routine or prior to sevicing any interrupts which may occur during this operation.

- (4) A fourth delay is associated with both the Write and Erase algorithms is the Write recovery time of 6μs. In order to improve memory cell operation, an internally generated margin voltage is applied to the addressed cell during Write/Erase Verify. It is during this 6μs delay that the internal circuitry is changing voltage levels between the Erase/Write level and those used for Verify and Read operations. Any attempt to Read the device(s) during this period will result in possible false data appearing on the outputs.

### PROGRAMMING ALGORITHM

These algorithms **MUST BE FOLLOWED** to ensure proper and reliable operation, and are shown for a single device only.

# **START PROGRAM** APPLY VPPH(1) PLSCNT = 0 WRITE SET-UP PROGRAM CMD WRITE PROGRAM CMD (A/D) TIME OUT 10 µs WRITE PROGRAM VERIFY CMD TIME OUT 6 µs READ DATA FROM DEVICE NO NO VERIFY INC PLSCN DATA =25? YES YES INCREMENT LAST ADDRESS **ADDRESS** YES WRITE READ CMD APPLY VPPL (1) APPLY VPPL (1) **PROGRAM PROGRAM** COMPLETE **ERROR**

#### Notes

(1) See DC Characteristics for the value of  $V_{PPH}$ . The  $V_{PP}$  supply can be hard wired to the device or switchable.When  $V_{PP}$  is switched,  $V_{PPL}$  may be GND, NC with a resistor tied to GND or less than  $V_{CC}$ +2.0V

## **ERASE ALGORITHM**

#### **DESIGN CONSIDERATIONS**

**Two Line Control** Two Read signals are provided for output control to accommodate large memory arrays, giving the lowest possible memory power dissipation and ensuring bus contention does not occur.

To use this feature efficiently, an address decoder output should drive the  $\overline{\text{CS}}$  line while the system read signal controls all memories in parallel. This ensures that only enabled memories have active outputs and deselected devices are in the low power Standby condition.

Supply Decoupling Flash memory power-switching characteristics require careful decoupling. Three supply current issues have to be considered - Standby, Active and transient current peaks caused by rising and falling edges of  $\overline{CS}$ .

Two line control and correct decoupling capacitor selection will help to suppress these transient voltage peaks. This module has four on-board decoupling capacitors of  $0.1\mu F$  connected between  $V_{cc}$  and GND. Additionally, a  $0.1\mu F$  or larger capacitor should be placed close to the module between  $V_{pp}$  and GND.

It is recommended that a 4.7 $\mu$ F electrolytic capacitor should be placed between V<sub>cc</sub> and GND every two PUMA 2F8003 modules. This capacitor will smooth out voltage dips in the supply caused by PCB track inductance and will supply charge to the onboard capacitors as needed.

$V_{pp}$  Trace Because Flash memories are designed to be programmed in situ, the PCB designer must be made aware of the  $V_{pp}$  supply trace. This should be made similar to the  $V_{cc}$  bus as the  $V_{pp}$  pin supplies the memory cell current for Programming and Erase.

**Power Up/Down** This Flash module is protected against accidental writes caused by power transitions, powering up in the Read only mode. Additionally, by using two step command register sequences this protection is further enhanced. While these functions are sufficient in most cases, it is recommended that  $V_{cc}$  should reach a steady state value before  $V_{pp}$  is greater than  $V_{cc}+2.0V$ , and during power down  $V_{pp}$  should be less than  $V_{cc}+2.0V$  before lowering  $V_{cc}$ .

ISSUE 1.0 : MARCH 1991 PUMA 2F8003-17/20/25

## Military Screening Procedure

Module Screening Flow for high reliability non compliant product processed to MIL-STD883C Method 5004 is detailed below:

| МВ                                | MB MODULE SCREENING FLOW                                                                                                    |              |  |  |  |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|

| SCREEN                            | TEST METHOD                                                                                                                 | LEVEL        |  |  |  |  |  |  |

| Visual and Mechanical             |                                                                                                                             |              |  |  |  |  |  |  |

| External visual Temperature cycle | 2017 Condition B (or manufacturers equivalent) 1010 Condition C (10 Cycles,-65°C to +150°C)                                 | 100%<br>100% |  |  |  |  |  |  |

| Burn-In                           |                                                                                                                             |              |  |  |  |  |  |  |

| Pre Burn-in Electrical<br>Burn-In | Per Applicable device Specifications at T <sub>A</sub> = +25°C (optional) Method 1015, Condition D, T <sub>A</sub> = +125°C | 100%<br>100% |  |  |  |  |  |  |

| Final Electrical Tests            | Per applicable Device Specification                                                                                         |              |  |  |  |  |  |  |

| Static (dc)                       | a) @ T <sub>x</sub> =+25°C and power supply extremes<br>b) @ temperature and power supply extremes                          | 100%<br>100% |  |  |  |  |  |  |

| Functional                        | a) @ T <sub>x</sub> =+25°C and power supply extremes<br>b) @ temperature and power supply extremes                          | 100%<br>100% |  |  |  |  |  |  |

| Switching (ac)                    | a) @ T <sub>A</sub> =+25°C and power supply extremes<br>b) @ temperature and power supply extremes                          | 100%<br>100% |  |  |  |  |  |  |

| Percent Defective Allowable (PDA) | Calculated at Post Burn-in at T <sub>A</sub> =+25°C                                                                         | 10%          |  |  |  |  |  |  |

| Quality Conformance               | Per applicable Device Specification                                                                                         | Sample       |  |  |  |  |  |  |

| External Visual                   | 2009 Per HMP or customer specification                                                                                      |              |  |  |  |  |  |  |

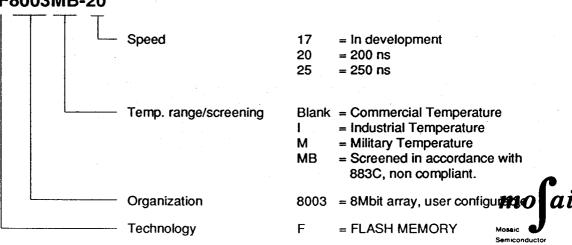

### **Ordering Information**

# PUMA 2F8003MB-20

The policy of the company is one of continuous development and while the information presented in this data sheet is believed to be accurate, no liability is assumed for any data contained within. The company reserves the right to make changes without notice at any time.

© 1988 This design is the property of Mosaic Semiconductor, Inc.

12

MAY 1 7 1993

7420 Carroll Road San Diego, CA 92121 Tel: (619) 271 4565 FAX: (619) 271 6055